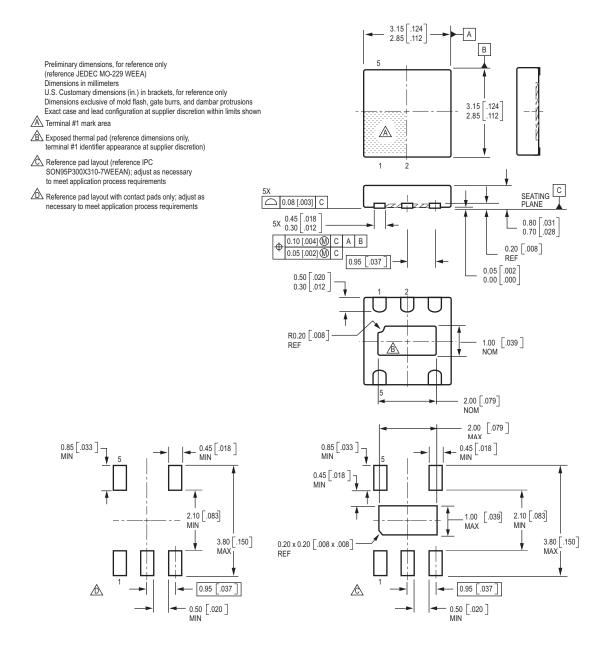

Package EK: MLP/TDFN,  $3 \times 3$  mm 0.75 mm Nominal Height

Approximate Scale 1:1

#### **FEATURES**

- Output voltage up to 35 V

- 2.5 to 10 V input

- 0.9 to 18 V input with separate bias supply

- Delivers 15 V at 15 mA with 2.7 V input

- Constant 1.2 MHz switching frequency provides low noise

- 350 mA switch current limit

- 1 μA shutdown current

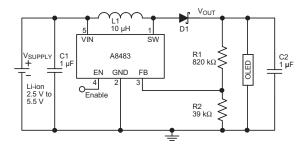

- Low-noise PWM/analog dimming

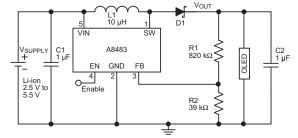

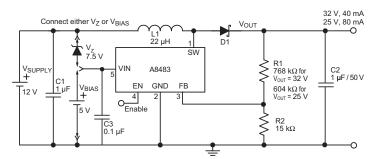

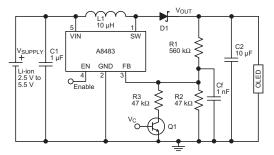

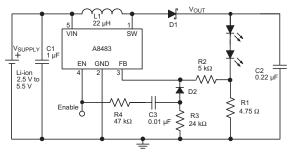

Figure 1. **OLED Bias Supply.** Use for cell phones, MP3 players, DSCs, and PDAs.  $_{\rm 32\,V,\,18\,mA}$

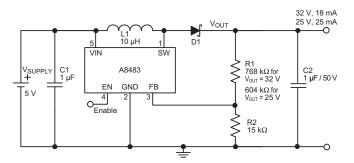

Figure 3. LCD TV, Plasma TV Bias, FED Display, Varactor Diode Bias. Using 5 V input.

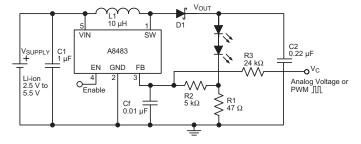

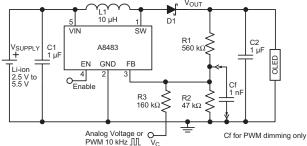

Figure 5. WLED Backlighting.

### A8483

# 1.2 MHz Step-up Converter for Display Bias Supply

The A8483 is a current mode step-up dc-to-dc converter, available in a 5-pin 3 mm × 3 mm thermally enhanced MLP/TDFN lead (Pb) free package. Smaller external components and integrated 36 V switch reduce component count and footprint for a variety of applications.

#### **APPLICATIONS**

- OLED bias supply/WLED backlight

- Portable battery-powered equipment

- Cellular phones

- PDAs (Personal Digital Assistant)

- Camcorders, personal stereos, MP3 players, cameras

- Mobile GPS systems

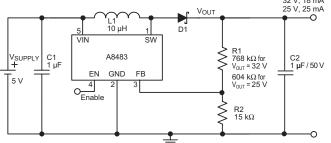

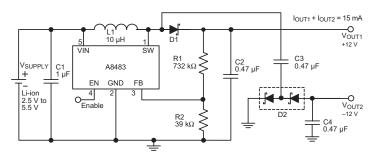

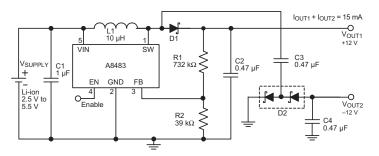

Figure 2. Small LCD Bias Supply. Li+ battery to ±12 V.

Figure 4. LCD TV, Plasma TV Bias, FED Display, Varactor Diode Bias. Using 12 V input.

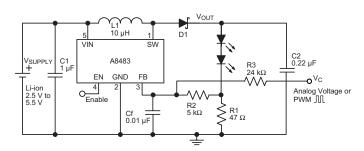

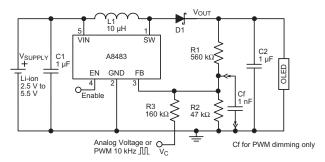

Figure 6. **OLED Bias Supply.** Use for low-noise PWM dimming, or with analog voltage through the FB pin.

#

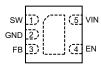

#### Terminal List Table

| Pin | Name | Function           |  |

|-----|------|--------------------|--|

| 1   | SW   | Internal power FET |  |

| 2   | GND  | Ground             |  |

| 3   | FB   | Feedback input     |  |

| 4   | EN   | Enable input       |  |

| 5   | VIN  | Input supply       |  |

### Device Pin-out Diagram

#### **Absolute Maximum Ratings**

| SW Pin                                        | 0.3 to 36 V    |

|-----------------------------------------------|----------------|

| Remaining Pins                                | 0.3 to 10 V    |

| Operating Ambient Temperature, T <sub>A</sub> | 40°C to 85°C   |

| Junction Temperature, T <sub>J(max)</sub>     | 150°C          |

| Storage Temperature T <sub>c</sub>            | -55°C to 150°C |

#### Package Thermal Characteristics

$R_{\rm \theta JA}$  = 50 °C/W, on a 4-layer board. Additional information is available on the Allegro Web site.

ELECTRICAL CHARACTERISTICS at T<sub>A</sub> = 25°C, V<sub>IN</sub> = 3 V (unless otherwise noted)

| Characteristics            | Symbol               | Test Conditions                                         | Min. | Тур. | Max. | Units |

|----------------------------|----------------------|---------------------------------------------------------|------|------|------|-------|

| Input Voltage Range        | V <sub>IN</sub>      | -                                                       | 2.5  | _    | 10   | V     |

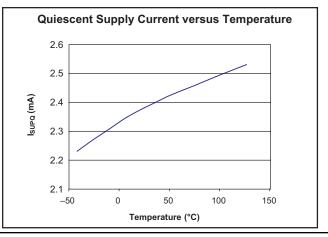

| Supply Current             |                      | Active: I <sub>OUT</sub> =15 mA, V <sub>OUT</sub> =12 V | _    | 2.5  | 3.5  | mA    |

|                            | I <sub>SUP</sub>     | Shutdown (EN=0V)                                        | -    | 0.1  | 1    | μA    |

| Feedback Reference Voltage | V <sub>FB</sub>      | -                                                       | 590  | 615  | 640  | mV    |

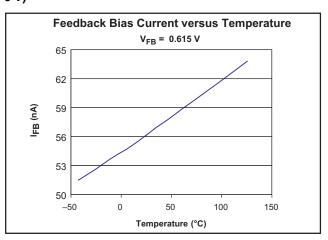

| Feedback Input Current     | I <sub>FB</sub>      | V <sub>FB</sub> = 0.615 V                               | _    | 50   | 100  | nA    |

| Switch Current Limit       | I <sub>SWLIM</sub>   | -                                                       | _    | 350  | _    | mA    |

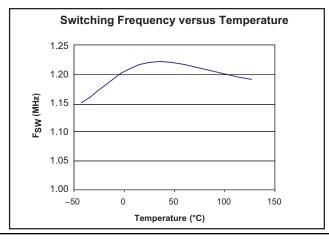

| Switch Frequency           | F <sub>SW</sub>      | -                                                       | 0.8  | 1.2  | 1.6  | MHz   |

| Switch Maximum Duty Cycle  | D                    | -                                                       | 85   | 90   | _    | %     |

| Switch Saturation voltage  | V <sub>CE(SAT)</sub> | I <sub>SW</sub> = 0.2 A                                 | _    | 350  | -    | mV    |

| Switch Leakage Current     | I <sub>SL</sub>      | V <sub>SW</sub> = 36 V                                  | _    | _    | 5    | μA    |

| Enable Input               |                      |                                                         |      |      |      |       |

| Input Threshold Low        | V <sub>IL</sub>      | -                                                       | _    | _    | 0.4  | V     |

| Input Threshold High       | V <sub>IH</sub>      | -                                                       | 1.5  | _    | _    | V     |

| Input Leakage              | Leakage              | I <sub>IL</sub>                                         | _    | _    | 1    | μA    |

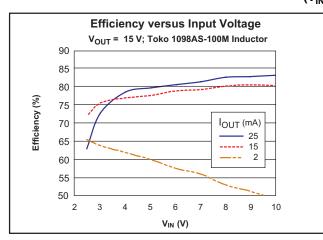

### **Operating Characteristics** $(V_{IN} = 3 V)$

### **Functional Description**

#### Pin Functions

VIN. Supply to the control circuit. A bypass capacitor, C1, must be connected from close to this pin to GND.

GND. Ground reference connected directly to the ground plane. The feedback resistor should have a separate connection directly to this point.

EN. Voltage lower than 0.4 V disables the A8483 and puts the control circuit into the low-power sleep mode. Voltage greater than 1.5 V fully enables the A8483.

SW. Low-side switch connection between the inductor, L1, and ground. Because rapid changes of current occur at this pin, the traces on the PCB that are connected to this pin should be minimized. In addition, L1 and the diode, D1, should be connected as close to this pin as possible.

FB. Feedback pin for OLED voltage control or WLED current control. The reference voltage is 615 mV. Connect the feedback resistor close to this pin to minimize noise.

#### **Device Operation**

The A8483 uses a 1.2 MHz constant switching frequency current-mode control scheme to regulate the output voltage or current through the load.

A typical OLED bias supply is shown in figure 7. For driving OLEDs, output voltage is sensed by the FB pin through a voltage divider network. Output voltage,  $V_{OUT}\left(V\right)$ , is set according to the following equation:

$$V_{\text{OUT}} = \frac{R_1 + R_2}{R_2} \times 0.615$$

(1)

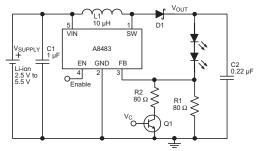

A typical WLED backlight supply is shown in figure 8. The load current,  $I_{LOAD}$ , is set by the selecting the external sense resistor, R1, to produce 615 mV at the desired load, for example:

$$R_1 = 0.615 / I_{\text{LOAD}}$$

(2)

Voltage sensed across the FB pin is compared with the internal 615 mV reference to produce an error signal. The switch current is sensed by the internal sense resistor and compared to the error signal for current mode PWM control. As the error signal increases,  $I_{LOAD}$ , increases to increase either output voltage,  $V_{OUT}$ , or current,  $I_{OUT}$ , such that the FB pin voltage follows the internal 615 mV reference voltage.

As  $I_{LOAD}$  is reduced, the energy required in the inductor, L1, also reduces, resulting in the inductor current dropping to zero for low load current levels. This is known as Discontinuous mode operation and results in some low-frequency ripple. The average load current will, however, remain regulated down to zero. In Discontinuous mode, when  $I_{LOAD}$  drops to zero, the voltage at the SW pin rings, due to the resonant LC circuit formed by L1 and the switch and diode D1 capacitance. This ringing is low-frequency and is not harmful. It can be damped with a resistor across the inductor but this will reduce efficiency and is not recommended.

Figure 8. WLED Backlighting. (Circuit also shown in figure 5.)

### **Applications Information**

#### **Dimming Control**

Display dimming can be achieved by controlling the output voltage,  $V_{OUT}$ , using the FB pin. The circuitry behind the FB pin is flexible, to accommodate a variety of schemes used for dimming:

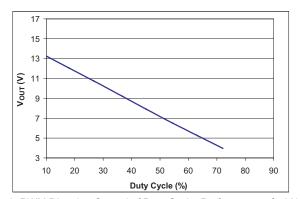

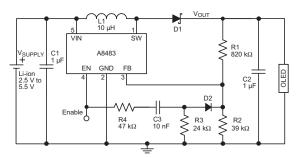

- Adjust the duty cycle of the pulse train applied to the FB pin through resistor R3, as shown in figure 11. Capacitor Cf is used to generate the average voltage level. Variation of output voltage with PWM duty cycle is shown in figure 9.

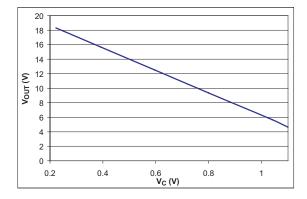

- Apply a constant dc voltage to the FB pin through resistor R3, as shown in figure 12. Variation of output voltage with dc voltage are shown in figure 10.

- Selection of the resistor connected between the FB pin and GND, as shown in figure 12 for OLED applications, and in figure 13 for WLED applications. The voltage drop across the transistor should be negligible compared to the FB sense voltage.

Figure 9. PWM Dimming Control of Duty Cycle. Performance of 5 V input circuit shown in figure 3.

Figure 10. DC Voltage Dimming Control of Duty Cycle. Performance of circuit shown in figure 11.

#### Soft Start

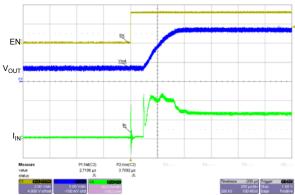

Output voltage rise time at power-on can be extended by using a soft start circuit, such as the one shown in figure 14 for an OLED application, and in figure 16 for a WLED application. At power-on, the device duty cycle begins initially at a high level, drawing a large current from the input supply, VIN. The soft-start circuits shown can reduce the level of current flow by controlling the FB pin.

When a signal is applied to the EN pin, capacitor C3 discharges, pulling the FB pin high, and reducing  $V_{OUT}$  to a minimum. When the EN signal is removed, C3 recharges and as it does, the voltage drop across R3 reduces, allowing the device duty cycle to

Figure 11. OLED Bias Supply. Use for low-noise PWM dimming, or with analog voltage through the FB pin.

Figure 12. OLED Dimming Control. Single-bit resolution using external transistor.

Figure 13. WLED Dimming Control. Single-bit resolution using external transistor.

increase gradually. When the voltage drop across R3 is reduced to less than about 0.8 V, the feedback from the sense resistor, R1, takes over full control of the output voltage.

The length of the soft start delay depends on the combined effect of R2, R3, R4, C3 and the amplitude of the EN signal. The delay can be adjusted by the selection of these values.

#### Component Selection

The component values shown in figure 1 are sufficient for most applications. To reduce output ripple, the value of the output inductor, L1, may be increased, but in most cases this results in excessive board area and additional cost.

Inductor Selection (L1). With an internal PWM frequency of 1.2 MHz, the optimum inductor value for most cases would be 10  $\mu$ H. The inductor should have low winding resistance, typically < 1  $\Omega$ , and the core should have low losses at 1.2 MHz.

For worst-case conditions of high output voltage and current, and low input voltage, the inductor should be rated at the switch current limit of 350 mA.

If high temperature operation is required, derating should be considered. In some cases where lower inductor currents are expected, the current rating can be decreased.

Several inductor manufacturers, including Coilcraft, Murata, Panasonic, Sumida, Taiyo Yuden, and TDK, have and are developing suitably small-size inductors. Two recommended inductors are:

- TDK: NLCV32T-100K-PF, 10 μH

- Toko: 1098AS-100M, 10 μH

Diode Selection (D1). The diode should have a low forward voltage to reduce conduction losses, and a low capacitance to reduce switching losses. Schottky diodes can provide both these features if carefully selected. The forward voltage drop is a natural advantage for Schottky diodes, and it reduces as the current rating of the component increases.

However, as the current rating increases, the diode capacitance also increases, so the optimum selection is usually the lowest current rating above the circuit maximum. In this application, an average current rating of 100 to 200 mA is usually sufficient.

Capacitor Selection. Because the values recommended for the capacitors are low, ceramic capacitors are the best choice for this application. To reduce performance variation over temperature changes, low drift types such as X7R and X5R should be used.

Figure 14. OLED Soft Start Circuit

Figure 15. OLED Soft Start Circuit. Performance of circuit shown in figure 14.

Figure 16. WLED Soft Start Circuit

- C1. A 1.0  $\mu F$  capacitor on the VIN pin is suitable for most applications. In cases where large inductor currents are switched, a larger capacitor may be needed.

- C2. The output capacitor can be as small as 0.22  $\mu$ F for most applications and most  $V_{IN}$  /  $V_{OUT}$  combinations. Increasing this capacitor value aids in reducing ripple and increasing efficiency in low input voltage / high output voltage conditions.

Suitable capacitors are available from: TDK, Taiyo Yuden, Murata, Kemet, and AVX.

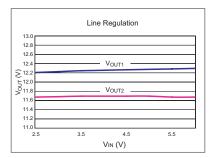

Figure 17. Line Regulation Perfomance for Small LCD Bias Supply,  $I_{OUT1} = I_{OUT2} = 7.5$  mA (circuit also shown in figure 2)

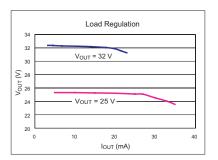

Figure 18.Load Regulation for LCD TV, Plasma TV Bias, FED Display, Varactor Diode Bias; VSUPPLY = 5 V (circuit also shown in figure 3)

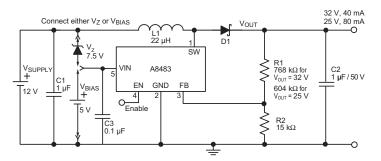

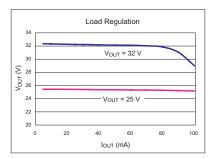

Figure 19. Load Regulation for LCD TV, Plasma TV Bias, FED Display, Varactor Diode Bias;  $V_{SUPPLY}$  = 12 V (circuit also shown in figure 4). The A8483 can operate with a  $V_{SUPPLY}$  from 0.9 to 18 V with a separate bias supply to operate the A8483 in the normal  $V_{IN}$  range. The bias voltage can be supplied by an external power supply, such as 3.3 or 5 V, or by using a suitable Zener diode,  $V_Z$ , for  $V_{SUPPLY} > 10 V$ .

Use the following complete part number when ordering:

| Part Number  | Packing                      | Description   |  |  |

|--------------|------------------------------|---------------|--|--|

| A8483EEKTR-T | 7-in. reel, 1500 pieces/reel | Surface Mount |  |  |

Leadframe plating 100% matte-tin. Solder pad layout compatible with SOT23-5 (SOT95P280-5).

#### Package EK, MLP/TDFN

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copyright© 2005 AllegroMicrosystems, Inc.