### **OVERVIEW**

The 24LLC16 serial EEPROM has a 16 Kbits (2,048 bytes) capacity, supporting the standard I<sup>2</sup>C<sup>™</sup>-bus serial interface. It is fabricated using CERAMATE's most advanced CMOS technology. One of its major features is a hardware-based write protection circuit for the entire memory area. Hardware-based write protection is controlled by the state of the write-protect (WP) pin. Using one-page write mode, you can load up to 16 bytes of data into the EEPROM in a single write operation. Another significant feature of the 24LLC1616 is its support for fast mode and standard mode.

### **FEATURES**

### I<sup>2</sup>C-Bus Interface

- Two-wire serial interface

- Automatic word address increment

#### **EEPROM**

- 16 Kbits (2,048 bytes) storage area

- 16-byte page buffer

- Typical 3 ms write cycle time with . auto-erase function

- Hardware-based write protection for the entire EEPROM (using the WP pin)

- EEPROM programming voltage generated on chip

- 1,000,000 erase/write cycles

- 100 years data retention

### **Operating Characteristics**

- Operating voltage: 2.0 V to 5.5 V

- Operating current

- Maximum write current: < 3 mA at 5.5 V</li>

- Maximum read current: < 200 μA at 5.5 V</li>

- Maximum stand-by current: < 2 μA at 2.0 V</li>

- Operating temperature range

- - 25°C to + 70°C (commercial)

- - 40°C to + 85°C (industrial)

- Operating clock frequencies

- 100 kHz at standard mode

- 400 kHz at fast mode

- Electrostatic discharge (ESD)

- 5,000 V (HBM)

- 400 V (MM)

#### **Packages**

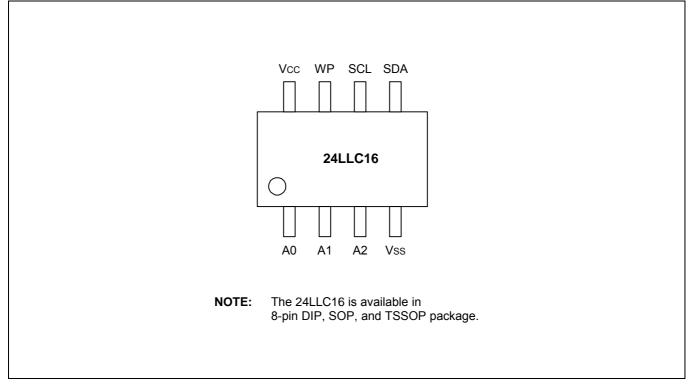

8-pin DIP, SOP, and TSSOP

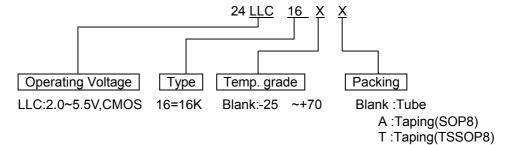

### ORDERING INFORMATION

### 16K-Bit-Serial EEPROM

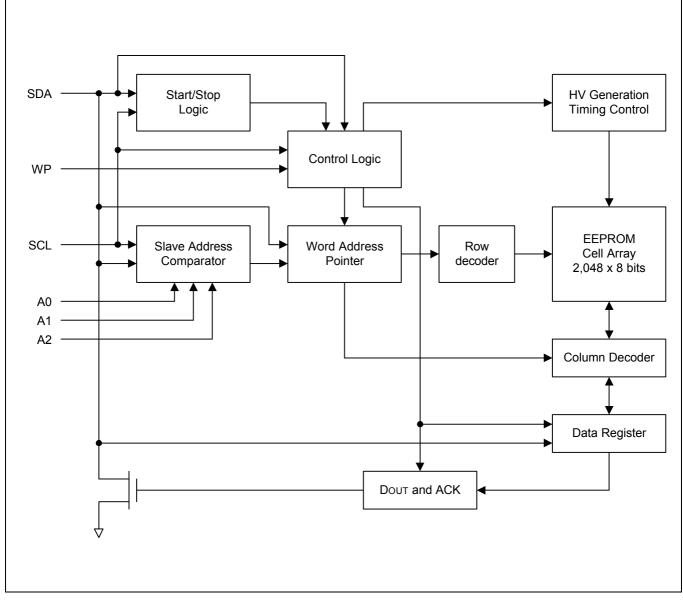

Figure 5-1. 24LLC16 Block Diagram

### 16K-Bit-Serial EEPROM

### Figure 5-2. Pin Assignment Diagram

#### Table 5-1. 24LLC16 Pin Descriptions

| Name            | Туре  | Description                                                                                                                                                                                                                                                                            | Circuit<br>Type |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| A0, A1, A2      | _     | No internal connection                                                                                                                                                                                                                                                                 | -               |

| V <sub>SS</sub> | -     | Ground pin.                                                                                                                                                                                                                                                                            | -               |

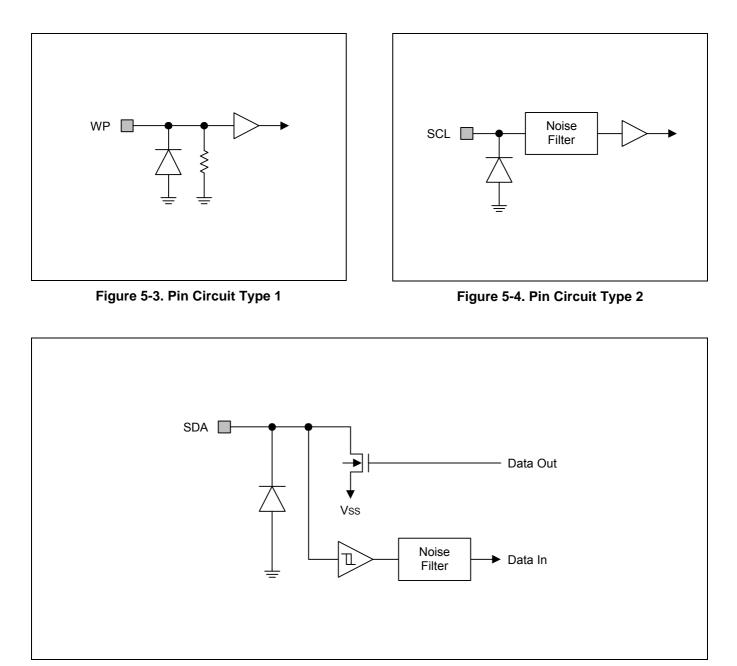

| SDA             | I/O   | Bi-directional data pin for the $I^2$ C-bus serial data interface. Schmitt trigger input and open-drain output. An external pull-up resistor must be connected to $V_{DD}$ .                                                                                                           | 3               |

| SCL             | Input | Schmitt trigger input pin for serial clock input.                                                                                                                                                                                                                                      | 2               |

| WP              | Input | Input pin for hardware write protection control. If you tie this pin to $V_{CC}$ , the write function is disabled to protect previously written data in the entire memory; if you tie it to $V_{SS}$ , the write function is enabled. This pin is internally pulled down to $V_{SS}$ . | 1               |

| V <sub>CC</sub> | _     | Single power supply.                                                                                                                                                                                                                                                                   | _               |

**NOTE**: See the following page for diagrams of pin circuit types 1, 2, and 3.

### 16K-Bit-Serial EEPROM

Figure 5-5. Pin Circuit Type 3

### 16K-Bit-Serial EEPROM

### FUNCTION DESCRIPTION

### I<sup>2</sup>C-BUS INTERFACE

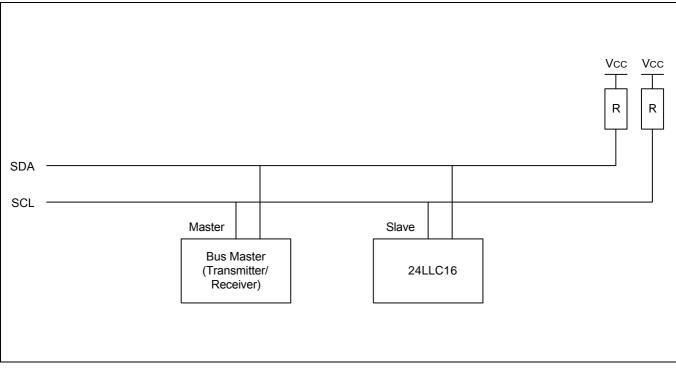

The 24LLC16 supports the  $I^2$ C-bus serial interface data transmission protocol. The two-wire bus consists of a serial data line (SDA) and a serial clock line (SCL). The SDA and the SCL lines must be connected to V<sub>CC</sub> by a pull-up resistor that is located somewhere on the bus.

Any device that puts data onto the bus is defined as a "transmitter" and any device that gets data from the bus is a "receiver." The bus is controlled by a master device which generates the serial clock and start/stop conditions, controlling bus access. Only one 24LLC16 devices can be connected to the I<sup>2</sup>C-bus as slaves (see Figure 5-6). Both the master and slaves can operate as a transmitter or a receiver, but the master device determines which bus operating mode would be active.

Figure 5-6. Typical Configuration

### 16K-Bit-Serial EEPROM

### I<sup>2</sup>C-BUS PROTOCOLS

Here are several rules for  $I^2C$ -bus transfers:

- A new data transfer can be initiated only when the bus is currently not busy.

- MSB is always transferred first in transmitting data.

- During a data transfer, the data line (SDA) must remains stable whenever the clock line (SCL) is High.

The I<sup>2</sup>C-bus interface supports the following communication protocols:

- Bus not busy: The SDA and the SCL lines remain in High level when the bus is not active.

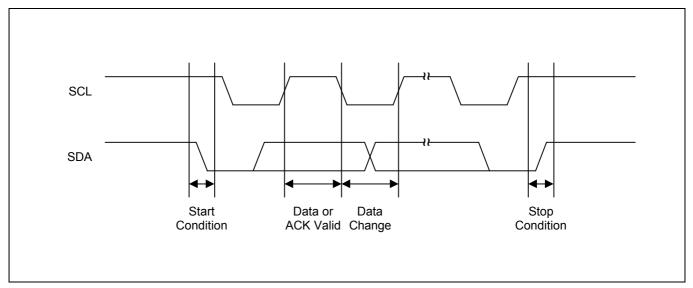

- <u>Start condition</u>: A start condition is initiated by a High-to-Low transition of the SDA line while SCL remains in High level. All bus commands must be preceded by a start condition.

- <u>Stop condition</u>: A stop condition is initiated by a Low-to-High transition of the SDA line while SCL remains in High level. All bus operations must be completed by a stop condition (see Figure 5-7).

Figure 5-7. Data Transmission Sequence

- <u>Data valid</u>: Following a start condition, the data becomes valid if the data line remains stable for the duration of the High period of SCL. New data must be put onto the bus while SCL is Low. Bus timing is one clock pulse per data bit. The number of data bytes to be transferred is determined by the master device. The total number of bytes that can be transferred in one operation is theoretically unlimited.

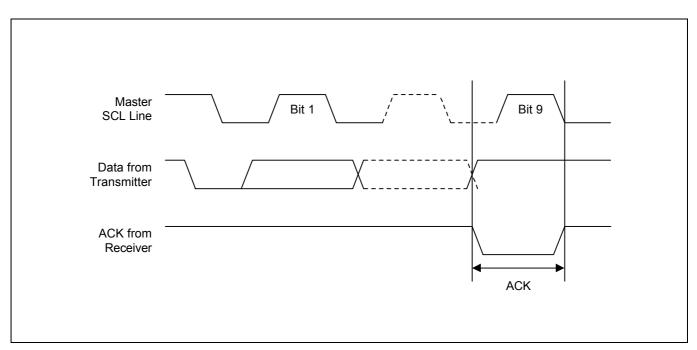

- <u>ACK (Acknowledge)</u>: An ACK signal indicates that a data transfer is completed successfully. The transmitter (the master or the slave) releases the bus after transmitting eight bits. During the 9th clock, which the master generates, the receiver pulls the SDA line low to acknowledge that it has successfully received the eight bits of data (see Figure 5-8). But the slave does not send an ACK if an internal write cycle is still in progress.

In data read operations, the slave releases the SDA line after transmitting 8 bits of data and then monitors the line for an ACK signal during the 9th clock period. If an ACK is detected, the slave will continue to transmit data. If an ACK is not detected, the slave terminates data transmission and waits for a stop condition to be issued by the master before returning to its stand-by mode.

16K-Bit-Serial EEPROM

Figure 5-8. Acknowledge Response From Receiver

- <u>Slave Address</u>: After the master initiates a start condition, it must output the address of the device to be accessed. The most significant four bits of the slave address are called the "device identifier." The identifier for the 24LLC16 is "1010B". The next three bits (B2, B1, B0) are for block selection. They are used by the master to select which of the blocks of internal memory (1 block=256 words) are to be accessed. (see Table 5-2 below.) These bits are in effect the three most significant bits of the word address

- <u>Read/Write</u>: The final (eighth) bit of the slave address defines the type of operation to be performed. If the R/w bit is "1", a read operation is executed. If it is "0", a write operation is executed.

| Function | Device Identifier |    |    | ier | Block Select |    |    | R/W Bit |

|----------|-------------------|----|----|-----|--------------|----|----|---------|

|          | b7                | b6 | b5 | b4  | b3           | b2 | b1 | b0      |

| Read     | 1                 | 0  | 1  | 0   | B2           | B1 | B0 | 1       |

| Write    | 1                 | 0  | 1  | 0   | B2           | B1 | B0 | 0       |

| Table | 5-2. | Slave | Address | Bvte |

|-------|------|-------|---------|------|

|       |      |       |         |      |

#### BYTE WRITE OPERATION

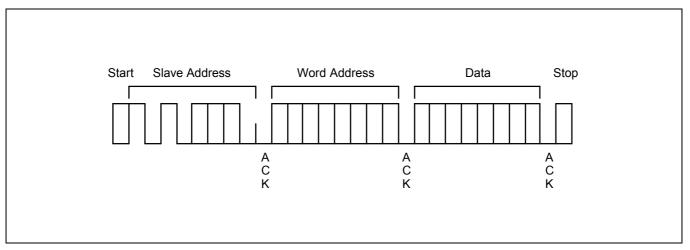

In a complete byte write operation, the master transmits the slave address, word address, and one data byte to the 24LLC16 slave device (see Figure 5-9).

Figure 5-9. Byte Write Operation

Following a start condition, the master sends the device identifier (4 bits), three "don't care" bits, and an R/W bit set to "0" onto the bus. Then the addressed 24LLC16 generates an ACK, and waits for the next byte. The next byte to be transmitted by the master is the word address. This 8-bit address is written into the word address pointer of the 24LLC16

When the 24LLC16 receives the word address, it responds by issuing an ACK and then waits for the next 8bit data. When it receives the data byte, the 24LLC16 again responds with an ACK. The master terminates the transfer by generating a Stop condition, at which time the 24LLC16 begins the internal write cycle.

While the internal write cycle is in progress, all 24LLC16 inputs are disabled and the 24LLC16 does not respond to any additional request from the master.

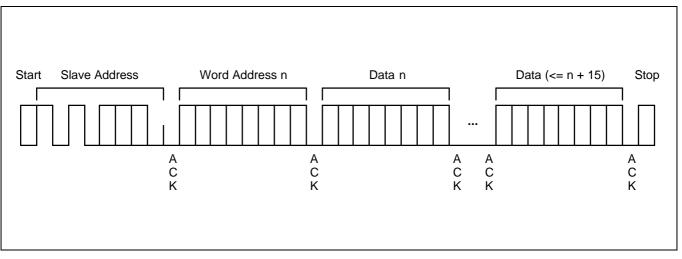

#### PAGE WRITE OPERATION

The 24LLC16 can also perform 16-byte page write operation. A page write operation is initiated in the same way as a byte write operation. However, instead of finishing the write operation after the first data byte is transferred, the master can transmit up to 15 additional bytes. The 24LLC166 responds with an ACK each time it receives a complete byte of data (see Figure 5-10).

Figure 5-10. Page Write Operation

The 24LLC16 automatically increments the word address pointer each time it receives a complete data byte. When one byte is received, the internal word address pointer increments to the next address so that the next data byte can be received.

If the master transmits more than 16 bytes before it generates a stop condition to end the page write operation, the 24LLC16 word address pointer value "rolls over" and the previously received data is overwritten. If the master transmits less than 16 bytes and generates a stop condition, the 24LLC16 writes the received data to the corresponding EEPROM address.

During a page write operation, all inputs are disabled and there would be no response to additional requests from the master until the internal write cycle is completed.

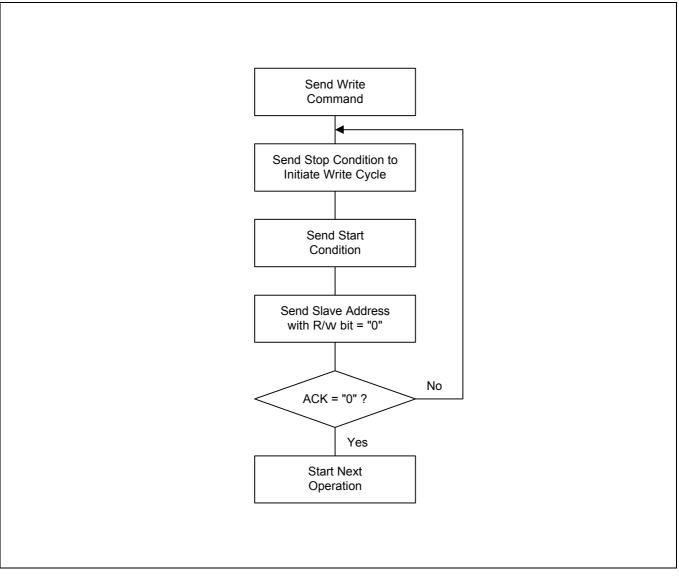

#### POLLING FOR AN ACK SIGNAL

When the master issues a stop condition to initiate a write cycle, the 24LLC16 starts an internal write cycle. The master can then immediately begin polling for an ACK from the slave device to determine whether the write cycle is completed.

To poll for an ACK signal in a write operation, the master issues a start condition followed by the slave address. As long as the 24LLC16 remains busy with the write operation, no ACK is returned. When the 24LLC16 completes the write operation, it returns an ACK and the master can then proceed with the next read or write operation (see Figure 5-11).

Figure 5-11. Master Polling for an ACK Signal from a Slave Device

### 16K-Bit-Serial EEPROM

#### HARDWARE-BASED WRITE PROTECTION

You can also write-protect the entire memory area of the 24LLC16 This method of write protection is controlled by the state of the Write Protect (WP) pin.

When the WP pin is connected to  $V_{CC}$ , any attempt to write a value to the memory is ignored.

The 24LLC16 will acknowledge slave and word address, but it will not generate an acknowledge after receiving first byte of data. In this situation the write cycle will not be started when a stop condition is generated. By connecting the WP pin to  $V_{SS}$ , the write function is allowed for the entire memory.

These write protection features effectively change the EEPROM to a ROM in order to protect data from being overwritten. Whenever the write function is disabled, a slave address and a word address are acknowledged on the bus, but data bytes are not acknowledged.

The WP pin is internally pulled down to V<sub>SS.</sub>

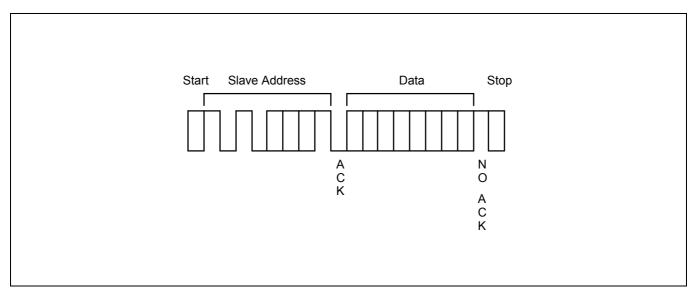

### CURRENT ADDRESS BYTE READ OPERATION

The internal word address pointer maintains the address of the last word accessed, incremented by one. Therefore, if the last access (either read or write) was to the address "n", the next read operation would access data at address "n+1".

When the 24LLC16 receives a slave address with the R/W bit set to "1", it issues an ACK and sends eight bits of data. In a current address byte read operation the master does not acknowledge the data, and it generates a Stop condition, forcing the 24LLC16 to stop the transmission (see Figure 5-12).

Figure 5-12. Current Address Byte Read Operation

### 16K-Bit-Serial EEPROM

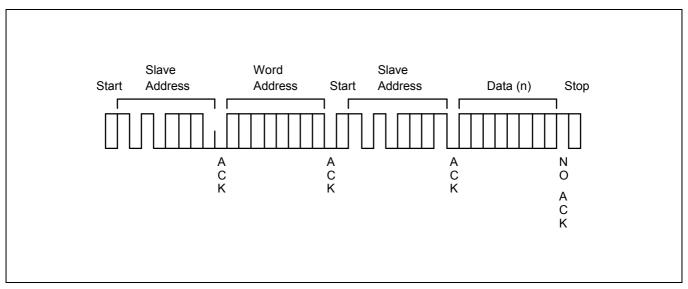

#### **RANDOM ADDRESS BYTE READ OPERATION**

Using random read operations, the master can access any memory location at any time. Before it issues the slave address with the R/W bit set to "1", the master must first perform a "dummy" write operation. This operation is performed in the following steps:

- The master first issues a start condition, the slave address, and the word address to be read. (This step sets 1. the internal word address pointer of the 24LLC16 to the desired address.)

- 2. When the master receives an ACK for the word address, it immediately re-issues a start condition followed by another slave address, with the R/W bit set to "1".

- 3. The 24LLC16 then sends an ACK and the 8-bit data stored at the pointed address.

- 4. At this point, the master does not acknowledge the transmission, generating a stop condition.

- 5. The 24LLC16 stops transmitting data and reverts to stand-by mode (see Figure 5-13).

Figure 5-13. Random Address Byte Read Operation

#### SEQUENTIAL READ OPERATION

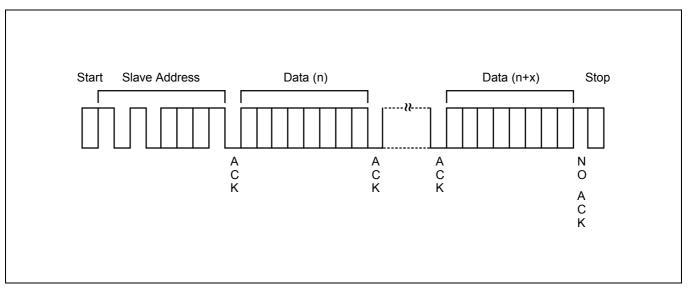

Sequential read operations can be performed in two ways: current address sequential read operation, and random address sequential read operation. The first data is sent in either of the two ways, current address byte read operation described earlier. If the master responds with an ACK, the 24LLC16 continues transmitting data. If the master does not issue an ACK, generating a stop condition, the slave stops transmission, ending the sequential read operation.

Using this method, data is output sequentially from address "n" followed by address "n+1". The word address pointer for read operations increments to all word addresses, allowing the entire EEPROM to be read sequentially in a single operation. After the entire EEPROM is read, the word address pointer "rolls over" and the 24LLC16 continues to transmit data for each ACK it receives from the master (see Figure 5-14).

Figure 5-14. Sequential Read Operation

### ELECTRICAL DATA

### Table 5-3. Absolute Maximum Ratings

### (T<sub>A</sub> = 25 °C)

| Parameter               | Symbol           | Conditions | Rating        | Unit |

|-------------------------|------------------|------------|---------------|------|

| Supply voltage          | V <sub>CC</sub>  | -          | -0.3 to +7.0  | V    |

| Input voltage           | V <sub>IN</sub>  | -          | -0.3 to +7.0  | V    |

| Output voltage          | Vo               | -          | -0.3 to +7.0  | V    |

| Operating temperature   | T <sub>A</sub>   | _          | - 40 to + 85  | °C   |

| Storage temperature     | T <sub>STG</sub> | -          | - 65 to + 150 | °C   |

| Electrostatic discharge | V <sub>ESD</sub> | HBM        | 5000          | V    |

|                         |                  | MM         | 400           |      |

### Table 5-4. D.C. Electrical Characteristics

(T<sub>A</sub> = -25 °C to + 70 °C (Commercial), -40 °C to + 85 °C (Industrial), V<sub>CC</sub> = 2.0 V to 5.5 V)

| Parameter           |                    | Symbol           | Conditions                                      | Min                 | Тур | Max                 | Unit |

|---------------------|--------------------|------------------|-------------------------------------------------|---------------------|-----|---------------------|------|

| Input low voltage   |                    | V <sub>IL</sub>  | SCL, SDA                                        | -                   | -   | 0.3 V <sub>CC</sub> | V    |

| Input high voltage  |                    | V <sub>IH</sub>  |                                                 | 0.7 V <sub>CC</sub> | _   | -                   | V    |

| Input leakage curre | nt                 | I <sub>LI</sub>  | $V_{IN} = 0$ to $V_{CC}$                        | -                   | _   | 10                  | μA   |

| Output leakage curr | rent               | I <sub>LO</sub>  | $V_{O} = 0$ to $V_{CC}$                         | -                   | _   | 10                  | μA   |

| Output Low voltage  | Output Low voltage |                  | I <sub>OL</sub> = 3 mA, V <sub>CC</sub> = 2.0 V | -                   | _   | 0.4                 | V    |

| Supply current      | Write              | I <sub>CC1</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                | -                   | _   | 3                   | mA   |

|                     |                    | I <sub>CC2</sub> | V <sub>CC</sub> = 2.0 V, 100 kHz                | -                   | _   | 1                   |      |

|                     | Read               | I <sub>CC3</sub> | V <sub>CC</sub> = 5.5 V, 400 kHz                | -                   | _   | 0.2                 |      |

|                     |                    | I <sub>CC4</sub> | V <sub>CC</sub> = 2.0 V, 100 kHz                | -                   | _   | 60                  | μA   |

| Stand-by current    |                    | I <sub>CC5</sub> | V <sub>CC</sub> = SDA = SCL = 5.5 V,            | -                   | _   | 5                   | μA   |

|                     |                    |                  | all other inputs = 0 V                          |                     |     |                     |      |

|                     |                    | I <sub>CC6</sub> | V <sub>CC</sub> = SDA = SCL = 2.0 V,            | —                   | -   | 2                   |      |

|                     |                    |                  | all other inputs = 0 V                          |                     |     |                     |      |

### 16K-Bit-Serial EEPROM

### Table 5-4. D.C. Electrical Characteristics (Continued)

$(T_A = -25 \degree C \text{ to } + 70 \degree C \text{ (Commercial)}, -40 \degree C \text{ to } + 85 \degree C \text{ (Industrial)}, V_{CC} = 2.0 \text{ V to } 5.5 \text{ V})$

| Parameter                | Symbol           | Conditions                                                                    | Min | Тур | Max | Unit |

|--------------------------|------------------|-------------------------------------------------------------------------------|-----|-----|-----|------|

| Input capacitance        | C <sub>IN</sub>  | 25 °C, 1MHz,<br>$V_{CC}$ = 5 V, $V_{IN}$ = 0 V,<br>A0, A1, A2, SCL and WP pin | _   | _   | 10  | pF   |

| Input/Output capacitance | C <sub>I/O</sub> | 25 °C, 1MHz,<br>V <sub>CC</sub> = 5 V, V <sub>I/O</sub> = 0 V,<br>SDA pin     | _   | _   | 10  |      |

### Table 5-5. A.C. Electrical Characteristics

| $(T_A = -25 \degree C \text{ to } + 70 \degree C \text{ (Commercial)}, -40 \degree C \text{ to } + 85$ | $^{\circ}$ C (Industrial), V <sub>CC</sub> = 2.0 V to 5.5 V) |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Parameter                                       | Symbol              | Conditions              | Conditions V <sub>CC</sub> = 2.0<br>(Standard |         |     |         | Unit |

|-------------------------------------------------|---------------------|-------------------------|-----------------------------------------------|---------|-----|---------|------|

|                                                 |                     |                         | Min                                           | Max     | Min | Max     |      |

| External clock frequency                        | F <sub>clk</sub>    | -                       | 0                                             | 100 (1) | 0   | 400 (1) | kHz  |

| Clock High time                                 | t <sub>HIGH</sub>   | -                       | 4                                             | -       | 0.6 | -       | μs   |

| Clock Low time                                  | t <sub>LOW</sub>    | -                       | 4.7                                           | -       | 1.3 | -       | μs   |

| Rising time                                     | t <sub>R</sub>      | SDA, SCL                | _                                             | 1       | -   | 0.3     | μs   |

| Falling time                                    | t <sub>F</sub>      | SDA, SCL                | _                                             | 0.3     | -   | 0.3     | μs   |

| Start condition hold time                       | t <sub>HD:STA</sub> | -                       | 4                                             | -       | 0.6 | -       | μs   |

| Start condition setup time                      | t <sub>SU:STA</sub> | -                       | 4.7                                           | -       | 0.6 | -       | μs   |

| Data input hold time                            | t <sub>HD:DAT</sub> | -                       | 0                                             | -       | 0   | -       | μs   |

| Data input setup time                           | t <sub>SU:DAT</sub> | -                       | 0.25                                          | -       | 0.1 | -       | μs   |

| Stop condition setup time                       | t <sub>SU:STO</sub> | -                       | 4                                             | -       | 0.6 | -       | μs   |

| Bus free time                                   | t <sub>BUF</sub>    | Before new transmission | 4.7                                           | _       | 1.3 | -       | μs   |

| Data output valid from clock low <sup>(2)</sup> | t <sub>AA</sub>     | -                       | 0.3                                           | 3.5     | _   | 0.9     | μs   |

| Noise spike width                               | t <sub>SP</sub>     | -                       | _                                             | 100     | -   | 50      | ns   |

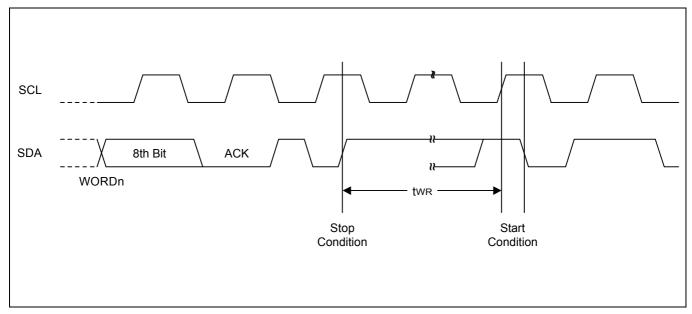

| Write cycle time                                | t <sub>WR</sub>     | -                       | _                                             | 5       | -   | 5       | ms   |

#### NOTES:

1. Upon customers request, up to 400 kHz (Max.) in standard mode and 1 MHz in fast mode are available.

2. When acting as a transmitter, the 24LLC16 must provide an internal minimum delay time to bridge the undefined period (minimum 300 ns) of the falling edge of SCL. This is required to avoid unintended generation of a start or stop condition.

16K-Bit-Serial EEPROM

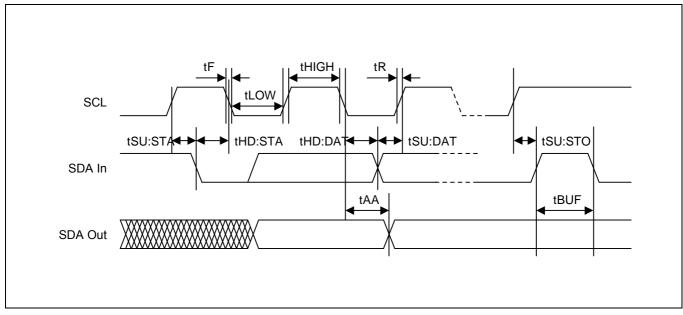

Figure 5-15. Timing Diagram for Bus Operations

Figure 5-16. Write Cycle Timing Diagram

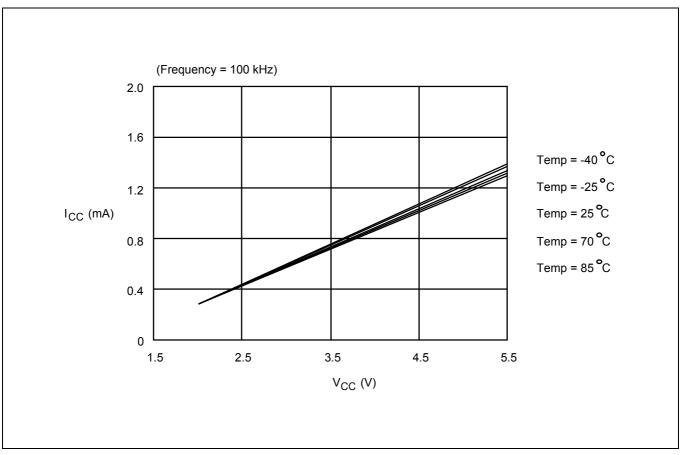

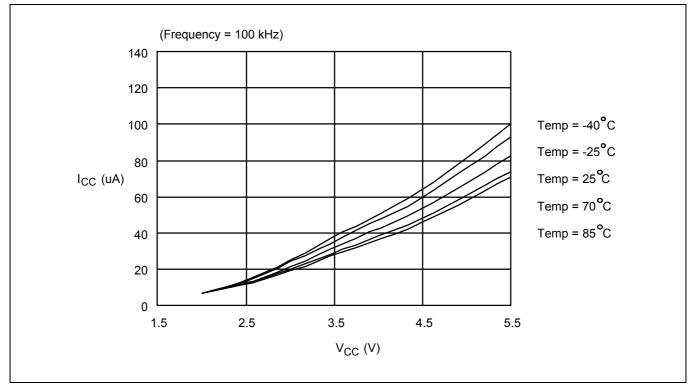

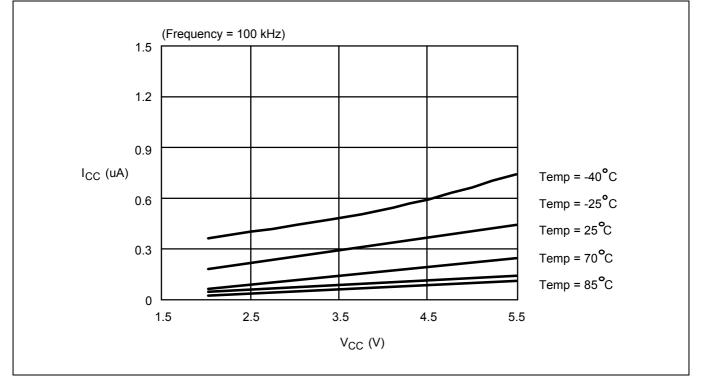

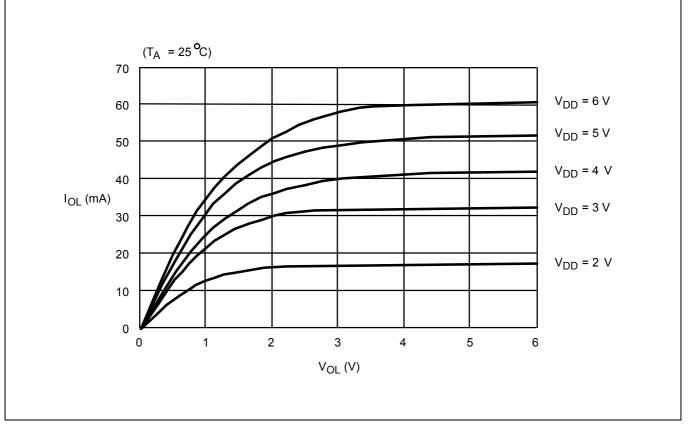

### CHARACTERISTIC CURVES

### NOTE

The characteristic values shown in the following graphs are based on actual test measurements. They do not, however, represent guaranteed operating values.

Figure 5-17. Write Current

### 16K-Bit-Serial EEPROM

Figure 5-18. Read Current

Figure 5-19. Stand-by Current

16K-Bit-Serial EEPROM

Figure 5-20. Output Low Voltage

### 16K-Bit-Serial EEPROM

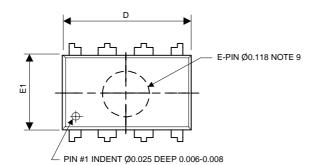

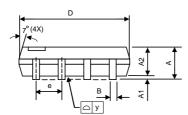

### Package Information

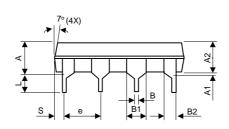

(1) PDIP-8L

| SYMBOL | DIMEN | SIONS IN MILLIN | <b>METERS</b> | DIMENSIONS IN INCHS |       |       |  |

|--------|-------|-----------------|---------------|---------------------|-------|-------|--|

| STMBUL | MIN   | NOM             | MAX           | MIN                 | NOM   | MAX   |  |

| Α      | -     | -               | 5.33          | -                   | -     | 0.210 |  |

| A1     | 0.38  | -               | -             | 0.015               | -     | -     |  |

| A2     | 3.25  | 3.30            | 3.45          | 0.128               | 0.130 | 0.136 |  |

| В      | 0.36  | 0.46            | 0.56          | 0.014               | 0.018 | 0.022 |  |

| B1     | 1.14  | 1.27            | 1.52          | 0.045               | 0.050 | 0.060 |  |

| B2     | 0.81  | 0.99            | 1.17          | 0.032               | 0.039 | 0.046 |  |

| С      | 0.20  | 0.25            | 0.33          | 0.008               | 0.010 | 0.013 |  |

| D      | 9.12  | 9.30            | 9.53          | 0.359               | 0.366 | 0.375 |  |

| Е      | 7.62  | -               | 8.26          | 0.300               | -     | 0.325 |  |

| E1     | 6.20  | 6.35            | 6.60          | 0.244               | 0.250 | 0.260 |  |

| е      | -     | 2.54            | -             | -                   | 0.100 | -     |  |

| L      | 3.18  | -               | -             | 0.125               | -     | -     |  |

| Eb     | 8.38  | -               | 9.40          | 0.330               | -     | 0.370 |  |

| S      | 0.71  | 0.84            | 0.97          | 0.028               | 0.033 | 0.038 |  |

### 16K-Bit-Serial EEPROM

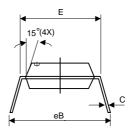

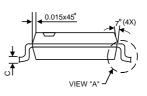

### (2) SOP-8L(JEDEC)

| SYMBOL | DIMEN          | SIONS IN MILLIN | IETERS | DIMENSIONS IN INCHS |       |        |  |

|--------|----------------|-----------------|--------|---------------------|-------|--------|--|

| STMBOL | MIN            | NOM             | MAX    | MIN                 | NOM   | MAX    |  |

| А      | 1.47           | 1.60            | 1.73   | 0.058               | 0.063 | 0.068  |  |

| A1     | 0.10           | -               | 0.25   | 0.004               | -     | 0.010  |  |

| A2     | -              | 1.45            | -      | -                   | 0.057 | -      |  |

| В      | 0.33           | 0.41            | 0.51   | 0.013               | 0.016 | 0.020  |  |

| С      | 0.19           | 0.20            | 0.25   | 0.0075              | 0.008 | 0.0098 |  |

| D      | 4.80           | 4.85            | 4.95   | 0.189               | 0.191 | 0.195  |  |

| E      | 3.81           | 3.91            | 3.99   | 0.150               | 0.154 | 0.157  |  |

| е      | -              | 1.27            | -      | -                   | 0.050 | -      |  |

| н      | 5.79           | 5.99            | 6.20   | 0.228               | 0.236 | 0.244  |  |

| L      | 0.38           | 0.71            | 1.27   | 0.015               | 0.028 | 0.050  |  |

| Y      | -              | -               | 0.10   | -                   | -     | 0.004  |  |

|        | 0 <sup>°</sup> | -               | 8°     | 0 <sup>°</sup>      | -     | 8°     |  |

### 16K-Bit-Serial EEPROM

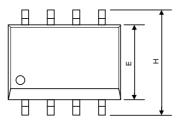

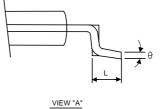

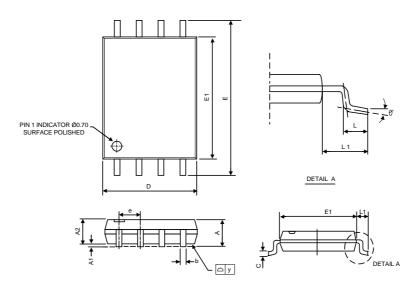

(3) TSSOP-8L

| SYMBOLS  | DIN  | IENSIONS IN MILLIMETE | RS   |

|----------|------|-----------------------|------|

| STIMBULS | MIN  | NOM                   | MAX  |

| A        | 1.05 | 1.10                  | 1.20 |

| A1       | 0.05 | 0.10                  | 0.15 |

| A2       | -    | 1.00                  | 1.05 |

| В        | 0.20 | 0.25                  | 0.28 |

| С        | -    | 0.127                 | -    |

| D        | 2.90 | 3.05                  | 3.10 |

| E        | 6.20 | 6.40                  | 6.60 |

| E1       | 4.30 | 4.40                  | 4.50 |

| E        | -    | 0.65                  | -    |

| L        | 0.50 | 0.60                  | 0.70 |

| L1       | 0.90 | 1.00                  | 1.10 |

| Y        | -    | -                     | 0.10 |

|          | 0°   | 4 <sup>o</sup>        | 8°   |