# SANYO Semiconductors DATA SHEET

# LV24010LP — Compact Portable Equipment 1-Chip FM+RDS Tuner IC

#### **Overview**

The LV24010LP is single-chip FM radio with RDS tuner IC that requires absolutely no external components. This design was achieved by combining Sanyo BiCMOS process technology, Sanyo packaging technology, and filtering circuit technology developed by Semiconductor Ideas to the Market (ItoM) B.V.

• Tuning.

• Standby.

• RDS.

#### **Functions**

- FM FE.

- FM IF.

- MPX stereo decoder.

# **Specifications**

#### Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                   | Symbol                | Conditions                   | Ratings              | unit |

|-----------------------------|-----------------------|------------------------------|----------------------|------|

| Maximum supply voltage      | V <sub>CC</sub> max   | Analog block supply voltage  | 5.0                  | V    |

|                             | V <sub>DD</sub> max   | Digital block supply voltage | 4.5                  | V    |

| Maximum input voltage       | V <sub>IN</sub> 1 max | Clock, Data, NR-W            | V <sub>DD</sub> +0.3 | V    |

|                             | V <sub>IN</sub> 2 max | Extenal_clk_in               | V <sub>DD</sub> +0.3 | V    |

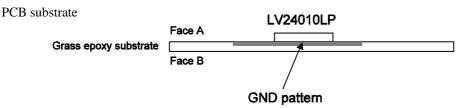

| Allowable power dissipation | Pd max                | Ta≤70°C *                    | 140                  | mW   |

| Storage temperature         | Tstg                  |                              | -40 to +125          | °C   |

| Operating temperature       | Topr                  |                              | -20 to +70           | °C   |

\*: With  $40 \times 50 \times 0.8 \text{mm}^3$ , glass epoxy substrate

#### **Operating Conditions** at Ta = 25 °C

| Parameter                      | Symbol             | Conditions                   | Ratings    | unit |

|--------------------------------|--------------------|------------------------------|------------|------|

| Decommended complexities       | V <sub>CC</sub>    | Analog block supply voltage  | 3.0        | V    |

| Recommended supply voltage     | V <sub>DD</sub>    | Digital block supply voltage | 3.0        | V    |

| Operating supply voltage range | V <sub>CC op</sub> |                              | 2.7 to 5.0 | V    |

|                                | V <sub>DD op</sub> |                              | 2.5 to 4.0 | V    |

|                                | V <sub>IO op</sub> | Interface voltage            | 1.8 to 4.0 | V    |

Note: The application voltage of V<sub>IO</sub> to be used must be either equal to V<sub>DD</sub> or the V<sub>DD</sub> value or less (V<sub>IO</sub>  $\leq$  V<sub>DD</sub>).

- Any and all SANYO Semiconductor products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO Semiconductor representative nearest you before using any SANYO Semiconductor products described or contained herein in such applications.

- SANYO Semiconductor assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor products described or contained herein.

#### SANYO Semiconductor Co., Ltd. TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

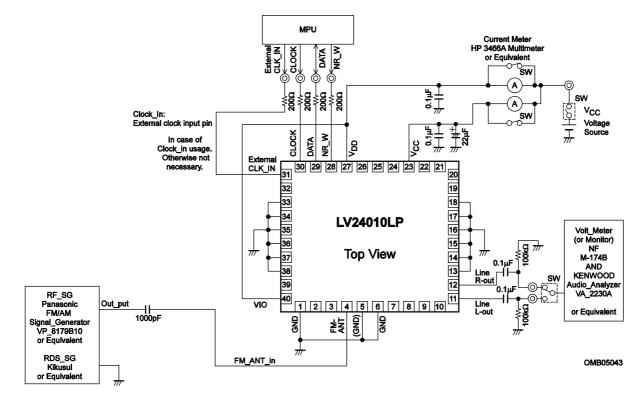

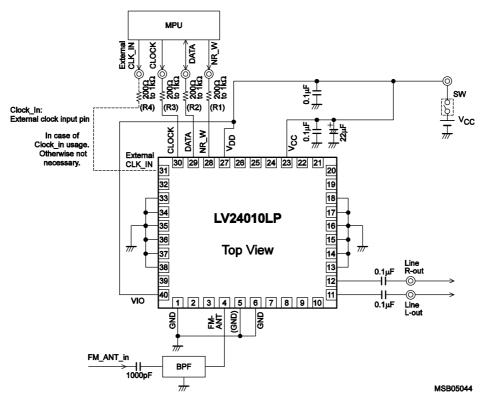

**Electrical Characteristics** at Ta = 25°C,  $V_{CC}$  = 3.0V,  $V_{DD}$  = 3.0V, in the measuring circuit specified, Soft

| Mute/Stereo = off |  |

|-------------------|--|

|                   |  |

| Parameter                            | Symbol         | Symbol Conditions                                                                                                                                       |                | Ratings       |       |             |  |

|--------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|---------------|-------|-------------|--|

|                                      | Gynbol         | Conditions                                                                                                                                              | min            | nin typ max   |       | unit        |  |

| Current drain<br>(in operation)      | ICCA           | Measurement at pin 23 with 60 dB $\!\mu$ input in the analog block, Monaural input                                                                      |                | 15            | 19    | mA          |  |

|                                      | ICCD           | Measurement at pins 27 and 40 with 60 dB $_{\mu}$ input in the digital block                                                                            | 0.2            | 0.4           | 0.8   | mA          |  |

| Current drain<br>(in standby)        | ICCA           | Measurement at pin 23 in the standby mode of the analog block                                                                                           |                | 3             | 30    | μA          |  |

|                                      | ICCD           | Measurement at pins 27 and 40 in the standby mode of the digital block.                                                                                 |                | 3             | 30    | μA          |  |

| FM receive band                      | F_range        |                                                                                                                                                         | 76             |               | 108   | MHz         |  |

| FM receive characteristics;          | MONO: fc = 80M | Hz,fm = 1kHz, 22.5kHzdev. Note that Soft_stereo,Soft_a                                                                                                  | nd mute funct  | ions are OFF. |       |             |  |

| 3dB sensitivity                      | -3dB LS        | 60dBµV, 22.5kHzdev output standard,<br>-3dB input -3dB.                                                                                                 |                | 13            | 20    | dBμ\<br>EMF |  |

| Practical sensitivity 1              | QS1            | · · ·                                                                                                                                                   |                | 10            | 17    | dBµ∖<br>EMF |  |

| Practical sensitivity 2 (Reference)  | QS2            | Input level with S/N = 26dB,<br>Deemphasis = 75μs, SG terminal display                                                                                  |                | 1.25          |       | μV          |  |

| Demodulation output                  | Vo             | 60dBμV, pin 11 output                                                                                                                                   | 50             | 70            | 110   | mV          |  |

| Channel balance                      | СВ             | 60dBμV, pin 11 output / pin 12 output                                                                                                                   | -2             | 0             | 2     | dB          |  |

| Signal-to-noise ratio                | S/N            | 60dBμV, pin 11 output                                                                                                                                   | 48             | 58            |       | dB          |  |

| Total harmonic distortion<br>1(MONO) | THD1           | 60dBμV, pin 11 output, 22.5kHdev                                                                                                                        |                | 0.4           | 1.5   | %           |  |

| Total harmonic distortion 2(MONO)    | THD2           | 60dBμV, pin 11 output, 75kHdev                                                                                                                          |                | 1.3           | 3     | %           |  |

| Field intensity display level        | FS             | Input level at which FS1 changes to FS2                                                                                                                 | 6              | 16            | 26    | dBμ         |  |

| Mute attenuation                     | Mute-Att       | 60dBμV, pin 11 output                                                                                                                                   | 60             | 70            |       | dB          |  |

| FM receive characteristics;          | STEREO: fc = 8 | 0MHz, fm = 1kHz, $V_{IN}$ = 60dB $\mu$ V, L+R = 30% (22.5kHz),                                                                                          | Pilot = 10% (7 | 7.5kHzdev)    |       |             |  |

| Separation                           | SEP            | L-mod, pin 11 output / pin 12 output                                                                                                                    | 20             | 35            |       | dB          |  |

| Total harmonic distortion (Main)     | THD-ST         | Main-mod (for L+R input), pin 11 / pin 12 output,<br>IHF_BPF                                                                                            |                | 0.6           | 1.8   | %           |  |

| RDS characteristics                  |                |                                                                                                                                                         | U              |               |       |             |  |

| RDS_center frequency                 | fcen           | Adjustment accuracy of RDS_VCO DAC value.<br>(Adjustment accuracy of free_run frequency)                                                                | 56.5           | 57.0          | 57.5  | kHz         |  |

| -3dB bandwidth                       | BW-3dB         | Bandwidth of BPF to 57KHZ Center frequency. Set<br>Block4 register 06h of Bit3-2 (RDSBW) to "11"<br>() is not guarantee value. Just for Reference value | (3.0)          | 5.5           | (7.0) | kHz         |  |

| RDS Current drain                    | Irds           | RDS current value at RDS Enable/Disable                                                                                                                 |                | 2             | 4     | mA          |  |

|                                      | 1              |                                                                                                                                                         |                |               |       |             |  |

The output level is set to the VOL = 14 when the block 2, register 09h of control register map has the bit 3,2,1,0 = 0010 in other cases:

• The IF\_OSC frequency must be adjust to 140kHz with DAC of block 1, register 05h.

• The IF\_CENTER set bit value (block 2, register 03h) applies to same DAC value of IF\_OSC.

• The IF\_BW set bit value (block2, register 05h) applies to the setting of the value 65% of the IF\_OSC set bit value.

• The RDS\_OSC frequency must be adjust to 114kHz with DAC of block 4, register 07h.

• The RDS\_FLTDAC (block 4, register 03h) set bit value applies to the setting of value 95% of RDS\_OSC set bit value.

# Interface Block Allowable Operation Range at $Ta=-20 \ to \ +70^{\circ}C, \ V_{SS}=0V$

| Deremeter                             | Sumbol                                             | Symbol Conditions                                 |                    | Ratings |                 |      |  |

|---------------------------------------|----------------------------------------------------|---------------------------------------------------|--------------------|---------|-----------------|------|--|

| Parameter                             | Symbol                                             | Conditions                                        | min                | typ     | max             | unit |  |

| Supply voltage                        | V <sub>DD</sub>                                    |                                                   | 2.5                |         | 4.0             | V    |  |

| Digital block input                   | VIH                                                | High-level input voltage range                    | 0.7V <sub>DD</sub> |         | V <sub>DD</sub> | V    |  |

|                                       | VIL                                                | Low-level input voltage range                     | 0                  |         | 0.6             | V    |  |

| Digital block output                  | output I <sub>OL</sub> Output current at Low level |                                                   | 2.0                |         |                 | mA   |  |

|                                       | V <sub>OL</sub>                                    | Output voltage at Low level I <sub>OL</sub> = 2mA |                    |         | 0.6             | V    |  |

| Clock input operating                 | fclk                                               | (Pin 29) clock frequency for 3wire_bus            |                    |         | 0.7             | MHz  |  |

| frequency<br>External clock operating | fclk ext                                           | (Pin 31) clock frequency for external input       | 32k                |         | 14M             | Hz   |  |

| frequency                             | .ooxt                                              |                                                   | 02K                |         |                 |      |  |

Note: External clock input (pin 31) allows also input of the sine wave signal.

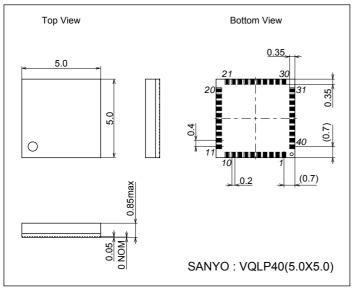

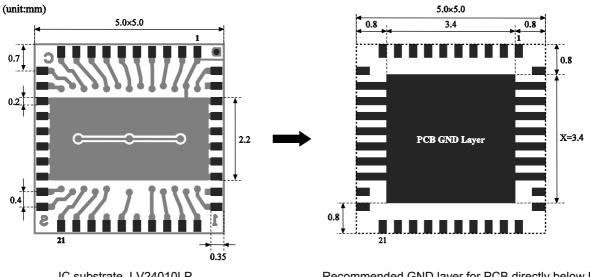

# Package Dimensions

unit : mm

3302A

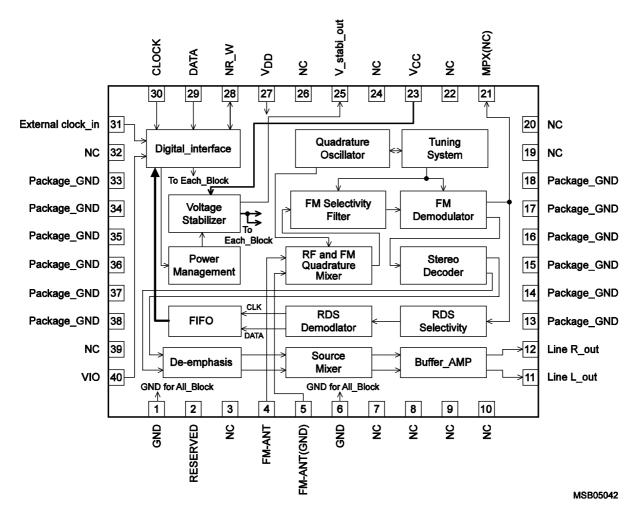

### **Block Diagram**

# **Pin Function**

| Pin No. | Pin name        | Description                                  | DC_bias               | Remark                      |

|---------|-----------------|----------------------------------------------|-----------------------|-----------------------------|

| 1       | GND             | GND (Analog and Digital GND)                 |                       |                             |

| 2       | NC              |                                              |                       | Do not connect.             |

| 3       | NC              |                                              |                       | Do not connect.             |

| 4       | FM-ANT1         | Antenna input                                |                       |                             |

| 5       | FM-ANT2         | Antenna GND                                  |                       | Connect to GND.             |

| 6       | GND             | GND (Analog and Digital GND)                 |                       |                             |

| 7       | NC              |                                              |                       | Do not connect.             |

| 8       | NC              |                                              |                       | Do not connect.             |

| 9       | NC              |                                              |                       | Do not connect.             |

| 10      | NC              |                                              |                       | Do not connect.             |

| 11      | LINE-OUT-L      | Radio Lch Line-output                        | 1.2V                  |                             |

| 12      | LINE-OUT-R      | Radio Rch Line-output                        | 1.2V                  |                             |

| 13      | Package-GND     | GND for Package-shied                        |                       |                             |

| 14      | Package-GND     | GND for Package-shied                        |                       |                             |

| 15      | Package-GND     | GND for Package-shied                        |                       |                             |

| 16      | Package-GND     | GND for Package-shied                        |                       |                             |

| 17      | Package-GND     | GND for Package-shied                        |                       |                             |

| 18      | Package-GND     | GND for Package-shied                        |                       |                             |

| 19      | NC              |                                              |                       | Do not connect.             |

| 20      | NC              |                                              |                       | Do not connect.             |

| 21      | MPX             | MPX-signal output                            | V <sub>CC</sub> -0.3V |                             |

| 22      | NC              |                                              |                       | Do not connect.             |

| 23      | V <sub>CC</sub> | Analog supply voltage                        |                       |                             |

| 24      | NC              |                                              |                       | Do not connect.             |

| 25      | Vstabi.         | Stabilizer voltage                           | 2.7V                  |                             |

| 26      | NC              |                                              |                       | Do not connect.             |

| 27      | V <sub>DD</sub> | Digital supply voltage                       |                       |                             |

| 28      | NR_W            | Digital interface Read/Write                 |                       |                             |

| 29      | DATA            | Digital interface DATA                       |                       |                             |

| 30      | CLOCK           | Digital interface Clock                      |                       |                             |

| 31      | CLK_IN          | Reference clock-source input for measurement |                       | Connect to GND if not used. |

| 32      | NC              |                                              |                       | Do not connect.             |

| 33      | Package-GND     | GND for Package-shied                        |                       |                             |

| 34      | Package-GND     | GND for Package-shied                        |                       |                             |

| 35      | Package-GND     | GND for Package-shied                        |                       |                             |

| 36      | Package-GND     | GND for Package-shied                        |                       |                             |

| 37      | Package-GND     | GND for Package-shied                        |                       |                             |

| 38      | Package-GND     | GND for Package-shied                        |                       |                             |

| 39      | NC              |                                              |                       | Do not connect.             |

| 40      | VI/O            | Digital interface supply voltage             |                       |                             |

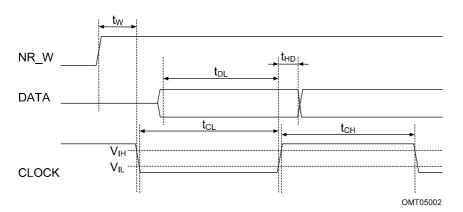

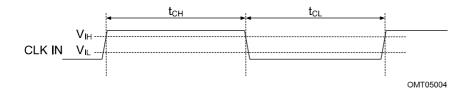

# Timing Diagram

Write timing

| Symbol          | Parameter                                 |     | Ratings |     |      |  |

|-----------------|-------------------------------------------|-----|---------|-----|------|--|

|                 |                                           |     | typ     | max | unit |  |

| tw              | Delay from command to data                | 750 |         |     | ns   |  |

| <sup>t</sup> DL | Delay from data stable to data latch time | 750 |         |     | ns   |  |

| <sup>t</sup> HD | Data Hold time                            | 750 |         |     | ns   |  |

| <sup>t</sup> CH | Clock High-level time                     | 750 |         |     | ns   |  |

| tCL             | Clock Low-level time                      | 750 |         |     | ns   |  |

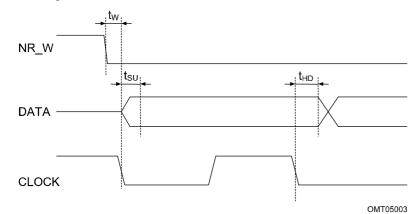

# Read timing

| Symbol          | Descenter                          |     | Ratings |     |      |  |

|-----------------|------------------------------------|-----|---------|-----|------|--|

|                 | Parameter                          | min | typ     | max | unit |  |

| tw              | Delay from command to 1st data bit | 350 |         |     | ns   |  |

| tsu             | Data Setup time                    |     |         | 350 | ns   |  |

| T <sub>HD</sub> | Data hold time                     |     |         | 350 | ns   |  |

External clock timing (Pin 31)

| Symbol          | Parameter             |    | Ratings |     |      |  |

|-----------------|-----------------------|----|---------|-----|------|--|

|                 |                       |    | typ     | max | unit |  |

| <sup>t</sup> CH | Clock High-level time | 35 |         |     | ns   |  |

| tCL             | Clock Low-level time  | 35 |         |     | ns   |  |

# Digital interface specification (Interface specification: reference)

(1) 3-wire bus (For communication line)

Access to the LV24010 is done through the 3-wire bus:

CLOCK Data strobe, input to the LV24010

NR\_W Command (Write or read data), input to the LV24010

DATA Bi-directional pin: input to the LV24010 when NR\_W is high, output from the LV24010 when NR\_W is low.

The LV24010 can be configured to generate interrupt through the DATA-line. When interrupt mode is selected, care should be taken that the DATA-line connection to the application micro-controller also supports interrupt.

When the required timing window for frequency measurements is not generated by the application micro-controller, an external clock must be connected to CLK\_IN pin of the LV24010

#### (2) Register map (For register map)

The LV24020 registers are divided in 2 blocks:

| Block 01h | Status and measurement |

|-----------|------------------------|

| Block 02h | Radio Control          |

| Block 04h | RDS control            |

To access a register in a block, the block must be first selected by writing the block number to the BLK\_SEL register. Block selection can be skipped for subsequent accesses to other registers in the same block.

The mapping is as follows:

| Block | Address | Register name | Access | Operation                                 |

|-------|---------|---------------|--------|-------------------------------------------|

| 01h   | 00h     | CHIP_ID       | R      | Chip identification                       |

|       | 01h     | BLK_SEL       | W      | Block Select                              |

|       | 02h     | MSRC_SEL      | W      | Measure source select                     |

|       | 03h     | FM_OSC        | W      | DAC control for FM-RF oscillator          |

|       | 04h     | SD_OSC        | W      | DAC control for stereo decoder oscillator |

|       | 05h     | IF_OSC        | W      | DAC control for IF oscillator             |

|       | 06h     | CNT_CTRL      | W      | Counter control                           |

|       | 07h     | NA            | -      |                                           |

|       | 08h     | IRQ_MSK       | W      | Interrupt mask                            |

|       | 09h     | FM_CAP        | W      | CAP bank control for RF-frequency         |

|       | 0Ah     | CNT_L         | R      | Counter value low byte                    |

|       | 0Bh     | CNT_H         | R      | Counter value high byte                   |

|       | 0Ch     | CTRL_STAT     | R      | Control status                            |

|       | 0Dh     | RADIO_STAT    | R      | Radio station status                      |

|       | 0Eh     | IRQ_ID        | R      | Interrupt identify                        |

|       | 0Fh     | IRQ_OUT       | W      | Set Interrupt on DATA-line                |

| 02h   | 01h     | BLK_SEL       | W      | Access register 01h of block 1            |

|       | 02h     | RADIO_CTRL1   | W      | Radio control 1                           |

|       | 03h     | IF_CENTER     | W      | IF Center Frequency                       |

|       | 04h     | NA            | W      |                                           |

|       | 05h     | IF_BW         | W      | IF Bandwidth                              |

|       | 06h     | RADIO_CTRL2   | W      | Radio Control 2                           |

|       | 07h     | RADIO_CTRL3   | W      | Radio control 3                           |

|       | 08h     | STEREO_CTRL   | W      | Stereo Control                            |

|       | 09h     | AUDIO_CTRL1   | W      | Audio Control 1                           |

|       | 0Ah     | AUDIO_CTRL2   | W      | Audio Control 1                           |

|       | 0Bh     | PW_SCTRL      | W      | Power and soft control                    |

| 04h   | 01h     | BLK_SEL       | W      | Access register 01h of block 1            |

|       | 03h     | RDS_FLTDAC    | W      | DAC control for RDS filter                |

|       | 04h     | RDAT_L        | R      | Demodulated RDS data - low byte           |

|       | 05h     | RDAT_H        | R      | Demodulated RDS data – high byte          |

|       | 06h     | RDS_CTRL      | W      | RDS control                               |

|       | 07h     | RDS_OSC       | W      | DAC control for RDS PLL oscillator        |

|       | 08h     | NA            | -      |                                           |

|       | 09h     | RDS INPS      | W      | RDS input setting                         |

Registers with blank colum are not defined and should not be accessed.

#### (3) Register description (For each register content)

### Block x, Register 01h - BLK\_SEL - Block Select register (Write Only)

| 7                                                   | 6                                                                                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------|---|---|---|---|---|---|--|--|

| BN[7:0]                                             |                                                                                             |   |   |   |   |   |   |  |  |

| bit 7-0:                                            | bit 7-0: BN[7:0]: 8-bit block number. For LV24010, the following numbers are valid:<br>01h. |   |   |   |   |   |   |  |  |

|                                                     | 01n.<br>02h.                                                                                |   |   |   |   |   |   |  |  |

| 04h.                                                |                                                                                             |   |   |   |   |   |   |  |  |

| Note: This register can be accessed from any block. |                                                                                             |   |   |   |   |   |   |  |  |

#### Block 1, Register 00h - CHIP\_ID - Chip identify register (Read Only)

| 7        | 6                                | 5                      | 4                   | 3    | 2 | 1 | 0 |

|----------|----------------------------------|------------------------|---------------------|------|---|---|---|

|          |                                  |                        | ID[                 | 7:0] |   |   |   |

| bit 7-0: | <b>ID[7:0]:</b> 8-b<br>0Bh for L | oit chip ID. The follo | wing ID's are defin | ed:  |   |   |   |

#### Block 1, Register 02h - MSRC\_SEL - Measurement Source Select Register (Write-only)

| 7               | 6                     | 5                     | 4                    | 3                   | 2      | 1      | 0      |

|-----------------|-----------------------|-----------------------|----------------------|---------------------|--------|--------|--------|

| MSR_O           | AFC_LVL               | AFC_SPD               | Reserved             | Reserved            | MSS_SD | MSS_FM | MSS_IF |

| bit 7:          | MSR_O: C              | utput measure sou     | rce to DATA-pin.     | •                   | •      | •      | •      |

|                 | 0 = Meas              | suring source not av  | ailable at DATA-pi   | n (normal operatior | ı).    |        |        |

|                 | 1 = Meas              | suring source availa  | ble at DATA-pin (te  | est mode).          |        |        |        |

| bit 6:          | AFC_LVL:              | AFC trigger level.    |                      |                     |        |        |        |

|                 | 0 = AFC               | is always active (tri | gger at 0dBμV).      |                     |        |        |        |

|                 | 1 = AFC               | is only active when   | field strength is ab | ove 20dBµV.         |        |        |        |

| bit 5:          | AFC_SPD:              | : AFC speed.          |                      |                     |        |        |        |

|                 | 0 = AFC               | adjusts with 3Hz sp   | eed.                 |                     |        |        |        |

|                 | 1 = AFC               | adjusts with 8kHz s   | peed (test mode).    |                     |        |        |        |

| bit 4:          | Reserved:             | Must be programm      | ned with 0.          |                     |        |        |        |

| bit 3:          | Reserved:             | Must be programm      | ned with 0.          |                     |        |        |        |

| bit 2:          | MSS_SD:               | Stereo decoder oso    | illator measuremer   | nt.                 |        |        |        |

|                 | 0 = Disat             | ole stereo decoder    | oscillator measuren  | nent.               |        |        |        |

|                 | 1 = Enab              | le stereo decoder o   | scillator measurem   | ient.               |        |        |        |

| bit 1:          | MSS_FM:               | FM RF oscillator m    | easurement.          |                     |        |        |        |

|                 | 0 = Disat             | ole FM RF oscillato   | r measurement.       |                     |        |        |        |

|                 | 1 = Enab              | le FM RF oscillator   | measurement.         |                     |        |        |        |

| bit 0:          | MSS_IF: IF            | - oscillator measure  | ement.               |                     |        |        |        |

|                 | 0 = Disat             | ole IF oscillator mea | surement.            |                     |        |        |        |

|                 | 1 = Enab              | le IF oscillator mea  | surement.            |                     |        |        |        |

| Note:           |                       |                       |                      |                     |        |        |        |

|                 | e measurement sour    | -                     |                      |                     |        |        |        |

| - The FM RF fre | equency is divided by | / 256 before it goes  | to the measuring of  | circuitry.          |        |        |        |

#### Block 1, Register 03h - FM\_OSC - FM RF Oscillator Register (Write-only)

| 7                 | 6                      | 5                   | 4                   | 3                     | 2 | 1 | 0 |

|-------------------|------------------------|---------------------|---------------------|-----------------------|---|---|---|

|                   |                        |                     | FMOS                | SC[7:0]               |   |   |   |

| bit 7-0:          | FMOSC[7:               | 0]: DAC value to co | ontrol the FM RF os | scillator (fine step) |   |   |   |

| Note:             |                        |                     |                     |                       |   |   |   |

| - Positive DAC co | ontrol (i.e. the frequ | ency increases with | the register's valu | e).                   |   |   |   |

| - See also FM_C   | AP register.           |                     |                     |                       |   |   |   |

| Block 1, Reg     | ister 04h - SD       | _OSC - Stere        | eo Decoder O          | scillator Regis   | ster (Write-onl | y) |   |

|------------------|----------------------|---------------------|-----------------------|-------------------|-----------------|----|---|

| 7                | 6                    | 5                   | 4                     | 3                 | 2               | 1  | 0 |

|                  |                      |                     | SDOS                  | 6C[7:0]           |                 |    |   |

| bit 7-0:         | SDOSC[7:             | 0]: DAC value to co | ontrol the stereo de  | coder oscillator. |                 |    |   |

| Note: Positive D | AC control (i.e. the | frequency increase  | s with the register's | value)            |                 |    |   |

|                  |                      |                     |                       |                   |                 |    |   |

# Block 1, Register 05h - IF\_OSC - IF Oscillator Register (Write-only)

| 7                 | 6                    | 5                  | 4                     | 3         | 2 | 1 | 0 |

|-------------------|----------------------|--------------------|-----------------------|-----------|---|---|---|

|                   |                      |                    | IFOS                  | C[7:0]    |   |   |   |

| bit 7-0:          | IFOSC[7:0]           | : DAC value to cor | trol the IF oscillato | r.        |   |   |   |

| Note: Positive DA | AC control (i.e. the | frequency increase | s with the register's | s value). |   |   |   |

### Block 1, Register 06h - CNT\_CTRL - Counters Control Register (Write-only)

| 7        | 6         | 5                    | 4                    | 3                     | 2      | 1       | 0       |

|----------|-----------|----------------------|----------------------|-----------------------|--------|---------|---------|

|          |           |                      |                      |                       |        |         |         |

| CNT1_CLR | CTAB2     | CTAB1                | CTAB0                | SWP_CNT_L             | CNT_EN | CNT_SEL | CNT_SET |

| bit 7:   | —         | R: Clear counter 1   | bit.                 |                       |        |         |         |

|          | 0 = Norm  |                      |                      |                       |        |         |         |

|          | 1 = Clear | r and keep counter   | 1 in reset mode.     |                       |        |         |         |

| bit 6-4: | CTAB[2:0] | : Tab select for co  | unter 2 measuring i  | nterval bits.         |        |         |         |

|          | Value     | Dec. Ste             | op value             |                       |        |         |         |

|          | 000b      | 0 St                 | op after 2 counts.   |                       |        |         |         |

|          | 001b      | 1 St                 | op after 8 counts .  |                       |        |         |         |

|          | 010b      | 2 St                 | op after 32 counts.  |                       |        |         |         |

|          | 011b      | 3 St                 | op after 128 counts  |                       |        |         |         |

|          | 100b      | 4 St                 | op after 512 counts  |                       |        |         |         |

|          | 101b      | 5 St                 | op after 2048 count  | S.                    |        |         |         |

|          | 110b      | 6 St                 | op after 8192 count  | S.                    |        |         |         |

|          | 111b      | 7 Ste                | op after 32768 cour  | nts.                  |        |         |         |

| bit 3:   | SWP_CNT   | L: Swap counter      | 1 and counter 2 bit  | (Active low).         |        |         |         |

|          | 0 = Clock | source 1 to count    | er 2, clock source 2 | to counter 1 (swap    | ping)  |         |         |

|          | 1 = Clock | source 1 to count    | er 1, clock source 2 | 2 to counter 2 (no sw | /ap)   |         |         |

| bit 2:   | CNT_EN:   | Enable the currentl  | y selected counter   | bit.                  |        |         |         |

|          | 0 = Disat | ole counter (stop co | ounting).            |                       |        |         |         |

|          | 1 = Enab  | le counter (countin  | g mode).             |                       |        |         |         |

| bit 1:   | CNT_SEL:  | counter select bit.  |                      |                       |        |         |         |

|          | 0 = Selec | ct counter 1 for mea | asurement.           |                       |        |         |         |

|          | 1 = Selec | ct counter 2 for mea | asurement.           |                       |        |         |         |

| bit 0:   | CNT_SET:  | Set counters bit.    |                      |                       |        |         |         |

|          | 0 = Norm  | nal mode.            |                      |                       |        |         |         |

|          | 1 = Set b | oth counter 1 and    | counter 2 to FFFFh   | and keep them set.    |        |         |         |

| 7        | 6          | 5                     | 4                   | 3                     | 2        | 1     | 0       |

|----------|------------|-----------------------|---------------------|-----------------------|----------|-------|---------|

| Reserved | IM_MS      | Reserved              | Reserved            | IRQ_LVL               | IM_AFC   | IM_FS | IM_CNT2 |

| bit 7:   | Reserved:  | Must be programm      | ned with 0.         | -                     |          |       |         |

| bit 6:   | IM_MS: Mo  | ono/Stereo interrup   | t mask bit.         |                       |          |       |         |

|          | 0 = Disat  | ole mono/stereo ch    | ange interrupt.     |                       |          |       |         |

|          | 1 = Enab   | le mono/stereo cha    | ange interrupt.     |                       |          |       |         |

| bit 5:   | Reserved:  | Must be programm      | ned with 0.         |                       |          |       |         |

| bit 4:   | Reserved:  | Must be programr      | ned with 0.         |                       |          |       |         |

| bit 3:   | IRQ_LVL:   | Interrupt level sele  | ct bit.             |                       |          |       |         |

|          | 0 = Drive  | DATA-line from lo     | w to high when inte | errupt occurs (active | e high). |       |         |

|          | 1 = Drive  | DATA-line from hi     | gh to low when inte | errupt occurs (active | e low).  |       |         |

| bit 2:   | IM_AFC: A  | FC out of range in    | terrupt mask bit.   |                       |          |       |         |

|          | 0 = Disat  | ole AFC out of rang   | e interrupt.        |                       |          |       |         |

|          | 1 = Enab   | le AFC out of range   | e interrupt.        |                       |          |       |         |

| bit 1:   | IM_FS: Fie | eld strength change   | interrupt mask bit. |                       |          |       |         |

|          | 0 = Disat  | ole field strength ch | ange interrupt.     |                       |          |       |         |

|          | 1 = Enab   | le field strength ch  | ange interrupt.     |                       |          |       |         |

| bit 0:   | IM_CNT2:   | Counter 2 counting    | g done interrupt ma | sk bit.               |          |       |         |

|          | 0 = Disat  | ole counter 2 count   | ing done interrupt. |                       |          |       |         |

|          | 1 = Enab   | le counter 2 counti   | ng done interrupt.  |                       |          |       |         |

#### Block 1, Register 09h - FM\_CAP - FM RF Capacitor Bank Register (Write-only)

| 7                   | 6                    | 5                  | 4                    | 3                   | 2         | 1 | 0 |

|---------------------|----------------------|--------------------|----------------------|---------------------|-----------|---|---|

|                     |                      |                    | FMCA                 | NP[7:0]             |           |   |   |

| bit 7-0:            | FMCAP[7:             | 0]: CAP bank value | to control the FM    | RF frequency (coars | se steps) |   |   |

| Note:               |                      |                    |                      |                     |           |   |   |

| - 71/2 bit CAP valu | ie (Bit[7:6]: Combin | ation 10b and 01b  | results in the same  | CAP-range).         |           |   |   |

| - Negative contro   | I: de RF frequency   | decreases when in  | creasing the registe | er's value.         |           |   |   |

| - See also FM_O     | SC register.         |                    |                      |                     |           |   |   |

#### Block 1, Register 0Ah - CNT\_L - Counter Value Low Register (Read-only)

| 7        | 6            | 5                    | 7 6 5 4 3 2 1 0       |        |  |  |  |  |  |  |  |  |  |

|----------|--------------|----------------------|-----------------------|--------|--|--|--|--|--|--|--|--|--|

|          | CNT_LSB[7:0] |                      |                       |        |  |  |  |  |  |  |  |  |  |

| bit 7-0: | CNT_LSB[     | 7:0]: Lower 8-bit va | alue of the 16 bit co | ounter |  |  |  |  |  |  |  |  |  |

#### Block 1, Register 0Bh - CNT\_H - Counter Value High Register (Read-only)

| <i>,</i> 0   |         | -                    | 5                     | 5 1    |   |   |   |  |  |

|--------------|---------|----------------------|-----------------------|--------|---|---|---|--|--|

| 7            | 6       | 5                    | 4                     | 3      | 2 | 1 | 0 |  |  |

| CNT_MSB[7:0] |         |                      |                       |        |   |   |   |  |  |

| bit 7-0:     | CNT_MSB | [7:0]: Upper 8-bit v | alue of the 16 bit co | ounter |   |   |   |  |  |

#### Block 1. Register 0Ch - CTRL STAT - Control Status Register (Read-only)

| 7        | 6                                        | 5                     | 4                     | 3                    | 2        | 1       | 0       |

|----------|------------------------------------------|-----------------------|-----------------------|----------------------|----------|---------|---------|

| REV3     | REV2                                     | REV1                  | REV0                  | Reserved             | Reserved | COV_FLG | AFC_FLG |

| bit 7-4: | REV[3:0]:                                | should be read as (   | )Dh.                  |                      |          |         |         |

| bit 3-1: | Reserved[                                | 1:0]: should be rea   | d as all 1            |                      |          |         |         |

| bit 1:   | COV_FLG:                                 | : counter overflow f  | lag.                  |                      |          |         |         |

|          | 0 = No ov                                | verflow of the intern | al counter.           |                      |          |         |         |

|          | 1 = The I                                | ast counting loop ca  | auses overflow of the | he internal counter. |          |         |         |

| bit 0:   | AFC_FLG:                                 | AFC out of range l    | oit                   |                      |          |         |         |

|          | 0 = AFC                                  | is within control ran | ge.                   |                      |          |         |         |

|          | 1 = AFC                                  | is out of control ran | ge.                   |                      |          |         |         |

| Note:    |                                          |                       |                       |                      |          |         |         |

| 0        | gister will clear AFC<br>ear when CLR_CN | ,                     |                       |                      |          |         |         |

| $0 = Mono.$ $1 = Stereo.$ bit 6-0: $RSS_FS[6:0]: Radio station field strength bits.$ $1111111b = Field strength less then 10dB\muV.$ $0111111b = Field strength between 10 to 20dB\muV.$ $0011111b = Field strength between 20 to 30dB\muV.$ $0001111b = Field strength between 30 to 40dB\muV.$ $0000111b = Field strength between 40 to 50dB\muV.$ $0000011b = Field strength between 50 to 60dB\muV.$ $0000001b = Field strength between 60 to 70dB\muV.$ $0000000b = Field strength above 70dB\muV.$                              | 7                  | 6                     | 5                     | 4                      | 3    | 2 | 1 | 0 |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------|-----------------------|------------------------|------|---|---|---|--|--|--|--|--|--|

| $0 = Mono.$ $1 = Stereo.$ bit 6-0: $RSS_FS[6:0]: Radio station field strength bits.$ $1111111b = Field strength less then 10dB\muV.$ $0111111b = Field strength between 10 to 20dB\muV.$ $0011111b = Field strength between 20 to 30dB\muV.$ $0001111b = Field strength between 30 to 40dB\muV.$ $0000111b = Field strength between 40 to 50dB\muV.$ $0000011b = Field strength between 50 to 60dB\muV.$ $0000001b = Field strength between 60 to 70dB\muV.$ $0000000b = Field strength above 70dB\muV.$                              | RSS_MS             |                       | RSS_FS                |                        |      |   |   |   |  |  |  |  |  |  |

| 1 = Stereo.         bit 6-0:       RSS_FS[6:0]: Radio station field strength bits.         1111111b = Field strength less then 10dBµV.         0111111b = Field strength between 10 to 20dBµV.         0011111b = Field strength between 20 to 30dBµV.         0001111b = Field strength between 30 to 40dBµV.         0000111b = Field strength between 40 to 50dBµV.         0000011b = Field strength between 50 to 60dBµV.         000001b = Field strength between 60 to 70dBµV.         0000000b = Field strength above 70dBµV. | bit 7:             | RSS_MS: F             | Radio station mono    | /stereo state bit.     |      |   |   |   |  |  |  |  |  |  |

| bit 6-0:<br><b>RSS_FS[6:0]:</b> Radio station field strength bits.<br>1111111b = Field strength less then $10dB\mu V$ .<br>0111111b = Field strength between 10 to $20dB\mu V$ .<br>0011111b = Field strength between 20 to $30dB\mu V$ .<br>0001111b = Field strength between 30 to $40dB\mu V$ .<br>0000111b = Field strength between 40 to $50dB\mu V$ .<br>0000011b = Field strength between 50 to $60dB\mu V$ .<br>0000001b = Field strength between 60 to $70dB\mu V$ .<br>0000000b = Field strength above $70dB\mu V$ .        |                    | 0 = Mono              | ).                    |                        |      |   |   |   |  |  |  |  |  |  |

| 111111b = Field strength less then $10dB_{\mu}V$ .<br>0111111b = Field strength between 10 to $20dB_{\mu}V$ .<br>0011111b = Field strength between 20 to $30dB_{\mu}V$ .<br>0001111b = Field strength between 30 to $40dB_{\mu}V$ .<br>0000111b = Field strength between 40 to $50dB_{\mu}V$ .<br>0000011b = Field strength between 50 to $60dB_{\mu}V$ .<br>000001b = Field strength between 60 to $70dB_{\mu}V$ .                                                                                                                   |                    | 1 = Stere             | 0.                    |                        |      |   |   |   |  |  |  |  |  |  |

| 0111111b = Field strength between 10 to 20dBμV.<br>0011111b = Field strength between 20 to 30dBμV.<br>0001111b = Field strength between 30 to 40dBμV.<br>0000111b = Field strength between 40 to 50dBμV.<br>0000011b = Field strength between 50 to 60dBμV.<br>0000001b = Field strength between 60 to 70dBμV.<br>0000000b = Field strength above 70dBμV.                                                                                                                                                                             | bit 6-0:           | RSS_FS[6:             | :0]: Radio station fi | eld strength bits.     |      |   |   |   |  |  |  |  |  |  |

| 0011111b = Field strength between 20 to $30dB\mu V$ .<br>0001111b = Field strength between 30 to $40dB\mu V$ .<br>0000111b = Field strength between 40 to $50dB\mu V$ .<br>0000011b = Field strength between 50 to $60dB\mu V$ .<br>0000001b = Field strength between 60 to $70dB\mu V$ .<br>0000000b = Field strength above $70dB\mu V$ .                                                                                                                                                                                            |                    | 1111111               | o = Field strength le | ess then $10dB\mu V$ . |      |   |   |   |  |  |  |  |  |  |

| 0001111b = Field strength between 30 to 40dB $\mu$ V.<br>0000111b = Field strength between 40 to 50dB $\mu$ V.<br>0000011b = Field strength between 50 to 60dB $\mu$ V.<br>0000001b = Field strength between 60 to 70dB $\mu$ V.<br>0000000b = Field strength above 70dB $\mu$ V.                                                                                                                                                                                                                                                     |                    | 0111111               | o = Field strength b  | etween 10 to 20dB      | βμV. |   |   |   |  |  |  |  |  |  |

| 0000111b = Field strength between 40 to 50dB $\mu$ V.<br>0000011b = Field strength between 50 to 60dB $\mu$ V.<br>0000001b = Field strength between 60 to 70dB $\mu$ V.<br>0000000b = Field strength above 70dB $\mu$ V.                                                                                                                                                                                                                                                                                                              |                    | 0011111               | o = Field strength b  | etween 20 to 30dB      | βμV. |   |   |   |  |  |  |  |  |  |

| 0000011b = Field strength between 50 to $60dB\mu V$ .<br>0000001b = Field strength between 60 to $70dB\mu V$ .<br>0000000b = Field strength above $70dB\mu V$ .                                                                                                                                                                                                                                                                                                                                                                       |                    | 00011118              | o = Field strength b  | etween 30 to 40dB      | βμV. |   |   |   |  |  |  |  |  |  |

| 0000001b = Field strength between 60 to 70dB $\mu$ V.<br>0000000b = Field strength above 70dB $\mu$ V.                                                                                                                                                                                                                                                                                                                                                                                                                                |                    | 00001111              | o = Field strength b  | etween 40 to 50dB      | βμV. |   |   |   |  |  |  |  |  |  |

| 0000000b = Field strength above 70dBµV.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                    | 00000118              | o = Field strength b  | etween 50 to 60dB      | βμV. |   |   |   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                    | 0000001               | o = Field strength b  | etween 60 to 70dB      | βμV. |   |   |   |  |  |  |  |  |  |

| Note: Reading this register will clear field strength and mono/stereo interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                    | 0000000               | o = Field strength a  | bove 70dBμV.           |      |   |   |   |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Note: Reading this | s register will clear | field strength and    | mono/stereo interro    | upt. |   |   |   |  |  |  |  |  |  |

#### Block 1, Register 0Eh - IRQ\_ID - Interrupt Identify Register (Read-only)

| 7        | 6                                                                                                                                                            | 5                                                                        | 4                     | 3                                                    | 2        | 1        | 0        |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------|------------------------------------------------------|----------|----------|----------|--|--|--|

| Reserved | II_RDS                                                                                                                                                       | II_CNT2                                                                  | Reserved              | II_AFC                                               | Reserved | Reserved | II_FS_MS |  |  |  |

| bit 7:   | Reserved: should be read as 1.                                                                                                                               |                                                                          |                       |                                                      |          |          |          |  |  |  |

| bit 6:   | <ul> <li>II_RDS: RDS data available interrupt.</li> <li>0 = No counting 2 counting done interrupt.</li> <li>1 = Measuring with counter 2 is done.</li> </ul> |                                                                          |                       |                                                      |          |          |          |  |  |  |

| bit 5:   | 0 = No co                                                                                                                                                    | Counter 2 counting of<br>counting 2 counting of<br>suring with counter 2 | done interrupt.       |                                                      |          |          |          |  |  |  |

| bit 4:   | Reserved:                                                                                                                                                    | should be read as                                                        | 0.                    |                                                      |          |          |          |  |  |  |

| bit 3:   | 0 = No A                                                                                                                                                     | FC out of range inte<br>FC interrupt.<br>fails to hold the RF            | ·                     | <b>.</b>                                             |          |          |          |  |  |  |

| bit 2:   | Reserved:                                                                                                                                                    | should be read as                                                        | 0.                    |                                                      |          |          |          |  |  |  |

| bit 1:   | Reserved:                                                                                                                                                    | should be read as                                                        | 0.                    |                                                      |          |          |          |  |  |  |

| bit 0:   | 0 = No ch                                                                                                                                                    | •                                                                        | field strength or the | upt bit.<br>e mono/stereo mode<br>ono/stereo mode ha |          |          |          |  |  |  |

# Block 1, Register 0Fh - IRQ\_OUT - Set Interrupt Out Register (Write Only)

| 7        | 7 6 5 4 3 2 1 0 |                     |                      |                         |                      |                |  |  |  |  |  |

|----------|-----------------|---------------------|----------------------|-------------------------|----------------------|----------------|--|--|--|--|--|

|          |                 |                     | IRQO_\               | VAL[7:0]                |                      |                |  |  |  |  |  |

| bit 7-0: | IRQO_VAL        | [7:0]: Write any va | lue to this register | will select the interru | upt as output on the | e DATA-line of |  |  |  |  |  |

|          |                 | the LV24010         | ) (the DATA-line ca  | n then be used as i     | nterrupt pin)        |                |  |  |  |  |  |

#### Block 2, Register 02h - RADIO\_CTRL1 - Radio Control 1 Register (Write-only)

| 5100K 2, 110g |           |                       |                     |         | <b>,</b> |          |          |

|---------------|-----------|-----------------------|---------------------|---------|----------|----------|----------|

| 7             | 6         | 5                     | 4                   | 3       | 2        | 1        | 0        |

| EN_MEAS       | EN_AFC    | Reserved              | Reserved            | DIR_AFC | RST_AFC  | Reserved | Reserved |

| bit 7:        | EN_MEAS   | : Enable measurem     | nent bit.           |         |          |          |          |

|               | 0 = Norm  | al mode.              |                     |         |          |          |          |

|               | 1 = Meas  | surement mode.        |                     |         |          |          |          |

| bit 6:        | EN_AFC:   | Enable AFC bit.       |                     |         |          |          |          |

|               | 0 = Disat | ble AFC.              |                     |         |          |          |          |

|               | 1 = Enab  | le AFC.               |                     |         |          |          |          |

| bit 5:        | Reserved: | should be written w   | vith 0.             |         |          |          |          |

| bit 4:        | Reserved: | should be written w   | vith 1.             |         |          |          |          |

| bit 3:        | DIR_AFC:  | AFC direction bit .   |                     |         |          |          |          |

|               | 0 = AFC   | normal direction.     |                     |         |          |          |          |

|               | 1 = AFC   | reverse direction (fo | or test purpose).   |         |          |          |          |

| bit 2:        | RST_AFC:  | Reset AFC bit.        |                     |         |          |          |          |

|               | 0 = Norm  | al operation.         |                     |         |          |          |          |

|               | 1 = Rese  | t AFC to the middle   | of the control rang | e.      |          |          |          |

| bit 1:        | Reserved: | should be written w   | vith 1.             |         |          |          |          |

| bit 0:        | Reserved: | should be written w   | vith 1.             |         |          |          |          |

#### Block 2, Register 03h - IF\_CENTER - IF Center Frequency Register (Write-only)

| 7        | 7 6 5 4 3 2 1 0 |                      |                     |         |  |  |  |  |  |  |

|----------|-----------------|----------------------|---------------------|---------|--|--|--|--|--|--|

|          |                 |                      | IFCOS               | SC[7:0] |  |  |  |  |  |  |

| bit 7-0: | IFCENT[7:       | 0]: Value for center | ing the IF frequenc | ÿ.      |  |  |  |  |  |  |

#### Block 2, Register 05h - IF\_BW - IF Bandwidth Register (Write-only)

| 7        | 6 5 4 3 2 1 0 |                    |        |  |  |  |  |  |  |  |  |

|----------|---------------|--------------------|--------|--|--|--|--|--|--|--|--|

|          | IFBW[7:0]     |                    |        |  |  |  |  |  |  |  |  |

| Bit 7-0: | IFBW[7:0]:    | Value for IF bandy | vidth. |  |  |  |  |  |  |  |  |

#### Block 2, Register 06h - RADIO\_CTRL2 - Radio Control 2 Register (Write-only)

| 7                 | 6                       | 5                                | 4                              | 3        | 2        | 1     | 0          |

|-------------------|-------------------------|----------------------------------|--------------------------------|----------|----------|-------|------------|

| VREF2             | VREF                    | STABI_BP                         | IF_PM_L                        | Reserved | Reserved | AGCSP | AM_ANT_BSW |

| bit 7:            | VREF2: V <sub>F</sub>   | REF2 control bit.                |                                |          |          |       |            |

|                   | 0 = V <sub>REF</sub>    | = <sub>2</sub> is ON.            |                                |          |          |       |            |

|                   | 1 = V <sub>REF</sub>    | = <sub>2</sub> is OFF.           |                                |          |          |       |            |

| bit 6:            | VREF: VRI               | EF control bit.                  |                                |          |          |       |            |

|                   | 0 = V <sub>REF</sub>    | = is ON.                         |                                |          |          |       |            |

|                   | 1 = V <sub>REF</sub>    | = is OFF.                        |                                |          |          |       |            |

| bit 5:            | STABI_BP                | : Stabi Bypass bit.              |                                |          |          |       |            |

|                   | 0 = Interr              | nal voltage is V <sub>stab</sub> | <sub>i</sub> (normal operation | ı).      |          |       |            |

|                   | 1 = Interr              | nal voltage is V <sub>CC</sub>   | (stabi bypassed).              |          |          |       |            |

| bit 4:            | IF_PM_L: I              | IF PLL mute bit.                 |                                |          |          |       |            |

|                   | 0 = IF PL               | L mute on (presetti              | ing IF mode).                  |          |          |       |            |

|                   | 1 = IF PL               | L mute off (normal               | operation mode).               |          |          |       |            |

| bit 3:            | Reserved:               | should be written                | with 0.                        |          |          |       |            |

| bit 2:            | Reserved:               | should be written                | with 0.                        |          |          |       |            |

| bit 1:            | AGCSP: A                | GC speed control b               | pit.                           |          |          |       |            |

|                   | 0 = Norm                | al speed.                        |                                |          |          |       |            |

|                   | 1 = High                | speed.                           |                                |          |          |       |            |

| Note: Turn on the | nis bit will speed up t | the field strength m             | easurement (fast ti            | uning).  |          |       |            |

| bit 0:            | Pasarvadu               | should be written                | with 0                         |          |          |       |            |

#### Block 2, Register 07h - RADIO\_CTRL3 - Radio Control 3 Register (Write-only)

| 210011 2, 1 10g. |           | 2/0_0//20                                                        |         | er er legieler | (mile emy) |          |          |

|------------------|-----------|------------------------------------------------------------------|---------|----------------|------------|----------|----------|

| 7                | 6         | 5                                                                | 4       | 3              | 2          | 1        | 0        |

| AGC_SLVL         | VOLSH     | Reserved                                                         | AMUTE_L | SE_FM          | Reserved   | Reserved | Reserved |

| bit 7:           |           | L: AGC set level bit<br>ist be set to 1 for no                   |         | de.            |            |          |          |

| bit 6:           | 0 = Norm  | olume level shift bit<br>nal volume level.<br>ase volume of 12dE | -       |                |            |          |          |

| bit 5:           | Reserved: | should be written w                                              | vith 0. |                |            |          |          |

| bit 4:           | 0 = Audio | Audio mute bit.<br>o muted.<br>o not muted.                      |         |                |            |          |          |

| bit 3:           | 0 = Disat | M radio select bit.<br>ble FM radio.<br>le FM radio.             |         |                |            |          |          |

| bit 2:           | Reserved: | should be written w                                              | vith 0. |                |            |          |          |

| bit 1:           | Reserved: | should be written w                                              | vith 0. |                |            |          |          |

| bit 0:           | Reserved: | should be written w                                              | vith 0. |                |            |          |          |

#### Block 2, Register 08h - STEREO\_CTRL - Stereo Control Register (Write-only)

| 7        | 6               | 5                    | 4                   | 3         | 2        | 1     | 0    |

|----------|-----------------|----------------------|---------------------|-----------|----------|-------|------|

| FRCST    |                 | FMCS[2:0]            | •                   | AUTOSSR   | DELTA_TN | SD_PM | ST_M |

| bit 7:   | FRCST: Fo       | orce stereo bit.     |                     |           |          |       |      |

|          | 0 = Norm        | al mode.             |                     |           |          |       |      |

|          | 1 = Force       | e stereo mode for te | est.                |           |          |       |      |

| bit 6-4: | FMCS[2:0]       | : FM channel sepa    | ration bits.        |           |          |       |      |

|          | 07 = FI         | M channel separati   | on level.           |           |          |       |      |

| bit 3:   | AUTOSSR         | : Auto stereo slew   | rate enable bit.    |           |          |       |      |

|          | 0 = Disat       | ole stereo auto slev | v rate.             |           |          |       |      |

|          | 1 = Enab        | le stereo auto slew  | rate.               |           |          |       |      |

| bit 2:   | DELTA_TM        | N: Delta tune bit.   |                     |           |          |       |      |

|          | 0 = Decre       | ease delta tune.     |                     |           |          |       |      |

|          | 1 = Norm        | al delta tune.       |                     |           |          |       |      |

| bit 1:   | SD_PM: Si       | tereo decoder PLL    | mute bit.           |           |          |       |      |

|          | 0 = Stere       | o decoder PLL not    | muted (normal ope   | eration). |          |       |      |

|          | 1 = Stere       | o decoder PLL is n   | nuted (presetting m | iode).    |          |       |      |

| bit 0:   | <b>ST_M:</b> FM | stereo/mono mode     | e bit.              |           |          |       |      |

|          | 0 = Stere       | o mode.              |                     |           |          |       |      |

|          | 1 = Mono        | mode.                |                     |           |          |       |      |

# Block 2, Register 09h - AUDIO\_CTRL1 - Audio Control 1 Register (Write-only)

| 7                                           | 6                  | 5                                                                                 | 4        | 3 2 1 0 |     |      |  |  |  |

|---------------------------------------------|--------------------|-----------------------------------------------------------------------------------|----------|---------|-----|------|--|--|--|

| Reserved                                    | Reserved           | Reserved                                                                          | Reserved |         | VOL | _LVL |  |  |  |

| bit 7-4: Reserved: should be written with 0 |                    |                                                                                   |          |         |     |      |  |  |  |

| bit 3-0:                                    | 1111b =<br>0000b = | volume level bits<br>Minimum volume le<br>Maximum volume le<br>is about 3dB volum | evel.    |         |     |      |  |  |  |

#### Block 2, Register 0Ah - AUDIO\_CTRL2 - Audio Control 2 Register (Write-only)

| , 3                   |                                                   |                 |          |          |          |          |          |  |  |  |  |

|-----------------------|---------------------------------------------------|-----------------|----------|----------|----------|----------|----------|--|--|--|--|

| 7                     | 6                                                 | 5               | 4        | 3        | 2        | 1        | 0        |  |  |  |  |

| Reserved              | Reserved                                          | DEEMP           | Reserved | Reserved | Reserved | Reserved | Reserved |  |  |  |  |

| bit 7-6:              | 7-6: Reserved: should be written with 11b.        |                 |          |          |          |          |          |  |  |  |  |

| bit 5:                | DEEMP: D                                          | e-emphasis bit. |          |          |          |          |          |  |  |  |  |

|                       | 0 = De-e                                          | mphasis 50µs.   |          |          |          |          |          |  |  |  |  |

| 1 = De-emphasis 75μs. |                                                   |                 |          |          |          |          |          |  |  |  |  |

| bit 4-0:              | bit 4-0: Reserved: should be written with 00000b. |                 |          |          |          |          |          |  |  |  |  |

#### Block 2, Register 0Bh - PW\_SCTRL - Power and Soft Control Register (Write-only)

| 7           | 6                   | 5                     | 4                | 3       | 2 | 1        | 0      |

|-------------|---------------------|-----------------------|------------------|---------|---|----------|--------|

|             | SS_CTRL             |                       |                  | SM_CTRL |   | Reserved | PW_RAD |

| bit 7-5:    | SS_CTRL:            | Soft stereo control   | bits (8 levels). |         |   |          |        |

|             | 000b = N            | 1inimal soft stereo ( | off).            |         |   |          |        |

|             | 111b = N            | laximal soft stereo   | level.           |         |   |          |        |

| bit 4-2:    | SM_CTRL:            | Soft audio mute bi    | ts (8 levels).   |         |   |          |        |

|             | 000b = N            | linimal audio mute    | (off).           |         |   |          |        |

|             | 111b = N            | laximal soft audio r  | nute level.      |         |   |          |        |

| bit 1:      | Reserved:           | should be written w   | ith 0.           |         |   |          |        |

| bit 0:      | PW_RAD:             | Radio circuitry pow   | er bit.          |         |   |          |        |

|             | 0 = Radio           | circuitry is switche  | d OFF.           |         |   |          |        |

|             | 1 = Switcl          | h radio circuitry ON  |                  |         |   |          |        |

| Note: PW_RA | D is 0 at power up. |                       |                  |         |   |          |        |

#### Block 4, Register 03h - RDS\_FLTDAC - RDS Filter DAC Register (Write-only)

| 7 6 5 4 3 2 1 0   |                                                  |                  |                   |               |  |  |  |  |  |  |

|-------------------|--------------------------------------------------|------------------|-------------------|---------------|--|--|--|--|--|--|

| RFLTDAC[7:0]      |                                                  |                  |                   |               |  |  |  |  |  |  |

| bit 7-0:          | bit 7-0: RFLTDAC[7:0]: DAC value for RDS filter. |                  |                   |               |  |  |  |  |  |  |

| Note: This regist | er should be progra                              | mmed with 95% of | the value of RDS_ | OSC register. |  |  |  |  |  |  |

#### Block 4, Register 04h - RDAT\_L - RDS Data Low Register (Read-only)