# FAN7033MP

# **2W Stereo Power Amplifier with Fixed Gain**

#### **Features**

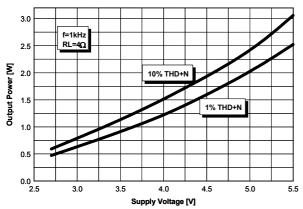

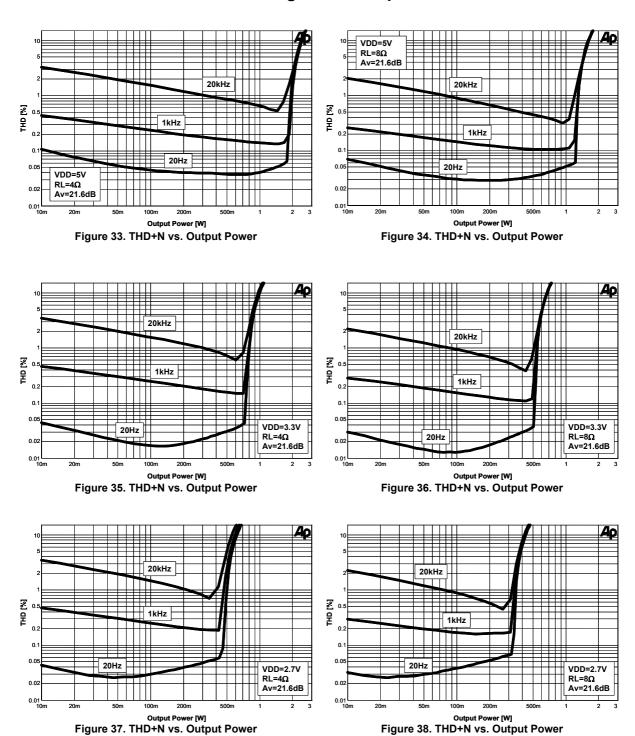

- 1.9WRMS and 2.45WRMS Power Per Each Channel Into  $4\Omega$  Load With Less Than 1% and 10% THD+N, Respectively

- Internally Fixed Gain: 21.6dB(Av=12)

Low Quiescent Current: Typical 5.5mA@5V

- Low Shutdown Current : Typical  $0.04\mu A@5V$

- Fully Differential Input, Which Immunes the Common Mode Noise

- · Active Low Shutdown Logic

- Guaranteed Stability Under No Load Condition

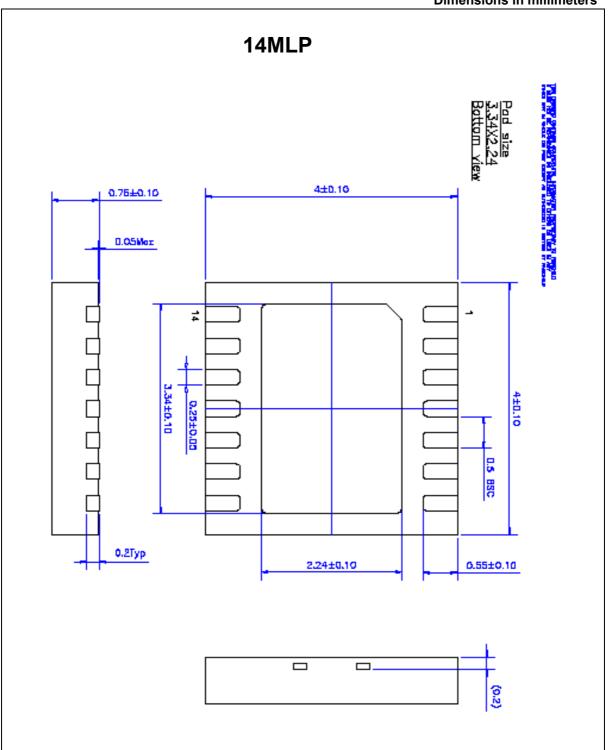

- Very Small Volume and Thermally Enhanced Surface-Mount 14MLP Package(4mm\*4mm)

### **Typical Applications**

- · Cellular Phones

- · Notebook Computer

- Desktop Computer

### **Description**

The FAN7033MP is a dual fully differential power amplifier in a thermally enhanced 14-pin MLP package. When delivering 1.9W of continuous RMS power into  $4\Omega$  speaker at 5V supply, the FAN7033MP has less than 1% of THD+N over the entire audible frequency range, 20Hz to 20kHz. To save power consumption in the portable applications, the FAN7033MP provides shutdown function. Setting the shutdown pin to ground level, the FAN7033MP falls into shutdown mode and consumes less than  $4\mu A$  over all supply voltage range, 2.7V to 5.5V. Additional components such as resistors for gain setting and bootstrap capacitors are not needed, making the FAN7033MP well suited for portable sound systems and other hand-held sound equipments. Target applications include the cellular phones, notebook, desktop computers, etc.

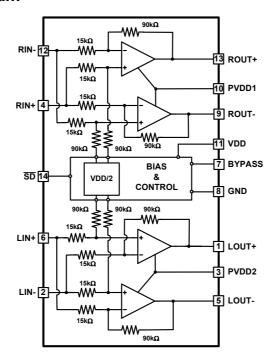

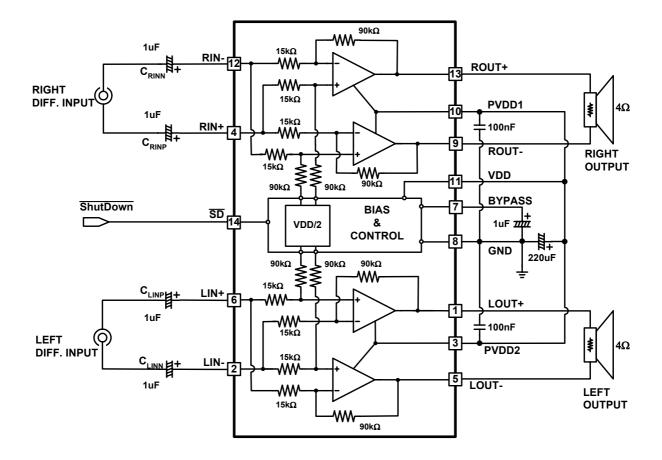

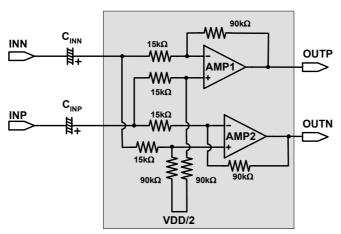

## **Internal Block Diagram**

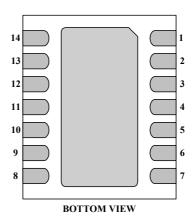

# **Pin Assignments**

# **Pin Descriptions**

| Pin No | Symbol | I/O | Decription                                                       |  |

|--------|--------|-----|------------------------------------------------------------------|--|

| 1      | LOUT+  | 0   | Left Channel (+) Output                                          |  |

| 2      | LIN-   | I   | Left Channel (-) Input                                           |  |

| 3**    | PVDD2  | I   | Left Channel Power Supply Voltage                                |  |

| 4      | RIN+   | I   | Right Channel (+) Input                                          |  |

| 5      | LOUT-  | 0   | Left Channel (-) Output                                          |  |

| 6      | LIN+   | I   | Left Channel (+) Input                                           |  |

| 7      | BYPASS | 0   | Bypass Capacitor Connect                                         |  |

| 8*     | GND    | -   | Ground                                                           |  |

| 9      | ROUT-  | 0   | Right Channel (-) Output                                         |  |

| 10**   | PVDD1  | I   | Right Channel Power Supply Voltage                               |  |

| 11**   | VDD    | I   | Power Supply Voltage                                             |  |

| 12     | RIN-   | I   | Right Channel (-) Input                                          |  |

| 13     | ROUT+  | 0   | Right Channel (+) Output                                         |  |

| 14     | SD     | I   | Shutdown Logic Low SD=VDD: Device Enable SD=GND: Device Shutdown |  |

<sup>\*</sup> Pin8(GND) and Exposed PAD are internally tied together.

\*\*For the best performance, VDD, PVDD1 and PVDD2 must be the same voltage level(strongly recommend).

# **Absolute Maximum Ratings**

| Parameter                     | Symbol            | Value                | Unit | Remark       |

|-------------------------------|-------------------|----------------------|------|--------------|

| Maximum Supply Voltage        | VDDmax            | 6.0V                 | V    |              |

| Power Dissipation             | PD                | Internally Limited W |      |              |

| Operating Temperature         | Topg              | -40 ~ +85            | °C   |              |

| Storage Temperature           | TSTG              | -65 ~ +150           | °C   |              |

| Junction Temperature          | T <sub>Jmax</sub> | 150                  | °C   |              |

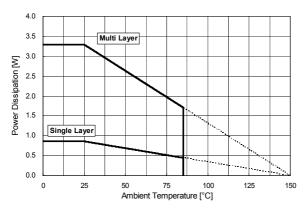

| Thermal Resistance            | Rthja*            | 38                   | °C/W | Multi-Layer  |

| (Junction to Ambient)         | Txiija            | 145                  | C/VV | Single-Layer |

| ESD Rating (Human Body Model) |                   | 2000                 | V    |              |

| ESD Rating (Machine Model)    |                   | 300                  | V    |              |

<sup>\*</sup> Rthja was derived using the JEDEC boards.

# **Operating Rating**

| Parameter            | Symbol   | Min. | Тур. | Max. | Unit |  |

|----------------------|----------|------|------|------|------|--|

| Power Supply Voltage | $V_{DD}$ | 2.7  | -    | 5.5  | V    |  |

### **Electrical Characteristics**

( $V_{DD}$  = 5.0V, Ta = 25°C, unless otherwise specified)

| Parameter                         | Symbol | Conditions                                                                      | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------|---------------------------------------------------------------------------------|------|------|------|------|

| Offset Voltage VOFF               |        | RL=4Ω, Av=21.6dB                                                                |      | -    | 25   | mV   |

| Supply Current                    | IDD    | No Input, No Load                                                               |      | 5.5  | 10   | mA   |

| Shutdown Current                  | ISD    | SD = GND                                                                        | -    | 0.04 | 4    | μΑ   |

| Output Power                      | Ро     | THD+N =1%, RL = $4\Omega$ , f = 1kHz                                            | -    | 1.9  | -    | W    |

| Output Fower                      |        | THD+N =1%, RL = 8Ω, f = 1kHz                                                    | -    | 1.25 | -    | W    |

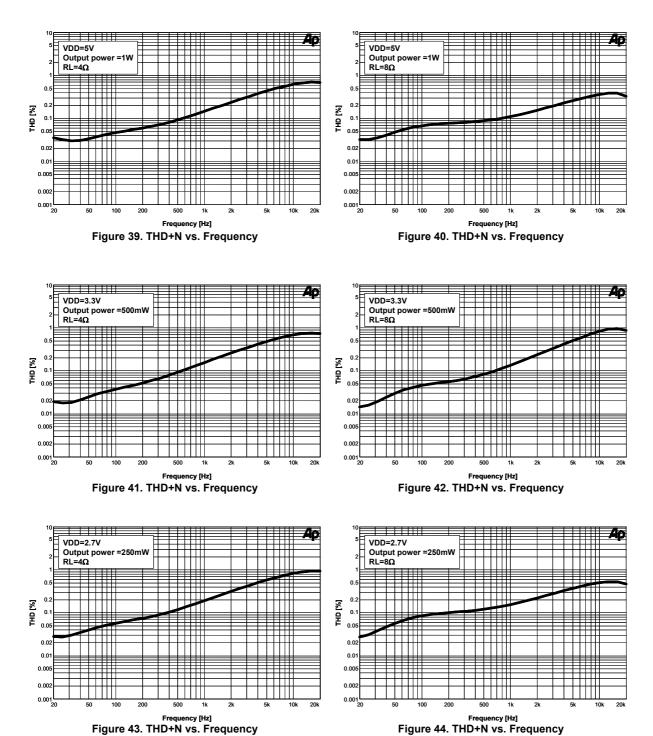

| Total Harmonic Distortion + Noise | THD+N  | $P_O = 1W$ , $RL=4\Omega$ , $f = 20kHz$                                         | -    | 0.6  | -    | %    |

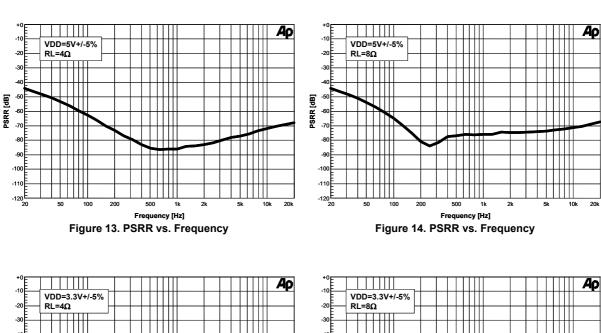

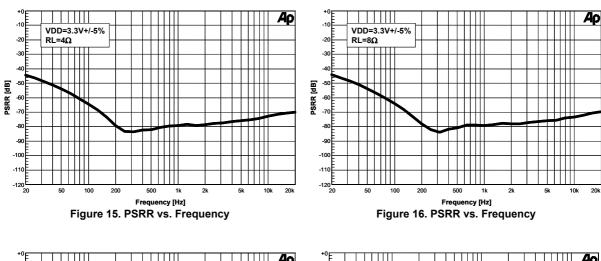

| Power Supply Rejection Ratio      | PSRR   | $C_{byp}$ = 1 $\mu$ F, RL=4 $\Omega$ , BTL Mode, $\Delta$ VDD=500mVpp, f = 1kHz | 38   | 68   | 1    | dB   |

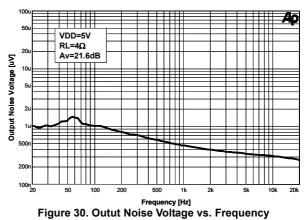

| Output Noise Voltage              | VN     | Input=GND, RL=4Ω, f=1kHz                                                        | -    | -120 | -    | dBv  |

### **Electrical Characteristics**

(V<sub>DD</sub> = 3.3 V, Ta = 25°C, unless otherwise specified)

| Parameter                         | Symbol     | Conditions                                                                      | Min. | Тур. | Max. | Unit |

|-----------------------------------|------------|---------------------------------------------------------------------------------|------|------|------|------|

| Offset Voltage                    | Voff       | RL=4Ω, Av=21.6dB                                                                |      | -    | 25   | mV   |

| Supply Current                    | IDD        | No Input, No Load                                                               |      | 4.5  | 8    | mA   |

| Shutdown Current                  | ISD        | SD = GND                                                                        | -    | 0.04 | 4    | μΑ   |

| Output Power                      | PO THD+N = | THD+N =1%, RL = $4\Omega$ , f = 1kHz                                            | -    | 0.75 | -    | W    |

| Output Fower                      | FU         | THD+N =1%, RL = 8Ω, f = 1kHz                                                    | -    | 0.53 | -    | W    |

| Total Harmonic Distortion + Noise | THD+N      | $P_O = 1W$ , $RL=4\Omega$ , $f = 20kHz$                                         | -    | 0.75 | -    | %    |

| Power Supply Rejection Ratio      | PSRR       | $C_{byp}$ = 1 $\mu$ F, RL=4 $\Omega$ , BTL Mode, $\Delta$ VDD=330mVpp, f = 1kHz | 38   | 68   | 1    | dB   |

| Output Noise Voltage              | VN         | Input=GND, RL=4Ω, f=1kHz                                                        | -    | -120 | -    | dBv  |

# **Electrical Characteristics**

(V<sub>DD</sub> = 2.7 V, Ta = 25°C, unless otherwise specified)

| Parameter                         | Symbol | Conditions                                                                      | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------|---------------------------------------------------------------------------------|------|------|------|------|

| Offset Voltage Vo                 |        | RL=4Ω, Av=21.6dB                                                                | -25  | -    | 25   | mV   |

| Supply Current                    | IDD    | No Input, No Load                                                               |      | 4.1  | 7    | mA   |

| Shutdown Current                  | ISD    | SD = GND                                                                        | -    | 0.04 | 4    | μΑ   |

| Output Power                      | Ро     | THD+N =1%, RL = $4\Omega$ , f = 1kHz                                            | -    | 0.45 | -    | W    |

| Output Fower                      |        | THD+N =1%, RL = $8\Omega$ , f = 1kHz                                            | -    | 0.32 | -    | W    |

| Total Harmonic Distortion + Noise | THD+N  | $P_O$ = 0.5W, RL=4Ω, f = 20kHz                                                  | -    | 0.9  | -    | %    |

| Power Supply Rejection Ratio      | PSRR   | $C_{byp}$ = 1 $\mu$ F, RL=4 $\Omega$ , BTL Mode, $\Delta$ VDD=270mVpp, f = 1kHz | 36   | 62   | -    | dB   |

| Output Noise Voltage              | VN     | Input=GND, RL=4Ω, f=1kHz                                                        | -    | -120 | -    | dBv  |

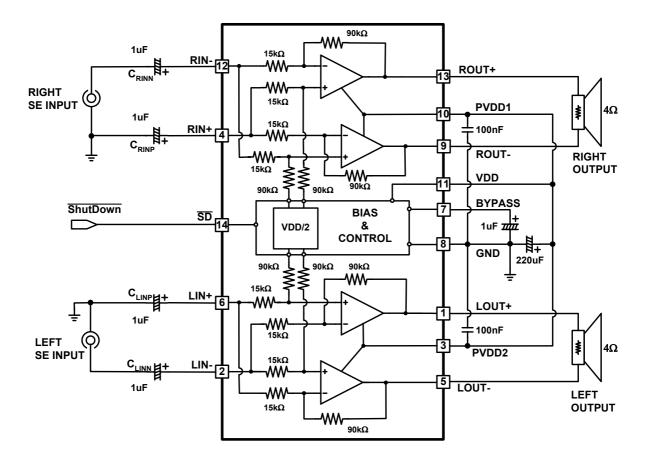

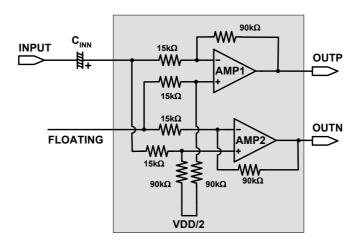

# **Typical Application Circuits**

### Single-Ended Input

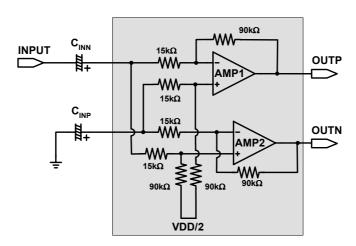

# **Typical Application Circuits (continued)**

### **Differential Input**

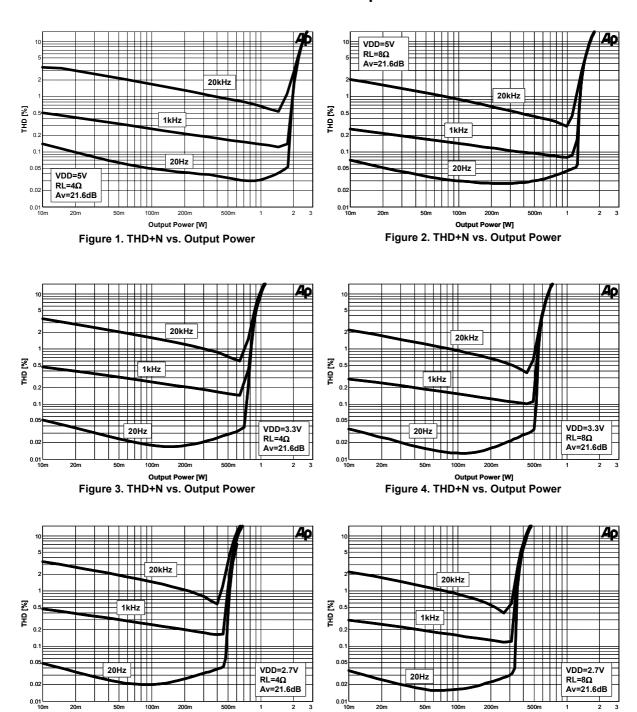

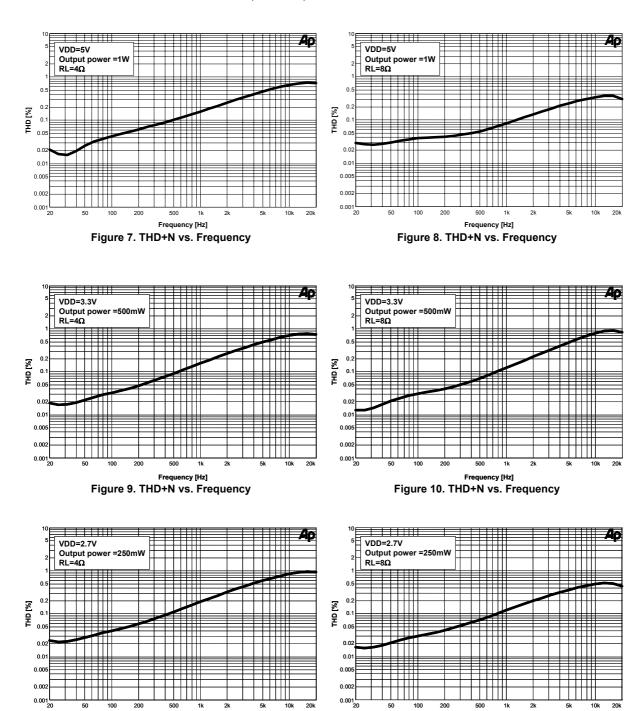

## **Performance Characteristics: Differential Input**

Figure 5. THD+N vs. Output Power

Output Power [W]

Figure 6. THD+N vs. Output Power

Frequency [Hz]

Figure 11. THD+N vs. Frequency

Figure 12. THD+N vs. Frequency

Output Power [W]

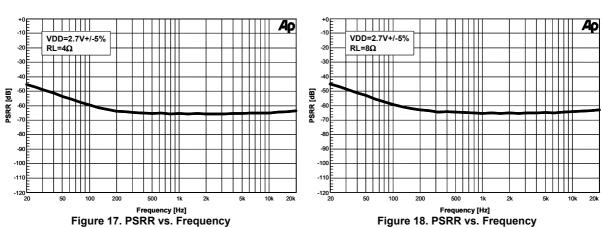

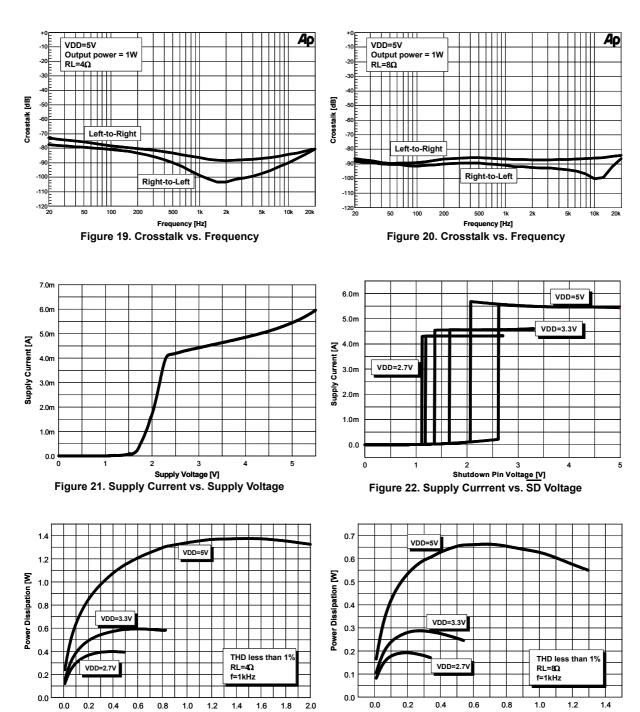

Figure 23. Power Dissipation vs. Output Power

Output Power [W]

Figure 24. Power Dissipation vs. Output Power

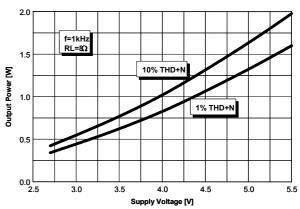

Figure 25. Output Power vs. Supply Voltage

Figure 26. Output Power vs. Supply Voltage

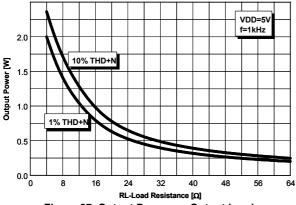

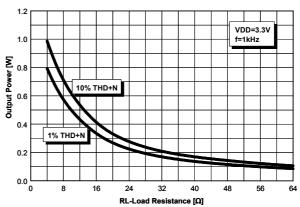

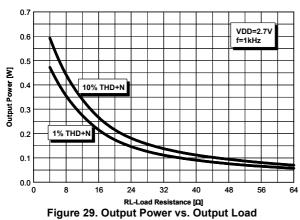

Figure 27. Output Power vs. Output Load

Figure 28. Output Power vs. Output Load

## **Performance Characteristics: Single-Ended Input**

Figure 45. Power Derating Curve

#### Notes:

- Single Layer(JESD51-3):

Thermal Vias: 0

Board Size: 76.2mm\*114.3mm\*1.57mm(JESD51-3)

- Board Size: '76.2min\*114.3min\*1.57min(JESD51-3)

Copper Thickness: 2.0oz

Copper Coverage: Top Layer: Traces + Metalization Area(3.34mm\*2.24mm)

Multi Layer(JESD51-7):

Thermal Vias: 6

- Thermal Vias: 6

Board Size: 76.2mm\*114.3mm\*1.6mm(JESD51-7)

Copper Thickness: 2.0oz/1.0oz/1.0oz

Copper Coverage: Top Layer: Traces + Metalization Area(3.34mm\*2.24mm)

Middle Layers(Power/Ground Planes): 74.2mm\*74.2mm

JESD51-3: Low Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages(Single Layer)

JESD51-7: High Effective Thermal Conductivity Test Board for Leaded Surface Mount Packages(Multi Layers)

JESD51-2: Integrated Circuits Thermal Test Method Environmental Conditions Natural Convection(Still Air)

### **Applications Information**

#### **Functional Description**

The FAN7033MP is a stereo power amplifier capable of delivering 1.9W continuous RMS(Root Mean Square) power into  $4\Omega$  load with 1% THD(Total Harmonic Distortion). At 10% THD, the FAN7033MP can deliver above 2W into  $4\Omega$  load. The FAN7033MP has 5 supply input pins. Three among them are used for positive supply and the rest of them is for the ground. Three positive supply input pins : pin3(PVDD2), pin10(PVDD1) and pin11(VDD) must be tied together. To improve the cross-talk between cannels, these pins are not connected internally. Therefore, these pins must be externally connected on the PCB. Pin 8 and the exposed pad are allocated to ground. Thus, the exposed pad must be connected to the ground.

The FAN7033MP is provided with differential inputs. These inputs increase the common-mode noise immunity. Furthermore, differential configuration in the input section helps to decrease total harmonic distortion and pop noise that occurs when shutdown is released. When only single input is available, the distortion performance is slightly degraded.

To save the standby power consumption, the FAN7033MP provides shutdown function. Putting pin14(SD) to be low, the chip falls into shutdown mode. At this mode, it consumes micro power at the room temperature of 25°C and this power consumption is only due to the leakage current of the chip. This leakage current is the strong function of the temperature. Thus at the high ambient temperature, the shutdown current slightly increases. The logic threshold of shutdown pin lies nearby VDD/2. So, the logic threshold level does not follow TTL logic level. Thus, when the users want to control the chip according to the TTL logic level, some kinds of logic-level-changing circuit may be needed.

### **Operation of the Amplifier**

Figure 1. Configuration of Power Amplifier

Figure 1 shows the configuration of the single channel BTL(Bridge-Tied Load) power amplifier. To make the differential input configuration, the FAN7033MP uses several resistor networks as depicted in figure 1. For the input resistor,  $15k\Omega$  is used. This resistor converts the input voltage signal to the current signal. The converted current signal flows to the feedback resistor. For FAN7033MP, the feedback resistance is six times larger than input resistance. Thus, the gain is 12(about 21.6dB). For the 5V supply, the input signal has 0.83Vpeak voltage swing makes 10Vpp output swing. The exact gain formula is given by

$$OUTP - OUTN = 12(INP - INN)$$

(1)

As shown in equation (1), for the single-ended input case, the gain is also preserved. However, to get the same output swing with the differential input case, the input swing must be double comparing with the differential input swing.

#### **PCB Layout and Supply Regulation**

Metal trace resistance between the BTL output and the parasitic resistance of the power supply line both heavily

affect the output power. In order to obtain the maximum power depicted in the performance characteristics figures, outputs, power, and ground lines need wide metal trace. The parasitic resistance of the power line increases ripple noise and degrades the THD and PSRR performance. To reduce such unwanted effect, a large capacitor must be connected between VDD pin and GND pin as close as possible. To improve power supply regulation performance, use a capacitor with low ESR.

#### **Power Supply Bypassing**

Selection of a proper power supply bypassing capacitor is critical to obtaining lower noise as well as higher power supply rejection. Larger capacitors may help to increase immunity to the supply noise. However, considering economical design, attaching  $10\mu F$  electrolytic capacitor or tantalum capacitor with  $0.1\mu F$  ceramic capacitor as close as possible to the VDD pins are enough to get a good supply noise rejection.

#### **Selection of Input Capacitor**

The input capacitors CINN and CINP block the DC voltage also low frequency input signal. Thus, these capacitors act as a high pass filter. When there are DC level differences between input source and the amplifier, these capacitors block DC voltage and make easy connection. However, these capacitors limit the low frequency input signal. Thus to cover the full audio frequency range, the values of these are very important. The input impedance and the capacitance of these capacitors stand for the low frequency characteristics and -3dB frequency is

$$f_{L} = \frac{1}{2\pi \cdot Zin \cdot C}$$

(2)

Where Zin is the input equivalent impedance and C is the capacitance of the input capacitor.

For FAN7033MP, the input has several resistors and these resistors determine the input impedance. In the normal condition, (-) input of the amplifier looks like a voltage source since the negative feedback topology makes (-) input virtually be the AC ground. Thus, resistance between the negative input of the amplifier and input pin is  $15k\Omega$ . The resistance toward (+) input is the summation of  $15k\Omega$  and  $90k\Omega$ . Thus total input impedance is

$$Zin = 15k\Omega \parallel (15k\Omega + 90k\Omega) = 13.125k\Omega$$

(3)

Considering  $f_L$ =20Hz(the lowest frequency of the audio frequency range), it is possible to get the capacitance value from equation(2) and (3) as follow:

$$Cin = \frac{1}{2\pi \cdot Zin \cdot f_1} = 0.606uF \tag{4}$$

Thus, Cin must be higher than 0.606uF. In the application note, 1uF is chosen by considering input impedance variation during the chip fabrication.

When using a capacitor which has the polarity, customers must carefully connect the capacitor. The input DC level of the FAN7033MP is a half of VDD. Thus, if the DC level of a source is higher than VDD/2, the positive lead of the capacitor must be faced toward the source.

### **Shutdown Mode**

In order to reduce power consumption while not in use, the FAN7033MP contains a shutdown pin to externally turnoff bias circuitry. This shutdown feature turns the amplifier off when a logic low is placed on the shutdown pin. The

trigger point between a logic low and logic high level is typically half-supply. It is best to switch between ground and

supply to provide maximum device performance. By switching the shutdown pin to VDD, the FAN7033MP supply

current draw will be minimized in idle mode. In either case, the shutdown pin should be tied to a definite voltages to

avoid unwanted state changes.

In many appplications, a microcontroller or microprocessor output is used to control the shutdown circuitry which provides a quick, smooth transition into shutdown. Another solution is to use a single-pole, single-throw switch in conjunction with an external pull-down resistor. When the switch is closed, the shutdown pin is connected to VDD and enables the amplifier. If the switch is open, then the external pull-down resistor will disable the FAN7033MP. This scheme guarantees that the shutdown pin will not float thus preventing unwanted state changes.

#### Single-Ended Input

For the case, a source does not provide the fully differential signal, the residual input must be well treated.

Case (A): Residual Input Pin Floating

Case (B): AC Coupling to Ground

Case(A): For this case, input is left alone without any treatment, that is, input pin is floating. Even the pin is floating, the BTL amplifier works and drives load. However, this configuration might cause unwanted noise at the output signal. Furthemore, floated configuration decreases PSRR(Power Supply Rejection Ratio) and increase POP noise.

Case(B): Case(B) is strongly recommended. This configuration increases PSRR and decreases POP noise as well. Of cource, to get the best performance, CINP must be the same value with CINN.

### THD+N(Total Harmonic Distortion plus Noise)

THD+N stands for linearity and output noise of the amplifier as well. The FAN7033MP has the circuit for enhancing THD. In spite of that, to get low THD+N, users should follow the recommendation:

- (1) Use fully differential input configuration: A fully differential input makes low THD at output. Thus, for a single-ended input case, THD+N slightly increaes.

- (2) Do not miss CBYP. CBYP helps to increase PSRR. Thus, using this capacitor, it is possible to increase noise immunity from the supply line.

- (3) Do not miss CSUP. Voltage fluctuation in supply line increases THD. Thus, such voltage fluctuation must be reduced to get low THD by connecting this capacitor between all VDD pins and the ground as closely as possible.

## **Mechanical Dimensions**

## Package

### **Dimensions in millimeters**

# **Ordering Information**

| Device    | Package | Operating Temperature |

|-----------|---------|-----------------------|

| FAN7033MP | 14MLP   | -40°C ~ +85°C         |

### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com