#### **Features**

- Antenna Driver Stage with Adjustable Antenna Peak Current for up to 1.5 A

- Frequency Tuning Range from 100 kHz to 150 kHz

- Automatic Antenna Peak Current Regulation

- Self-tuning Oscillator for Antenna Resonant Frequency Adaption

- Capable of Driving a High-Q Antenna

- Integrated 5 V Regulator for External Load up to 10 mA

- Bi-directional Single Wire Interface for Microcontroller or ECU

- LF Baud Rates up to 4 kbaud and Amplitude Shift Keying (ASK) Modulation

- Low Power Standby Mode < 50 μA</li>

- Antenna Driver Diagnosis: Peak Current, Antenna Frequency and Battery Voltage Monitoring

- Power Supply Range 8 V to 24 V Direct Battery Input

- Load Dump Protection up to 45 V for 12 V Boards

- Operation at Temperature -40°C to +105°C

- EMI and ESD According to Automotive Requirements

- Highly Integrated, Fewer External Components Required

- Driver Overcurrent Protection

- Overtemperature Protection

# **Applications**

• Tire Pressure Measurement (TPM)

### **Benefits**

- Self Tuning Capability to Antenna Resonance Frequency

- Adjustable Antenna Peak Current Value

- Highest Integration Level for Embedded Automotive Systems

Electrostatic sensitive device.

Observe precautions for handling.

# **Description**

The ATA5275 is an integrated 1.5 A peak current BCDMOS antenna driver IC dedicated as a 125 kHz wake-up channel transmitter for TPM applications.

It includes the full functionality to generate a magnetic LF field in conjunction with an antenna coil to transmit data and power to a receiver. The transmission can be controlled via a one wire I/O-interface by an external unit.

The smart power IC is delivered in a QFN20 power package with heat slug.

# 125 kHz Transmitter IC for TPM

**ATA5275**

**Preliminary**

# 1. General Description

The ATA5275 is a 125-kHz transmitter IC. It is dedicated to driving 125 kHz LC antenna tanks, specifically for the wake-up channel in Tire Pressure Measurement (TPM) applications.

It includes a control logic with VCO which generates the 125 kHz signal for the output driver stage. A phase lock circuit regulates the driver output frequency on the antenna resonance frequency, achieving a maximum field strength on the antenna. The driver duty cycle is regulated and stabilizes the antenna current for a wide supply voltage range.

The IC can be controlled by a microcontroller or ECU via the one wire bi-directional interface. It is used for the data transmission and to indicate errors. For the data transmission ASK modulation is used. The antenna signal is modulated by the DIO interface line.

The IC has a build in diagnosis function and detects detuning and broken or short wire of the antenna circuitry. If a failure is detected the IC indicates it by an error signal via the DIO line.

The integrated 5 V regulator can be used externally for a load up to 10 mA.

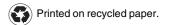

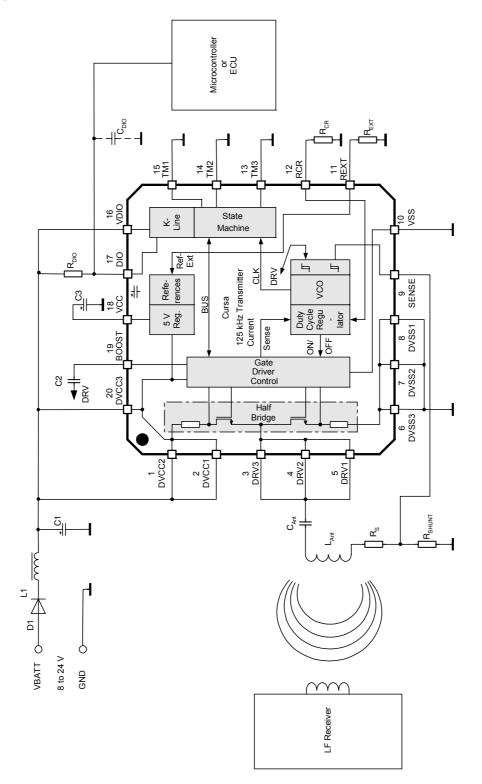

Figure 1-1. Block Diagram

# 2. Pin Configuration

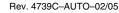

Figure 2-1. Pinning QFN20

Table 2-1. Pin Description

|         | 2000   | paor                                                    |

|---------|--------|---------------------------------------------------------|

| Pin (1) | Symbol | Function                                                |

| 1       | DVCC2  | Battery supply input                                    |

| 2       | DVCC1  | Battery supply input                                    |

| 3       | DRV3   | Antenna driver stage output                             |

| 4       | DRV2   | Antenna driver stage output                             |

| 5       | DRV1   | Antenna driver stage output                             |

| 6       | DVSS3  | Power supply ground                                     |

| 7       | DVSS2  | Power supply ground                                     |

| 8       | DVSS1  | Power supply ground                                     |

| 9       | SENSE  | Current zero crossing sense input                       |

| 10      | VSS    | Analog and digital ground                               |

| 11      | REXT   | External reference current input                        |

| 12      | RCR    | External reference for antenna peak current             |

| 13      | TM3    | For test purposes only                                  |

| 14      | TM2    | For test purposes only                                  |

| 15      | TM1    | For test purposes only                                  |

| 16      | VDIO   | DIO line interface voltage selection                    |

| 17      | DIO    | One-wire serial interface line                          |

| 18      | VCC    | 5 V supply output (for external storage capacitor only) |

| 19      | BOOST  | External bootstrap cap                                  |

| 20      | DVCC3  | Battery supply input                                    |

| 20      | DVCC3  | Dattery Supply Imput                                    |

Note: 1. Pin numbers valid for all revisions of the ATA5275

# 3. Functional Description

### 3.1 Operation Modes

There are two different operation modes for the ATA5275:

- · Standby mode

- Transmission mode

### 3.2 Standby Mode and Wake-up

After power-on-reset, the ATA5275 is in standby mode. For minimum power consumption, only the internal 5 V supply and the DIO line interface are active. The IC can be activated by the external control unit via the serial interface. The DIO line is called logic high if it is pulled up to the VDIO voltage level. The DIO line is called logic low if it is pulled down to the VSS voltage level. A low signal at the DIO line wakes-up the IC.

The circuit enters the standby mode if either of these three conditions are fulfilled:

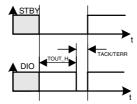

- 1. After power-on-reset and the DIO is high (see Figure 3-1)

- 2. After a time out of T<sub>OUTL</sub><sup>(1)</sup> during which DIO is permanently low (see Figure 3-3 on page 5)

- 3. After a time out of  $T_{OUTH}^{(2)}$  during which DIO is permanently high and an acknowledge time  $T_{ACK}/T_{EBB}^{(1)}$  (see Figure 3-2)

Notes: 1. Time does not depend on the antenna resonance frequency.

2. Time depends on the antenna resonance frequency.

Figure 3-1. STBY After POR

Figure 3-2. STBY After DIO = H

Figure 3-3. STBY After DIO = L

#### 3.3 Transmission Mode

#### 3.3.1 ASK Modulation

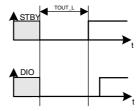

For the transmission of a wake-up signal or data to a receiver, the ATA5275 generates a antenna resonance synchronized signal at the antenna driver output (DRV pin). A connected LC antenna radiates a magnetic field. For the data transmission the field can be 100% amplitude modulated by the DIO interface input. If a low level signal is applied at the DIO pin, the driver generates a square wave signal DRV for the antenna. If a high level signal is applied at the DIO pin the driver is stopped and switched to ground. In this way ASK modulated data can be transmitted (see Figure 3-4).

Figure 3-4. Data Transmission

#### 3.3.2 Anti-bouncing Filter in Transmission Mode

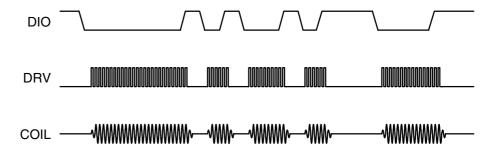

The DIO input signal is delayed for a anti-bouncing time.

The driver is switched on after a delay time of  $T_{DL}$  (typically 64  $\mu$ s) if the DIO is pulled to a low level continuously. The driver is switched-off after a delay time of  $T_{DH}$  if the DIO is pulled to high level.

The  $T_{DH}$  time depends on the antenna resonance frequency, suppressing short disturbance pulses from the DIO Line.

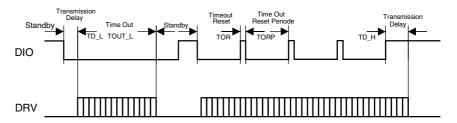

Figure 3-5. Anti-bouncing

#### 3.3.3 Time Out and Time Out Reset

The IC has a time out supervisor for the interface line to avoid unintended continuous transmission in case of line errors. The time out timer runs if the DIO pin is pulled to a low level. If the DIO pin is permanently low for more than the time  $T_{\text{OUTL}}$  the driver is switched off and the IC enters the standby mode. This avoids the discharging of the supply battery if the DIO line has a failure like a body contact or another permanent low level failure. The time  $T_{\text{OUTL}}$  depends on the antenna resonance frequency.

Figure 3-6. Time Out and Time Out Reset Protocol

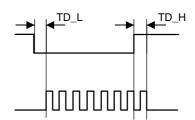

For continuous transmission periods the internal time out timer must be reset within the time out reset period  $T_{ORP}$  with a short high pulse of length  $T_{OR}$  at DIO. Any transmission time periods can be made by cyclical resetting of the time out timer (see Figure 3-6). The time  $T_{ORP}$  and  $T_{OR}$  depends on the antenna resonance frequency.

#### 3.3.4 Transmission Acknowledge and Error Signal

If no failure is detected during a transmission sequence the IC acknowledges the transmission by pulling the DIO line to low level for time  $T_{ACK}$  (typically 256  $\mu$ s). The acknowledge signal is generated at the end of a transmission sequence if the DIO line was high for the time  $T_{OUTH}$  (typically 16 ms).

Their are two types of error detection (see section "Diagnosis and Protection"):

- Immediate switch-off of the driver stage

- The failure is indicated through the DIO line based on transmission acknowledge and Error signal

At the end of transmission the IC indicates the failure by an error signal by pulling the DIO line to a low level for time  $T_{\text{ERR}}$  (typically 128  $\mu$ s) instead of  $T_{\text{ACK}}$ .

With the acknowledge and the error signal a connected microcontroller is able to recognize failures of the IC or the antenna module as well as DIO line failures like a broken wire or a short circuit.

DIO

Time Out TOUT\_H Acknowledge Failure Detection ToUT\_H TERR

TACK

Failure Detection ToUT\_H TERR

TERR

Failure Detection Tout Tout TERR

TERR

Figure 3-7. Transmission Acknowledge and Error Signal

The various failure types are monitored during transmission in time TFDx (see section "Diagnosis and Protection"). The time TFDx depends on the antenna resonance frequency.

## 3.4 Internal Voltage Regulator and POR

The IC contains a 5-V regulator. It is used for the supply voltage  $V_{CC}$  of the logic circuits and the low voltage analog circuits. Additionally, the  $V_{CC}$  can be used externally for loads up to 10 mA. The stabilized voltage is available at pin VCC and must be buffered with an external capacitor.

#### 3.4.1 Reset

After power on or after a voltage breakdown the power-on-reset circuit of the IC generates a reset pulse which sets the logic circuit to a defined initial state. A RESET is generated if the VCC is below the reset threshold voltage  $V_{POR}$  and after power on.

### 3.4.2 DIO Interface

The interface can be operated either as a 5-V microcontroller interface or as automotive K-line interface with the car battery voltage. In which mode it operates must be selected with the VDIO pin. If it is connected to 5 V the DIO pin operates as microcontroller interface and if it is connected with the battery voltage it operates as automotive interface according to the K-line specification.

### 3.5 Oscillator and Carrier Frequency Generation

A Voltage Controlled Oscillator (VCO) is used to clock the interface logic and the gate driver logic. The antenna driver output signal DRV is derived from this clock. The VCO operates in two modes: the self-oscillation mode with clock  $CLK_{SO}$  and the resonance tracking mode with clock  $CLK_{BT}$ .

#### 3.5.1 Self-oscillating Mode

If the antenna half-bridge is not activated the VCO is in self-oscillating mode. It runs at a center frequency  $CLK_{SO}$  of typically 125 kHz with an accuracy of  $\pm 8\%$ . For that purpose, an external reference resistor has to be applied to pin REXT. The resistor at pin REXT determines the VCO frequency proportionally. The recommended value is 100 k $\Omega$  achieving 125 kHz oscillator frequency.

#### 3.5.2 Resonance Tracking Mode

In case the antenna half-bridge is activated the VCO is tracked by the antenna current by means of it zero crossing detection. The VCO runs at the antenna resonance frequency stationary. The clock  $CLK_{RT}$  deviates  $\pm 1.4\%$  from the antenna resonance frequency, depending on the antenna quality and resonance frequency (see section "Application Hints"). For that purpose, an antenna current shunt resistor has to be applied to the SENSE pin. The shunt resistance is used internally for the zero crossing detection of the antenna current only.

By this feature the antenna operates with the maximum voltage, current and field strength. It is recommended specially for systems with high antenna Q-factors and low LC tolerances.

### 3.6 Coil Driver Output and Antenna Peak Current Control

The driver circuit consists on a DMOS half-bridge designed for 1.5 A peak current with low onresistance RDSON. It is short-circuit and overtemperature protected (see section "Diagnosis and Protection"). The half-bridge is switched on by a low level signal at DIO and generates a square wave voltage for the antenna RLC circuitry.

A very useful function of the driver stage is the build-in antenna current control loop. The IC senses the current through the antenna internally and controls the peak value  $IA_{PEAK}$  by controlling the duty cycle  $DC_{DRV}$  of the driver output.

So the antenna can be designed for maximum antenna current with the typical or even the minimum supply voltage. For higher supply voltages the current is controlled by reducing the driver duty cycle. The reference value for the antenna current  $IA_{PEAK}$  can be adjusted externally with a resistor  $R_{CR}$  at the RCR pin.

$$IA_{PEAK} = 750 \text{ mA} \times \frac{50 \text{ k}\Omega}{R_{CB}}$$

Note: Applying the formula above, the right driver current for the antenna has to be adjusted for the worst supply voltage case. The IC operates from 14% up to 86% duty cycle for that case and reduces the duty cycle for higher voltages (for the definition of the duty cycle DC<sub>DRV</sub>, see "Application Hints" on page 13).

This feature allows the user to operate the IC in a wide field of operational voltage field and protects the driver stage and the antenna from antenna overcurrent.

The driver out square wave starts with a duty cycle of 50%. After tree or four cycles the duty cycle can reach its maximum. As far as the peak current will stay smaller than  $IA_{peak}$  this duty cycle maximum is really 100%. If during the ramp up of the antenna current the envelope of the peak current will be greater than  $IA_{peak} + 20\%$  a pulse skipping function will suppress the next driver output pulse to minimize the antenna current overshoot.

### 3.7 Diagnosis and Protection

The IC supervises several parameters of IC operation for transmission diagnosis and circuit protection.

In any case of circuit protection mode or error detection the IC indicates this states according to the transmission protocol via the DIO line (see chapter "Transmission Acknowledge and Error Signal" on page 6).

# · ATA5275 [Preliminary]

#### 3.7.1 Circuit Protection Cases

The circuit protection is activated in normal mode. It is switched off in standby mode. In case a protection switch-off occurs the half-bridge is set in tri-state mode.

For all cases, there is a filter implemented to debounce half-bridge switch-off for a time of  $T_{DEB}$  (typically 20  $\mu$ s). This debounce filter is activated in case the half-bridge is activated. Otherwise it is RESET.

These are the following circuit protection cases:

- Load dump protection: In case the voltage at DVCC exceeds a voltage VBAT<sub>LD</sub> (typically 31 V).

- 2. Overcurrent protection: In case the current through the high side DMOS of the half-bridge exceeds a value of IOCH or the current through the low side DMOS of the half-bridge exceeds a value of IOCL (typically 2 A).

- 3. Overtemperature protection: In case the junction temperature exceeds a value of TSD (typically 165°C).

### 3.7.2 Error Diagnosis

During the transmission the diagnosis function of the IC supervises the antenna current and frequency and the half-driver bridge supply voltage. If any error is detected at the end of the transmission cycle the error indication is set (as in circuit protection case).

There are the following diagnosis cases:

- 1. Under-voltage detection: Monitors if DVCC is below VBAT<sub>UV</sub> (typically 6.5 V).

- 2. Antenna frequency error: Diagnosis if the oscillation frequency during transmission is outside the typical tracking range 90 kHz to 160 kHz.

- 3. Antenna peak current error: Diagnosis if the peak current is greater than the adjusted IA<sub>PEAK</sub> + 15% typically.

# 4. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameters                                     | Symbol                      | Min. | Max.                    | Unit |

|------------------------------------------------|-----------------------------|------|-------------------------|------|

| Ground                                         | VSS                         | 0    | 0                       | V    |

| Power ground                                   | DVSS1,2,3                   | -0.3 | +0.3                    | V    |

| Reverse protected battery voltage              | DVCC1,2,3                   | -0.3 | +44                     | V    |

| Half-bridge driver output                      | DRV1,2,3                    | -0.3 | DVCC + 0.3              | V    |

| Bootstrap                                      | BOOST                       | -0.3 | DVCC + 6 <sup>(2)</sup> | V    |

| 5-V regulator output                           | VCC                         | -0.3 | +7                      | V    |

| Analog reference input                         | REXT                        | -0.3 | VCC + 0.3               | V    |

| Analog reference input                         | RCR                         | -0.3 | VCC + 0.3               | V    |

| Digital test mode                              | TM1,2,3                     | -0.3 | VCC + 0.3               | V    |

| DIO interface supply                           | VDIO                        | -0.3 | DVCC + 0.3              | V    |

| DIO interface                                  | DIO                         | -0.3 | DVCC + 0.3              | V    |

| Zero crossing analog input                     | SENSE                       | -2   | DVCC + 0.3              | V    |

| Electromagnetic Interference                   | EMI                         |      | 250                     | V/M  |

| Minimum ESD protection (100 pF through 1.5 kΩ) |                             |      | 2 (on PCB)              | kV   |

| Power dissipation                              | P <sub>tot</sub>            |      | 2 <sup>(1)</sup>        | W    |

| Junction temperature                           | $\vartheta_{j}$             |      | 150                     | °C   |

| Storage temperature                            | $\vartheta_{STORE}$         | -55  | +125                    | °C   |

| Ambient temperature range under bias           | $\vartheta_{ambient}$       | -40  | +105                    | °C   |

| Soldering temperature (10 s)                   | $\vartheta_{\sf SOLDERING}$ |      | 220 + 5                 | °C   |

Notes: 1. May be limited by external thermal resistance.

# 5. Thermal Resistance

| Parameters                           | Symbol     | Value | Unit |

|--------------------------------------|------------|-------|------|

| Thermal resistance, junction ambient | $R_{thJA}$ | 35    | K/W  |

# 6. Operating Range

The operating conditions define the limits for functional operation and parametric characteristics of the device. Functionality outside these limits is not implied if not otherwise stated explicitly.

| Parameters                  | Symbol            | Value       | Unit |

|-----------------------------|-------------------|-------------|------|

| Operating supply voltage    | $V_{VBAT1}$       | 8 to 24     | V    |

| Operating temperature range | $\vartheta_{amb}$ | -40 to +105 | °C   |

<sup>2.</sup> If the low side driver is switched on, it is not allowed to connect a voltage source to pin BOOST.

# 7. Electrical Characteristics<sup>(1)</sup>

| No. | Parameters                                 | Test Conditions                                                                         | Pin          | Symbol                           | Min. | Тур.  | Max. | Unit | Type* |

|-----|--------------------------------------------|-----------------------------------------------------------------------------------------|--------------|----------------------------------|------|-------|------|------|-------|

| 1   | Power Supply                               |                                                                                         |              |                                  |      |       |      |      |       |

| 1.1 | Main supply voltage                        | I(VCC) = 10 mA,<br>including load and line<br>regulation                                | VCC          | V <sub>CC</sub>                  | 4.7  | 5.0   | 5.3  | V    | А     |

| 1.2 | Supply current                             | without antenna load                                                                    | DVCC         | I <sub>SUPP</sub>                | 2    | 10    | 20   | mA   | Α     |

| 1.3 | Standby current                            | Pin DVCC = 13.5 V,<br>$T_{amb} = 90^{\circ}C$                                           | DVCC         | I <sub>STBY</sub>                | 20   | 35    | 60   | μА   | В     |

| 1.4 | Power-on-reset threshold voltage           |                                                                                         | VCC          | V <sub>POR</sub>                 | 3.5  | 4     | 4.5  | V    | А     |

| 1.5 | Load dump protection voltage               |                                                                                         | DVCC         | VBAT <sub>LD</sub>               | 29   | 31    | 35   | V    | Α     |

| 1.6 | Under voltage detection                    |                                                                                         | DVCC         | VBAT <sub>UV</sub>               | 6.0  | 6.5   | 7.0  | V    | Α     |

| 1.7 | Thermal shut down                          |                                                                                         |              | TSD                              | 150  | 165   | 180  | °C   | В     |

| 1.8 | Protection debounce filter                 |                                                                                         |              | T <sub>DEB</sub>                 | 5    | 15    | 25   | μs   | C, D  |

| 2   | Half-bridge Driver Sta                     | ge                                                                                      |              |                                  |      |       |      |      |       |

| 2.1 | Coil driver resistance low side driver     |                                                                                         | DRV,<br>DVSS | RDS <sub>ONL</sub>               |      | 0.3   | 0.7  | Ω    | А     |

| 2.2 | Coil driver resistance high side driver    |                                                                                         | DVCC,<br>DRV | RDS <sub>ONH</sub>               |      | 0.3   | 0.7  | Ω    | А     |

| 2.3 | Overcurrent protection threshold low side  |                                                                                         | DRV,<br>DVSS | I <sub>OCL</sub>                 | 1.5  | 1.9   | 2.2  | А    | А     |

| 2.4 | Overcurrent protection threshold high side |                                                                                         | DVCC,<br>DRV | Госн                             | 1.5  | 1.75  | 2.2  | А    | А     |

| 2.5 | Driver output rise time                    | 10% to 90% slope<br>time,<br>0% = DVSS,<br>100% = DVCC<br>DVCC = 12 V<br>(smooth edges) | DRV          | T <sub>DRV,RISE</sub>            | 50   | 100   | 150  | ns   | D     |

| 2.6 | Driver output fall time                    | 10% to 90% slope<br>time,<br>0% = DVSS,<br>100% = DVCC<br>DVCC = 12 V<br>(smooth edges) | DRV          | T <sub>DRV,FALL</sub>            | 50   | 100   | 150  | ns   | D     |

| 3   | Antenna Peak Current                       | Control                                                                                 |              |                                  |      |       |      |      |       |

| 3.1 | Duty cycle control range                   |                                                                                         | DRV          | DC <sub>DRV</sub> <sup>(2)</sup> | 15   |       | 85   | %    | В     |

| 3.2 | Peak current control reference             |                                                                                         | RCR          | V <sub>RCR</sub>                 | 1.15 | 1.215 | 1.28 | V    | А     |

| 3.3 | Peak current control accuracy              | $R_{CR} = 25 \text{ k}\Omega$                                                           |              | IA <sub>peak</sub>               | 1.0  | 1.3   | 1.8  | А    | В     |

|     |                                            |                                                                                         |              |                                  |      |       |      |      |       |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. 8 V < V(DVCC) < 24 V; -40° C <  $\vartheta_{amb}$  < 105° C, unless otherwise specified; all values refer to GND

2. Definition of  $\mathrm{DC}_{\mathrm{DRV}}$  see "Application Hints" on page 13

# 7. Electrical Characteristics<sup>(1)</sup> (Continued)

| No. | Parameters                                                                                | Test Conditions                                                                              | Pin           | Symbol                 | Min. | Тур. | Max. | Unit         | Type* |

|-----|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------|------------------------|------|------|------|--------------|-------|

| 3.4 | Antenna peak under current threshold                                                      | 0% NOM value = $IA_{acc}$<br>RCR = 25 kΩ                                                     |               | IA <sub>UC</sub>       | -30  | -20  | -10  | %            | А     |

| 3.5 | Antenna peak overcurrent threshold                                                        | 0% NOM value = IA <sub>acc</sub><br>RCR = 25 kΩ                                              |               | IA <sub>OV</sub>       | 30   | 20   | 10   | %            | А     |

| 4   | Oscillator and Phase (                                                                    | Control                                                                                      |               |                        |      |      |      |              |       |

| 4.1 | VCO initial frequency                                                                     | Self oscillating mode = half-bridge not activated                                            |               | CLK <sub>SO</sub>      | 115  | 125  | 135  | kHz          | A     |

| 4.2 | VCO frequency tracking range                                                              | Tracking frequency<br>mode = half-bridge<br>activated                                        |               | CLK <sub>TR</sub>      | 80   |      | 200  | kHz          | В     |

| 4.3 | Phase shift between<br>voltage at DRV and<br>zero crossing of<br>current through<br>SENSE | Antenna resonance<br>frequency range =<br>100 kHz to150 kHz,<br>antenna quality = 5 to<br>50 | DRV,<br>SENSE | $\phi_{A}$             | -120 | 0    | +120 | ns           | В     |

| 4.4 | Phase control set-up time                                                                 | -240 ns ≤ φA ≤<br>+240 ns                                                                    | DRV,<br>SENSE | T <sub>setup</sub>     |      |      | 160  | μs           | D     |

| 4.5 | High frequency failure threshold                                                          |                                                                                              | DRV           | f <sub>vcoн</sub>      | 150  | 160  | 200  | kHz          | А     |

| 4.6 | Low frequency failure threshold                                                           |                                                                                              | DRV           | f <sub>VCOL</sub>      | 80   | 90   | 105  | kHz          | А     |

| 5   | DIO Interface                                                                             | 1                                                                                            |               |                        | •    | ı    |      | ı            | •     |

| 5.1 | VDIO leakage current                                                                      | Pin VDIO = 13.5 V,<br>Pin DIO = 13.5 V<br>T <sub>amb</sub> = 90°C                            | VDIO          | I <sub>VDIO,STBY</sub> | 2    | 4    | 5    | μА           | Α     |

| 5.2 | DIO leakage current                                                                       | Pin VDIO = 13.5 V,<br>Pin DIO = 13.5 V<br>T <sub>amb</sub> = 90°C                            | DIO           | I <sub>DIO,LEAK</sub>  | 2    | 4    | 200  | μА           | Α     |

| 5.3 | DIO sink current                                                                          |                                                                                              | DIO           | I <sub>DIO,LIMIT</sub> | 36   | 44   | 52   | mA           | Α     |

| 5.4 | Output low level                                                                          | I <sub>DIO</sub> = 20 mA                                                                     | DIO           | $V_{DIOL}$             |      | 1.2  | 1.5  | V            | Α     |

| 5.5 | Input low level threshold                                                                 | 100% = DVCC                                                                                  | DIO           | $V_{\mathrm{DIO,THL}}$ | 30   | 45   | 70   | %V<br>(VDIO) | Α     |

| 5.6 | Input high level threshold                                                                | 100% = DVCC                                                                                  | DIO           | $V_{\mathrm{DIO,TLH}}$ | 30   | 50   | 70   | %V<br>(VDIO) | А     |

| 6   | Transmission Protocol                                                                     |                                                                                              |               |                        |      |      |      |              |       |

| 6.1 | LF data baud rate                                                                         |                                                                                              |               | Bd <sub>RF</sub>       |      | 1    | 4    | kbit/s       | C, D  |

| 6.2 | Anti-bouncing time for activate half-bridge                                               | DIO = H $\rightarrow$ L,<br>for f <sub>VCO</sub> = 125 kHz                                   |               | T <sub>DL</sub>        |      | 64   |      | μs           | В     |

| 6.3 | Anti-bouncing time for de-activate half-bridge                                            | DIO = L $\rightarrow$ H,<br>for f <sub>VCO</sub> = 125 kHz                                   |               | T <sub>DH</sub>        |      | 64   |      | μs           | В     |

| 6.4 | Acknowledge pulse width                                                                   |                                                                                              |               | T <sub>ACK</sub>       |      | 256  |      | μs           | В     |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. 8 V < V(DVCC) < 24 V; -40 $^{\circ}$  C <  $\vartheta_{amb}$  < 105 $^{\circ}$  C, unless otherwise specified; all values refer to GND

<sup>2.</sup> Definition of  $\mathrm{DC}_{\mathrm{DRV}}$  see "Application Hints" on page 13

# 7. Electrical Characteristics<sup>(1)</sup> (Continued)

| No. | Parameters                                     | Test Conditions | Pin | Symbol            | Min. | Тур. | Max. | Unit | Type* |

|-----|------------------------------------------------|-----------------|-----|-------------------|------|------|------|------|-------|

| 6.5 | Error signal pulse width                       |                 |     | T <sub>ERR</sub>  |      | 128  |      | μs   | В     |

| 6.6 | Transmission time out de-activated half-bridge |                 |     | T <sub>OUTL</sub> |      | 16   |      | ms   | В     |

| 6.7 | Transmission time out activated half-bridge    |                 |     | T <sub>OUTH</sub> |      | 16   |      | ms   |       |

| 6.8 | Time out reset pulse width                     |                 |     | T <sub>OR</sub>   |      | 32   |      | μs   |       |

| 6.9 | Time out reset pulse period                    |                 |     | T <sub>ORP</sub>  |      | 15   |      | ms   |       |

<sup>\*)</sup> Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Notes: 1. 8 V < V(DVCC) < 24 V; -40° C <  $\vartheta_{amb}$  < 105° C, unless otherwise specified; all values refer to GND

2. Definition of DC<sub>DRV</sub> see "Application Hints" on page 13

# 8. External Components

The following external components have to be applied to the circuit for functional operation.

| Component        | Pin                  | Min.               | Тур. | Max. | Unit |

|------------------|----------------------|--------------------|------|------|------|

| R <sub>ext</sub> | REXT                 |                    | 100  |      | kΩ   |

| R <sub>CR</sub>  | RCR <sup>(4)</sup>   | 25                 |      | 200  | kΩ   |

| C <sub>0</sub>   | VCC                  |                    | 22   |      | μF   |

| C <sub>RF</sub>  | VCC <sup>(1)</sup>   |                    | 100  |      | nF   |

| Св               | BOOST                | 0.68               | 1    | 2    | nF   |

| R <sub>S</sub>   | SENSE <sup>(2)</sup> | 0.1 <sup>(3)</sup> | 0.5  | 1    | Ω    |

| R <sub>DIO</sub> | DIO                  | 0.6                | 1    | 6    | kΩ   |

Notes: 1. For EMC reasons only.

- 2. Sensitivity at input SENSE is proportional to resistor Rs times antenna peak current.

- 3. For antenna peak value 1.5 A.

- 4. Recommended range:  $R_{CR}$  = 25 to 100 k $\Omega$

# 9. Application Hints

A typical application of ATA5275 is shown in Figure 9-1 on page 14. The peak value of the antenna current can be estimated by the formula:

$$\hat{I}_{A} = \frac{2}{\pi} \times \frac{V_{DVCC}}{R_{A}} \times \sin\left(\frac{\pi}{2} \times DC_{DRV}\right) \times \cos\phi_{A}$$

Here  $R_A$  denotes the equivalent series resistance of the driver load, i.e., the external coil series resistance in series with the shunt resistance and the internal drain-source-on-resistance of the NDMOS. The duty cycle  $DC_{DRV}$  is the ratio of the driver high-side on-time with respect to the half of the oscillation period.

The phase difference  $\phi_A$  is measured as the time difference between the point of mass of VDRV and the peak value of the antenna current.

Figure 9-1. Application Circuit

Note: For the typical values of the external components, see table "Electrical Components" on page 13.

# 10. Ordering Information

| Extended Type Number | Package            | Remarks |

|----------------------|--------------------|---------|

| ATA5275-PGQ          | QFN20, 5 mm x 5 mm | -       |

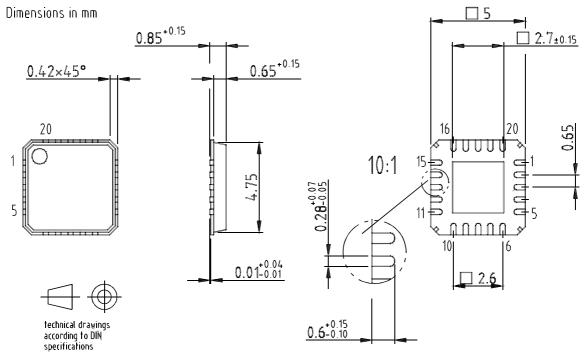

# 11. Package Information

Package: QFN 20 – 5x5 Exposed pad 2.7x2.7

(acc. JEDEC OUTLINE No. MO-220)

Drawing-No.: 6.543-5069.01-4

Issue: 3; 24.01.03

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland Tel: (41) 26-426-5555

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18

# Fax: (33) 2-40-18-19-60 *ASIC/ASSP/Smart Cards*

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building

East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine

BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2005. All rights reserved. Atmel®, logo and combinations thereof, and others, are registered trademarks, and Everywhere You Are<sup>SM</sup> and others are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.