### 2 K Digital Switch with Enhanced Stratum 3 DPLL

**Data Sheet**

**Features**

2048 channel x 2048 channel non-blocking digital Time Division Multiplex (TDM) switch at 8.192 and 16.384 Mbps or using a combination of ports running at 2.048, 4.096, 8.192 and/or 16.384 Mbps

32 serial TDM input, 32 serial TDM output streams

- Integrated Digital Phase-Locked Loop (DPLL) exceeds Telcordia GR-1244-CORE Stratum 3 specifications

- Output clocks have less than 1 ns of jitter (except for the 1.544 MHz output)

- DPLL provides holdover, freerun and jitter attenuation features with four independent reference source inputs

- Programmable key DPLL parameters (filter corner frequency, locking range, auto-holdover

November 2006

| Ordering Information                    |                                            |                          |  |  |  |  |  |  |  |

|-----------------------------------------|--------------------------------------------|--------------------------|--|--|--|--|--|--|--|

| ZL50018GAC<br>ZL50018QCC<br>ZL50018QCG1 | Trays<br>Trays<br>Trays, Bake &<br>Drypack |                          |  |  |  |  |  |  |  |

| ZL50018GAG2                             | 256 Ball PBGA**                            | Trays, Bake &<br>Drypack |  |  |  |  |  |  |  |

| •                                       | *Pb Free Matte Tin                         |                          |  |  |  |  |  |  |  |

| **Pb Free Tin/Silver/Copper             |                                            |                          |  |  |  |  |  |  |  |

|                                         | -40°C to +85°C                             |                          |  |  |  |  |  |  |  |

hysteresis range, phase slope, lock detector range)

- Exceptional input clock cycle to cycle variation tolerance (20 ns for all rates)

- Output streams can be configured as bidirectional for connection to backplanes

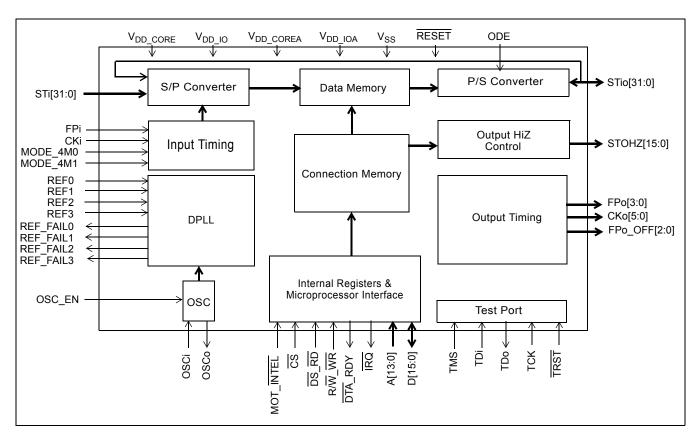

Figure 1 - ZL50018 Functional Block Diagram

Zarlink Semiconductor US Patent No. 5,602,884, UK Patent No. 0772912, France Brevete S.G.D.G. 0772912; Germany DBP No. 69502724.7-08

- Per-stream input and output data rate conversion selection at 2.048, 4.096, 8.192 or 16.384 Mbps. Input and output data rates can differ

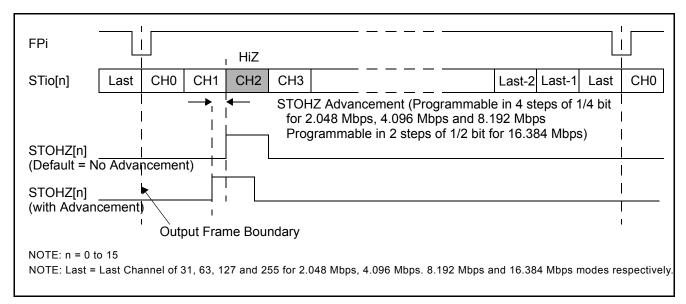

- · Per-stream high impedance control outputs (STOHZ) for up to 16 output streams

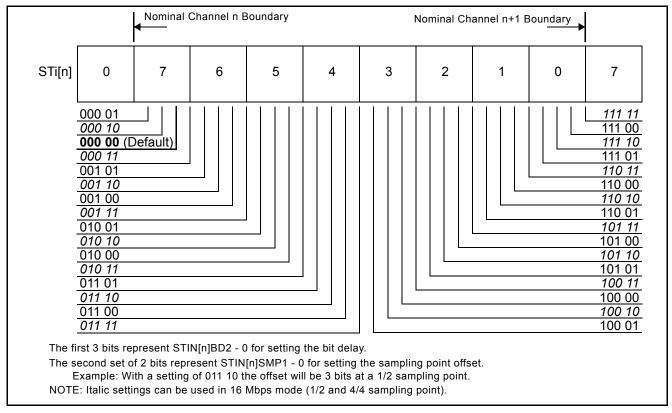

- · Per-stream input bit delay with flexible sampling point selection

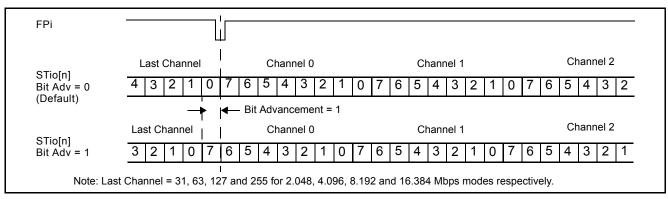

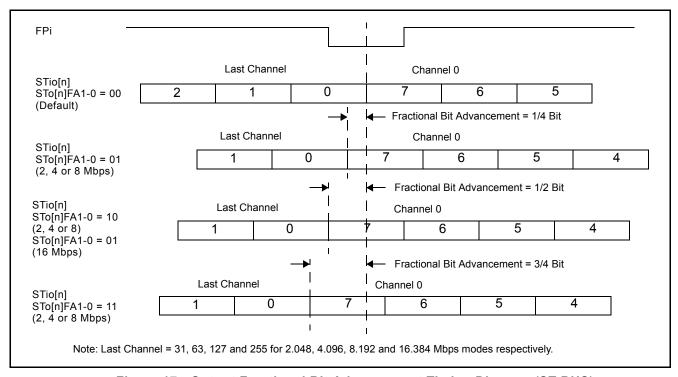

- · Per-stream output bit and fractional bit advancement

- Per-channel ITU-T G.711 PCM A-Law/μ-Law Translation

- · Multiple frame pulse and reference clock output

- Input clock: 4.096 MHz, 8.192 MHz, 16.384 MHz

- Input frame pulses: 61 ns, 122 ns, 244 ns

- · Per-channel constant or variable throughput delay for frame integrity and low latency applications

- · Per Stream Bit Error Rate Test circuits

- Per-channel high impedance output control

- · Per-channel message mode

- · Control interface compatible with Intel and Motorola 16-bit non-multiplexed buses

- · Connection memory block programming

- Supports ST-BUS and GCI-Bus standards for input and output timing

- IEEE-1149.1 (JTAG) test port

- 3.3 V I/O with 5 V tolerant inputs; 1.8 V core voltage

#### **Applications**

- PBX and IP-PBX

- · Small and medium digital switching platforms

- · Wireless base stations and controllers

- Remote access servers and concentrators

- Multi service access platforms

- Digital Loop Carriers

- Computer Telephony Integration

#### **Description**

The ZL50018 is a maximum 2,048 x 2,048 channel non-blocking digital Time Division Multiplex (TDM) switch. It has thirty-two input streams (STio - 31) and thirty-two output streams (STio0 - 31). The device can switch 64 kbps and Nx64 kbps TDM channels from any input stream to any output stream. Each of the input and output streams can be independently programmed to operate at any of the following data rates: 2.048, 4.096, 8.192 or 16.384 Mbps. The ZL50018 provides up to sixteen high impedance control outputs (STOHZ0 - 15) to support the use of external tristate drivers for the first sixteen output streams (STio0 - 15). The output streams can be configured to operate in bi-directional mode, in which case STi0 - 31 will be ignored.

The device contains two types of internal memory - data memory and connection memory. There are four modes of operation - Connection Mode, Message Mode, BER Mode and High Impedance Mode. In Connection Mode, the contents of the connection memory define, for each output stream and channel, the source stream and channel (the actual data to be output is stored in the data memory). In Message Mode, the connection memory is used for the storage of microprocessor data. Using Zarlink's Message Mode capability, microprocessor data can be broadcast to the data output streams on a per-channel basis. This feature is useful for transferring control and status information for external circuits or other TDM devices. In BER mode the output channel data is replaced with a pseudorandom bit sequence (PRBS) from one of 32 PRBS generators that generates a 2<sup>15</sup>-1 pattern. On the input side channels can be routed to one of 32 bit error detectors. In high impedance mode the selected output channel can be put into a high impedance state.

When the device is operating as a timing master, the internal digital PLL is in use. In this mode, an external 20.000 MHz crystal is required for the on-chip crystal oscillator. The DPLL is phase-locked to one of four input reference signals (which can be 8 kHz, 1.544, 2.048, 4.096, 8.192, 16.384 or 19.44 MHz provided on REF0 - 3). The on-chip DPLL operates in normal, holdover or freerun mode and offers jitter attenuation. The jitter attenuation function exceeds the Stratum 3 specification.

The configurable non-multiplexed microprocessor port allows users to program various device operating modes and switching configurations. Users can employ the microprocessor port to perform register read/write, connection memory read/write, and data memory read operations. The port is configurable to interface with either Motorola or Intel-type microprocessors.

The device also supports the mandatory requirements of the IEEE-1149.1 (JTAG) standard via the test port.

## **Table of Contents**

| Features                                                   |      |

|------------------------------------------------------------|------|

| Applications                                               |      |

| Description                                                |      |

| Changes Summary                                            | . 10 |

| 1.0 Pinout Diagrams                                        | . 11 |

| 1.1 BGA Pinout                                             |      |

| 1.2 QFP Pinout                                             |      |

| 2.0 Pin Description                                        |      |

| 3.0 Device Overview                                        | . 20 |

| 4.0 Data Rates and Timing                                  | . 21 |

| 4.1 External High Impedance Control, STOHZ0 - 15           |      |

| 4.2 Input Clock (CKi) and Input Frame Pulse (FPi) Timing   | . 22 |

| 5.0 ST-BUS and GCI-Bus Timing                              |      |

| 6.0 Output Timing Generation                               | . 24 |

| 7.0 Data Input Delay and Data Output Advancement           | . 29 |

| 7.1 Input Bit Delay Programming                            |      |

| 7.2 Input Bit Sampling Point Programming                   |      |

| 7.3 Output Advancement Programming                         |      |

| 7.4 Fractional Output Bit Advancement Programming          |      |

| 7.5 External High Impedance Control Advancement            |      |

| 3.0 Data Delay Through the Switching Paths                 |      |

| 8.1 Variable Delay Mode                                    |      |

| 8.2 Constant Delay Mode                                    |      |

| 9.0 Connection Memory Description                          |      |

| 10.0 Connection Memory Block Programming                   |      |

| 10.1 Memory Block Programming Procedure                    |      |

| 11.0 Device Operation in Master Mode and Slave Modes       |      |

| 11.1 Master Mode Operation.                                |      |

| 11.2 Divided Slave Mode Operation                          |      |

| 11.3 Multiplied Slave Mode Operation.                      |      |

| 12.0 Overall Operation of the DPLL                         |      |

| 12.1 DPLL Timing Modes                                     |      |

| 12.1.2 Holdover Mode.                                      |      |

| 12.1.3 Automatic Mode                                      |      |

| 12.1.3.1 Automatic Reference Switching Without Preferences |      |

| 12.1.3.2 Automatic Reference Switching With Preference     |      |

| 12.1.4 Freerun Mode                                        |      |

| 12.1.5 Software Controlled Mode                            | . 42 |

| 12.1.6 DPLL Internal Reset Mode                            | . 42 |

| 13.0 DPLL Frequency Behaviour                              | . 42 |

| 13.1 Input Frequencies                                     |      |

| 13.2 Input Frequencies Selection                           |      |

| 13.3 Output Frequencies                                    |      |

| 13.4 Pull-In/Hold-In Range (also called Locking Range)     |      |

| 14.0 Jitter Performance                                    |      |

| 14.1 Input Clock Cycle to Cycle Timing Variation Tolerance |      |

| 14.2 Input Jitter Acceptance                               |      |

|                                                            |      |

| 15.0 DPLL Specific Functions and Requirements              | . 44 |

# **Table of Contents**

| 15.1 Lock Detector                                    | 11  |

|-------------------------------------------------------|-----|

| 15.2 Maximum Time Interval Error (MTIE)               |     |

| 15.3 Phase Alignment Speed (Phase Slope)              |     |

| 15.4 Fast Locking Mode                                |     |

| 15.5 Reference Monitoring                             |     |

| 15.6 Single Period Reference Monitoring               | 45  |

| 15.7 Multiple Period Reference Monitoring             | 46  |

| 16.0 Microprocessor Port                              | 47  |

| 17.0 Device Reset and Initialization                  | 47  |

| 17.1 Power-up Sequence                                |     |

| 17.2 Device Initialization on Reset                   |     |

| 17.3 Software Reset                                   |     |

| 18.0 Pseudo-random Bit Generation and Error Detection | 48  |

| 19.0 PCM A-law/m-law Translation                      | 49  |

| 20.0 Quadrant Frame Programming                       | 50  |

| 21.0 JTAG Port                                        | 50  |

| 21.1 Test Access Port (TAP)                           | 50  |

| 21.2 Instruction Register                             |     |

| 21.3 Test Data Registers                              |     |

| 21.4 BSDL                                             |     |

| 22.0 Register Address Mapping                         |     |

| 23.0 Detailed Register Description                    | 55  |

| 24.0 Memory                                           |     |

| 24.1 Memory Address Mappings                          |     |

| 24.2 Connection Memory Low (CM_L) Bit Assignment      |     |

| 24.3 Connection Memory High (CM_H) Bit Assignment     |     |

| 25.0 Applications                                     |     |

| 25.1 OSCi Master Clock Requirement                    |     |

| 25.1.1 External Crystal Oscillator                    |     |

| 25.1.2 External Clock Oscillator                      |     |

| 26.0 DC Parameters                                    |     |

| 27.0 AC Darameters                                    | 107 |

Data Sheet

# **List of Figures**

| Figure 1 - 2              | ZL50018 Functional Block Diagram                                        | . 1 |

|---------------------------|-------------------------------------------------------------------------|-----|

| Figure 2 - 2              | ZL50018 256-Ball 17 mm x 17 mm PBGA (as viewed through top of package)  | 11  |

| _                         | ZL50018 256-Lead 28 mm x 28 mm LQFP (top view)                          |     |

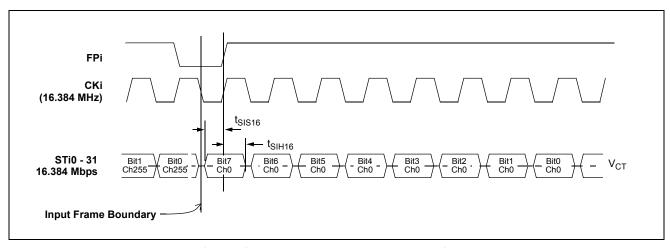

| _                         | nput Timing when CKIN1 - 0 bits = "10" in the CR                        |     |

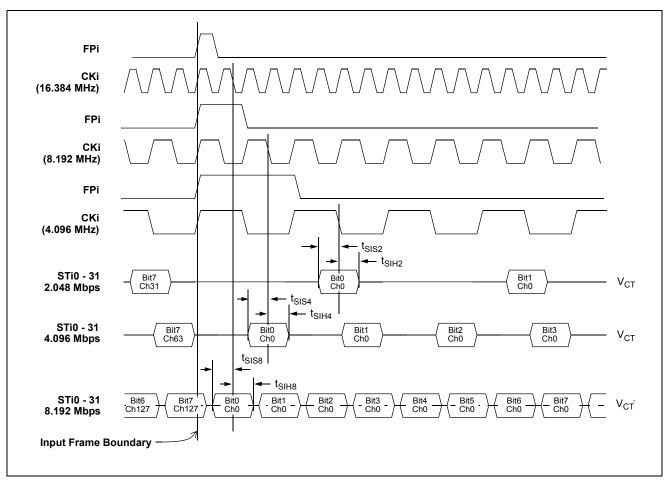

| _                         | nput Timing when CKIN1 - 0 bits = "01" in the CR                        |     |

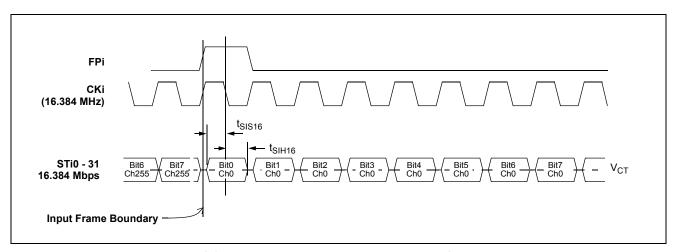

| _                         | nput Timing when CKIN1 - 0 = "00" in the CR                             |     |

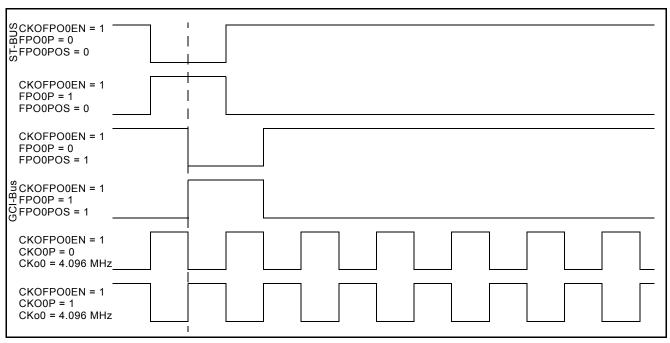

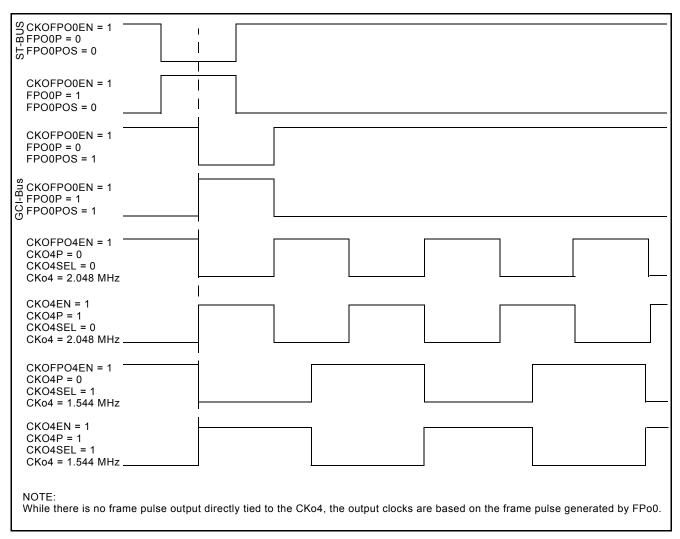

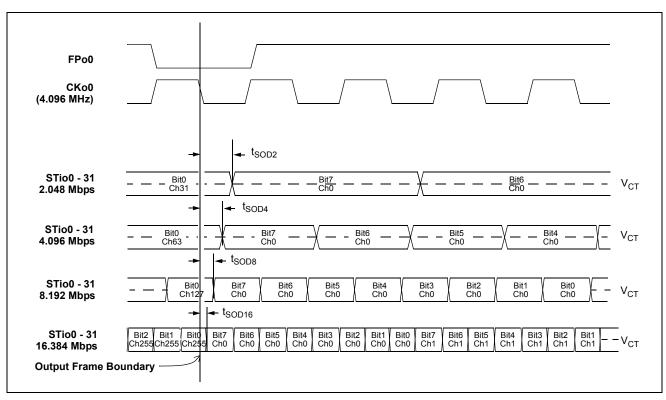

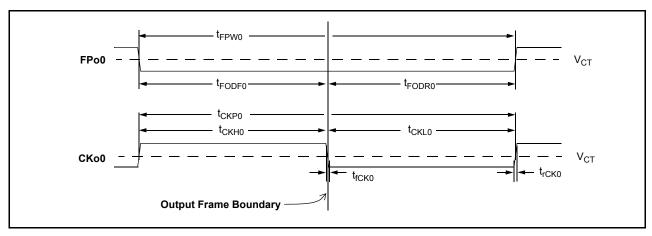

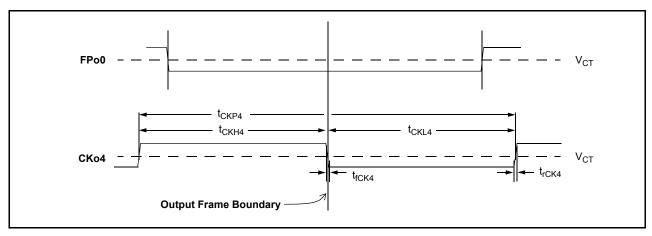

| •                         | Dutput Timing for CKo0 and FPo0                                         |     |

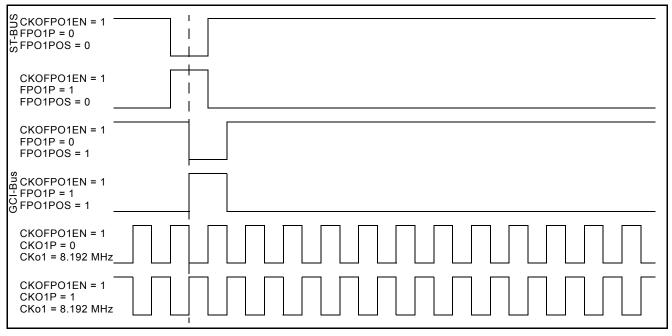

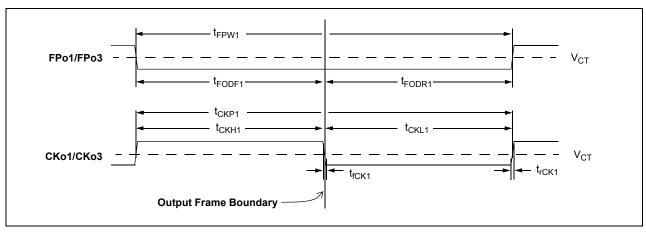

|                           | Dutput Timing for CKo1 and FPo1                                         |     |

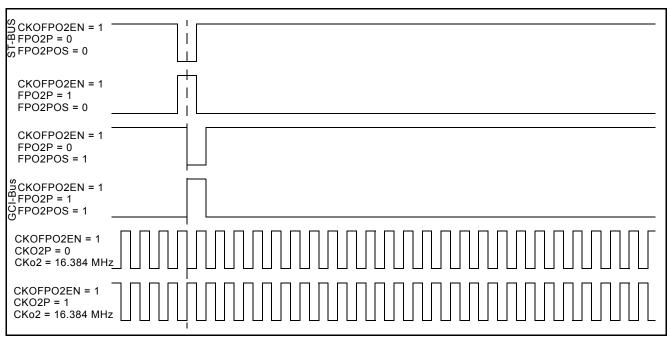

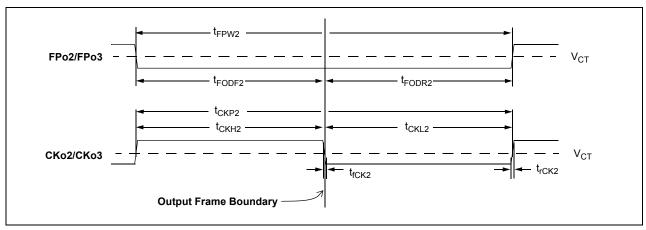

|                           | Dutput Timing for CKo2 and FPo2                                         |     |

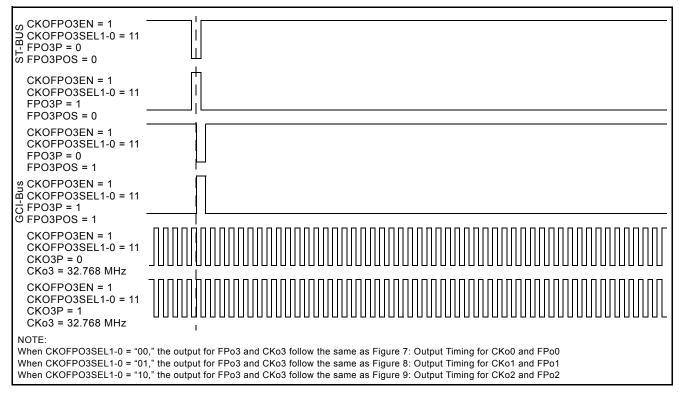

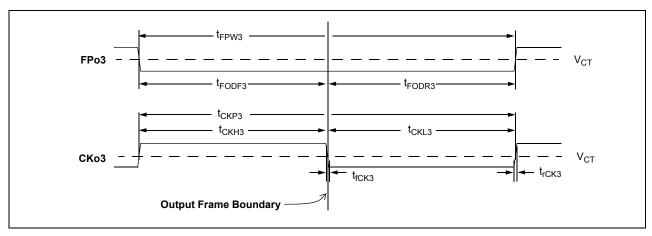

| Figure 10 -               | Output Timing for CKo3 and FPo3 with CKoFPo3SEL1-0="11"                 | 27  |

|                           | Output Timing for CKo4                                                  |     |

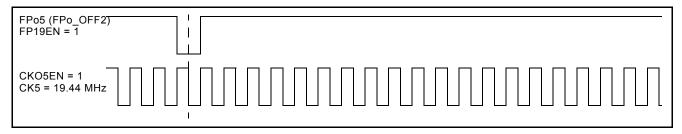

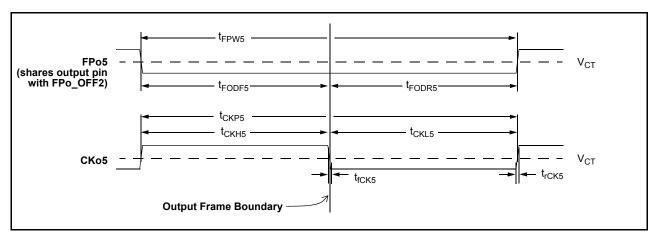

| •                         | Output Timing for CKo5 and FPo5 (FPo_OFF2)                              |     |

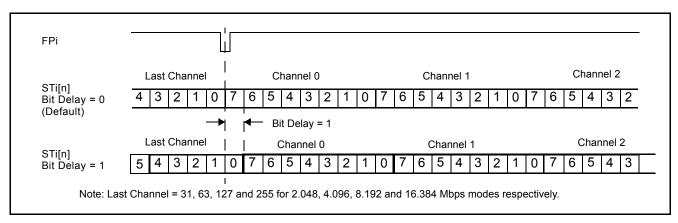

| _                         | Input Bit Delay Timing Diagram (ST-BUS)                                 |     |

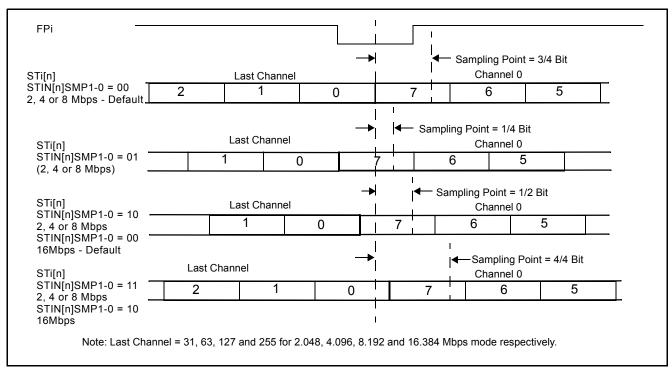

|                           | Input Bit Sampling Point Programming                                    |     |

| _                         | Input Bit Delay and Factional Sampling Point                            |     |

|                           | Output Bit Advancement Timing Diagram (ST-BUS)                          |     |

|                           | Output Fractional Bit Advancement Timing Diagram (ST-BUS)               |     |

| _                         | Channel Switching External High Impedance Control Timing                |     |

|                           | Data Throughput Delay for Variable Delay                                |     |

| _                         | Data Throughput Delay for Constant Delay                                |     |

| _                         | Automatic Reference Switching State Diagram with No Preferred Reference |     |

| _                         | Automatic Reference Switching State Diagrams with Preferred Reference   |     |

| _                         | Crystal Oscillator Circuit                                              |     |

| •                         | Clock Oscillator Circuit.                                               |     |

| _                         | Timing Parameter Measurement Voltage Levels.                            |     |

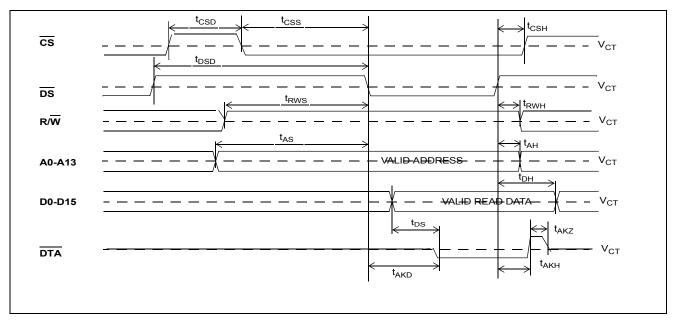

| •                         | Motorola Non-Multiplexed Bus Timing - Read Access                       |     |

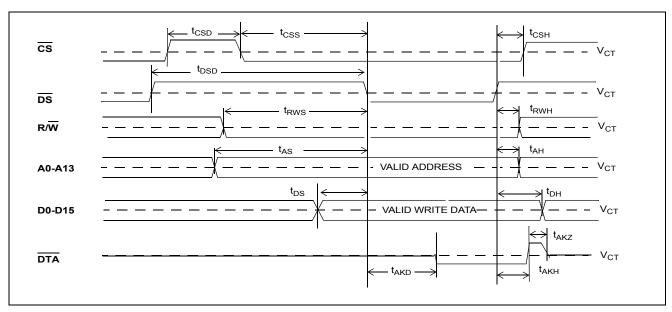

| _                         | Motorola Non-Multiplexed Bus Timing - Write Access                      |     |

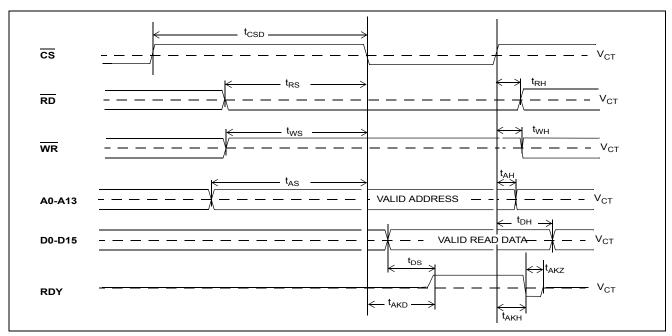

| _                         | Intel Non-Multiplexed Bus Timing - Read Access                          |     |

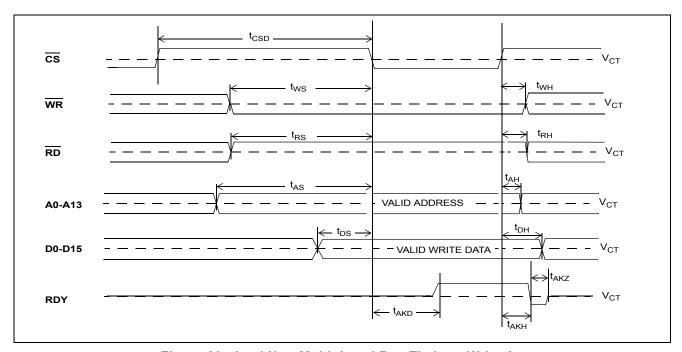

| _                         | Intel Non-Multiplexed Bus Timing - Write Access                         |     |

| •                         | JTAG Test Port Timing Diagram                                           |     |

| _                         | Frame Pulse Input and Clock Input Timing Diagram (ST-BUS).              |     |

|                           | Frame Pulse Input and Clock Input Timing Diagram (GCI-Bus)              |     |

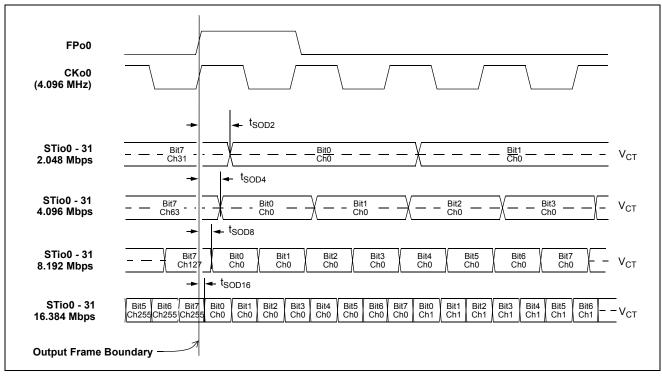

|                           | ST-BUS Input Timing Diagram when Operated at 2 Mbps, 4 Mbps, 8 Mbps     |     |

| _                         | ST-BUS Input Timing Diagram when Operated at 16 Mbps                    |     |

| _                         | GCI-Bus Input Timing Diagram when Operated at 2 Mbps, 4 Mbps, 8 Mbps    |     |

|                           | GCI-Bus Input Timing Diagram when Operated at 16 Mbps                   |     |

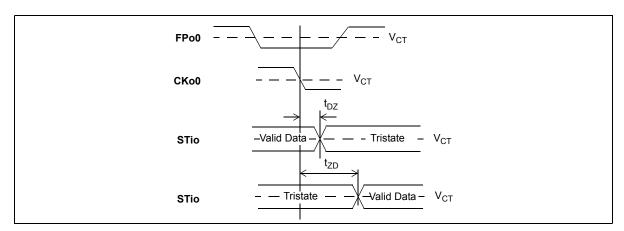

| •                         | ST-BUS Output Timing Diagram when Operated at 2, 4, 8 or 16 Mbps        |     |

| _                         | GCI-Bus Output Timing Diagram when Operated at 2, 4, 8 or 16 Mbps       |     |

| _                         | Serial Output and External Control                                      |     |

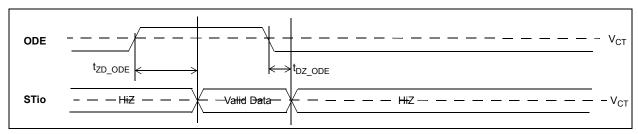

| •                         | Output Drive Enable (ODE)                                               |     |

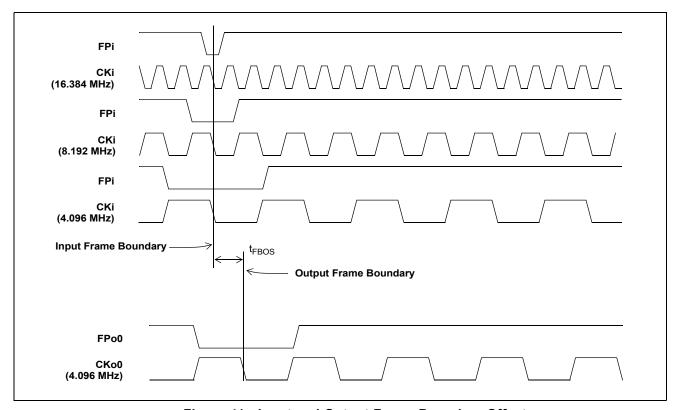

| _                         | Input and Output Frame Boundary Offset                                  |     |

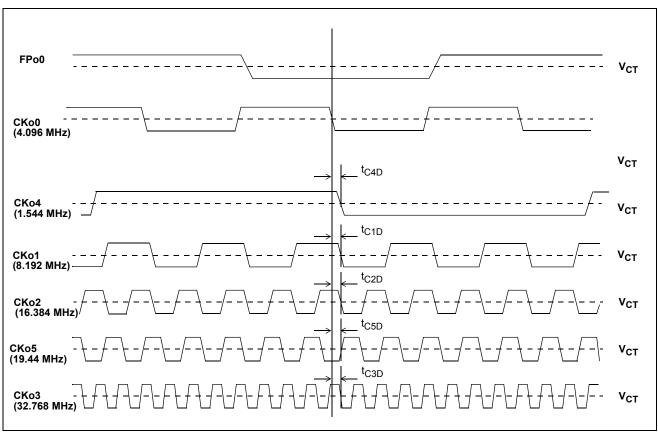

| _                         | FPo0 and CKo0 or FPo3 and CKo3 (4.096 MHz) Timing Diagram               |     |

| _                         | FPo1 and CKo1 or FPo3 and CKo3 (8.192 MHz) Timing Diagram               |     |

| _                         | FPo2 and CKo2 or FPo3 and CKo3 (16.384 MHz) Timing Diagram              |     |

| _                         | FPo3 and CKo3 (32.768 MHz) Timing Diagram                               |     |

|                           | FPo4 and CKo4 Timing Diagram (1.544/2.048 MHz)                          |     |

|                           | CKo5 Timing Diagram                                                     |     |

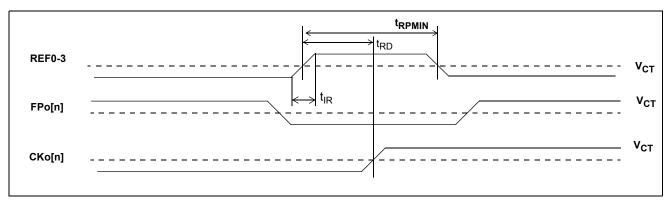

|                           | REF0 - 3 Reference Input/Output Timing                                  |     |

| i iyui <del>- 4</del> 0 - | TALL 0 - 0 Treference inharmathat timiling                              | 120 |

| 7 | L5 | N | N | 1 | R |

|---|----|---|---|---|---|

| _ | ᆫ  | v | v |   | v |

|      | •           | _            |        |

|------|-------------|--------------|--------|

| Liet | $^{\wedge}$ | $L_{1} \sim$ | IIIPAC |

| LISL | OI.         | ГIU          | ures   |

|      | •           |              |        |

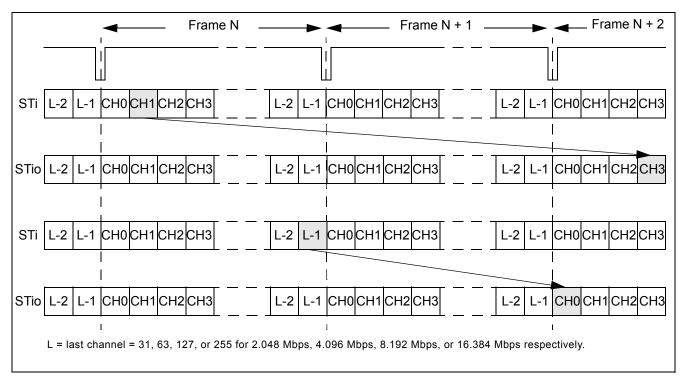

| Figure 49 - Ou | tput Timing (S | ST-BUS Format) |  |

|----------------|----------------|----------------|--|

|----------------|----------------|----------------|--|

## **List of Tables**

| Table 1 - CKi and FPi Configurations for Master and Divided Slave Modes     | <mark>22</mark>  |

|-----------------------------------------------------------------------------|------------------|

| Table 2 - CKi and FPi Configurations for Multiplied Slave Mode              | 22               |

| Table 3 - Output Timing Generation                                          | 25               |

| Table 4 - Delay for Variable Delay Mode                                     | 34               |

| Table 5 - Connection Memory Low After Block Programming                     | 36               |

| Table 6 - Connection Memory High After Block Programming                    | 36               |

| Table 7 - ZL50018 Operating Modes                                           | 37               |

| Table 8 - Preferred Reference Selection Options                             | 40               |

| Table 9 - DPLL Input Reference Frequencies                                  | 42               |

| Table 10 - Generated Output Frequencies                                     | 43               |

| Table 11 - Values for Single Period Limits                                  | 45               |

| Table 12 - Default Values for Single Period Limits                          | 46               |

| Table 13 - Default Multi-period Hysteresis Limits                           | 47               |

| Table 14 - Input and Output Voice and Data Coding                           | 49               |

| Table 15 - Definition of the Four Quadrant Frames                           | 50               |

| Table 16 - Quadrant Frame Bit Replacement                                   | 50               |

| Table 17 - Address Map for Registers (A13 = 0)                              | 52               |

| Table 18 - Control Register (CR) Bits                                       | 55               |

| Table 19 - Internal Mode Selection Register (IMS) Bits                      | 57               |

| Table 20 - Software Reset Register (SRR) Bits                               | 58               |

| Table 21 - Output Clock and Frame Pulse Control Register (OCFCR) Bits       | <mark>5</mark> 9 |

| Table 22 - Output Clock and Frame Pulse Selection Register (OCFSR) Bits     | 60               |

| Table 23 - FPo_OFF[n] Register (FPo_OFF[n]) Bits                            | 62               |

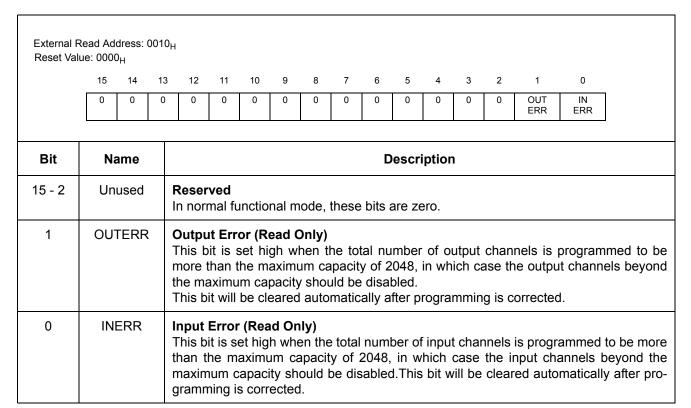

| Table 24 - Internal Flag Register (IFR) Bits - Read Only                    | 63               |

| Table 25 - BER Error Flag Register 0 (BERFR0) Bits - Read Only              | 63               |

| Table 26 - BER Error Flag Register 1 (BERFR1) Bits - Read Only              | 64               |

| Table 27 - BER Receiver Lock Register 0 (BERLR0) Bits - Read Only           | 64               |

| Table 28 - BER Receiver Lock Register 1 (BERLR1) Bits - Read Only           | 65               |

| Table 29 - DPLL Control Register (DPLLCR) Bits                              | 65               |

| Table 30 - Reference Frequency Register (RFR) Bits                          | 67               |

| Table 31 - Centre Frequency Register - Lower 16 Bits (CFRL)                 | <mark>6</mark> 9 |

| Table 32 - Centre Frequency Register - Upper 10 Bits (CFRU)                 | 70               |

| Table 33 - Software Delta Frequency Register (SWDFR) Bits                   | 70               |

| Table 34 - Frequency Offset Register (FOR) Bits - Read Only                 | 71               |

| Table 35 - Frequency Locking Range Register (FLRR) Bits                     |                  |

| Table 36 - Lock Detector Threshold Register (LDTR) Bits                     | 72               |

| Table 37 - Lock Detector Interval Register (LDIR) Bits                      | 72               |

| Table 38 - Slew Rate Limit Register (SRLR) Bits                             | 73               |

| Table 39 - Bandwidth Control Register (BWCR) Bits                           | 73               |

| Table 40 - Reference Change Control Register (RCCR) Bits                    | 75               |

| Table 41 - Reference Change Status Register (RCSR) Bits - Read Only         | 76               |

| Table 42 - Multi-period Near Upper Limit Register - Lower 16 Bits (MPNULRL) | 78               |

| Table 43 - Multi-period Near Upper Limit Register - Upper 16 Bits (MPNULRU) | 78               |

| Table 44 - Multi-period Far Upper Limit Register - Lower 16 Bits (MPFULRL)  | <b>7</b> 9       |

| Table 45 - Multi-period Far Upper Limit Register - Upper 16 Bits (MPFULRU)  | <b>7</b> 9       |

| Table 46 - Multi-period Near Lower Limit Register - Lower 16 Bits (MPNLLRL) | 80               |

| Table 47 - Multi-period Near Lower Limit Register - Upper 16 Bits (MPNLLRU) | 80               |

| Table 48 - Multi-period Far Lower Limit Register - Lower 16 Bits (MPFLLRL)  | 81               |

|                                                                             |                  |

Data Sheet

## **List of Tables**

| Table 49 - Multi-period Far Lower Limit Register - Upper 16 Bits (MPFLLRU)         | 81  |

|------------------------------------------------------------------------------------|-----|

| Table 50 - Multi-period Count Register - Lower 16 Bits (RnMPCRL) Bits, (n = 0 - 3) |     |

| Table 51 - Multi-period Count Register - Upper 16 Bits (RnMPCRU) Bits, (n = 0 - 3) | 83  |

| Table 52 - Upper Limit Register (RnULR) Bits, (n = 0 - 3)                          | 84  |

| Table 53 - Lower Limit Register (RnLLR) Bits, (n = 0 - 3)                          |     |

| Table 54 - Interrupt Register (IR) Bits - Read Only                                | 86  |

| Table 55 - Interrupt Mask Register (IMR) Bits                                      |     |

| Table 56 - Interrupt Clear Register (ICR) Bits                                     | 87  |

| Table 57 - Reference Failure Status Register (RSR) Bits - Read Only                | 88  |

| Table 58 - Reference Mask Register (RMR) Bits                                      | 89  |

| Table 59 - Reference Frequency Status Register (RFSR) Bits - Read only             | 91  |

| Table 60 - Output Jitter Control Register (OJCR) Bits                              | 93  |

| Table 61 - Stream Input Control Register 0 - 31 (SICR0 - 31) Blts                  | 93  |

| Table 62 - Stream Input Quadrant Frame Register 0 - 31 (SIQFR0 - 31) Bits          | 95  |

| Table 63 - Stream Output Control Register 0 - 31 (SOCR0 - 31) Bits                 | 97  |

| Table 64 - BER Receiver Start Register [n] (BRSR[n]) Bits                          | 98  |

| Table 65 - BER Receiver Length Register [n] (BRLR[n]) Bits                         | 98  |

| Table 66 - BER Receiver Control Register [n] (BRCR[n]) Bits                        | 99  |

| Table 67 - BER Receiver Error Register [n] (BRER[n]) Bits - Read Only              | 99  |

| Table 68 - Address Map for Memory Locations (A13 = 1)                              |     |

| Table 69 - Connection Memory Low (CM_L) Bit Assignment when CMM = 0                |     |

| Table 70 - Connection Memory Low (CM_L) Bit Assignment when CMM = 1                | 102 |

| Table 71 - Connection Memory High (CM_H) Bit Assignment                            | 103 |

### **Changes Summary**

The following table captures the changes from January 2006 to November 2006.

| Page | Item | Change                        |

|------|------|-------------------------------|

| 1    |      | Updated Ordering Information. |

The following table captures the changes from the October 2004 issue.

| Page       | Item                                                                                                                                                                          | Change                                                                                                                                                                                                                                                      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39, 76, 77 | Section 12.1, "DPLL Timing Modes" on page 39 RCCR Register bits "FDM1 - 0" on page 76 RCSR Register bits "DPM1 - 0" on page 77                                                | The on-chip DPLL's normal, holdover, automatic, and freerun modes are now collectively referred to as DPLL timing modes instead of operation modes. This change is to avoid confusion with the two main device operating modes; the master and slave modes. |

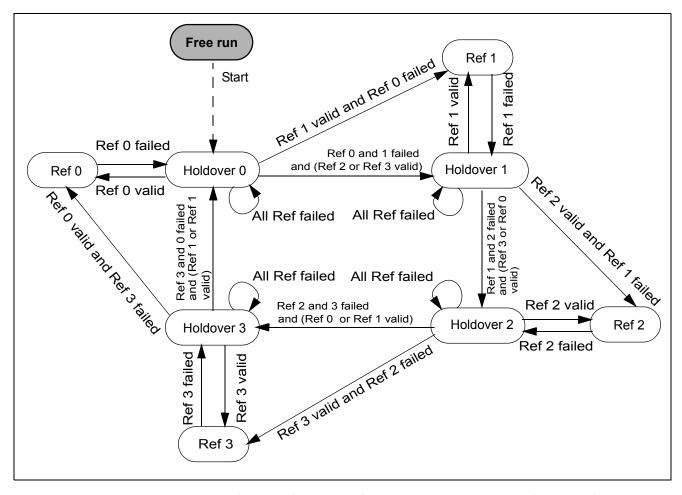

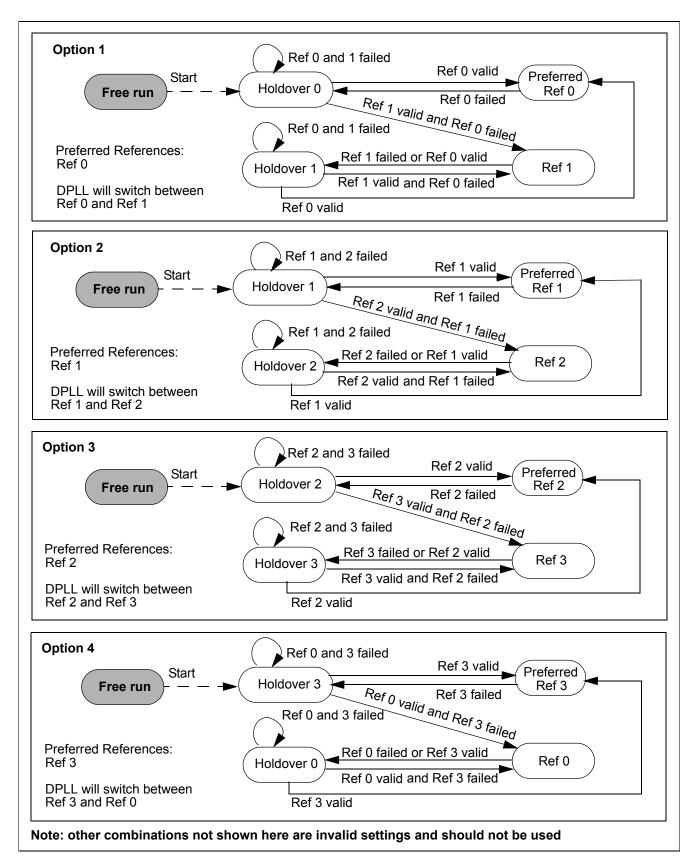

| 39, 40     | Section 12.1.3.1, "Automatic Reference<br>Switching Without Preferences" on page 39<br>and Section 12.1.3.2, "Automatic<br>Reference Switching With Preference" on<br>page 40 | Section 12.1.3.1 and Section 12.1.3.2 added to<br>clarify the DPLL's automatic reference switching<br>with and without preference operations in<br>Automatic Timing Mode.                                                                                   |

| 42, 45     | Section 12.1.4, "Freerun Mode" on page 42, and Section 15.4, "Fast Locking Mode" on page 45                                                                                   | Added description to specify that the device<br>should not be in freerun and fast lock modes<br>simultaneously. This is important in order to<br>avoid incorrect output frame pulse generation.                                                             |

| 72         | Table 36, Lock Detector Threshold Register (LDTR) Bits                                                                                                                        | Clarified threshold calculations.                                                                                                                                                                                                                           |

| 74         | Table 39, "Bandwidth Control Register (BWCR) Bits" Note 3.                                                                                                                    | Added a table footnote to specify that the DPLL's fastlock and freerun modes should not be set simultaneously.                                                                                                                                              |

| 75         | Table 40, "Reference Change Control<br>Register (RCCR) Bits" Bits "PRS1 - 0" and<br>Bits "PMS2 - 0"                                                                           | Added description to clarify that only two<br>consecutive references can be used in<br>automatic timing mode with a preferred<br>reference.                                                                                                                 |

| 76         | Table 40, "Reference Change Control<br>Register (RCCR) Bits", Bits "FDM1 - 0"                                                                                                 | Added description to specify the device should<br>not be in freerun and fast lock modes<br>simultaneously.                                                                                                                                                  |

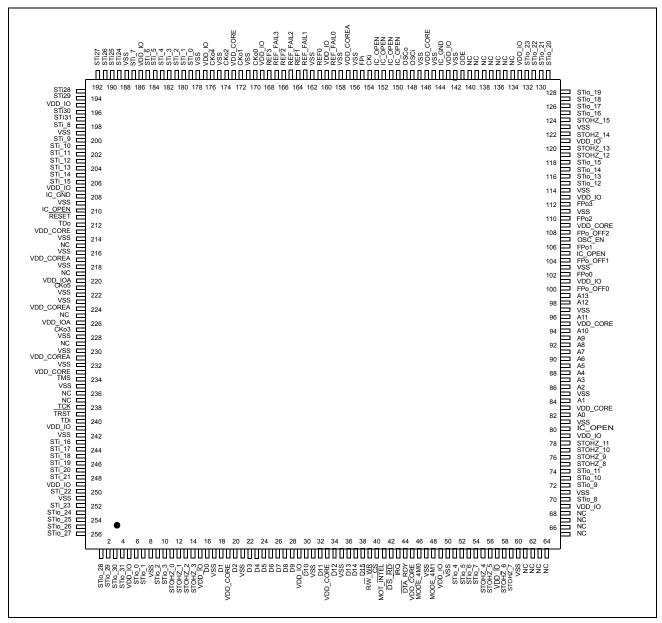

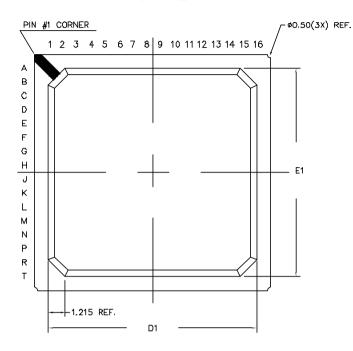

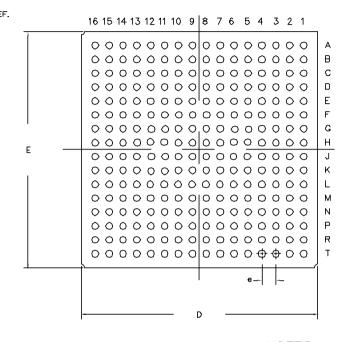

#### 1.0 **Pinout Diagrams**

#### 1.1 **BGA Pinout**

| • | 1               | 2                          | 3                   | 4                          | 5                          | 6                         | 7                         | 8               | 9                          | 10                        | 11                        | 12                 | 13                 | 14                 | 15           | 16              |   |

|---|-----------------|----------------------------|---------------------|----------------------------|----------------------------|---------------------------|---------------------------|-----------------|----------------------------|---------------------------|---------------------------|--------------------|--------------------|--------------------|--------------|-----------------|---|

| Α | V <sub>SS</sub> | STi29                      | STi28               | STi27                      | STi25                      | STi26                     | STi24                     | NC              | NC                         | STio22                    | STio23                    | STio21             | STio20             | NC                 | NC           | V <sub>SS</sub> | Α |

| В | STi31           | STi10                      | STi5                | STi4                       | CKo2                       | STi0                      | CKo0                      | REF2            | V <sub>DD</sub> _<br>COREA | FPi                       | CKi                       | IC_<br>OPEN        | IC_<br>OPEN        | OSCi               | ODE          | STio19          | В |

| С | STi30           | STi9                       | V <sub>SS</sub>     | STi7                       | STi6                       | STi1                      | CKo1                      | REF_<br>FAIL2   | V <sub>SS</sub>            | IC_<br>OPEN               | IC_<br>OPEN               | OSCo               | IC_GND             | $V_{SS}$           | STio15       | STio18          | С |

| D | STi17           | STi11                      | V <sub>DD_IO</sub>  | STi3                       | STi2                       | CKo4                      | REF3                      | REF1            | REF_<br>FAIL0              | V <sub>SS</sub>           | FPo_<br>OFF1              | OSC_<br>EN         | STio13             | V <sub>DD_IO</sub> | STio14       | STio16          | D |

| Е | STi16           | STi14                      | STi8                | V <sub>DD_IO</sub>         | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | REF_<br>FAIL3             | REF_<br>FAIL1   | REF0                       | NC                        | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>    | V <sub>DD_IO</sub> | STio12             | FPo2         | STio17          | Е |

| F | STi19           | STi15                      | STi12               | STi13                      | V <sub>DD_IO</sub>         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>DD_IO</sub> | IC_<br>OPEN        | FPo3               | FPo_<br>OFF2 | STOHZ15         | F |

| G | STi18           | RESET                      | IC_GND              | IC_<br>OPEN                | TDo                        | V <sub>DD_IO</sub>        | V <sub>SS</sub>           | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | V <sub>DD_IO</sub>        | A12                | A13                | FPo1               | FPo0         | STOHZ14         | G |

| Н | STi21           | V <sub>SS</sub>            | V <sub>SS</sub>     | V <sub>DD</sub> _<br>COREA | CKo5                       | V <sub>SS</sub>           | V <sub>SS</sub>           | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | A7                        | A9                 | A10                | FPo_<br>OFF0       | A11          | STOHZ12         | н |

| J | STi20           | V <sub>DD_IOA</sub>        | V <sub>DD_IOA</sub> | V <sub>SS</sub>            | V <sub>SS</sub>            | CKo3                      | V <sub>SS</sub>           | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | А3                        | A4                 | A5                 | A8                 | A6           | STOHZ13         | J |

| K | STi22           | V <sub>SS</sub>            | TMS                 | V <sub>SS</sub>            | V <sub>DD</sub> _<br>COREA | V <sub>DD_IO</sub>        | V <sub>SS</sub>           | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>SS</sub>           | V <sub>DD_IO</sub>        | IC_<br>OPEN        | A0                 | A2                 | A1           | STOHZ11         | K |

| L | STi23           | V <sub>DD</sub> _<br>COREA | TRST                | TCK                        | V <sub>DD_IO</sub>         | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub> | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>DD_IO</sub> | STio10             | STio11             | STio9        | STOHZ10         | L |

| М | STio25          | NC                         | TDi                 | D0                         | V <sub>SS</sub>            | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | D6              | D10                        | V <sub>DD</sub> _<br>CORE | V <sub>DD</sub> _<br>CORE | V <sub>SS</sub>    | MOT_<br>INTEL      | MODE_<br>4M0       | STio8        | STOHZ9          | М |

| N | STio24          | NC                         | V <sub>DD_IO</sub>  | STio0                      | STOHZ3                     | D1                        | D5                        | D7              | D11                        | D13                       | R <u>/W</u><br>_WR        | DTA_<br>RDY        | STio4              | $V_{DD\_IO}$       | STOHZ5       | STOHZ8          | N |

| Ρ | STio26          | NC                         | V <sub>SS</sub>     | STio1                      | STio3                      | STOHZ1                    | D3                        | D8              | D14                        | ĪRQ                       | STio5                     | STOHZ4             | STOHZ6             | $V_{SS}$           | STOHZ7       | NC              | Р |

| R | STio27          | NC                         | STOHZ0              | STio2                      | STOHZ2                     | D2                        | D4                        | D9              | D12                        | D15                       | CS                        | DS_RD              | MODE_<br>4M1       | STio6              | STio7        | NC              | R |

| Т | V <sub>SS</sub> | STio28                     | STio29              | STio31                     | STio30                     | NC                        | NC                        | NC              | NC                         | NC                        | NC                        | NC                 | NC                 | NC                 | NC           | V <sub>SS</sub> | Т |

|   | 1               | 2                          | 3                   | 4                          | 5                          | 6                         | 7                         | 8               | 9                          | 10                        | 11                        | 12                 | 13                 | 14                 | 15           | 16              |   |

**Note:** A1 corner identified by metallized marking. **Note:** Pinout is shown as viewed through top of package.

Figure 2 - ZL50018 256-Ball 17 mm x 17 mm PBGA (as viewed through top of package)

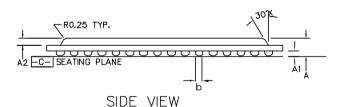

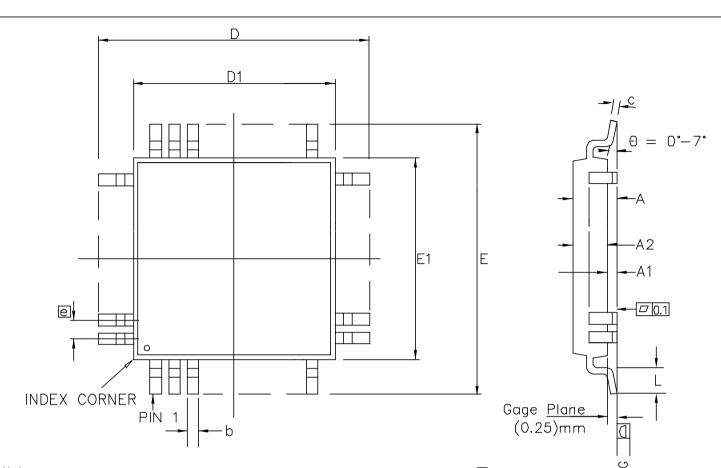

#### 1.2 QFP Pinout

Figure 3 - ZL50018 256-Lead 28 mm x 28 mm LQFP (top view)

# 2.0 Pin Description

| PBGA Pin<br>Number                                                                                                                                                                                                         | LQFP Pin<br>Number                                                                                                                                                                                                                         | Pin Name              | Description                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------|

| E6, E11, F6,<br>F7, F10,<br>F11, L6, L7,<br>L10, L11,<br>M6, M7,<br>M10, M11                                                                                                                                               | 19, 33,<br>45, 83,<br>95, 109,<br>146, 173,<br>213, 233                                                                                                                                                                                    | V <sub>DD_CORE</sub>  | Power Supply for the core logic: +1.8 V            |

| H4, K5, B9,<br>L2                                                                                                                                                                                                          | 217, 231,<br>157, 224                                                                                                                                                                                                                      | V <sub>DD_COREA</sub> | Power Supply for analog circuitry: +1.8V           |

| D3, D14, E4,<br>E13, F5,<br>F12, G6,<br>G11, K6,<br>K11, L5,<br>L12, N3,<br>N14                                                                                                                                            | 5, 15, 29,<br>49, 57,<br>69, 79,<br>101, 113,<br>121, 133,<br>143, 160,<br>169, 177,<br>186, 195,<br>207, 241,<br>249                                                                                                                      | V <sub>DD_IO</sub>    | Power Supply for I/O: +3.3 V                       |

| J2, J3                                                                                                                                                                                                                     | 220, 226                                                                                                                                                                                                                                   | V <sub>DD_IOA</sub>   | Power Supply for the CKo5 and CKo3 outputs: +3.3 V |

| A1, A16, C3,<br>C9, C14,<br>D10, E5,<br>E12, F8, F9,<br>G7, G8, G9,<br>G10, H2,<br>H3, H6, H7,<br>H8, H9,<br>H10, J4, J5,<br>J7, J8, J9,<br>J10, K2, K4,<br>K7, K8, K9,<br>K10, L8, L9,<br>M5, M12,<br>P3, P14, T1,<br>T16 | 8, 17, 21,<br>31, 35,<br>47, 50,<br>60, 71,<br>81, 85,<br>97, 103,<br>111, 114,<br>123, 142,<br>145, 147,<br>156, 158,<br>162, 171,<br>175, 178,<br>188, 199,<br>209, 214,<br>216, 218,<br>222, 223,<br>228, 230,<br>232, 235,<br>242, 251 | V <sub>SS</sub>       | Ground                                             |

| PBGA Pin<br>Number                                                                                                    | LQFP Pin<br>Number                                                                                                            | Pin Name              | Description                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

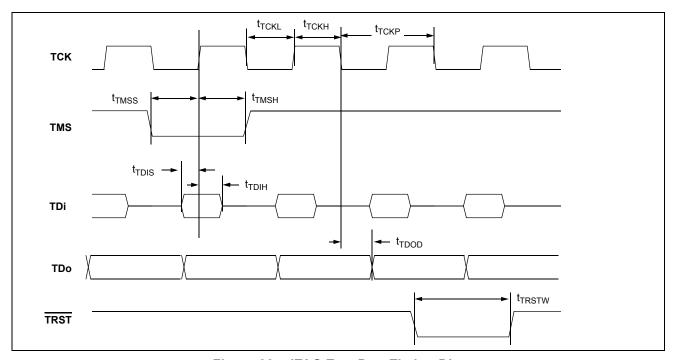

| К3                                                                                                                    | 234                                                                                                                           | TMS                   | Test Mode Select (5 V-Tolerant Input with Internal Pull-up) JTAG signal that controls the state transitions of the TAP controller. This pin is pulled high by an internal pull-up resistor when it is not driven.                                                                                                                                                          |  |  |  |

| L4                                                                                                                    | 238                                                                                                                           | TCK                   | Test Clock (5 V-Tolerant Schmitt-Triggered Input with Internal Pull-up) Provides the clock to the JTAG test logic.                                                                                                                                                                                                                                                         |  |  |  |

| L3                                                                                                                    | 239                                                                                                                           | TRST                  | Test Reset (5 V-Tolerant Input with Internal Pull-up) Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-Reset state. This pin should be pulsed low during power-up to ensure that the device is in the normal functional mode. When JTAG is not being used, this pin should be pulled low during normal operation.                        |  |  |  |

| M3                                                                                                                    | 240                                                                                                                           | TDi                   | Test Serial Data In (5 V-Tolerant Input with Internal Pull-up) JTAG serial test instructions and data are shifted in on this pin. This pin is pulled high by an internal pull-up resistor when it is not driven.                                                                                                                                                           |  |  |  |

| G5                                                                                                                    | 212                                                                                                                           | TDo                   | Test Serial Data Out (5 V-Tolerant Three-state Output) JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high impedance state when JTAG is not enabled.                                                                                                                                                                               |  |  |  |

| B12, B13,<br>C10, C11,<br>F13, G4,<br>K12                                                                             | 80, 105,<br>150, 151,<br>152, 153,<br>210                                                                                     | IC_OPEN               | Internal Test Mode (5 V-Tolerant Input with Internal Pull-down) These pins may be left unconnected.                                                                                                                                                                                                                                                                        |  |  |  |

| C13, G3                                                                                                               | 144, 208                                                                                                                      | IC_GND                | Internal Test Mode Enable (5 V-Tolerant Input): These pins MUST be low.                                                                                                                                                                                                                                                                                                    |  |  |  |

| A8, A9, A14,<br>A15, E10,<br>M2, N2, P2,<br>P16, R2,<br>R16, T6, T7,<br>T8, T9, T10,<br>T11, T12,<br>T13, T14,<br>T15 | 61, 62,<br>63, 64,<br>65, 66,<br>67, 68,<br>134, 135,<br>136, 137,<br>138, 139,<br>140, 215,<br>219, 225,<br>229, 236,<br>237 | NC                    | No Connect These pins MUST be left unconnected.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| M14, R13                                                                                                              | 46, 48                                                                                                                        | MODE_4M0,<br>MODE_4M1 | <b>4 M Input Clock Mode 0 to 1 (5 V-Tolerant Input with internal pull-down)</b> These two pins should be tied together and are typically used to select CKi = 4.096 MHz operation. See Table 7, "ZL50018 Operating Modes" on page 37 for a detailed explanation. See Table 18, "Control Register (CR) Bits" on page 55 for CKi and FPi selection using the CKIN1 - 0 bits. |  |  |  |

| PBGA Pin<br>Number | LQFP Pin<br>Number    | Pin Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|--------------------|-----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| D12                | 107                   | OSC_EN        | Oscillator Enable (5 V-Tolerant Input with Internal Pull-down) If tied high, this pin indicates that there is a 20 MHz external oscillator interfacing with the device. If tied low, there is no oscillator and CKi will be used for master clock generation. If the DPLL is activated, an external oscillator is required and this pin MUST be tied high.                                                                                                                                                                                                                                                               |  |  |  |

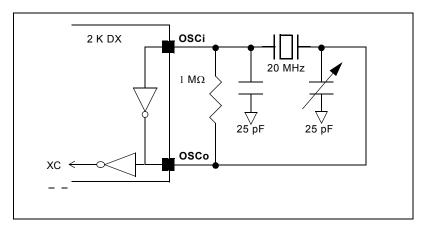

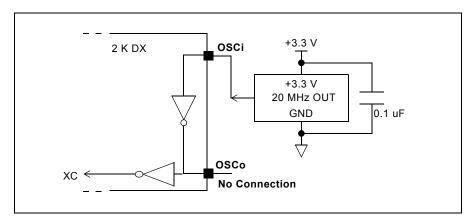

| C12                | 149                   | OSCo          | Oscillator Clock Output (3.3 V Output)  If OSC_EN = '1', this pin should be connected to a 20 MHz crystal (See Figure 23 on page 104) or left unconnected if a clock oscillator is connected to OSCi pin under normal operation (See Figure 24 on page 105).  If OSC_EN = 0, this pin MUST be left unconnected.                                                                                                                                                                                                                                                                                                          |  |  |  |

| B14                | 148                   | OSCi          | Oscillator Clock Input (3.3 V Input)  If OSC_EN = '1', this pin should be connected to a 20 MHz crystal (See Figure 23 on page 104) or to a clock oscillator under normal operation (See Figure 24 on page 105).  If OSC_EN = 0, this pin MUST be driven high or low by connecting either to V <sub>DD_IO</sub> or to ground.                                                                                                                                                                                                                                                                                            |  |  |  |

| E9, D8, B8,<br>D7  | 161, 164,<br>166, 168 | REF0 - 3      | Inputs)  If the device is in Master mode, these input pins accept 8 kHz, 1.544 MHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz or 19.44 MHz timing references independently. One of these inputs is defined as the preferred or forced input reference for the DPLL. The Reference Change Control Register (RCCR) selects the control of the preferred reference.  These pins are ignored if the device is in slave mode unless SLV_DPLLEN (bit 13) in the Control Register (CR) is set. When these input pins are not in use, they MUST be driven high or low by connecting either to V <sub>DD_IO</sub> or to ground. |  |  |  |

| D9, E8, C8,<br>E7  | 159, 163,<br>165, 167 | REF_FAIL0 - 3 | Failure Indication for DPLL References 0 to 3 (5 V-Tolerant Three-state Outputs) These output pins are used to indicate input reference failure when the device is in master mode. If REF0 fails, REF_FAIL0 will be driven high. If REF1 fails, REF_FAIL1 will be driven high. If REF2 fails, REF_FAIL2 will be driven high. If REF3 fails, REF_FAIL3 will be driven high. If the device is in slave mode, these pins are driven low, unless SLV_DPLLEN (bit 13) in the Control Register (CR) is set.                                                                                                                    |  |  |  |

| PBGA Pin<br>Number        | LQFP Pin<br>Number                 | Pin Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| G15, G14,<br>E15, F14     | 102, 106,<br>110, 112              | FPo0 - 3               | ST-BUS/GCI-Bus Frame Pulse Outputs 0 to 3 (5 V-Tolerant Three-state Outputs)  FPo0: 8 kHz frame pulse corresponding to the 4.096 MHz output clock of CKo0.  FPo1: 8 kHz frame pulse corresponding to the 8.192 MHz output clock of CKo1.  FPo2: 8kHz frame pulse corresponding to 16.384 MHz output clock of CKo2.  FPo3: Programmable 8kHz frame pulse corresponding to 4.096, 8.192, 16.384, or 32.768 MHz output clock of CKo3.  In Divided Slave modes, the frame pulse width of FPo0 - 3 cannot be narrower than the input frame pulse (FPi) width.                                                                        |

| H14, D11                  | 100, 104                           | FPo_OFF0 - 1           | Generated Offset Frame Pulse Outputs 0 to 1 (5 V-Tolerant Three-state Outputs) Individually programmable 8 kHz frame pulses, offset from the output frame boundary by a programmable number of channels.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F15                       | 108                                | FPo_OFF2<br>or<br>FPo5 | Generated Offset Frame Pulse Output 2 or 19.44 MHz Frame Pulse Output (5 V-Tolerant Three-state Output)  As FPo_OFF2, this is an individually programmable 8 kHz width frame pulse, offset from the output frame boundary by a programmable number of channels.  By programming the FP19EN (bit 10) of FPOFF2 register to high, this signal becomes FPo5, a non-offset frame pulse corresponding to the 19.44 MHz clock presented on CKo5. FPo5 is only available in Master mode or when the SLV_DPLLEN bit in the Control Register is set high while the device is in one of the slave modes.                                  |

| B7, C7, B5,<br>J6, D6, H5 | 170, 172,<br>174, 227,<br>176, 221 | CKo0 - 5               | ST-BUS/GCI-Bus Clock Outputs 0 to 5 (5 V-Tolerant Three-state Outputs)  CK00: 4.096 MHz output clock.  CK01: 8.192 MHz output clock.  CK02: 16.384 MHz output clock.  CK03: 4.096, 8.192, 16.384 or 32.768 MHz programmable output clock;  CK04: 1.544 or 2.048 MHz programmable output clock.  CK05: 19.44 MHz output clock.  See Section 6.0 on page 24 for details. In Divided Slave mode, the frequency of CK00 - 3 cannot be higher than input clock (CKi).  CK04 and CK05 are only available in Master mode or when the SLV_DPLLEN bit in the Control Register is set high while the device is in one of the slave modes. |

| PBGA Pin<br>Number | LQFP Pin<br>Number | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|--------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

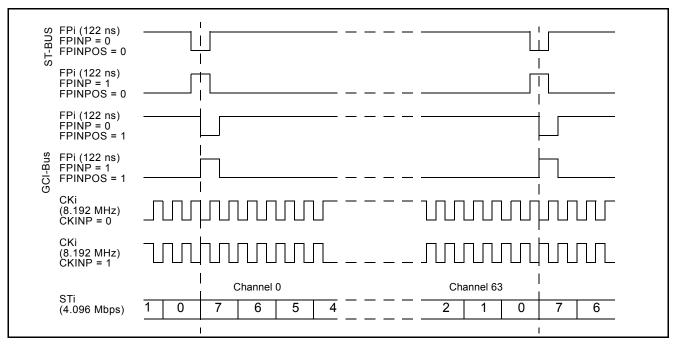

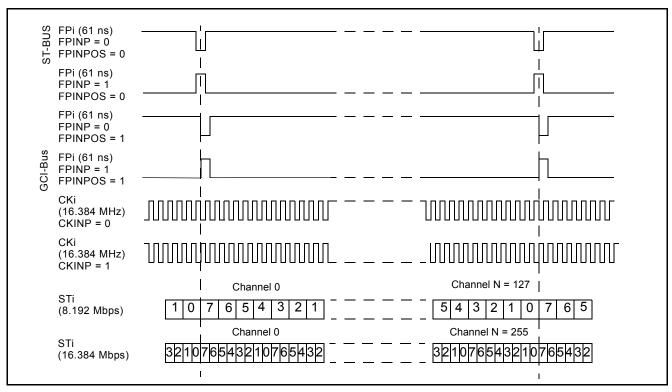

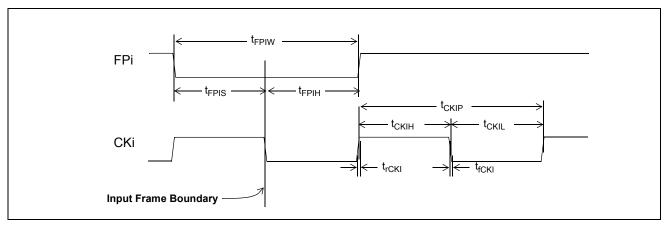

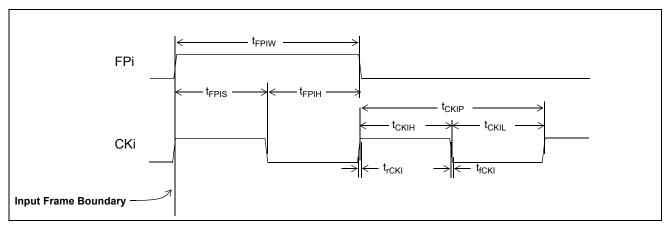

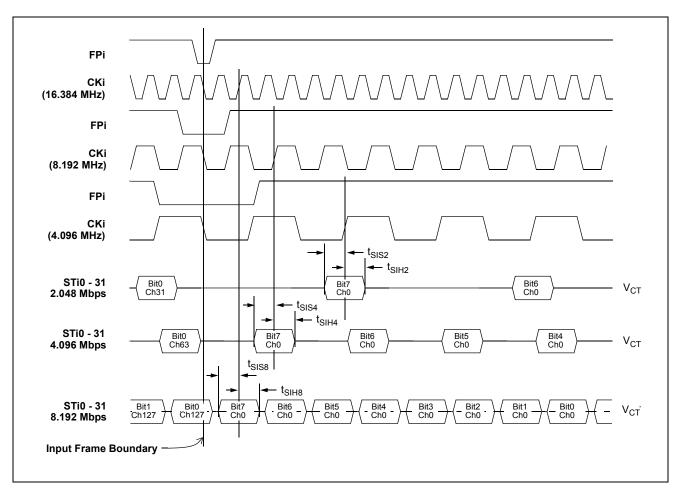

| B10                | 155                | FPi      | ST-BUS/GCI-Bus Frame Pulse Input (5 V-Tolerant Schmitt-Triggered Input)  This pin accepts the frame pulse which stays active for 61 ns, 122 ns or 244 ns at the frame boundary. The frame pulse frequency is 8 kHz.  The frame pulse associated with the highest input or output data rate must be applied to this pin when the device is operating in Divided Slave mode or Master mode. The exception is if the device is operating in Master mode with loopback (i.e., CKi_LP is set in the Control Register). In that case, this input must be tied high or low externally.  When the device is operating in Multiplied Slave mode, the frame pulse associated with the highest input data rate must be applied to this pin.  For all modes (except Master mode with loopback), if the data rate is 16.384 Mbps, a 61 ns wide frame pulse must be used.  By default, the device accepts a negative frame pulse in ST-BUS format, but it can accept a positive frame pulse instead if the FPINP bit is set high in the Control Register (CR). It can accept a GCI-formatted frame pulse by programming the FPINPOS bit in the Control Register (CR) to high. |

| B11                | 154                | CKi      | ST-BUS/GCI-Bus Clock Input (5 V-Tolerant Schmitt Triggered Input)  This pin accepts a 4.096, 8.192 or 16.384 MHz clock.  The clock frequency associated with twice the highest input or output data rate must be applied to this pin when the device is operating in either Divided Slave mode or Master mode. The exception is if the device is operating in Master mode with loopback (i.e., CKi_LP is set in the Control Register). In that case, this input must be tied high or low externally. The clock frequency associated with twice the highest input data rate must be applied to this pin when the device is operating in Multiplied Slave mode. In all modes of operation (except Master mode with loopback), when data is running at 16.384 Mbps, a 16.384 MHz clock must be used. By default, the clock falling edge defines the input frame boundary, but the device allows the clock rising edge to define the frame boundary by programming the CKINP bit in the Control Register (CR).                                                                                                                                                      |

| PBGA Pin<br>Number                                                                                                                                                                           | LQFP Pin<br>Number                                                                                                                                                                                          | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B6, C6, D5,<br>D4, B4, B3,<br>C5, C4, E3,<br>C2, B2, D2,<br>F3, F4, E2,<br>F2, E1, D1,<br>G1, F1, J1,<br>H1, K1, L1,<br>A7, A5, A6,<br>A4, A3, A2,<br>C1, B1                                 | 179, 180,<br>181, 182,<br>183, 184,<br>185, 187,<br>198, 200,<br>201, 202,<br>203, 204,<br>205, 206,<br>243, 244,<br>245, 246,<br>247, 248,<br>250, 252,<br>189, 190,<br>191, 192,<br>193, 194,<br>196, 197 | STi0 -31    | Serial Input Streams 0 to 31 (5 V-Tolerant Inputs with Enabled Internal Pull-downs)  The data rate of each input stream can be selected independently using the Stream Input Control Registers (SICR[n]). In the 2.048 Mbps mode, these pins accept serial TDM data streams at 2.048 Mbps with 32 channels per frame. In the 4.096 Mbps mode, these pins accept serial TDM data streams at 4.096 Mbps with 64 channels per frame. In the 8.192 Mbps mode, these pins accept serial TDM data streams at 8.192 Mbps with 128 channels per frame. In the 16.384 Mbps mode, these pins accept TDM data streams at 16.384 Mbps with 256 channels per frame.                                                                                                                                                                                  |

| N4, P4, R4,<br>P5, N13,<br>P11, R14,<br>R15, M15,<br>L15, L13,<br>L14, E14,<br>D13, D15,<br>C15, D16,<br>E16, C16,<br>B16, A13,<br>A12, A10,<br>A11, N1,<br>M1, P1, R1,<br>T2, T3, T5,<br>T4 | 6, 7, 9,<br>10, 51,<br>52, 53,<br>54, 70,<br>72, 73,<br>74, 115,<br>116, 117,<br>118, 125,<br>126, 127,<br>128, 129,<br>130, 131,<br>132, 253,<br>254, 255,<br>256, 1, 2,<br>3, 4                           | STio0 - 31  | Serial Output Streams 0 to 31 (5 V-Tolerant Slew-Rate-Limited Three-state I/Os with Enabled Internal Pull-downs)  The data rate of each output stream can be selected independently using the Stream Output Control Registers (SOCR[n]). In the 2.048 Mbps mode, these pins output serial TDM data streams at 2.048 Mbps with 32 channels per frame. In the 4.096 Mbps mode, these pins output serial TDM data streams at 4.096 Mbps with 64 channels per frame. In the 8.192 Mbps mode, these pins output serial TDM data streams at 8.192 Mbps with 128 channels per frame. In the 16.384 Mbps mode, these pins output serial TDM data streams at 16.384 Mbps with 256 channels per frame.  These output streams can be used as bi-directionals by programming BDH (bit 7) and BDL (bit 6) of Internal Mode Selection (IMS) register. |

| R3, P6, R5,<br>N5, P12,<br>N15, P13,<br>P15, N16,<br>M16, L16,<br>K16, H16,<br>J16, G16,<br>F16                                                                                              | 11, 12,<br>13, 14,<br>55, 56,<br>58, 59,<br>75, 76,<br>77, 78,<br>119, 120,<br>122, 124                                                                                                                     | STOHZ0 - 15 | Serial Output Streams High Impedance Control 0 to 15 (5 V-Tolerant Slew-Rate-Limited Three-state Outputs) These pins are used to enable (or disable) external three-state buffers. When an output channel is in the high impedance state, the STOHZ drives high for the duration of the corresponding output channel. When the STio channel is active, the STOHZ drives low for the duration of the corresponding output channel. STOHZ outputs are available for STio0 - 15 only.                                                                                                                                                                                                                                                                                                                                                      |

| PBGA Pin<br>Number                                                                     | LQFP Pin<br>Number                                                                  | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B15                                                                                    | 141                                                                                 | ODE      | Output Drive Enable (5 V-Tolerant Input with Internal Pull-up) This is the output enable control for STio0 - 31 and the output-driven-high control for STOHZ0 - 15. When it is high, STio0 - 31 and STOHZ0 - 15 are enabled. When it is low, STio0 - 31 are tristated and STOHZ0 - 15 are driven high.                                                                                                                                              |  |

| M4, N6, R6,<br>P7, R7, N7,<br>M8, N8, P8,<br>R8, M9, N9,<br>R9, N10, P9,<br>R10        | 16, 18,<br>20, 22,<br>23, 24,<br>25, 26,<br>27, 28,<br>30, 32,<br>34, 36,<br>37, 38 | D0 - 15  | Data Bus 0 to 15 (5 V-Tolerant Slew-Rate-Limited Three-state I/Os) These pins form the 16-bit data bus of the microprocessor port.                                                                                                                                                                                                                                                                                                                  |  |

| N12                                                                                    | 44                                                                                  | DTA_RDY  | Data Transfer Acknowledgment_Ready (5 V-Tolerant Three-state Output)  This active low output indicates that a data bus transfer is complete for the Motorola interface. For the Intel interface, it indicates a transfer is completed when this pin goes from low to high.  An external pull-up resistor MUST hold this pin at HIGH level for the Motorola mode. An external pull-down resistor MUST hold this pin at LOW level for the Intel mode. |  |

| R11                                                                                    | 40                                                                                  | CS       | Chip Select (5V-Tolerant Input) Active low input used by the Motorola or Intel microprocessor to enable the microprocessor port access.                                                                                                                                                                                                                                                                                                             |  |

| N11                                                                                    | 39                                                                                  | R/W_WR   | Read/Write_Write (5 V-Tolerant Input) This input controls the direction of the data bus lines (D0 - 15) during a microprocessor access. For the Motorola interface, this pin is set high and low for the read and write access respectively. For the Intel interface, a write access is indicated when this pin goes low.                                                                                                                           |  |

| R12                                                                                    | 42                                                                                  | DS_RD    | Data Strobe_Read (5 V-Tolerant Input)  This active low input works in conjunction with CS to enable the microprocessor port read and write operations for the Motorola interface. A read access is indicated when it goes low for the Intel interface.                                                                                                                                                                                              |  |

| K13, K15,<br>K14, J11,<br>J12, J13,<br>J15, H11,<br>J14, H12,<br>H13, H15,<br>G12, G13 | 82, 84,<br>86, 87,<br>88, 89,<br>90, 91,<br>92, 93,<br>94, 96,<br>98, 99            | A0 - 13  | Address 0 to 13 (5 V-Tolerant Inputs) These pins form the 14-bit address bus to the internal memories and registers.                                                                                                                                                                                                                                                                                                                                |  |

| PBGA Pin<br>Number | LQFP Pin<br>Number | Pin Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|--------------------|--------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M13                | 41                 | MOT_INTEL | Motorola_Intel (5 V-Tolerant Input with Internal Pull-up) This pin selects the Motorola or Intel microprocessor interface to be connected to the device. When this pin is unconnected or connected to high, Motorola interface is assumed. When this pin connected to ground, Intel interface should be used.                                                                                                                                                                                                                                                                                                                                                   |  |

| P10                | 43                 | ĪRQ       | Interrupt (5 V-Tolerant Three-state Output) This programmable active low output indicates that the internal operating status of the DPLL has changed. An external pull-up resistor MUST hold this pin at HIGH level.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| G2                 | 211                | RESET     | Device Reset (5 V-Tolerant Input with Internal Pull-up) This input (active LOW) puts the device in its reset state that disables the STio0 - 31 drivers and drives the STOHZ0 - 15 outputs to high. It also preloads registers with default values and clears all internal counters. To ensure proper reset action, the reset pin must be low for longer than 1 $\mu$ s. Upon releasing the reset signal to the device, the first microprocessor access cannot take place for at least 600 $\mu$ s due to the time required to stabilize the device and the crystal oscillator from the power-down state. Refer to Section Section 17.2 on page 48 for details. |  |

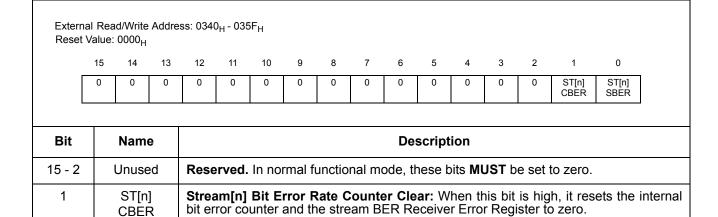

#### 3.0 Device Overview