# OXFORD SEMICONDUCTOR

# **OX16PCI958** DATA SHEET

# Octal UART with PCI Interface

#### **FEATURES**

- Efficient 32-bit, 33¹/₃ MHz multi-function, target-only PCI controller, compliant to PCI Local Bus Specification 3.0 & PCI Power Management Specification 1.1

- Eight UARTs fully software compatible with 16C550type devices

- Compatible with existing 16C550/450 device drivers

- PCI 2.1, 2.2, 2.3 & 3.0 compliant

- Supports both 5.0-V & 3.3-V PCI signalling

- 32-byte deep FIFO per transmitter & receiver

- Baud rates up to 4.125 Mega-baud (using a 16.5 MHz input clock).

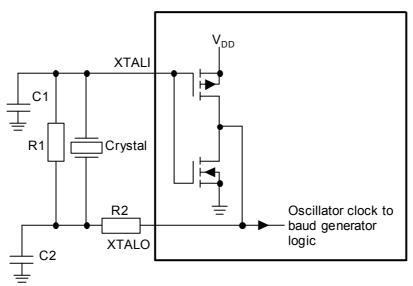

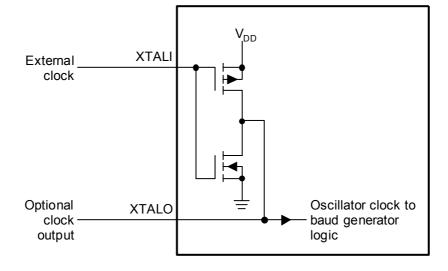

- Clock can be provided from crystal oscillator or external clock source

- Automated out-of-band flow control using CTS#/RTS#

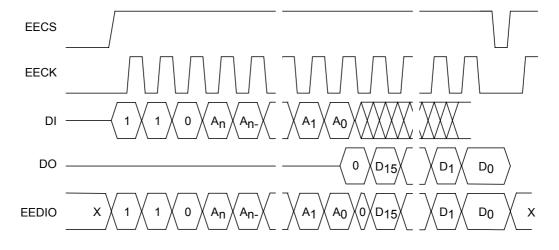

- Configuration data is held in a small, low-cost serial Microwire™ compatible EEPROM

- Driver-facilitated DSR/DTR & Xon/Xoff handshaking

- 5-,6-,7- & 8-bit data framing

- 1, 1.5 or 2 stop bits

- UART enhancements:

- Clock prescaler allows more baud rate options

- Readable FIFO levels & tuneable trigger levels improve device driver performance

- Programmable "synchronization factor" allows baud rates up to fclock/4

- Extensions to standard register set are implemented in a safe, easy-to-use way

- Low-power design with separate power management control

- Operating temp. range : 0°C—70°C

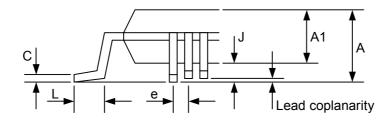

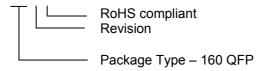

- 160-pin QFP package

- Operation via IO or memory mapping

- Support for multiple wake-up events

#### **DESCRIPTION**

The OX16PCI958 contains eight UARTs (Universal Asynchronous Receiver-Transmitters) and a host interface suitable for direct connection to a PCI bus. Once installed and configured by the host OS, it provides an eight-byte programming interface to each UART. The UARTs are fully software-compatible with 16C550 devices. The device can be configured to fit the requirements of RS232 or RS422 applications.

The UARTs convert between RS232-format serial data on separate transmit and receive lines, and byte-wide I/O writes and reads on the host interface. Malformed incoming serial data is flagged along with the data in the receive FIFO. The state of the UART can be found at any time by reading status registers, and modem control (handshaking output) lines can be individually controlled.

Although polled-mode operation is possible, the UART will usually be operated on a host-interrupt basis. The interrupt system is designed to allow efficient handling of

interrupt service requests from the UART, for example by using the prioritised interrupt identification register, readable FIFO levels, and tuneable FIFO trigger levels.

The internal transmitter and receiver logic runs at a programmable synchronisation factor of 4x, 8x, or 16x the serial baud rate. This internal clock is generated by dividing a reference clock by an integer divisor from 1 to  $(2^{16}-1)$ . In this way the UART can accommodate a serial rate of up to 4 125 000 baud (using a 16.5 MHz input clock).

The OX16PCI958 provides a host interface that can be directly connected to a PCI bus. It responds to configuration accesses, and once configured it also responds to I/O and memory accesses for control of the UART. The data for configuration space is read from a small external serial EEPROM at start-up, together with information on how the OX16PCI958 should be set up.

# **C**ONTENTS

| Features                                  | 1  |

|-------------------------------------------|----|

| Description                               | 1  |

| Contents                                  | 2  |

| 1. Block Diagram                          | 3  |

| 2. Pin Information—160-pin QFP            | 4  |

| 2.1. Pinout                               | 4  |

| 2.2. Pin Descriptions                     | 5  |

| 3. PCI interface                          | 7  |

| 3.1. Internal Address Map                 | 7  |

| 3.2. Configuration & Control Registers    | 9  |

| 3.3. PCI Configuration Space Registers    | 11 |

| 3.4. PCI Set-up Registers                 | 15 |

| 4. UART function                          | 16 |

| 4.1. Programming                          | 16 |

| 4.2. Accessible Registers                 | 16 |

| 4.3. Serial Data Format                   | 21 |

| 4.4. Transmitter/Receiver Section         | 21 |

| 4.5. FIFO Interrupt Mode Operation        | 24 |

| 4.6. FIFO Polled Mode Operation           | 25 |

| 4.7. Loopback Mode                        | 26 |

| 4.8. Auto Flow Control                    | 27 |

| 4.8.1. Auto-RTS                           | 28 |

| 4.8.2. Auto-CTS                           | 28 |

| 4.8.3. Enabling Auto-RTS & Auto-CTS       | 28 |

| 4.9. Chip Type Identification             | 29 |

| 4.10. SISR Function                       | 30 |

| 5. EEPROM                                 | 31 |

| 5.1. The EEPROM Reader                    | 31 |

| 5.2. EEPROM Data Format                   | 32 |

| 5.3. Example EEPROM Data                  | 33 |

| 6. Clock/Oscillator Pins                  | 35 |

| 7. Operating conditions                   | 36 |

| 7.1. Recommended Operating Conditions     | 36 |

| 7.2. DC Characteristics                   | 36 |

| 8. I/O electrical & timing specifications | 37 |

| 9. Package information                    | 43 |

| 10. Glossary                              | 44 |

| 11. Ordering information                  | 45 |

| 12. Contact Details                       | 46 |

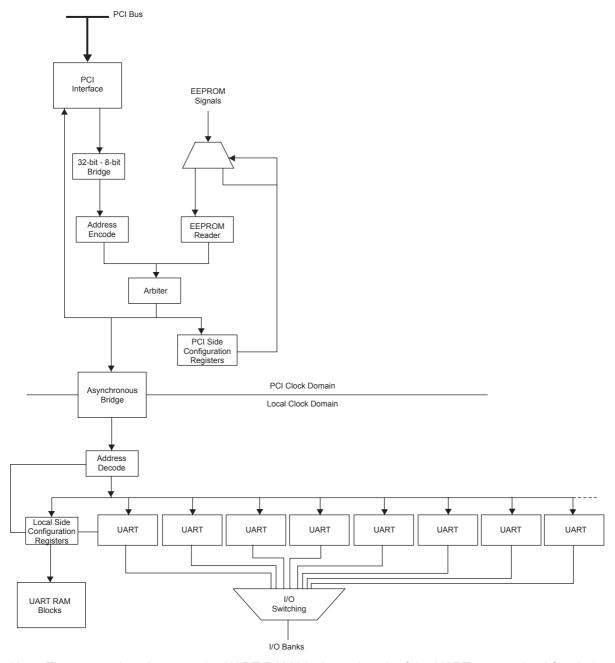

# 1. BLOCK DIAGRAM

Note: The connections between the UART RAM blocks and each of the UARTs are omitted for clarity.

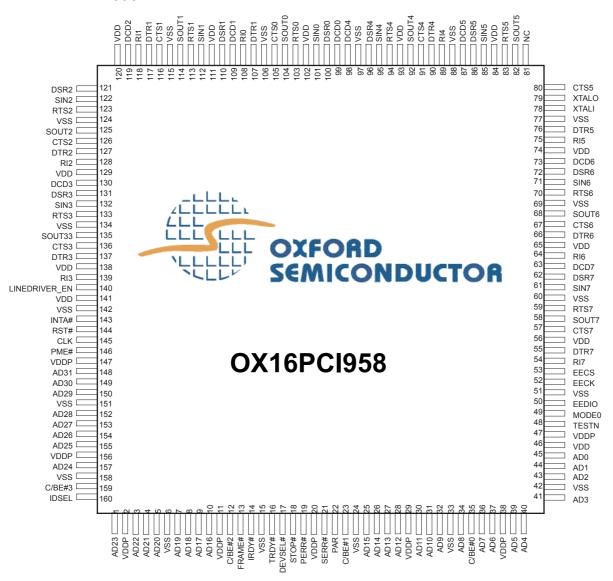

## 2. PIN INFORMATION—160-PIN QFP

#### 2.1. Pinout

# 2.2. Pin Descriptions

Table 1 lists the pin allocations, names and describes them.

**Table 1 Pin Descriptions**

| Name      | Pin                                                                                                                            | Dir        | Description        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|

|           |                                                                                                                                |            | PCI bus signals    |

| PAR       | 22                                                                                                                             | Ю          |                    |

| CLK       | 145                                                                                                                            | ı          |                    |

| RST#      | 144                                                                                                                            | ı          |                    |

| FRAME#    | 13                                                                                                                             | ı          |                    |

| RDY#      | 14                                                                                                                             | I          |                    |

| TRDY#     | 16                                                                                                                             | ОТ         |                    |

| DEVSEL#   | 17                                                                                                                             | ОТ         |                    |

| STOP#     | 18                                                                                                                             | ОТ         |                    |

| PERR#     | 19                                                                                                                             | ОТ         |                    |

| SERR#     | 21                                                                                                                             | ОТ         |                    |

| NTA#      | 143                                                                                                                            | ОТ         |                    |

| PME#      | 146                                                                                                                            | ОТ         |                    |

| DSEL      | 160                                                                                                                            | I          |                    |

| AD[31:0]  | 148, 149,150, 152, 153, 154, 155, 157, 1, 3, 4, 5, 7, 8, 9, 10, 25, 26, 27, 28, 30, 31, 32, 34, 36, 37, 39, 40, 41, 43, 44, 45 | Ю          |                    |

| C/BE#3    | 159                                                                                                                            | ı          |                    |

| C/BE#2    | 12                                                                                                                             | I          |                    |

| C/BE#1    | 23                                                                                                                             | I          |                    |

| C/BE#0    | 35                                                                                                                             | I          |                    |

|           |                                                                                                                                |            | Chip configuration |

| EECS      | 53                                                                                                                             | 0          |                    |

| EECK      | 52                                                                                                                             | 0          |                    |

| EEDIO     | 50                                                                                                                             | Ю          |                    |

|           |                                                                                                                                |            | Local clock        |

| XTALI     | 78                                                                                                                             | I          |                    |

| XTALO     | 79                                                                                                                             | 0          |                    |

|           |                                                                                                                                |            | Local side         |

| LD_EN     | 140                                                                                                                            | 0          |                    |

|           |                                                                                                                                |            | Power and ground   |

| VSS (GND) | 6, 15, 24, 33, 42, 49, 51, 60, 69, 77, 88, 97, 106, 115, 124, 1                                                                | 34, 142, 1 | 51, 158            |

| /DD (5V)  | 56, 65, 74, 84, 93, 102, 111, 120, 129, 138                                                                                    |            |                    |

| /DDP      | 2, 11, 20, 29, 38, 46, 47, 141, 147, 156                                                                                       |            |                    |

The VDDP pins provide power to the PCI I/O buffers, and must be connected to the  $+V_{\text{I/O}}$  pins on the PCI connector.

Table 2 &

Table 3 list pin allocations for the local I/O banks.

Table 2 Local I/O Bank 0—3 Pin Allocations

| IO# | Bank | Pin | Dir | Name |

|-----|------|-----|-----|------|

| 0   | 0    | 99  | I   | DCD  |

| 1   |      | 100 | 1   | DSR  |

| 2   |      | 101 | 1   | SIN  |

| 3   |      | 103 | 0   | RTS  |

| 4   |      | 104 | 0   | SOUT |

| 5   |      | 105 | 1   | CTS  |

| 6   |      | 107 | 0   | DTR  |

| 7   |      | 108 | I   | RI   |

| 0   | 1    | 109 | I   | DCD  |

| 1   |      | 110 | 1   | DSR  |

| 2   |      | 112 | 1   | SIN  |

| 3   |      | 113 | 0   | RTS  |

| 4   |      | 114 | 0   | SOUT |

| 5   |      | 116 | 1   | CTS  |

| 6   |      | 117 | 0   | DTR  |

| 7   |      | 118 | I   | RI   |

| 0   | 2    | 119 | 1   | DCD  |

| 1   |      | 121 | 1   | DSR  |

| 2   |      | 122 | 1   | SIN  |

| 3   |      | 123 | 0   | RTS  |

| 4   |      | 125 | 0   | SOUT |

| 5   |      | 126 | 1   | CTS  |

| 6   |      | 127 | 0   | DTR  |

| 7   |      | 128 | 1   | RI   |

| 0   | 3    | 130 | 1   | DCD  |

| 1   |      | 131 | 1   | DSR  |

| 2   |      | 132 | I   | SIN  |

| 3   |      | 133 | 0   | RTS  |

| 4   |      | 135 | 0   | SOUT |

| 5   |      | 136 | I   | CTS  |

| 6   |      | 137 | 0   | DTR  |

| 7   |      | 139 | I   | RI   |

Table 3 Local I/O Bank 4—7 Pin Allocations

| IO# | Bank | Pin | Dir | Name |

|-----|------|-----|-----|------|

| 0   | 4    | 98  | 1   | DCD  |

| 1   |      | 96  | I   | DSR  |

| 2   |      | 95  | 1   | SIN  |

| 3   |      | 94  | 0   | RTS  |

| 4   |      | 92  | 0   | SOUT |

| 5   |      | 91  | 1   | CTS  |

| 6   |      | 90  | 0   | DTR  |

| 7   |      | 89  | I   | RI   |

| 0   | 5    | 87  | I   | DCD  |

| 1   |      | 86  | 1   | DSR  |

| 2   |      | 85  | I   | SIN  |

| 3   |      | 83  | 0   | RTS  |

| 4   |      | 82  | 0   | SOUT |

| 5   |      | 80  | I   | CTS  |

| 6   |      | 76  | 0   | DTR  |

| 7   |      | 75  | Ι   | RI   |

| 0   | 6    | 73  | 1   | DCD  |

| 1   |      | 72  | 1   | DSR  |

| 2   |      | 71  | 1   | SIN  |

| 3   |      | 70  | 0   | RTS  |

| 4   |      | 68  | 0   | SOUT |

| 5   |      | 67  | I   | CTS  |

| 6   |      | 66  | 0   | DTR  |

| 7   |      | 64  | I   | RI   |

| 0   | 7    | 63  | I   | DCD  |

| 1   |      | 62  | I   | DSR  |

| 2   |      | 61  | I   | SIN  |

| 3   |      | 59  | 0   | RTS  |

| 4   |      | 58  | 0   | SOUT |

| 5   |      | 57  | I   | CTS  |

| 6   |      | 55  | 0   | DTR  |

| 7   |      | 54  | I   | RI   |

#### 3. PCI INTERFACE

The PCI interface conforms to revisions 2.1, 2.2, 2.3 and 3.0 of the PCI Specification, and version 1.1 of the PCI Power Management Specification.

Six base address registers are implemented in the OXPCI958:

- BAR0—128-byte memory-mapped region

- BAR1—128-byte I/O-mapped region

- BAR2—64-byte I/O-mapped region

- BAR3—16-byte I/O-mapped region

- BAR4—64-byte memory-mapped region

- BAR5—16-byte memory-mapped region

All memory regions are in 32-bit address space, and are marked as non-prefetchable.

#### 3.1. Internal Address Map

The internal address map is referenced by the EEPROM to configure the UARTs. Table 4 shows how PCI accesses are mapped to internal addresses:

| PCI side |                          | PCI bridge configuration         | 00h to 2Fh |

|----------|--------------------------|----------------------------------|------------|

|          |                          | EEPROM control, power management | 30h to 3Fh |

| BAR0, 1  | local side configuration | UART, SISR                       | 40h to 7Fh |

| BAR2, 4  | local functions          | UARTs                            | 80h to BFh |

| BAR3, 5  | local functions          | SISR                             | C0h to CFh |

**Table 4 PCI Address Mapping**

#### Notes:

- Addresses in the range 40h-7Fh are aliased with a period of 32, i.e., address bit 5 is not decoded

in this range

- Addresses in the range C0h-FFh are aliased with a period of 16, i.e., address bits 5:4 are not decoded in this range. For example, if BAR4 is configured as C8000400h, a memory access at C8000413h, which is BAR4+13h, would access internal address 80h+13h = 93h

- The serial EEPROM reader can access any internal address

Table 5 lists the PCI register offsets.

**Table 5 Register Offsets**

| BAR     | Internal address | Use                                               |

|---------|------------------|---------------------------------------------------|

| BAR0, 1 | 00h – 19h        | PCI setup registers, as described in section 3.4. |

|         | 30h              | EEPROM-control register                           |

|         | 31h              | Power-management control register                 |

|         | 34h              | UART interrupt status                             |

|         | 35h              |                                                   |

|         | 40h              | UART-enable register                              |

|         | 41h              | UART IO bank switching/rotation                   |

|         | 42h              | SISR enable register                              |

|         | 4Ch              | UART configuration                                |

|         | 50h              | Global UART clock pre-divider                     |

| BAR2,4  | 80h-87h          | UART 0 registers 0-7                              |

|         | 88h-8Fh          | UART 1 registers 0-7                              |

|         | 90h-97h          | UART 2 registers 0-7                              |

|         | 98h-9Fh          | UART 3 registers 0-7                              |

|         | A0h-A7h          | UART 4 registers 0-7                              |

|         | A8h-AFh          | UART 5 registers 0-7                              |

|         | B0h-B7h          | UART 6 registers 0-7                              |

|         | B8h-BFh          | UART 7 registers 0-7                              |

| BAR3,5  | C0h              | SISR, if SISR enabled                             |

|         | C0h-C1h          | UART 0 registers 8-9, if SISR not enabled         |

|         | C2h-C3h          | UART 1 registers 8-9                              |

|         | C4h-C5h          | UART 2 registers 8-9                              |

|         | C6h-C7h          | UART 3 registers 8-9                              |

|         | C8h-C9h          | UART 4 registers 8-9                              |

|         | CAh-CBh          | UART 5 registers 8-9                              |

|         | CCh-CDh          | UART 6 registers 8-9                              |

|         | CEh-CFh          | UART 7 registers 8-9                              |

|         | other            | RFU                                               |

#### Notes:

- Writes to undefined internal addresses are ignored, and reads from undefined internal addresses return zero

- For shared address ranges, the SISR takes priority over the UARTs

## 3.2. Configuration & Control Registers

Table 6 summarizes the configuration and control registers for quick reference.

**Table 6 Configuration & Control Register Summary**

| Α   | use                                      | D7    | D6         | D5      | D4               | D3     | D2    | D1                        | D0                |

|-----|------------------------------------------|-------|------------|---------|------------------|--------|-------|---------------------------|-------------------|

| 30h | EEPROM-<br>control register              | EET2  | EET1       | RFU     | EEDIO<br>data in | EECS   | EECK  | EEDIO<br>output<br>enable | EEDIO<br>data out |

| 31h | Power-<br>management<br>control register | RFU   |            | PM_DRI\ | /ER              | PM_LCL | <     | PM_OSC                    |                   |

| 34h | UART interrupt status (RO)               | U7INT | U6INT      | U5INT   | U4INT            | U3INT  | U2INT | U1INT                     | U0INT             |

| 40h | UART-enable register                     | U7EN  | U6EN       | U5EN    | U4EN             | U3EN   | U2EN  | U1EN                      | U0EN              |

| 42h | SISR enable                              | SEN   |            |         |                  | RFU    |       |                           |                   |

| 4Ch | UART configuration                       | RI    | RFU 1b RFU |         |                  |        |       |                           |                   |

| 50h | Global pre-<br>divider                   | RFU1  | RFU1       | GCS1    | RFU1             | RFU    | GCS0  | RFU1                      | RFU               |

### **EEPROM-Control Register**

The OX16PCI958 automatically takes control of the EECS, EECK and EEDIO pins after a deassertion of the host bus RESET signal, in order to read in configuration data. Afterwards, the signals may be controlled though accesses to this register.

| Field (Bits)       | Description                                                                                                                                                       |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EET2 (7)           | High—at least 70 PCI clock cycles have occurred since the register was last written.                                                                              |

|                    | Cleared when the register is written. Set to the value of EET1 every 70th PCI clock cycle. This may be useful for ensuring that EEPROM timing constraints are met |

| EET1 (6)           | Cleared when the register is written. Set every 70th PCI clock cycle                                                                                              |

| EEDIO data in (4)  | Returns the current logic level on the EEDIO pin.                                                                                                                 |

| EECS (3)           | Controls EECS output.                                                                                                                                             |

| EECK (2)           | Controls EECK output                                                                                                                                              |

| EEDIO output       | 1—the value last written to bit 0 is driven on the EEDIO pin                                                                                                      |

| enable (1)         | 0—EEDIO pin is tri-stated                                                                                                                                         |

| EEDIO data out (0) | Controls the logic level driven onto EEDIO when bit 1 is set.                                                                                                     |

This register is set to 00h on a PCI reset.

#### Power-Management Control Register

Each two-bit group represents a powermanagement level range, as shown in Table 7, defining whether an element is disabled, which is shown in Table 8.

**Table 7 Power Management Group**

| Field (Bits) | Control Measure                |

|--------------|--------------------------------|

| PM_DRIVER    | driver_en output deasserted    |

| PM_LCLK      | Local-side clock gated off     |

| PM OSC       | Local-side oscillator disabled |

**Table 8 Element Disabling**

| Value | Description             |

|-------|-------------------------|

| 0.0   | Never disabled          |

| 0.1   | Disabled in D1, D2 & D3 |

| 10    | Disabled in D2 and D3   |

| 11    | Disabled in D3 only     |

This register is set to 00h on a PCI reset.

#### **UART Interrupt State**

Each bit in this read-only register reports the interrupt status of the corresponding internal UART.

#### **UART Enable**

Each bit in this register enables the corresponding internal UART to be accessed on the internal bus, by either the PCI interface or the EEPROM reader.

#### SISR Enable

Bit 7 must be set to enable access to the shared interrupt status register (SISR).

This register is set to 80h on a PCI reset.

#### **UART Configuration**

Bit 5 must be set to binary 1 to ensure correct operation of the UART

#### Global UART Clock Pre-Divider

This register sets a pre-division value for all the internal UARTs.

Bit 5—One of the clock pre-division factors, see Table 9

Bit 2—One of the clock pre-division factors, see Table 9

After a reset, this register is set to F6h, giving a divide-by-8 clock setting for all UARTs. For the standard 14.7456 MHz external crystal, this gives a 1.8432 MHz effective clock to the UARTs.

For backwards compatibility, write only one of the four values in Table 9 to bits 5 and 2:

**Table 9 Clock Pre-Division Values**

| Value | Divisor |

|-------|---------|

| F6h   | 8       |

| F2h   | 4       |

| D6h   | 2       |

| D2h   | 1       |

The above register settings are recommended for backwards compatibility, but Table 10 shows how the actual control logic operates.

**Table 10 Clock Division Logic**

| GCS1 | GCS0 | Division |

|------|------|----------|

| 1    | 1    | 8        |

| 1    | 0    | 4        |

| 0    | 1    | 2        |

| 0    | 0    | 1        |

#### 3.3. PCI Configuration Space Registers

The PCI interface presents a type 0 configuration register set in configuration space, with the standard extension for power management. Table 11 summarizes the PCI configuration space registers.

| Address | Configuration register              |          |     |                                      |             |                 |           |

|---------|-------------------------------------|----------|-----|--------------------------------------|-------------|-----------------|-----------|

| Offset  | 31 24                               | 23       | 16  | 15                                   | 8           | 7               | 0         |

| 00h     | Device ID                           |          |     | Vendor IE                            | )           |                 |           |

| 04h     | Status                              |          |     | Comman                               | Command     |                 |           |

| 08h     | Class code                          |          |     |                                      | Revision ID |                 |           |

| 0Ch     | BIST                                | Header t | уре | Latency ti                           | mer         | Cache           | line size |

| 10h     | Base address register 0 (E          | BAR0)    |     |                                      |             |                 |           |

| 14h     | Base address register 1 (BAR1)      |          |     |                                      |             |                 |           |

| 18h     | Base address register 2 (BAR2)      |          |     |                                      |             |                 |           |

| 1Ch     | Base address register 3 (BAR3)      |          |     |                                      |             |                 |           |

| 20h     | Base address register 4 (BAR4)      |          |     |                                      |             |                 |           |

| 24h     | Base address register 5 (BAR5)      |          |     |                                      |             |                 |           |

| 28h     | Cardbus CIS pointer                 |          |     |                                      |             |                 |           |

| 2Ch     | Subsystem device ID                 |          |     | Subsystem vendor ID                  |             |                 |           |

| 30h     | Expansion ROM base address register |          |     |                                      |             |                 |           |

| 34h     | RFU                                 |          |     | Capabilities pointer                 |             | ilities pointer |           |

| 38h     | RFU                                 |          |     |                                      |             |                 |           |

| 3Ch     | Max_lat                             | Min_gnt  |     | Interrupt                            | oin         | Interru         | pt line   |

| 40h     | Power management capabilities (PMC) |          |     | Next Ptr (always 0) Cap_ID (always 0 |             | D (always 0)    |           |

| 44h     | PM_Data PMCSR_BSE                   |          |     | PMC Control/Status register (PMCSR)  |             |                 | SR)       |

**Table 11 PCI Configuration Space Registers**

### **Device ID Register**

This register is read-only via configuration accesses, and returns the current value of the DID register (see section 3.4 for details of this and other PCI set-up registers).

#### Vendor ID Register

This register is read-only via configuration accesses, and returns the current value of the VID register.

#### Status Register

This register records information on the PCI interface state, as described in the PCI specification.

Write 1 to bits 11, 14 and 15 to clear them, all others are read-only.

|      | 1                                                                                                                                                                                                                                               |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits | Description                                                                                                                                                                                                                                     |

| 15   | 1—parity error, even if parity error handling is disabled by bit 6 in the Command register                                                                                                                                                      |

| 14   | Set whenever the device asserts SERR#.                                                                                                                                                                                                          |

| 13   | 0                                                                                                                                                                                                                                               |

| 12   | 0                                                                                                                                                                                                                                               |

| 11   | Set whenever the device terminates a transaction with Target-Abort.                                                                                                                                                                             |

| 10:9 | Device select timing. Target access timing of the function via the DEVSEL# output. This device is a medium speed target device (01b)                                                                                                            |

| 8    | 0                                                                                                                                                                                                                                               |

| 7    | 0                                                                                                                                                                                                                                               |

| 5    | 0                                                                                                                                                                                                                                               |

| 4    | 1                                                                                                                                                                                                                                               |

| 3    | Reflects the interrupt state in the device/function. INTA# is only asserted when the Interrupt Disable bit in Command is 0 & this Interrupt Status bit is a 1. Setting the Interrupt Disable bit to a 1 has no effect on the state of this bit. |

#### **Command Register**

This register enables certain features of the PCI interface.

| Bits | Description                                                            |  |

|------|------------------------------------------------------------------------|--|

| 10   | 1—disables INTA# assertion                                             |  |

|      | 0—enables INTA# assertion                                              |  |

|      | After RST# is 0                                                        |  |

| 9    | 0                                                                      |  |

| 8    | 1—enables. the function to report address parity errors via SERR#      |  |

| 7    | 0                                                                      |  |

| 6    | 1—enables the function to report parity errors via PERR#               |  |

| 5    | 0                                                                      |  |

| 4    | 0                                                                      |  |

| 3    | 0                                                                      |  |

| 2    | 0                                                                      |  |

| 1    | Controls the response to memory space accesses.                        |  |

|      | 1—allows the device respond to the PCI bus memory accesses as a target |  |

| 0    | Controls the response to I/O accesses.                                 |  |

|      | 1—allows the device respond to the PCI bus I/O accesses as a target    |  |

#### Class-Code Register

This register is read-only via configuration accesses, and returns the current value of the PCC register.

#### Revision ID Register

This register is read-only via configuration accesses, and returns the current value of the REV register.

#### **BIST Register**

This byte always returns 00h, and writes to the byte are ignored, as there is no BIST function.

#### Header Type

This byte always returns 00h, indicating a type 0 header and a single-function device. Writes to the byte are ignored.

#### Latency Timer

Read-only register always returns 00h. (Not relevant for target-only PCI devices).

#### Cache Line Size

This register is read-only and always returns 00h. (The device does not support cache line wrap mode)

#### Base Address Register 0

This register sets the PCI base address in memory space for access to local configuration registers. The register has bits 31-7 writable, and the remainder of the bits are always 0. This forms a request for 128 bytes of memory space with a 32-bit address, marked as non-prefetchable. Accesses made to the memory range defined by this BAR map to internal configuration registers at internal addresses 00h-07h.

#### Base Address Register 1

This register sets the PCI base address in I/O space for access to local configuration registers. The register has bits 31:7 writable; the remainder are always 01h. This forms a request for 128 bytes of I/O space. Accesses made to the I/O range defined by this BAR map to internal configuration registers at internal addresses 00h-07h.

#### Base Address Register 2

This base address register is for a mapping of 64 bytes in I/O space. Accesses made to the I/O range defined by this BAR map to internal UARTs at internal addresses 80h-BFh.

#### Base Address Register 3

This base address register is for a mapping of 16 bytes in I/O space. Accesses made to the I/O range defined by this BAR map to unused internal addresses C0h-CFh.

#### Base Address Register 4

This base address register is for a mapping of 64 bytes in 32-bit memory space (non-prefetchable memory). Accesses made to the memory range defined by this BAR map to internal UARTs at internal addresses 80h-BFh.

#### Base Address Register 5

This base address register is for a mapping of 16 bytes in 32-bit memory space (non-prefetchable memory). Accesses made to the memory range defined by this BAR map to internal addresses C0h-CFh.

#### Cardbus CIS Pointer

Hard-wired to zero, as this device is not for use in CardBus applications.

#### Subsystem Device ID Register

This register is read-only via configuration accesses, and returns the current value of the SDID register.

#### Subsystem Vendor ID register

This register is read-only via configuration accesses, and returns the current value of the SVID register.

#### Expansion ROM Base Address Register

Hard-wired to zero.

#### **Capabilities Pointer**

This register is read-only and always returns 40h, as this is where the power management registers are located.

#### Max\_lat Register

Read-only register which always returns 00h. (Not relevant for target-only PCI devices)

#### Min\_gnt Register

Read-only register which always returns 00h. (Not relevant for target-only PCI devices)

#### Interrupt Pin Register

This register is read-only via configuration accesses, but may be set to either 00h or 01h using local-register access via BAR0, BAR1 or EEPROM configuration. It is set to 01h following a PCI reset.

#### Interrupt Line Register

This register is read-write accessible via configuration accesses. It is set to 00h following a PCI reset.

#### **Power-Management Registers**

The Power Management Capabilities register is read-only via configuration accesses. It provides the host system with information on the power-management capabilities of the PCI device and returns the current value of the PMC register. It is set to a generic-configured value following a PCI reset.

This register is mostly just for the passing of power management information to the host system, but two of the fields also have an affect on the operation of the block:

| Bits | Description                                                                                     |

|------|-------------------------------------------------------------------------------------------------|

| 10   | 0—writing 10b to the PowerState bits in PMCSR (see below) leaves PowerState unchanged           |

| 9    | 0—writing 01b to the PowerState bits in<br>the PMCSR (see below) leaves<br>PowerState unchanged |

The Power Management Control/Status register (PMCSR) has a mixture of read-only, read/write and read/clear-on-write bits.

| Bits  | Description                                                                                                                                                                                                                                                                       |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 15    | Set when the function would assert the PME# signal if bit 8 is enabled. Writing 1 clears it & causes the function to stop asserting PME#. Writing 0 has no effect.                                                                                                                |  |

|       | Cleared on PCI reset                                                                                                                                                                                                                                                              |  |

| 14:13 | Read-only scaling factor to be used when interpreting the value of the Power Management Data register. The value and meaning of this field will depend on which data value has been selected using bits 12:9                                                                      |  |

| 12:9  | Read/write field used to select which data is to be reported through the Data register & bits 14:13. Resets to 0                                                                                                                                                                  |  |

| 8     | 1—enables PME#                                                                                                                                                                                                                                                                    |  |

|       | 0—disables PME# (default)                                                                                                                                                                                                                                                         |  |

| 1:0   | Determines the current power state of a function & sets it into a new power state using the values below.  00b—D0  01b—D1  10b—D2  11b—D3                                                                                                                                         |  |

|       | If software attempts to write an unsupported, optional state to this field (i.e. D1 when D1_Support is not set, or D2 when D2_Support is not set), the write operation completes normally on the bus; however, the data is discarded and no state change occurs.  Reset value 00b |  |

The Power Management Bridge Support Extensions register at offset 46h is read-only, and always returns the value 00h.

The Power Management Data register at offset 47h is read-only, and returns a value which depends on which data value has been selected using PMCSR [12:9].

#### 3.4. PCI Set-up Registers

Table 12 lists the PCI set up registers.

**Table 12 Address Map**

| Address | Register  | Register description                                              | Default Value |

|---------|-----------|-------------------------------------------------------------------|---------------|

| 00h     | VID7:0    | Vendor ID, lower byte                                             | 15h*          |

| 01h     | VID15:8   | Vendor ID, upper byte                                             | 14h*          |

| 02h     | DID7:0    | Device ID, lower byte 38h*                                        |               |

| 03h     | DID15:8   | Device ID, upper byte                                             | 95h*          |

| 04h     | REV       | PCI silicon revision                                              | 01h           |

| 05h     | PCC7:0    | PCI class code, programming interface byte                        | 00h           |

| 06h     | PCC15:8   | PCI class code, subclass code byte                                | 02h           |

| 07h     | PCC23:16  | PCI class code, base class code byte                              | 07h           |

| 08h     | SVID7:0   | Subsystem Vendor ID, lower byte                                   | 15h*          |

| 09h     | SVID15:8  | Subsystem Vendor ID, upper byte                                   | 14h*          |

| 0Ah     | SDID7:0   | Subsystem Device ID, lower byte                                   | 00h*          |

| 0Bh     | SDID15:8  | Subsystem Device ID, upper byte                                   | 00h*          |

| 0Ch     | PIP       | Interrupt pin (bit 0 only used) 01h                               |               |

| 0Dh     |           | RFU                                                               | -             |

| 0Eh     | PMC7:0    | Power management capabilities, lower byte 02h                     |               |

| 0Fh     | PMC15:8   | Power management capabilities, upper byte 00h                     |               |

| 10h     | PMD(0)    | Power management data, for when data_select=0 00h                 |               |

| 11h     | PMD(1)    | Power management data, for when data_select=1                     | 00h           |

| 12h     | PMD(2)    | Power management data, for when data_select=2                     | 00h           |

| 13h     | PMD(3)    | Power management data, for when data_select=3 00h                 |               |

| 14h     | PMD(4)    | Power management data, for when data_select=4 00h                 |               |

| 15h     | PMD(5)    | Power management data, for when data_select=5 00h                 |               |

| 16h     | PMD(6)    | Power management data, for when data_select=6 00h                 |               |

| 17h     | PMD(7)    | Power management data, for when data_select=7 00h                 |               |

| 18h     | PMDS(3:0) | Power management data_scale, for when data_select=0, 1, 2, 3  00h |               |

| 19h     | PMDS(7:4) | Power management data_scale, for when data_select=4, 5, 6, 7 00h  |               |

<sup>\*</sup> Ensure these registers are written by the configuration EEPROM.

Most of these registers simply hold values which are presented in read-only registers in PCI configuration space (see section 3.3).

PMDS(3:0) and PMDS(7:4) contain eight 2-bits, packed as shown below, returned as a value for bits 14:13 in PMCSR when PMCSR [12:9] = n where n references PMDSn (see section 3.3).

#### 4. UART FUNCTION

Each UART in the OX16PCI958 is identical. The depth of the FIFOs is 32 bytes.

Each UART converts between RS232-format serial data on separate transmit and receive lines, and byte-wide I/O writes and reads on the host interface. Malformed incoming serial data is flagged along with the data in the receive FIFO. The state of the UART can be found at any time by reading status registers, and modem control (handshaking output) lines can be individually controlled.

Although polled-mode operation is possible, the UARTs will usually be operated on a host-interrupt basis. The interrupt system is designed to allow efficient handling of interrupt service requests from the UART, for example by using the prioritised interrupt identification register, readable FIFO levels, and tuneable FIFO trigger levels.

The internal transmitter and receiver logic runs at a programmable synchronisation factor of 4x, 8x, or 16x the serial baud rate. This internal clock is generated by dividing a reference clock by an integer divisor from 1 to  $(2^{16} - 1)$  and a fractional divisor from 8/8 to 255/8.

#### 4.1. Programming

To prepare the UART for communication, it is necessary to first configure the serial channel using the control registers LCR, SFR, DLL and DLM. These set the number of data and stop bits, the parity setting and the baud rate. These registers can be changed at any time, but if data is being received or transmitted then corruption of the serial data is likely to occur.

It is also a good idea to enable FIFOs using FCR and UCR, to decrease the number of data-transfer services the UART will require. The trigger levels can also be set at this stage using RFTR, RITR and TITR, although the TL16C550-compatible method using FCR7:6 will still work. If appropriate, auto-flow control may be enabled by writing the MCR, and the same register sets the initial state of the output handshaking lines.

Once the serial channel is configured, interrupts can be enabled by writing IER and setting MCR3.

The interrupt handler can read the IIR to determine what type of event needs servicing: the interrupt types are prioritised so that if

more than one event needs servicing, the most urgent one is indicated.

A "transmitter FIFO empty" interrupt is cleared as soon as the IIR is read, so if there is no data waiting to be transmitted then no further action is needed. To restart the flow of transmitted data, the usual practice is for the user-mode part of the device driver to add the data to the software transmit queue and then kick-start transmission by re-writing to the IER with its current value (with bit 0 set). This will re-enable the "transmitter FIFO empty" interrupt and the interrupt handler will handle the transfer of transmit data to the UART, pushing another block every time the FIFO becomes empty.

#### 4.2. Accessible Registers

The internal registers of the UART are listed in Table 13, organized by function with both full name and mnemonic.

**Table 13 Accessible UART Registers**

| Register Selection      | Mnem. |

|-------------------------|-------|

| Indexed register select | IRSR  |

| Line control (bit 7)    | LCR   |

| Safety catch control    | SCC   |

| UART Data           | Mnem. |

|---------------------|-------|

| Receiver buffer     | RBR   |

| Transmitter holding | THR   |

| UART Control                      | Mnem.     |

|-----------------------------------|-----------|

| OAKT COILLOI                      | willelli. |

| LSB divisor latch                 | DLL       |

| MSB divisor latch                 | DLM       |

| Interrupt enable                  | IER       |

| FIFO control                      | FCR       |

| Line control                      | LCR       |

| Modem control                     | MCR       |

| Synchronisation factor            | SFR       |

| Clock prescaler                   | CPR       |

| UART configuration                | UCR       |

| Port control                      | PCR       |

| Receive FIFO flow-control trigger | RFTR      |

| Receive FIFO interrupt trigger    | RITR      |

| Transmit FIFO interrupt trigger   | TITR      |

| UART Status (read only)  | Mnem. |

|--------------------------|-------|

| Interrupt identification | IIR   |

| Line status              | LSR   |

| Modem status             | MSR   |

| Chip ID register         | CIDR  |

| Receive FIFO level       | RFLR  |

| Transmit FIFO level      | TFLR  |

| Build & Test         | Mnem. |

|----------------------|-------|

| Scratch pad          | SCR   |

| Inverted scratch pad | ISCR  |

Individual bits within the registers are referred to by the register mnemonic with the bit number appended. For example, LCR7 refers to bit 7 of the line control register.

The register accessed when an I/O read or write is performed depends on the bits 2:0 of the internal address, the divisor latch access bit (DLAB, which is LCR7), and the Indexed Register Select register (IRSR). Registers with A2:0 from 0 to 7 are accessed through BAR2 or BAR4, and those with A2:0 from 8 to 9 are accessed through BAR3 or BAR5. See section 3.1 for details.

The transmitter holding register and receiver buffer register are used to transfer data for transmission and received data respectively. These are eight-bit registers, but the serial data may be 5, 6, 7 or 8 bits long: data is right-justified and padded with zeroes on the left. The UART always receives and transmits bit 0 first. The THR and RBR can be accessed at the same time as serial data transmission and reception are taking place, because the serializer and deserializer are separate from the data buffers/FIFOs.

Table 14 shows how to select the required UART register.

**Table 14 Register Selection**

| IRSR | DLAB | A2:0 | Mnemonic | Register                                       |

|------|------|------|----------|------------------------------------------------|

| Χ    | 0    | 0    | RBR      | Receiver buffer register (read only)           |

| Х    | 0    | 0    | THR      | Transmitter holding register (write only)      |

| Χ    | 1    | 0    | DLL      | LSB divisor latch                              |

| Χ    | 1    | 1    | DLM      | MSB divisor latch                              |

| Χ    | 0    | 1    | IER      | Interrupt enable register                      |

| Χ    | Χ    | 2    | IIR      | Interrupt identification register (read only)  |

| Χ    | Χ    | 2    | FCR      | FIFO control register (write only)             |

| Χ    | Χ    | 3    | LCR      | Line control register                          |

| Χ    | Χ    | 4    | MCR      | Modem control register                         |

| Χ    | Χ    | 5    | LSR      | Line status register (read only)               |

| Χ    | Χ    | 6    | MSR      | Modem status register (read only)              |

| Χ    | Χ    | 6    | IRSR     | Indexed register select register (write only)  |

| Χ    | Χ    | 8    | PCR      | Port-control: alternate control for CPR        |

| Χ    | Χ    | 9    | SCC      | Safety-catch control                           |

| 0    | Χ    | 7    | SCR      | Scratch pad register                           |

| 1    | Χ    | 7    | ISCR     | Inverted scratch pad register                  |

| 2    | Χ    | 7    | CIDR     | Chip ID register (read only)                   |

| 3    | Χ    | 7    | SFR      | Synchronisation factor register                |

| 4    | Χ    | 7    | -        | Reserved for compatibility                     |

| 5    | Χ    | 7    | -        | Reserved for compatibility                     |

| 6    | Χ    | 7    | UCR      | UART configuration register                    |

| 7    | Χ    | 7    | -        | Reserved for compatibility                     |

| 8    | Χ    | 7    | RFLR     | Receive FIFO level register                    |

| 9    | Χ    | 7    | TFLR     | Transmit FIFO level register                   |

| 10   | Х    | 7    | -        | Reserved for compatibility                     |

| 11   | Χ    | 7    | -        | Reserved for compatibility                     |

| 12   | Χ    | 7    | -        | Reserved for compatibility                     |

| 13   | Х    | 7    | RFTR     | Receive FIFO flow-control trigger register     |

| 14   | Χ    | 7    | RITR     | Receive FIFO interrupt trigger register        |

| 15   | Х    | 7    | TITR     | Transmit FIFO interrupt trigger register       |

| 16   | Х    | 7    | CPR      | Clock prescaler register                       |

| 17   | Х    | 7    | WER      | Wake event enable register                     |

| >17  | Х    | 7    | -        | Reserved for future use – do not read or write |

X = irrelevant, 0 = low level, 1 = high level

The system programmer, using the host, can access any of the UART registers, as summarized in Table 15.

**Table 15 UART Register Summary**

| Register                           | Register Bit Number                       |                                 |                                           |                                      |                                                   |                                                           |                                                                   |                                                                 |

|------------------------------------|-------------------------------------------|---------------------------------|-------------------------------------------|--------------------------------------|---------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------|

| Mnemonic,<br>Access†               | Bit 7                                     | Bit 6                           | Bit 5                                     | Bit 4                                | Bit 3                                             | Bit 2                                                     | Bit 1                                                             | Bit 0                                                           |

| RBR<br>(read only)<br>A=0, DLAB=0  | Data Bit 7<br>(MSB)                       | Data Bit 6                      | Data Bit 5                                | Data Bit 4                           | Data Bit 3                                        | Data Bit 2                                                | Data Bit 1                                                        | Data Bit 0<br>(LSB)                                             |

| THR<br>(write only)<br>A=0, DLAB=0 | Data Bit 7                                | Data Bit 6                      | Data Bit 5                                | Data Bit 4                           | Data Bit 3                                        | Data Bit 2                                                | Data Bit 1                                                        | Data Bit 0                                                      |

| DLL<br>A=0, DLAB=1                 | Bit 7                                     | Bit 6                           | Bit 5                                     | Bit 4                                | Bit 3                                             | Bit 2                                                     | Bit 1                                                             | Bit 0                                                           |

| DLM<br>A=1, DLAB=1                 | Bit 15                                    | Bit 14                          | Bit 13                                    | Bit 12                               | Bit 11                                            | Bit 10                                                    | Bit 9                                                             | Bit 8                                                           |

| IER<br>A=1, DLAB=0                 | 0                                         | 0                               | Low power<br>enable<br>(ignored)          | Sleep<br>mode<br>enable<br>(ignored) | (EDSSI)<br>Enable<br>modem<br>status<br>interrupt | (ERLSI)<br>Enable<br>receiver<br>line status<br>interrupt | (ETHREI)<br>Enable<br>transmitter<br>buffer<br>empty<br>interrupt | (ERBFI)<br>Enable<br>received<br>data<br>available<br>interrupt |

| FCR<br>(write only)<br>A=2         | Receiver<br>Trigger<br>(MSB)              | Receiver<br>Trigger<br>(LSB)    | 0                                         | 0                                    | DMA<br>mode<br>select<br>(ignored)                | Transmitte<br>r FIFO<br>reset                             | Receiver<br>FIFO reset                                            | FIFO<br>enable                                                  |

| IIR<br>(read only)<br>A=2          | FIFOs<br>Enabled <sup>‡</sup>             | FIFOs<br>Enabled <sup>‡</sup>   | 0                                         | 0                                    | Interrupt<br>ID Bit 3 <sup>‡</sup>                | Interrupt<br>ID Bit 2                                     | Interrupt<br>ID Bit 1                                             | 0 if interrupt pending                                          |

| LCR<br>A=3                         | (DLAB)<br>Divisor<br>latch<br>access bit  | Set break                       | Stick<br>parity                           | (EPS)<br>Even<br>parity<br>select    | (PEN)<br>Parity<br>enable                         | (STB)<br>Number of<br>stop bits                           | (WLSB1)<br>Word<br>length<br>select bit 1                         | (WLSB0)<br>Word<br>length<br>select bit 0                       |

| MCR<br>A=4                         | 0                                         | 0                               | AFE                                       | Loop                                 | OUT2<br>(interrupt<br>enable)                     | OUT1                                                      | RTS                                                               | DTR                                                             |

| LSR<br>(read only)<br>A=5          | Error in<br>Receiver<br>FIFO <sup>‡</sup> | Transmitte<br>r Empty<br>(TEMT) | Transmit<br>holding<br>register<br>(THRE) | Break<br>Interrupt<br>(BI)           | Framing<br>Error<br>(FE)                          | Parity<br>Error<br>(PE)                                   | Overrun<br>Error<br>(OE)                                          | Data<br>Ready<br>(DR)                                           |

| MSR<br>(read only)<br>A=6          | (DCD) Data carrier detect                 | (RI)<br>Ring<br>indicator       | (DSR) Data set ready                      | (CTS)<br>Clear to<br>send            | (ΔDCD) Delta data carrier detect                  | (TERI) Trailing edge ring indicator                       | (ΔDSR)<br>Delta data<br>set ready                                 | (ΔCTS)<br>Delta clear<br>to send                                |

| IRSR<br>(write only)<br>A=6        | Bit 7                                     | Bit 6                           | Bit 5                                     | Bit 4                                | Bit 3                                             | Bit 2                                                     | Bit 1                                                             | Bit 0                                                           |

| PCR<br>A=8                         | RFU                                       | RFU                             | Clock<br>select bit 1                     | Clock<br>select bit 0                | Hold CTS                                          | RFU                                                       | RFU                                                               | RFU                                                             |

| SCC<br>A=9                         | Indexed reg safety catch                  | RFU                             | RFU                                       | RFU                                  | RFU                                               | RFU                                                       | RFU                                                               | RFU                                                             |

| SCR<br>A=7, IRSR=0                 | Bit 7                                     | Bit 6                           | Bit 5                                     | Bit 4                                | Bit 3                                             | Bit 2                                                     | Bit 1                                                             | Bit 0                                                           |

| Register                           | Register B                   | Register Bit Number |       |       |       |       |                         |              |

|------------------------------------|------------------------------|---------------------|-------|-------|-------|-------|-------------------------|--------------|

| Mnemonic, Access†                  | Bit 7                        | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| ISCR<br>A=7, IRSR=1                | Bit 7                        | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| CIDR<br>(read only)<br>A=7, IRSR=2 | 0                            | 0                   | 0     | 1     | 0     | 0     | 0                       | 0            |

| SFR<br>A=7, IRSR=3                 | RFU                          | RFU                 | RFU   | SF=16 | SF=8  | SF=4  | RFU                     | RFU          |

| UCR<br>A=7, IRSR=6                 | RFU                          | RFU                 | RFU   | RFU   | RFU   | RFU   | Enable<br>deep<br>FIFOs | Force AFC on |

| RFLR<br>(read only)<br>A=7, IRSR=8 | Error in<br>Receiver<br>FIFO | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| TFLR<br>(read only)<br>A=7, IRSR=9 | Bit 7                        | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| RFTR<br>A=7, RSR=13                | RFU                          | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| RITR<br>A=7, RSR=14                | RFU                          | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| TITR<br>A=7, RSR=15                | RFU                          | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| CPR<br>A=7, RSR=16                 | Bit 7                        | Bit 6               | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1                   | Bit 0        |

| WER<br>A=7, RSR=17                 | INT                          | RFU                 | RFU   | SIN#  | ΔDCD  | TERI  | ΔDSR                    | ΔCTS         |

<sup>†</sup> In this column, 'A' refers to the decimal value of the internal address bus. disabled.

<sup>‡</sup> These bits are always 0 when FIFOs are

#### Master Reset

The UARTs are reset when PCI RESET# is asserted. Table 16 and Table 17 summarize the effect of reset on the UART circuits.

**Table 16 Effect of RESET on UART Signals**

| UART Signal | Reset control | Signal<br>Reset State |

|-------------|---------------|-----------------------|

| DTR#        | Reset         | High                  |

| RTS#        | Reset         | High                  |

| SOUT        | Reset         | High                  |

Table 17 Effect of RESET on UART Registers

| UART<br>Register | Register reset state                               |

|------------------|----------------------------------------------------|

| LSR              | Bits 7,4,3,2,1,0 cleared<br>Bits 6 & 5 set         |

| MCR              | All bits cleared Note bits 7:6 permanently cleared |

| IER              | All bits cleared Note bits 7:6 permanently cleared |

| FCR              | All bits cleared                                   |

| IIR              | Bits 7,6,3,2,1 cleared<br>Bit 0 is set             |

| LCR              | All bits are cleared                               |

| TFTR             | All bits are cleared                               |

| MSR              | Bits 3–0 cleared                                   |

|                  | Bits 7–4 input signals                             |

| IRSR             | All bits cleared                                   |

| SCR              | All bits cleared                                   |

| LSB & MSB        | All bits cleared                                   |

| RBR              | All bits cleared                                   |

| THR              | All bits cleared                                   |

| RFTR             | All bits cleared                                   |

| RITR             | All bits are cleared                               |

| UCR              | All bits are cleared                               |

| WER              | All bits are cleared                               |

Table 18 Effect of RESET on UART Interrupts

| Interrupt<br>Type    | Reset Control               | Interrupt<br>Reset<br>State |

|----------------------|-----------------------------|-----------------------------|

| modem status changes | Reset/Read MSR              | Low                         |

| receiver data ready  | Reset/Read RBR              | Low                         |

| RCVR errors          | Reset/Read LSR              | Low                         |

| THRE                 | Reset/Read<br>IIR/Write THR | Low                         |

**Table 19 Effect of RESET on UART FIFOs**

| FIFO             | Reset Control               | FIFO Reset State |

|------------------|-----------------------------|------------------|

| Receiver<br>FIFO | Reset<br>FCR1–FCR0<br>∆FCR0 | FIFO empty       |

| Transmitter FIFO | Reset<br>FCR1–FCR0<br>∆FCR0 | FIFO empty       |

#### **Serial Data Format**

A 0 in RBR or THR corresponds to a logic low on SIN or SOUT, and a 1 in RBR or THR corresponds to a logic high on SIN or SOUT.

Bit 0 is always the least significant bit (LSB) and is the first bit to be serially transmitted or received.

A start bit or line break state corresponds to a logic low on SIN or SOUT, and a stop bit or inter-byte marking state corresponds to a logic high on SIN or SOUT.

#### 4.3. Transmitter/Receiver Section

The status of the receiver is given by the Line Status Register (LSR).

The control of the receiver section and format of the data characters such as number of data bits, parity, etc is controlled by the Line Control Register (LCR). Note if parity is used (LCR3) then the polarity of parity LCR4 is required.

As serial asynchronous data is fed into the receiver serial data input terminal SIN, the UART continually looks for a high-to-low transition. Upon detection of the transition, an internal counter is reset and counts the SF× clock input to SF/2, which is the centre of the start bit. (SF is the Synchronisation Factor)

The receiver is prevented from assembling a false data character caused by noise on the SIN input, by verification of the start bits. Note: The start bit is valid only if SIN is still low.

The UART receiver section contains a Receiver Buffer Register (RBR) which is a FIFO and a Receiver Deserializer Register (RDR). Data fed into the receiver serial data input terminal SIN is deserialized by the RDR and is fed into RBR.

The control of the receiver section and format of the data characters such as number of data bits, parity, etc is controlled by LCR. Note if parity is used (LCR3) then the polarity of parity LCR4 is required.

The receiver timing is supplied by the baud clock generator.

In FIFO modes, FCR is used to enable and reset the receiver FIFO and also can be used to set data trigger levels for when interrupts are generated.

In non FIFO mode (16C450 style), when the received data available interrupt is enabled, an interrupt is generated when a character is placed in the receiver buffer register. When RBR is read, the interrupt is cleared.

# Transmitter Holding Register & Multiplexer Register (THR & TMR)

The UART transmitter section contains a Transmitter Holding Register (THR), which is a FIFO, and a transmitter multiplexer register (TMR). THR receives data off the internal data bus and moves it into the TMR, while the transmitter is idle, which serializes the data and outputs it to the transmitter data serial output terminal SOUT.

The transmitter timing is supplied by the baud clock generator.

In FIFO modes, FCR is used to enable and reset the transmitter FIFOs and can be used to set data trigger levels for when interrupts are generated. For more details see Section 4.2.

In non FIFO mode (16C450), when the transmitter holding register empty interrupt is enabled, an interrupt is generated when THR is empty. When a character is loaded into the register, the interrupt is cleared.

#### Line Control Register (LCR)

LCR controls the format of the data character and is applicable to both transmitter and receiver. The LCR is read-writable. Its contents are described below.

| Bits | Description                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | Divisor latch access bit (DLAB) 1—enables access to DLL & DLM 0—enables access to IER, THR &RBR                                                                                                                                  |

| 6    | 1—SOUT is forced to the spacing state (low)                                                                                                                                                                                      |

| 5    | 1—If LCR3 is 1, parity bit transmission & reception is the state opposite to LCR4 value. If LCR4 is 1, even parity enabled. (or cleared parity enabled, if LCR5 is 1) 0—odd parity enabled (or set parity enabled, if LCR5 is 1) |

|      | This forces parity to a known state                                                                                                                                                                                              |

| 4    | 1—even parity enabled. (or cleared parity is enabled, if LCR5 is 1) 0—odd parity enabled (or set parity enabled, if LCR5 is 1).                                                                                                  |

| Bits | Description                                                                                                                                                                                      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3    | 1—a parity bit is generated between the last data word bit & stop bit in data transmitted & checked by the receiver                                                                              |

|      | 0—no parity is selected; see Table 20                                                                                                                                                            |

| 2    | Specifies either one or two stop bits in each transmitted character.                                                                                                                             |

|      | 0—one stop bit is generated in the data 1—1½ or 2 stop bits are generated in the data: see Table 22. The receiver clocks only the first stop bit, regardless of the number of stop bits selected |

| 1:0  | These two bits specify the number of bits in each transmitted or received serial character; see Table 21                                                                                         |

**Table 20 Parity Selection**

| LCR5:3 | Description    |

|--------|----------------|

| X X 0  | No parity      |

| 001    | Odd parity     |

| 0 1 1  | Even parity    |

| 101    | Set parity     |

| 111    | Cleared parity |

**Table 21 Word Length Selection**

| LCR1:0 | Description           |

|--------|-----------------------|

| 0 0    | Word length is 5 bits |

| 0 1    | Word length is 6 bits |

| 10     | Word length is 7 bits |

| 11     | Word length is 8 bits |

**Table 22 Stop Bit Length Selection**

| LCR2:0 | Description            |

|--------|------------------------|

| 0 X X  | 1 stop bit generated   |

| 100    | 1½ stop bits generated |

| 101    | 2 stop bits generated  |

| 110    | 2 stop bits generated  |

| 111    | 2 stop bits generated  |

Use the following steps to create a line break:

Note: no invalid characters are transmitted because of the break.

- When THRE empty status occurs, load a zero byte

- 2. After the next THRE, set the break

- 3. When TEMT is set to high, wait for the transmitter to be idle

- 4. Clear the break when the transmission has to be re-established.

#### Line Status Register (LSR)

Read-only register that indicates the status of serial data reception.

|      | T                                                                                                                                                                                                                                                                                                                                                  |

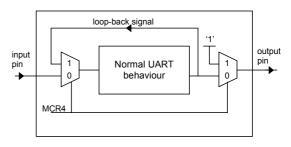

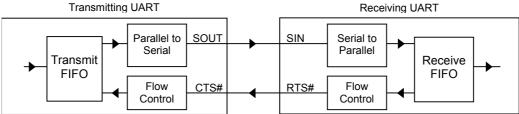

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|