# ANALOG<br/>DEVICESRail-to-Rail, Fast, Low Power 2.5 V to 5.5 V,<br/>Single-Supply TTL/CMOS Comparator

## ADCMP608

#### FEATURES

Fully specified rail to rail at V<sub>cc</sub> = 2.5 V to 5.5 V Input common-mode voltage from -0.2 V to V<sub>cc</sub> + 0.2 V Low glitch CMOS-/TTL-compatible output stage 40 ns propagation delay Low power: 1 mW at 2.5 V Shutdown pin Power supply rejection > 60 dB -40°C to +125°C operation

#### **APPLICATIONS**

High speed instrumentation Clock and data signal restoration Logic level shifting or translation High speed line receivers Threshold detection Peak and zero-crossing detectors High speed trigger circuitry Pulse-width modulators Current-/voltage-controlled oscillators

#### **GENERAL DESCRIPTION**

The ADCMP608 is a fast comparator fabricated on XFCB2, an Analog Devices, Inc. proprietary process. This comparator is exceptionally versatile and easy to use. Features include an input range from  $V_{EE} - 0.2$  V to  $V_{CC} + 0.2$  V, low noise, TTL-/CMOS-compatible output drivers, and shutdown inputs. The device offers 40 ns propagation delays driving a 15 pF load with 10 mV overdrive on 500  $\mu$ A typical supply current.

A flexible power supply scheme allows the device to operate with a single +2.5 V positive supply and a -0.2 V to + 2.7 V input signal range up to a +5.5 V positive supply with a -0.2 V to +5.7 V input signal range.

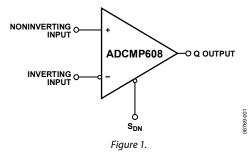

#### FUNCTIONAL BLOCK DIAGRAM

The TTL-/CMOS-compatible output stage is designed to drive up to 15 pF with full rated timing specifications and to degrade in a graceful and linear fashion as additional capacitance is added. The input stage of the comparator offers robust protection against large input overdrive, and the outputs do not phase reverse when the valid input signal range is exceeded.

The ADCMP608 is available in a tiny 6-lead SC70 package with a single-ended output and a shutdown pin.

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram1                    |

| General Description                          |

| Revision History                             |

| Specifications                               |

| Electrical Characteristics                   |

| Absolute Maximum Ratings                     |

| Thermal Resistance                           |

| ESD Caution                                  |

| Pin Configuration and Function Descriptions5 |

| Typical Performance Characteristics          |

| Application Information                 | 7  |

|-----------------------------------------|----|

| Power/Ground Layout and Bypassing       |    |

| TTL-/CMOS-Compatible Output Stage       | 7  |

| Optimizing Performance                  | 7  |

| Comparator Propagation Delay Dispersion | 7  |

| Crossover Bias Point                    | 8  |

| Minimum Input Slew Rate Requirement     | 8  |

| Typical Application Circuits            | 9  |

| Outline Dimensions                      | 10 |

| Ordering Guide                          | 10 |

#### **REVISION HISTORY**

4/07—Revision 0: Initial Version

#### **SPECIFICATIONS**

#### **ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 2.5 V,  $T_A$  = -40°C to +125°C. Typical values are  $T_A$  = 25°C, unless otherwise noted.

#### Table 1.

| Parameter                                 | Symbol                          | Conditions                                                                  | Min            | Тур      | Max  | Unit |

|-------------------------------------------|---------------------------------|-----------------------------------------------------------------------------|----------------|----------|------|------|

| DC INPUT CHARACTERISTICS                  |                                 |                                                                             | 1              |          |      |      |

| Voltage Range                             | $V_{P}, V_{N}$                  | $V_{cc} = 2.5 \text{ V} \text{ to } 5.5 \text{ V}$                          | -0.2           |          | Vcc  | V    |

| Common-Mode Range                         |                                 | $V_{CC} = 2.5 \text{ V} \text{ to } 5.5 \text{ V}$                          | -0.2           |          | Vcc  | V    |

| Differential Voltage                      |                                 | $V_{cc} = 2.5 V \text{ to } 5.5 V$                                          |                |          | Vcc  | V    |

| Offset Voltage                            | Vos                             |                                                                             | -5.0           | ±3       | +5.0 | mV   |

| Bias Current                              | I <sub>P</sub> , I <sub>N</sub> |                                                                             | -0.4           |          | +0.4 | μA   |

| Offset Current                            |                                 |                                                                             | -1.0           |          | +1.0 | μA   |

| Capacitance                               | $C_P, C_N$                      |                                                                             |                | 1        |      | pF   |

| Resistance, Differential Mode             |                                 | –0.5 V to V <sub>cc</sub> + 0.5 V                                           | 200            |          | 7000 | kΩ   |

| Resistance, Common Mode                   |                                 | -0.5 V to V <sub>cc</sub> + 0.5 V                                           | 100            |          | 4000 | kΩ   |

| Active Gain                               | Av                              |                                                                             |                | 80       |      | dB   |

| Common-Mode Rejection                     | CMRR                            | $V_{CC} = 2.5 \text{ V}, V_{CM} = -0.2 \text{ V} \text{ to } 2.7 \text{ V}$ | 45             |          |      | dB   |

| ,                                         |                                 | $V_{cc} = 5.5 V$                                                            | 45             |          |      | dB   |

| SHUTDOWN PIN CHARACTERISTICS <sup>1</sup> |                                 |                                                                             | 1              |          |      |      |

| V <sub>IH</sub>                           |                                 | Comparator is operating                                                     | 2.0            |          | Vcc  | v    |

| V <sub>IL</sub>                           |                                 | Shutdown guaranteed                                                         | -0.2           | +0.4     | +0.4 | v    |

| I <sub>H</sub>                            |                                 | $V_{IH} = V_{CC}$                                                           | -6             |          | +6   | μA   |

| Sleep Time                                | t <sub>sp</sub>                 | $I_{cc} < 100 \mu A$                                                        |                | 300      |      | ns   |

| Wake-Up Time                              | t <sub>H</sub>                  | $V_{PP} = 10 \text{ mV}$ , output valid                                     |                | 150      |      | ns   |

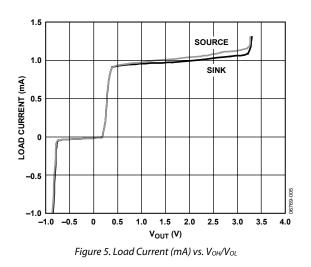

| DC OUTPUT CHARACTERISTICS                 |                                 | $V_{cc} = 2.5 V \text{ to } 5.5 V$                                          |                |          |      |      |

| Output Voltage High Level                 | V <sub>OH</sub>                 | $I_{OH} = 0.8 \text{ mA}, V_{CC} = 2.5 \text{ V}$                           | $V_{cc} - 0.4$ |          |      | v    |

| Output Voltage Low Level                  | Vol                             | $I_{OL} = 0.8 \text{ mA}, V_{CC} = 2.5 \text{ V}$                           |                |          | 0.4  | v    |

| AC PERFORMANCE <sup>2</sup>               |                                 | $V_{cc} = 2.5 V \text{ to } 5.5 V$                                          |                |          |      |      |

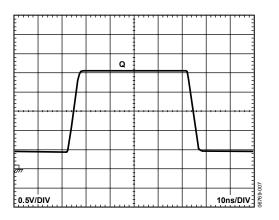

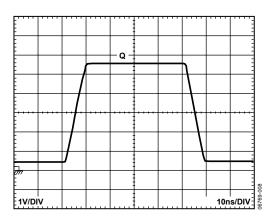

| Rise Time/Fall Time                       | t <sub>R</sub> , t <sub>F</sub> | 10% to 90%, V <sub>cc</sub> = 2.5 V                                         |                | 25 to 50 |      | ns   |

|                                           |                                 | 10% to 90%, $V_{cc} = 5.5 V$                                                |                | 45 to 75 |      | ns   |

| Propagation Delay                         | t <sub>PD</sub>                 | $V_{OD} = 10 \text{ mV}, V_{CC} = 2.5 \text{ V}$                            |                | 30 to 50 |      | ns   |

| r lopugation beidy                        | CrD                             | $V_{OD} = 50 \text{ mV}, V_{CC} = 5.5 \text{ V}$                            |                | 35 to 60 |      | ns   |

| Propagation Delay Skew—Rising to          |                                 | $V_{cc} = 2.5 V$                                                            |                | 4.5      |      | ns   |

| Falling Transition                        |                                 | $V_{cc} = 5.5 V$                                                            |                | 8        |      | ns   |

| Overdrive Dispersion                      |                                 | $10 \text{ mV} < V_{OD} < 125 \text{ mV}$                                   |                | 12       |      | ns   |

| Common-Mode Dispersion                    |                                 | $-0.2 V < V_{CM} < V_{CC} + 0.2 V$                                          |                | 1.5      |      | ns   |

| POWER SUPPLY                              |                                 |                                                                             | 1              |          |      |      |

| Supply Voltage Range                      | Vcc                             |                                                                             | 2.5            |          | 5.5  | V    |

| Positive Supply Current                   | Ivcc                            | $V_{cc} = 2.5 V$                                                            |                | 550      | 800  | μA   |

|                                           |                                 | $V_{cc} = 5.5 V$                                                            |                | 800      | 1300 | μΑ   |

| Power Dissipation                         | PD                              | $V_{cc} = 2.5 V$                                                            |                | 1.375    | 2.0  | mW   |

| •                                         | -                               | $V_{cc} = 5.5 V$                                                            |                | 4.95     | 7.15 | mW   |

| Power Supply Rejection Ratio              | PSRR                            | $V_{cc} = 2.5 \text{ V to } 5.5 \text{ V}$                                  | -50            |          |      | dB   |

| Shutdown Current                          | I <sub>SD</sub>                 | $V_{cc} = 2.5 V \text{ to } 5.5 V$                                          |                | 250      | 350  | μA   |

<sup>1</sup> The output will be in a high impedance mode when the device is in shutdown mode. Note that this feature should be used with care since the enable/disable time is much longer than with a true tristate output.

$^{2}$  V<sub>IN</sub> = 100 mV square input at 1 MHz, V<sub>CM</sub> = 0 V, CL = 15 pF, V<sub>CCI</sub> = 2.5 V, unless otherwise noted.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                  | Rating                            |

|--------------------------------------------|-----------------------------------|

| Supply Voltages                            |                                   |

| Supply Voltage<br>(V <sub>CC</sub> to GND) | –0.5 V to +6.0 V                  |

| Supply Differential                        | –6.0 V to +6.0 V                  |

| Input Voltages                             |                                   |

| Input Voltage                              | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Differential Input Voltage                 | $\pm(V_{CC} + 0.5 V)$             |

| Maximum Input/Output Current               | ±50 mA                            |

| Shutdown Control Pin                       |                                   |

| Applied Voltage (S <sub>DN</sub> to GND)   | -0.5 V to V <sub>CC</sub> + 0.5 V |

| Maximum Input/Output Current               | ±50 mA                            |

| Output Current                             | ±50 mA                            |

| Temperature                                |                                   |

| Operating Temperature, Ambient             | -40°C to +125°C                   |

| Operating Temperature, Junction            | 150°C                             |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{IA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

#### Table 3. Thermal Resistance

| Package Type         | θ <sub>JA</sub> 1 | Unit |

|----------------------|-------------------|------|

| ADCMP608 6-Lead SC70 | 426               | °C/W |

<sup>1</sup> Measurement in still air.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

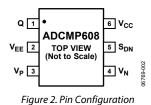

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Table 4. ADCMP608 Pin Function Descriptions

Pin No.

Mnemonic

Description

| Pin No. | Mnemonic        | Description                                                                                                                                                         |

|---------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | Q               | Noninverting Output. Q is at logic high if the analog voltage at the noninverting input, $V_P$ , is greater than the analog voltage at the inverting input, $V_N$ . |

| 2       | VEE             | Negative Supply Voltage.                                                                                                                                            |

| 3       | VP              | Noninverting Analog Input.                                                                                                                                          |

| 4       | V <sub>N</sub>  | Inverting Analog Input.                                                                                                                                             |

| 5       | S <sub>DN</sub> | Shutdown. Drive this pin low to shut down the device.                                                                                                               |

| 6       | V <sub>cc</sub> | V <sub>cc</sub> Supply.                                                                                                                                             |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{CC}$  =2.5 V,  $T_A$  = 25°C, unless otherwise noted.

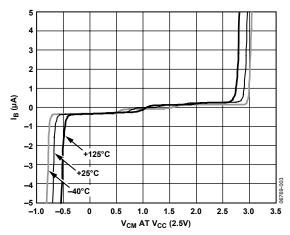

Figure 3. Input Bias Current vs. Input Common-Mode Voltage

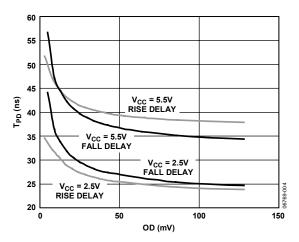

Figure 4. Propagation Delay vs. Input Overdrive at  $V_{CC} = 2.5$  V and 5.5 V

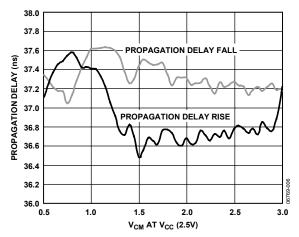

Figure 6. Propagation Delay vs. Input Common-Mode Voltage

Figure 7. 1 MHz Output Voltage Waveform  $V_{CC} = 2.5 V$

Figure 8. 1 MHz Output Voltage Waveform  $V_{CC} = 5.5 V$

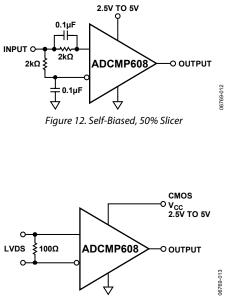

### APPLICATION INFORMATION power/ground layout and bypassing

The ADCMP608 comparator is a high speed device. Despite the low noise output stage, it is essential to use proper high speed design techniques to achieve the specified performance. Because comparators are uncompensated amplifiers, feedback in any phase relationship is likely to cause oscillations or undesired hysteresis. Of critical importance is the use of low impedance supply planes, particularly the output supply plane ( $V_{CC}$ ) and the ground plane (GND). Individual supply planes are recommended as part of a multilayer board. Providing the lowest inductance return path for switching currents ensures the best possible performance in the target application.

It is also important to adequately bypass the input and output supplies. A 0.1  $\mu$ F bypass capacitor should be placed as close as possible to the V<sub>CC</sub> supply pin. The capacitor should be connected to the GND plane with redundant vias placed to provide a physically short return path for output currents flowing back from ground to the V<sub>CC</sub> pin. High frequency bypass capacitors should be carefully selected for minimum inductance and ESR. Parasitic layout inductance should also be strictly controlled to maximize the effectiveness of the bypass at high frequencies.

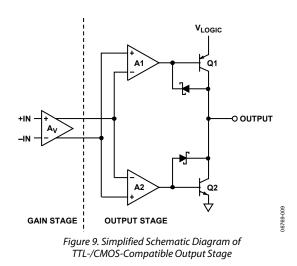

#### TTL-/CMOS-COMPATIBLE OUTPUT STAGE

Specified propagation delay performance can be achieved only by keeping the capacitive load at or below the specified minimums. The output of the ADCMP608 is designed to directly drive one Schottky TTL, or three low power Schottky TTL loads, or the equivalent. For large fan outs, buses, or transmission lines, use an appropriate buffer to maintain the excellent speed and stability of the comparator.

With the rated 15 pF load capacitance applied, more than half of the total device propagation delay is output stage slew time. Because of this, the total propagation delay decreases as  $V_{\rm CC}$  decreases, and instability in the power supply may appear as excess delay dispersion.

Delay is measured to the 50% point for whatever supply is in use; thus, the fastest times are observed with the  $V_{\rm CC}$  supply at 2.5 V, and larger values are observed when driving loads that switch at other levels.

Overdrive and input slew rate dispersions are not significantly affected by output loading and  $V_{\rm CC}$  variations.

The TTL-/CMOS-compatible output stage is shown in the simplified schematic diagram (see Figure 9). Because of its inherent symmetry and generally good behavior, this output stage is readily adaptable for driving various filters and other unusual loads.

#### **OPTIMIZING PERFORMANCE**

As with any high speed comparator, proper design and layout techniques are essential for obtaining the specified performance. Stray capacitance, inductance, common power and ground impedances, or other layout issues can severely limit performance and can often cause oscillation. The source impedance should be minimized as much as is practicable. High source impedance, in combination with the parasitic input capacitance of the comparator, causes an undesirable degradation in bandwidth at the input, thus degrading the overall response. Higher impedances encourage undesired coupling.

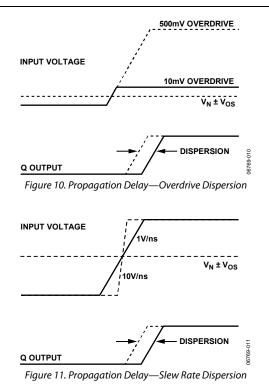

# COMPARATOR PROPAGATION DELAY DISPERSION

The ADCMP608 comparator is designed to reduce propagation delay dispersion over a wide input overdrive range of 10 mV to  $V_{CC}$  – 1 V. Propagation delay dispersion is the variation in propagation delay that results from a change in the degree of overdrive or slew rate (how far or how fast the input signal exceeds the switching threshold).

Propagation delay dispersion is a specification that becomes important in high speed, time-critical applications, such as data communication, automatic test and measurement, and instrumentation. It is also important in event-driven applications, such as pulse spectroscopy, nuclear instrumentation, and medical imaging. Dispersion is defined as the variation in propagation delay as the input overdrive conditions are changed (Figure 10 and Figure 11).

ADCMP608 dispersion is typically < 12 ns as the overdrive varies from 10 mV to 125 mV. This specification applies to both positive and negative signals because the device has very closely matched delays for both positive-going and negativegoing inputs, and very low output skews. Remember to add the actual device offset to the overdrive for repeatable dispersion measurements.

#### **CROSSOVER BIAS POINT**

Rail-to-rail inputs of this type, in both op amps and comparators, have a dual front-end design. Certain devices are active near the  $V_{CC}$  rail and others are active near the  $V_{EE}$  rail. At some predetermined point in the common-mode range, a crossover occurs. At this point, normally  $V_{CC}$ /2, the direction of the bias current reverses and there are changes in measured offset voltages and currents.

The ADCMP608 slightly elaborates on this scheme. Crossover points can be found at approximately 0.8 V and 1.6 V.

#### MINIMUM INPUT SLEW RATE REQUIREMENT

With the rated load capacitance and normal good PC board design practice, as discussed in the Optimizing Performance section, these comparators should be stable at any input slew rate with no hysteresis. Broadband noise from the input stage is observed in place of the violent chattering seen with most other high speed comparators. With additional capacitive loading or poor bypassing, oscillation may be encountered. These oscillations are due to the high gain bandwidth of the comparator in combination with feedback through parasitics in the package and PC board. In many applications, chattering is not harmful.

## **TYPICAL APPLICATION CIRCUITS**

Figure 13. LVDS-to-CMOS Receiver

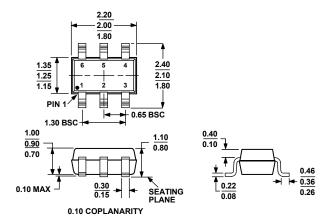

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-203-AB

Figure 14. 6-Lead Thin Shrink Small Outline Transistor Package (SC70) (KS-6) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model                        | Temperature<br>Range | Package Description                                        | Package<br>Option | Branding |

|------------------------------|----------------------|------------------------------------------------------------|-------------------|----------|

| ADCMP608BKSZ-R21             | -40°C to +125°C      | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6              | G0U      |

| ADCMP608BKSZ-RL <sup>1</sup> | -40°C to +125°C      | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6              | GOU      |

| ADCMP608BKSZ-REEL71          | -40°C to +125°C      | 6-Lead Thin Shrink Small Outline Transistor Package (SC70) | KS-6              | GOU      |

<sup>1</sup> Z = RoHS Compliant Part.

## NOTES

## **NOTES**

©2007 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D06769-0-4/07(0)

www.analog.com

Rev. 0 | Page 12 of 12