#### **Features**

- 8-bit Resolution

- ADC Gain Adjust

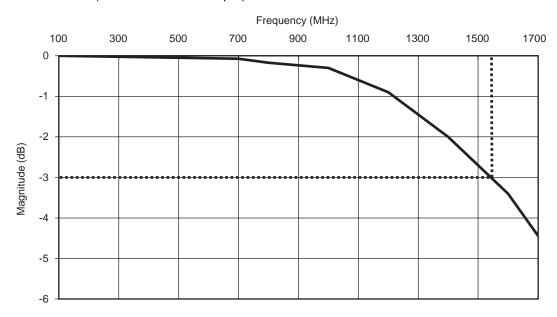

- 1.5 GHz Full Power Input Bandwidth (-3 dB)

- 1 GSPS (min) Sampling Rate

- SINAD = 44.3 dB (7.2 Effective Bits), SFDR = 58 dBc, at  $F_S$  = 1 GSPS,  $F_{IN}$  = 20 MHz

- SINAD = 42.9 dB (7.0 Effective Bits), SFDR = 52 dBc, at F<sub>S</sub> = 1 GSPS, F<sub>IN</sub> = 500 MHz

- SINAD = 40.3 dB (6.8 Effective Bits), SFDR = 50 dBc, at F<sub>S</sub> = 1 GSPS, F<sub>IN</sub> = 1000 MHz (-3 dB FS)

- 2-tone IMD: -52 dBc (489 MHz, 490 MHz) at 1 GSPS

- DNL = 0.3 lsb, INL = 0.7 lsb

- Low Bit Error Rate (10<sup>-13</sup>) at 1 GSPS

- Very Low Input Capacitance: 3 pF

- 500 mVpp Differential or Single-ended Analog Inputs

- Differential or Single-ended 50Ω ECL Compatible Clock Inputs

- ECL or LVDS/HSTL Output Compatibility

- Data Ready Output with Asynchronous Reset

- Gray or Binary Selectable Output Data; NRZ Output Mode

- Power Consumption: 3.4W at Tj = 70°C Typical

- Radiation Tolerance Oriented Design (150 Krad (Si) measured)

- Two Package Versions

- ESA/SCC Detailed Specification Available on Request

- Enhanced CQFP68 Packaged Device: TS8388BFS

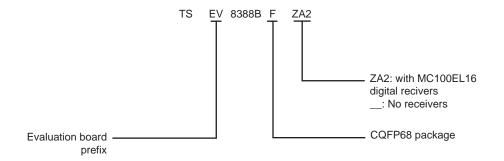

- Evaluation board: TSEV8388BF

- Demultiplexer: TS81102G0: Companion Device Available

### **Applications**

- Digital Sampling Oscilloscopes

- Satellite Receiver

- Electronic Countermeasures/Electronic Warfare

- Direct RF Down-conversion

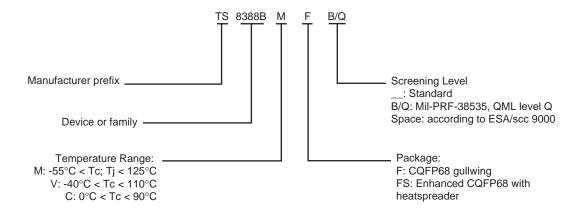

### Screening

- Atmel Standard Screening Level

- Mil-PRF-38535, QML Level Q for Package Version, DSCC 5962-0050401QYC

- Temperature Range: up to -55°C < Tc; Tj < +125°C

### **Description**

The TS8388BF is a monolithic 8-bit analog-to-digital converter, designed for digitizing wide bandwidth analog signals at very high sampling rates of up to 1 GSPS.

The TS8388BF uses an innovative architecture, including an on-chip Sample and Hold (S/H), and is fabricated with an advanced high speed bipolar process.

The on-chip S/H has a 1.5 GHz full power input bandwidth, providing excellent dynamic performance in undersampling applications (High IF digitizing).

F Suffix: CQFP 68

Ceramic Quad Flat Pack

ADC 8-bit 1 GSPS

**TS8388BF**

# Functional Description

#### **Block Diagram**

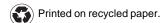

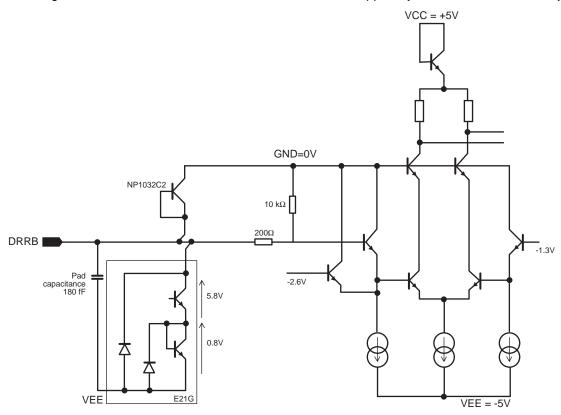

The following figure shows the simplified block diagram.

Figure 1. Simplified Block Diagram

# Functional Description

The TS8388BF is an 8-bit 1 GSPS ADC based on an advanced high-speed bipolar technology featuring a cutoff frequency of 25 GHz.

The TS8388BF includes a front-end master/slave Track and Hold stage (S/H), followed by an analog encoding stage and interpolation circuitry.

Successive banks of latches regenerate the analog residues into logical data before entering an error correction circuitry and a resynchronization stage followed by  $75\Omega$  differential output buffers.

The TS8388BF works in fully differential mode from analog inputs up to digital outputs.

The TS8388BF features a full-power input bandwidth of 1.5 GHz.

A control pin GORB is provided to select either Gray or Binary data output format.

A gain control pin is provided in order to adjust the ADC gain.

A Data Ready output asynchronous reset (DRRB) is available on TS8388BF.

The TS8388BF uses only vertical isolated NPN transistors together with oxide isolated polysilicon resistors, which allow enhanced radiation tolerance (no performance drift measured at 150 kRad total dose).

## **Specifications**

### Absolute Maximum Ratings

Table 1. Absolute Maximum Ratings

| Parameter                                                         | Symbol                                | Comments | Value                                            | Unit |

|-------------------------------------------------------------------|---------------------------------------|----------|--------------------------------------------------|------|

| Positive supply voltage                                           | V <sub>cc</sub>                       |          | GND to 6                                         | V    |

| Digital negative supply voltage                                   | DV <sub>EE</sub>                      |          | GND to -5.7                                      | V    |

| Digital positive supply voltage                                   | V <sub>PLUSD</sub>                    |          | GND -0.3 to 2.8                                  | V    |

| Negative supply voltage                                           | V <sub>EE</sub>                       |          | GND to -6                                        | V    |

| Maximum difference between negative supply voltage                | DV <sub>EE</sub> to V <sub>EE</sub>   |          | 0.3                                              | V    |

| Analog input voltages                                             | V <sub>IN</sub> or V <sub>INB</sub>   |          | -1 to +1                                         | V    |

| Maximum difference between V <sub>IN</sub> and V <sub>INB</sub>   | V <sub>IN</sub> - V <sub>INB</sub>    |          | -2 to +2                                         | V    |

| Digital input voltage                                             | V <sub>D</sub>                        | GORB     | -0.3 to V <sub>CC</sub> +0.3                     | V    |

| Digital input voltage                                             | V <sub>D</sub>                        | DRRB     | V <sub>EE</sub> -0.3 to +0.9                     | V    |

| Digital output voltage                                            | Vo                                    |          | V <sub>PLUSD</sub> -3 to V <sub>PLUSD</sub> -0.5 | V    |

| Clock input voltage                                               | V <sub>CLK</sub> or V <sub>CLKB</sub> |          | -3 to +1.5                                       | V    |

| Maximum difference between V <sub>CLK</sub> and V <sub>CLKB</sub> | V <sub>CLK</sub> - V <sub>CLKB</sub>  |          | -2 to +2                                         | V    |

| Maximum junction temperature                                      | T <sub>j</sub>                        |          | +135                                             | °C   |

| Storage temperature                                               | T <sub>stg</sub>                      |          | -65 to +150                                      | °C   |

| Lead temperature (soldering 10s)                                  | T <sub>leads</sub>                    |          | +300                                             | °C   |

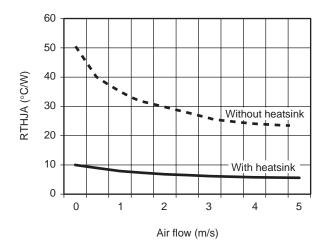

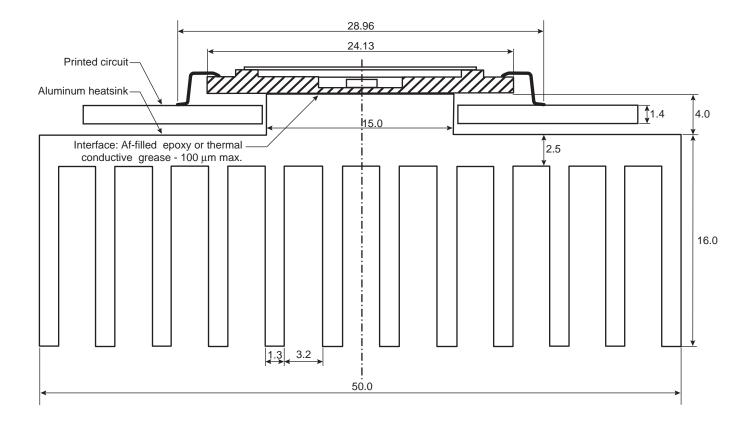

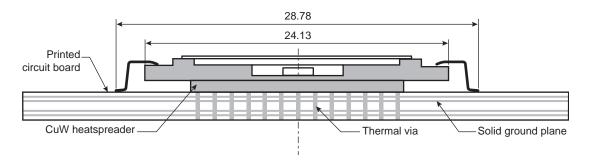

Note: Absolute maximum ratings are limiting values (referenced to GND = 0V), to be applied individually, while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability. The use of a thermal heat sink is mandatory. See "The board set comes fully assembled and tested, with the TS8388BF in CQFP68 package installed." on page 37.

# Recommended Operating Conditions

Table 2. Recommended Operating Conditions

|                                 |                                    |                           | Reco  | mmended ' | Value |      |

|---------------------------------|------------------------------------|---------------------------|-------|-----------|-------|------|

| Parameter                       | Symbol                             | Comments                  | Min   | Тур       | Max   | Unit |

| Positive supply voltage         | V <sub>CC</sub>                    |                           | 4.5   | +5        | 5.25  | V    |

| Positive digital supply voltage | V <sub>PLUSD</sub>                 | ECL output compatibility  | _     | GND       | -     | V    |

| Positive digital supply voltage | V <sub>PLUSD</sub>                 | LVDS output compatibility | +1.4  | +2.4      | +2.6  | V    |

| Negative supply voltage         | V <sub>EE</sub> , DV <sub>EE</sub> |                           | -5.25 | -5        | -4.75 | V    |

Table 2. Recommended Operating Conditions (Continued)

|                                                |                                                                         |                                                                 | Reco        | mmended                                        | Value       |            |

|------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|------------------------------------------------|-------------|------------|

| Parameter                                      | Symbol                                                                  | Comments                                                        | Min         | Тур                                            | Max         | Unit       |

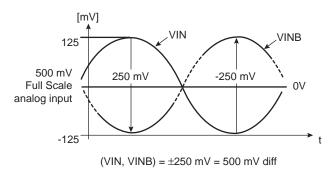

| Differential analog input voltage (Full Scale) | V <sub>IN,</sub> V <sub>INB</sub><br>V <sub>IN</sub> - V <sub>INB</sub> | $50\Omega$ differential or single-ended                         | ±113<br>450 | ±125<br>500                                    | ±137<br>550 | mV<br>mVpp |

| Clock input power level                        | P <sub>CLK</sub> , P <sub>CLKB</sub>                                    | $50\Omega$ single-ended clock input                             | 3           | 4                                              | 10          | dBm        |

| Operating temperature range                    | TJ                                                                      | Commercial grade: "C" Industrial grade: "V" Military grade: "M" | -40         | < Tc; Tj < 9<br>) < Tc; Tj < 1<br>< Tc; Tj < + | 110         | °C         |

Electrical

Operating

Characteristics

$V_{EE}$  = DV<sub>EE</sub> = -5V;  $V_{CC}$  = +5V;  $V_{IN}$  -V<sub>INB</sub> = 500 mVpp Full Scale differential input;

Digital outputs 75 or  $50\Omega$  differentially terminated;

Tj (typical) =  $70^{\circ}$ C. Full Temperature Range: up to  $-55^{\circ}$ C < Tc; Tj <  $+125^{\circ}$ C.

Table 3. Electrical Specifications

|                              |         |                    | Test    |      | Value |      |      |      |

|------------------------------|---------|--------------------|---------|------|-------|------|------|------|

| Parameter                    |         | Symbol             | Level   | Min  | Тур   | Max  | Unit | Note |

| Power Requirements           |         |                    |         |      |       | •    |      |      |

| Positive supply voltage      |         |                    |         |      |       |      |      |      |

| A                            | Analog  | $V_{CC}$           | 1, 2, 6 | 4.7  | 5     | 5.3  | V    |      |

| Digital                      | (ECL)   | $V_{PLUSD}$        | 4       | _    | 0     | _    | V    |      |

| Digital (I                   | LVDS)   | $V_{PLUSD}$        | 4       | 1.4  | 2.4   | 2.6  | V    |      |

| Positive supply current      |         |                    |         |      |       |      |      |      |

| A                            | Analog  | $I_{CC}$           | 1, 2    | _    | 385   | 445  | mA   |      |

|                              |         |                    | 6       | _    | 395   | 445  | mA   |      |

|                              | Digital | I <sub>PLUSD</sub> | 1, 2    | _    | 115   | 145  | mA   |      |

|                              |         |                    | 6       | _    | 120   | 145  | mA   |      |

| Negative supply voltage      |         | $V_{EE}$           | 1, 2, 6 | -5.3 | -5    | -4.7 | V    |      |

| Negative supply current      |         |                    |         |      |       |      |      |      |

| A                            | Analog  | $AI_EE$            | 1, 2    | _    | 165   | 200  | mA   |      |

|                              |         |                    | 6       | _    | 170   | 200  | mA   |      |

|                              | Digital | $DI_EE$            | 1, 2    | _    | 135   | 180  | mA   |      |

|                              |         |                    | 6       | _    | 145   | 180  | mA   |      |

| Nominal power dissipation    |         | DD                 | 1, 2    |      | 3.4   | 4.1  | W    |      |

|                              |         | PD                 | 6       | _    | 3.6   | 4.3  | W    |      |

| Power supply rejection ratio |         | PSRR               | 4       | _    | 0.5   | 2    | mW   |      |

| Resolution                   |         |                    | _       | -    | 8     | _    | bits | (2)  |

Table 3. Electrical Specifications (Continued)

|                                                                                                                 |                                     | Test        |              | Value         |            |          |        |

|-----------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------|--------------|---------------|------------|----------|--------|

| Parameter                                                                                                       | Symbol                              | Level       | Min          | Тур           | Max        | Unit     | Note   |

| Analog Inputs                                                                                                   |                                     |             |              |               |            |          |        |

| Full Scale Input Voltage range (differential mode) (0V common mode voltage)                                     | V <sub>IN</sub><br>V <sub>INB</sub> | 4 –         | -125<br>-125 | _<br>_        | 125<br>125 | mV<br>mV |        |

| Full Scale Input Voltage range (single-ended input option) (See Application Notes)                              | V <sub>IN</sub><br>V <sub>INB</sub> | 4 –         | -250<br>–    | _<br>0        | 250<br>–   | mV<br>mV |        |

| Analog input capacitance                                                                                        | C <sub>IN</sub>                     | 4           | _            | 3             | 3.5        | pF       |        |

| Input bias current                                                                                              | I <sub>IN</sub>                     | 4           | _            | 10            | 20         | μΑ       |        |

| Input Resistance                                                                                                | R <sub>IN</sub>                     | 4           | 0.5          | 1             | _          | MΩ       |        |

| Full Power input Bandwidth                                                                                      | FPBW                                | 4           | 1.3          | 1.5           | _          | GHz      |        |

| Small signal input Bandwidth (10% full scale)                                                                   | SSBW                                | 4           | 1.5          | 1.7           | _          | GHz      |        |

| Clock Inputs                                                                                                    | <u>I</u>                            |             | <u>I</u>     | 1             |            |          |        |

| Logic compatibility for clock inputs (See Application Notes)                                                    | _                                   | _           |              | specified clo |            | _        | (10)   |

| ECL Clock inputs voltages (V <sub>CLK</sub> or V <sub>CLKB</sub> ):                                             | _                                   | 4           | _            | _             | _          | _        |        |

| Logic "0" voltage                                                                                               | V <sub>IL</sub>                     | _           | _            | _             | -1.5       | V        |        |

| Logic "1" voltage                                                                                               | V <sub>IH</sub>                     | _           | -1.1         | _             | _          | V        |        |

| Logic "0" current                                                                                               | I <sub>IL</sub>                     | _           | _            | 5             | 50         | μA       |        |

| Logic "1" current                                                                                               | I <sub>IH</sub>                     | _           | _            | 5             | 50         | μA       |        |

| Clock input power level into 50Ω termination                                                                    | _                                   | _           | (            | dBm into 50   | Ω          | _        |        |

| Clock input power level                                                                                         | _                                   | 4           | -2           | 4             | 10         | dBm      |        |

| Clock input capacitance                                                                                         | C <sub>CLK</sub>                    | 4           | _            | 3             | 3.5        | pF       |        |

| <b>Digital Outputs</b> Single-ended or differential input mode, 50% clock of Tj (typical) = 70°C.               | duty cycle (CLK                     | , CLKB), Bi | nary output  | data format   | ,          |          | (1)(6) |

| Logic compatibility for digital outputs (Depending on the value of V <sub>PLUSD</sub> ) (See Application Notes) | _                                   | _           | I            | ECL or LVD    | S          | _        |        |

| Differential output voltage swings (assuming $V_{PLUSD} = 0V$ ):                                                | _                                   | 4           | _            | _             | _          | _        |        |

| $75\Omega$ open transmission lines (ECL levels)                                                                 | _                                   | _           | 1.5          | 1.620         | _          | V        |        |

| $75\Omega$ differentially terminated                                                                            |                                     | _           | 0.70         | 0.825         | _          | V        |        |

| 50Ω differentially terminated                                                                                   | _                                   | _           | 0.54         | 0.660         | _          | V        |        |

| Output levels (assuming $V_{PLUSD} = 0V$ )<br>75 $\Omega$ open transmission lines:                              | _                                   | 4           | _            | _             | _          | _        | (6)    |

| 1 ' "0" 1                                                                                                       | V                                   | _           |              | -1.62         | -1.54      | V        |        |

| Logic "0" voltage                                                                                               | $V_{OL}$                            | _           | _            | -1.02         | -1.54      | V        |        |

Table 3. Electrical Specifications (Continued)

|                                                                                        |                      | Test       |                | Value          |                |                                      |        |

|----------------------------------------------------------------------------------------|----------------------|------------|----------------|----------------|----------------|--------------------------------------|--------|

| Parameter                                                                              | Symbol               | Level      | Min            | Тур            | Max            | Unit                                 | Note   |

| Output levels (assuming $V_{PLUSD} = 0V$ )<br>75 $\Omega$ differentially terminated:   | -                    | 4          | _              | _              | _              | _                                    | (6)    |

| Logic "0" voltage                                                                      | V <sub>OL</sub>      | _          | _              | -1.41          | -1.34          | V                                    |        |

| Logic "1" voltage                                                                      | V <sub>OH</sub>      | _          | -1.07          | -1             | _              | V                                    |        |

| Output levels (assuming $V_{PLUSD} = 0V$ )<br>50 $\Omega$ differentially terminated:   | _                    | _          | _              | _              | _              | _                                    | (6)    |

| Logic "0" voltage                                                                      | V <sub>OL</sub>      | 1, 2<br>6  | _<br>_         | -1.40<br>-1.40 | -1.32<br>-1.25 | V<br>V                               |        |

| Logic "1" voltage                                                                      | V <sub>OH</sub>      | 1, 2<br>6  | -1.16<br>-1.25 | -1.10<br>-1.10 | _<br>_         | V<br>V                               |        |

| Differential Output Swing                                                              | DOS                  | 4          | 270            | 300            | _              | mV                                   |        |

| Output level drift with temperature                                                    | _                    | 4          | _              | _              | 1.6            | mV/°C                                |        |

| <b>DC Accuracy</b> Single-ended or differential input mode, 50% c Tj (typical) = 70°C. | lock duty cycle (CLK | , CLKB), B | inary output   | data format    |                |                                      |        |

| Differential non linearity                                                             | DNL-                 | 1, 2<br>6  | -0.5<br>-0.6   | -0.25<br>-0.35 | _<br>_         | lsb<br>Isb                           | (2)(3) |

| Differential non linearity                                                             | DNL+                 | 1, 2<br>6  | _<br>_         | 0.3<br>0.4     | 0.6<br>0.7     | Isb<br>Isb                           |        |

| Integral non linearity                                                                 | INL-                 | 1, 2<br>6  | -1.0<br>-1.2   | 0.7<br>0.9     | _<br>_         | lsb<br>lsb                           | (2)(3) |

| Integral non linearity                                                                 | INL+                 | 1, 2<br>6  | _<br>_         | 0.7<br>0.9     | 1.0<br>1.2     | lsb<br>lsb                           |        |

| No missing code                                                                        | _                    | Gua        | ranteed ove    | er specified t | emperature     | range                                | (3)    |

| Gain error                                                                             | -                    | 1, 2<br>6  | -10<br>-11     | -2<br>-2       | 10<br>11       | % F <sub>S</sub><br>% F <sub>S</sub> |        |

| Input offset voltage                                                                   | _                    | 1, 2<br>6  | -26<br>-30     | -5<br>-5       | 26<br>30       | mV<br>mV                             |        |

| Gain error drift Offset error drift                                                    |                      | 4 4        | 100<br>40      | 125<br>50      | 150<br>60      | ppm/°C<br>ppm/°C                     |        |

| Transient Performance                                                                  | ,                    | +          |                | •              |                | •                                    |        |

| Bit Error Rate $F_S = 1 \text{ GSPS } F_{IN} = 62.5 \text{ MHz}$                       | BER                  | 4          | _              | _              | 1E-12          | Error/<br>sample                     | (2)(4) |

| ADC settling time $V_{IN} - V_{INB} = 400 \text{ mVpp}$                                | TS                   | 4          | _              | 0.5            | 1              | ns                                   | (2)    |

| Overvoltage recovery time                                                              | TOR                  | 4          | _              | 0.5            | 1              | ns                                   | (2)    |

Table 3. Electrical Specifications (Continued)

|                                                                                                                 |                   | Test        |            | Value        |             |      |      |

|-----------------------------------------------------------------------------------------------------------------|-------------------|-------------|------------|--------------|-------------|------|------|

| Parameter                                                                                                       | Symbol            | Level       | Min        | Тур          | Max         | Unit | Note |

| <b>AC Performance</b> Single-ended or differential input and clock mode, Tj = 70°C, unless otherwise specified. | 50% clock duty of | cycle (CLK, | CLKB), Bin | ary output d | ata format, |      |      |

| Signal to Noise and Distortion ratio                                                                            |                   | _           | _          | _            | _           | _    | (2)  |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 20 MHz                                                               |                   | 4           | 42         | 44           | _           | dB   |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 500 MHz                                                              | SINAD             | 4           | 41         | 43           | _           | dB   |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 1000 MHz (-1 dBFs)                                                   |                   | 4           | 38         | 40           | _           | dB   |      |

| F <sub>S</sub> = 50 MSPS, F <sub>IN</sub> = 25 MHz                                                              |                   | 1, 2, 6     | 40         | 44           | _           | dB   |      |

| Effective Number Of Bits                                                                                        |                   | _           | _          | _            | _           | _    |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 20 MHz                                                               |                   | 4           | 7.0        | 7.2          | _           | Bits |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 500 MHz                                                              | ENOB              | 4           | 6.6        | 6.8          | _           | Bits |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 1000 MHz (-1 dBFs)                                                   |                   | 4           | 6.2        | 6.4          | _           | Bits |      |

| F <sub>S</sub> = 50 MSPS, F <sub>IN</sub> = 25 MHz                                                              |                   | 1, 2, 6     | 7.0        | 7.2          | _           | Bits |      |

| Signal to Noise Ratio                                                                                           |                   | _           | _          | _            | _           | _    | (2)  |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 20 MHz                                                               |                   | 4           | 42         | 45           | _           | dB   |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 500 MHz                                                              | SNR               | 4           | 41         | 44           | _           | dB   |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 1000 MHz (-1 dBFs)                                                   |                   | 4           | 41         | 44           | _           | dB   |      |

| F <sub>S</sub> = 50 MSPS, F <sub>IN</sub> = 25 MHz                                                              |                   | 1, 2, 6     | 44         | 45           | _           | dB   |      |

| Total Harmonic Distortion                                                                                       |                   | _           | _          | _            | _           | _    | (2)  |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 20 MHz                                                               |                   | 4           | 50         | 54           | _           | dB   |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 500 MHz                                                              | THD               | 4           | 46         | 50           | _           | dB   |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 1000 MHz (-1 dBFs)                                                   |                   | 4           | 42         | 46           | _           | dB   |      |

| F <sub>S</sub> = 50 MSPS, F <sub>IN</sub> = 25 MHz                                                              |                   | 1, 2, 6     | 46         | 45           | _           | dB   |      |

| Spurious Free Dynamic Range                                                                                     |                   | _           | _          | _            | _           | _    | (2)  |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 20 MHz                                                               |                   | 4           | 52         | 57           | _           | dBc  |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 500 MHz                                                              | 0500              | 4           | 47         | 52           | _           | dBc  |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 1000 MHz (-1 dBFs)                                                   | SFDR              | 4           | 42         | 47           | _           | dBc  |      |

| F <sub>S</sub> = 1 GSPS, F <sub>IN</sub> = 1000 MHz (-3 dBFs)                                                   |                   | 4           | 45         | 50           | _           | dBc  |      |

| F <sub>S</sub> = 50 MSPS, F <sub>IN</sub> = 25 MHz                                                              |                   | 1, 2, 6     | 40         | 54           | _           | dBc  |      |

| Two-tone Inter-modulation Distortion                                                                            |                   | 4           | _          | _            | _           | _    | (2)  |

| $F_{IN1}$ = 489 MHz at $F_S$ = 1 GSPS,<br>$F_{IN2}$ = 490 MHz at $F_S$ = 1 GSPS                                 | IMD               | _           | -47        | -52          | _           | dBc  |      |

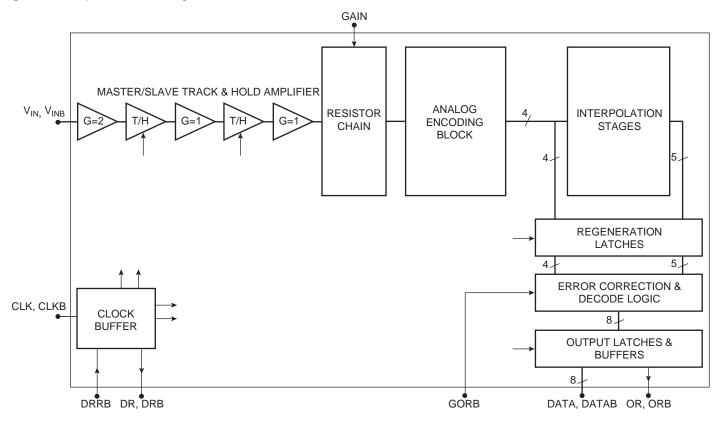

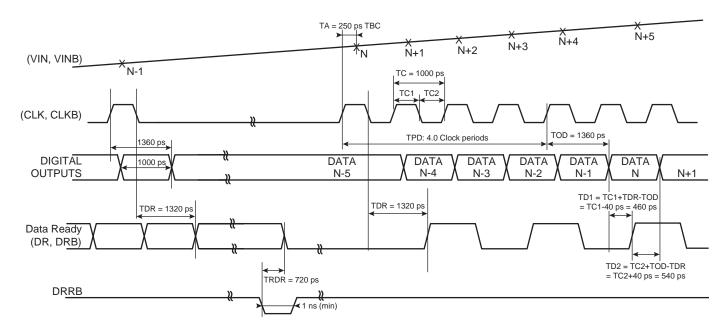

| Switching Performance and Charcteristics – S                                                                    | ee Figure 2 and   | Figure 3 o  | n page 9   |              |             |      |      |

| Maximum clock frequency                                                                                         | F <sub>S</sub>    | _           | 1          | _            | 1.4         | GSPS | (14) |

| Minimum clock frequency                                                                                         | F <sub>S</sub>    | 4           | 10         | _            | 50          | MSPS | (15) |

| Minimum Clock pulse width (high)                                                                                | TC1               | 4           | 0.280      | 0.500        | 50          | ns   |      |

Table 3. Electrical Specifications (Continued)

|                                                                                               |         | Test  |       | Value |      |                 |                     |

|-----------------------------------------------------------------------------------------------|---------|-------|-------|-------|------|-----------------|---------------------|

| Parameter                                                                                     | Symbol  | Level | Min   | Тур   | Max  | Unit            | Note                |

| Minimum Clock pulse width (low)                                                               | TC2     | 4     | 0.350 | 0.500 | 50   | ns              |                     |

| Aperture delay                                                                                | Та      | 4     | 100   | +250  | 400  | ps              | (2)                 |

| Aperture uncertainty                                                                          | Jitter  | 4     | _     | 0.4   | 0.6  | ps (rms)        | (2)(5)              |

| Data output delay                                                                             | TDO     | 4     | 1150  | 1360  | 1660 | ps              | (2)(10)<br>(11)(12) |

| Output rise/fall time for DATA (20% – 80%)                                                    | TR/TF   | 4     | 250   | 350   | 550  | ps              | (11)                |

| Output rise/fall time for DATA READY (20% – 80%)                                              | TR/TF   | 4     | 250   | 350   | 550  | ps              | (11)                |

| Data ready output delay                                                                       | TDR     | 4     | 1110  | 1320  | 1620 | ps              | (2)(10)<br>(11)(12) |

| Data ready reset delay                                                                        | TRDR    | 4     | _     | 720   | 1000 | ps              |                     |

| Data to data ready – Clock low pulse width (See "Timing Diagrams" on page 9.)                 | TOD-TDR | 4     | 0     | 40    | 80   | ps              | (9)(13)<br>(14)     |

| Data to data ready output delay (50% duty cycle) at 1 GSPS (See "Timing Diagrams" on page 9.) | TD1     | 4     | 420   | 460   | 500  | ps              | (2)(15)             |

| Data pipeline delay                                                                           | TPD     | 4     |       | 4     |      | clock<br>cycles |                     |

Notes: 1. Differential output buffers are internally loaded by 75 $\Omega$  resistors. Buffer bias current = 11 mA.

- 2. See "Definition of Terms" on page 41.

- 3. Histogram testing based on sampling of a 10 MHz sinewave at 50 MSPS.

- 4. Output error amplitude < ± 4 lsb around correct code (including gain and offset error).

- 5. Maximum jitter value obtained for single-ended clock input on the JTS8388B die (chip on board): 200 fs. (500 fs expected on TS8388BG)

- 6. Digital output back termination options depicted in Application Notes.

- 7. With a typical value of TD = 465 ps, at 1 GSPS, the timing safety margin for the data storing using the ECLinPS 10E452 output registers from Motorola<sup>®</sup> is of ± 315 ps, equally shared before and after the rising edge of the Data Ready signals (DR, DRB).

- 8. The clock inputs may be indifferently entered in differential or single-ended, using ECL levels or 4 dBm typical power level into the  $50\Omega$  termination resistor of the inphase clock input. (4 dBm into  $50\Omega$  clock input correspond to 10 dBm power level for the clock generator.)

- 9. At 1 GSPS, 50/50 clock duty cycle, TC2 = 500 ps (TC1). TDR TOD = -100 ps (typ) does not depend on the sampling rate.

- 10. Specified loading conditions for digital outputs:

- $50\Omega$  or  $75\Omega$  controlled impedance traces properly  $50/75\Omega$  terminated, or unterminated  $75\Omega$  controlled impedance traces.

- Controlled impedance traces far end loaded by 1 standard ECLinPS register from Motorola. (i.e.: 10E452) (Typical input parasitic capacitance of 1.5 pF including package and ESD protections.)

- 11. Termination load parasitic capacitance derating values:

- $50\Omega$  or  $75\Omega$  controlled impedance traces properly  $50/75\Omega$  terminated: 60 ps/pF or 75 ps per additionnal ECLinPS load.

- Unterminated (source terminated) 75 $\Omega$  controlled impedance lines: 100 ps/pF or 150 ps per additionnal ECLinPS termination load.

- 12. Apply proper  $50/75\Omega$  impedance traces propagation time derating values: 6 ps/mm (155 ps/inch) for TSEV8388BF Evaluation Board.

- 13. Values for TOD and TDR track each other over temperature, (1% variation for TOD-TDR per 100°C temperature variation). Therefore TOD-TDR variation over temperature is negligible. Moreover, the internal (on-chip) and package skews between each Data TODs and TDR effect can be considered as negligible. Consequently, minimum values for TOD and TDR are never more than 100 ps apart. The same is true for the TOD and TDR maximum values (see Advanced Application Notes about "TOD-TDR Variation Over Temperature" on page 23).

- 14. Min value guarantees performance. Max value guarantees functionality.

- 15. Min value guarantees functionality. Max value guarantees performance.

#### **Timing Diagrams**

Figure 2. TS8388BF Timing Diagram (1 GSPS Clock Rate), Data Ready Reset, Clock Held at LOW Level

Figure 3. TS8388BF Timing Diagram (1 GSPS Clock Rate), Data Ready Reset, Clock Held at HIGH Level

### **Explanation of Test Levels**

Table 4. Explanation of Test Levels

| Num | Characteristics                                                                                                                                   |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | 100% production tested at +25°C <sup>(1)</sup> (for "C" Temperature range <sup>(2)</sup> ).                                                       |

| 2   | 100% production tested at +25°C <sup>(1)</sup> , and sample tested at specified temperatures (for "V" and "M" Temperature range <sup>(2)</sup> ). |

| 3   | Sample tested only at specified temperatures.                                                                                                     |

| 4   | Parameter is guaranteed by design and characterization testing (thermal steady-state conditions at specified temperature).                        |

| 5   | Parameter is a typical value only.                                                                                                                |

| 6   | 100% production tested over specified temperature range (for "B/Q" Temperature range <sup>(2)</sup> ).                                            |

- Notes: 1. Unless otherwise specified, all tests are pulsed tests: therefore Tj = Tc = Ta, where Tj, Tc and Ta are junction, case and ambient temperature respectively.

- 2. Refer to "Ordering Information" on page 43.

- 3. Only MIN and MAX values are guaranteed (typical values are issuing from characterization results).

### **Functions Description**

Table 5. Functions Description

| Name                                    | Function                                                               |                        |                         |                                                          |

|-----------------------------------------|------------------------------------------------------------------------|------------------------|-------------------------|----------------------------------------------------------|

| V <sub>CC</sub>                         | Positive power supply                                                  |                        | VPLUSD                  | = +0V (ECL)                                              |

| V <sub>EE</sub> V <sub>PLUSD</sub> GND  | Analog negative power supply  Digital positive power supply  Ground    | VCC =                  | +5V VPLUSD =            | +2.4V (LVDS)                                             |

| V <sub>IN</sub> , V <sub>INB</sub>      | Differential analog inputs  Differential clock inputs                  | VIN→<br>VINB→          |                         | → OR<br>→ ORB                                            |

| <d0:d7><br/><d0b:d7b></d0b:d7b></d0:d7> | Differential output data port                                          | CLK→<br>CLKB→<br>GAIN→ | TS8388BF                | $ \begin{array}{c}                                     $ |

| DR, DRB                                 | Differential data ready outputs                                        | GORG→                  |                         | → DR<br>→ DRB                                            |

| OR, ORB                                 | Out of range outputs                                                   | DIOD/→                 |                         | → DRB                                                    |

| GAIN                                    | ADC gain adjust                                                        | DRRB                   |                         |                                                          |

| GORB                                    | Gray or Binary digital output select                                   |                        |                         |                                                          |

| DIOD/DRRB                               | Die junction temperature measurement/<br>asynchronous data ready reset | DVEE = -5              | i i i<br>V VEE = -5V GN | ID                                                       |

# Digital Output Coding

NRZ (Non Return to Zero) mode, ideal coding: does not include gain, offset, and linearity voltage errors.

Table 6. Digital Output Coding

|                              |                                                                | Digital C                          | Output                             |              |

|------------------------------|----------------------------------------------------------------|------------------------------------|------------------------------------|--------------|

| Differential<br>Analog Input | Voltage Level                                                  | Binary<br>GORB = VCC or Floating   | Gray<br>GORB = GND                 | Out of Range |

| > +251 mV                    | > Positive full scale + 1/2 lsb                                | 1111111                            | 1000000                            | 1            |

| +251 mV<br>+249 mV           | Positive full scale + 1/2 lsb<br>Positive full scale - 1/2 lsb | 1111111<br>1111110                 | 10000000<br>10000001               | 0            |

| +126 mV<br>+124 mV           | Positive 1/2 scale + 1/2 lsb<br>Positive 1/2 scale - 1/2 lsb   | 1 1 0 0 0 0 0 0<br>1 0 1 1 1 1 1 1 | 10100000<br>11100000               | 0            |

| +1 mV<br>-1 mV               | Bipolar zero + 1/2 lsb<br>Bipolar zero - 1/2 lsb               | 10000000                           | 1 1 0 0 0 0 0 0<br>0 1 0 0 0 0 0 0 | 0            |

| -124 mV<br>-126 mV           | Negative 1/2 scale + 1/2 lsb<br>Negative 1/2 scale - 1/2 lsb   | 0100000<br>00111111                | 01100000<br>00100000               | 0            |

| -249 mV<br>-251 mV           | Negative full scale + 1/2 lsb<br>Negative full scale - 1/2 lsb | 0000001                            | 0000001                            | 0            |

| < -251 mV                    | < Negative full scale - 1/2 lsb                                | 0000000                            | 0000000                            | 1            |

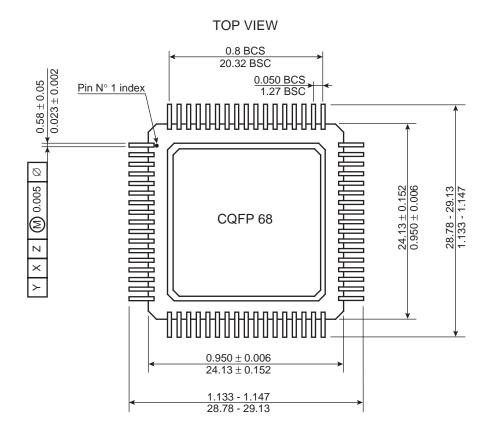

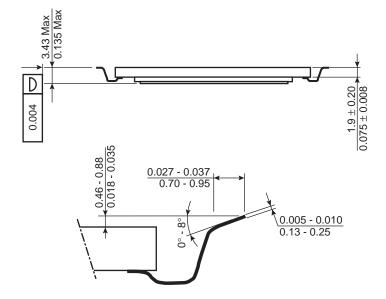

### **Package Description**

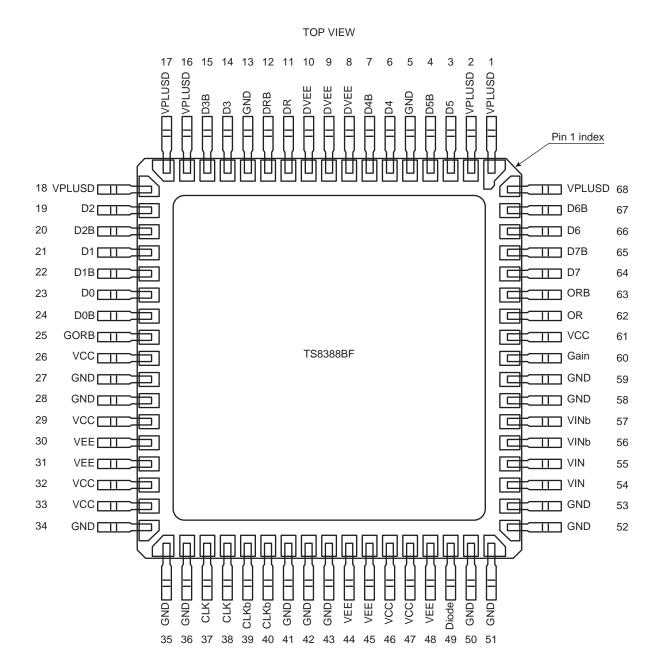

### **Pin Description**

Table 7. TS8388BF Pin Description

| Symbol                                    | Pin number                                     | Function                                                                                                                                                                     |

|-------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                                       | 5, 13, 27, 28, 34, 35, 36, 41, 42, 43, 50, 51, | Ground pins.                                                                                                                                                                 |

|                                           | 52, 53, 58, 59                                 | To be connected to external ground plane.                                                                                                                                    |

| V <sub>PLUSD</sub>                        | 1, 2, 16, 17, 18, 68                           | Digital positive supply (0V for ECL compatibility, 2.4V for LVDS compatibility). (2)                                                                                         |

| V <sub>cc</sub>                           | 26, 29, 32, 33, 46, 47, 61                     | +5V positive supply.                                                                                                                                                         |

| V <sub>EE</sub>                           | 30, 31, 44, 45, 48                             | -5V analog negative supply.                                                                                                                                                  |

| DV <sub>EE</sub>                          | 8, 9, 10                                       | -5V digital negative supply.                                                                                                                                                 |

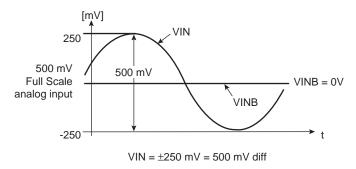

| V <sub>IN</sub>                           | 54 <sup>(1)</sup> , 55                         | In phase (+) analog input signal of the Sample and Hold differential preamplifier.                                                                                           |

| V <sub>INB</sub>                          | 56, 57 <sup>(1)</sup>                          | Inverted phase (-) of analog input signal (V <sub>IN</sub> ).                                                                                                                |

| CLK                                       | 37 <sup>(1)</sup> , 38                         | In phase (+) ECL clock input signal. The analog input is sampled and held on the rising edge of the CLK signal.                                                              |

| CLKB                                      | 39, 40 <sup>(1)</sup>                          | Inverted phase (-) of ECL clock input signal (CLK).                                                                                                                          |

| D0, D1, D2, D3, D4,<br>D5, D6, D7         | 23, 21, 19, 14, 6, 3, 66, 64                   | In phase (+) digital outputs. B0 is the LSB. B7 is the MSB.                                                                                                                  |

| D0B, D1B, D2B, D3B,<br>D4B, D5B, D6B, D7B | 24, 22, 20, 15, 7, 4, 67, 65                   | Inverted phase (-) digital outputs. B0B is the inverted LSB. B7B is the inverted MSB.                                                                                        |

| OR                                        | 62                                             | In phase (+) Out of Range Bit. Out of Range is high on the leading edge of code 0 and code 256.                                                                              |

| ORB                                       | 63                                             | Inverted phase (+) Out of Range Bit (OR).                                                                                                                                    |

| DR                                        | 11                                             | In phase (+) output of Data Ready Signal.                                                                                                                                    |

| DRB                                       | 12                                             | Inverted phase (-) output of Data Ready Signal (DR).                                                                                                                         |

| GORB                                      | 25                                             | Gray or Binary select output format control pin.  - Binary output format if GORB is floating or V <sub>CC</sub> .  - Gray output format if GORB is connected at ground (0V). |

| GAIN                                      | 60                                             | ADC gain adjust pin.                                                                                                                                                         |

| DIOD/DRRB                                 | 49                                             | This pin has a double function (can be left open or grounded if not used): - DIOD: die junction temperature monitoring pin DRRB: asynchronous data ready reset function.     |

- Notes: 1. Following pin numbers 37 (CLK), 40 (CLKB), 54 ( $V_{IN}$ ) and 57 ( $V_{INB}$ ) have to be connected to GND through a  $50\Omega$  resistor as close as possible to the package (50 $\Omega$  termination preferred option).

- 2. The common mode level of the output buffers is 1.2V below the positive digital supply. For ECL compatibility the positive digital supply must be set at 0V (ground). For LVDS compatibility (output common mode at +1.2V) the positive digital supply must be set at 2.4V. If the subsequent LVDS circuitry can withstand a lower level for input common mode, it is recommended to lower the positive digital supply level in the same proportion in order to spare power dissipation.

#### **TS8388BF Pinout**

Figure 4. TS8388BF Pinout

### Typical Characterization Results

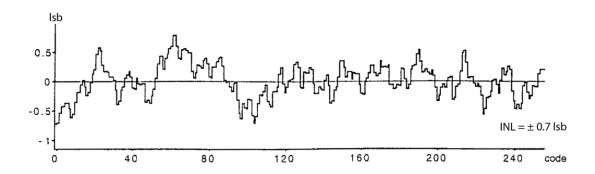

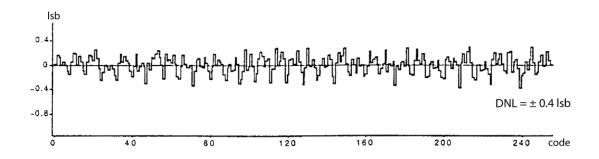

**Static Linearity**

$F_S = 50 \text{ MSPS/F}_{IN} = 10 \text{ MHz}$

Figure 5. Integral Non Linearity

Note: Clock Frequency = 50 MSPS; Signal Frequency = 10 MHz; Positive peak: 0.78 lsb; Negative peak: -0.73 lsb

Figure 6. Differential Non Linearity

Note: Clock Frequency = 50 MSPS; Signal Frequency = 10 MHz; Positive peak: 0.3 lsb; Negative peak: -0.39 lsb

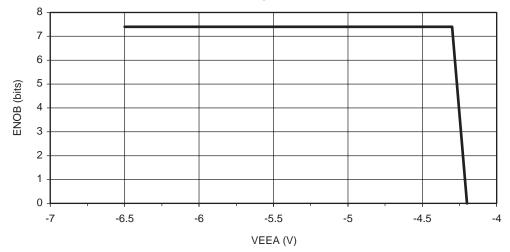

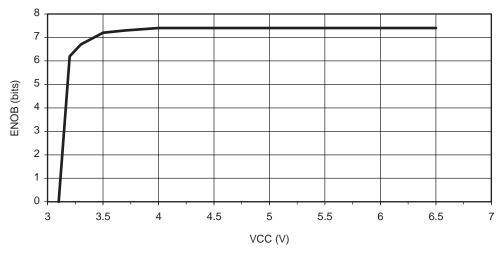

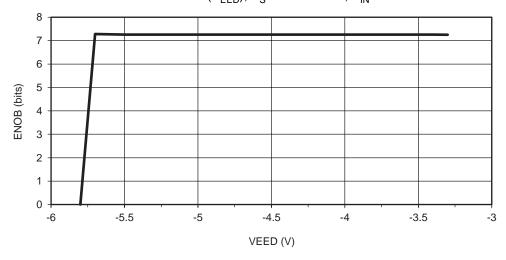

Effective Number of Bits Versus Power Supplies Variation

**Figure 7.** Effective Number of Bits = f ( $V_{EEA}$ );  $F_S = 500$  MSPS;  $F_{IN} = 100$  MHz

**Figure 8.** Effective Number of Bits = f ( $V_{CC}$ );  $F_S = 500$  MSPS;  $F_{IN} = 100$  MHz

**Figure 9.** Effective Number of Bits = f ( $V_{EED}$ );  $F_S = 500$  MSPS;  $F_{IN} = 100$  MHz

### **Typical FFT Results**

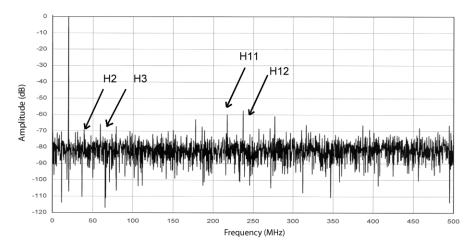

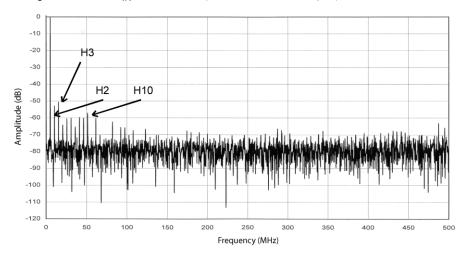

Figure 10.  $F_S = 1$  GSPS;  $F_{IN} = 20$  MHz

## Single Ended or differential

Fs =1 GSPS Fin = 20 MHz

Eff. Bits =7.2 SINAD = 44.3 dB SNR = 44.7dB THD = -54dBc SFDR = -57 dBc

Binary output coding

clock duty cycle = 50 %

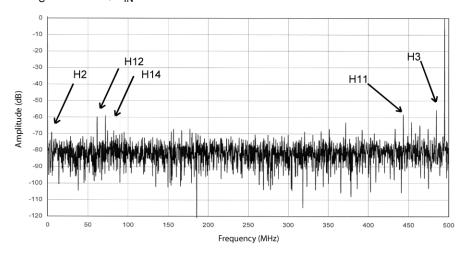

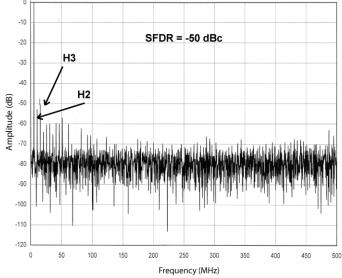

Figure 11.  $F_S = 1$  GSPS;  $F_{IN} = 495$  MHz

## Single Ended or differential

Fs =1 GSPS Fin=495MHz

Eff. Bits =6.8 SINAD =43 dB SNR = 44.1 dB THD = -50 dBc SFDR= -52 dBc

Binary output coding

clock duty cycle = 50 %

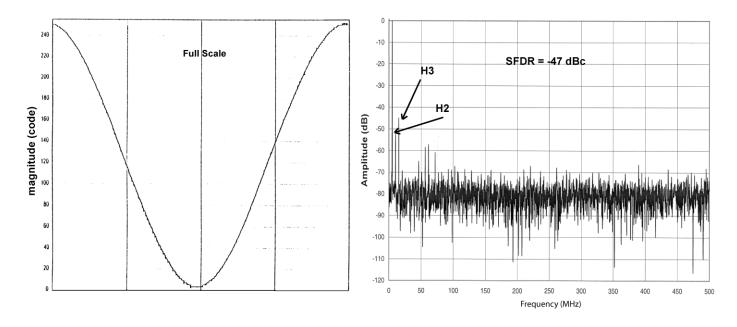

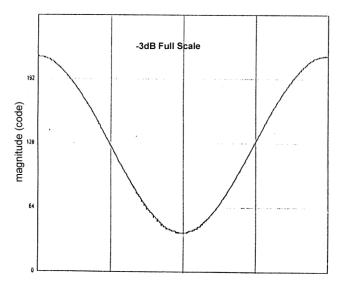

Figure 12.  $F_S = 1$  GSPS;  $F_{IN} = 995$  MHz (-3 dB Full Scale Input)

## Single Ended or differential

Fs =1 GSPS Fin=995 MHz

Eff. Bits =6.6 SINAD =40.8 dB SNR = 44 dB THD = -48 dBc SFDR= -50 dBc

Binary output coding clock duty cycle = 50 %

Spurious Free Dynamic Range Versus Input Amplitude

**Figure 13.** Sampling Frequency:  $F_S = 1$  GSPS; Input Frequency  $F_{IN} = 995$  MHz; Full Scale; ENOB = 6.4; SINAD = 40 dB; SNR = 44 dB; THD = -46 dBc; SFDR = -47 dBc; Gray or Binary Output Coding

**Figure 14.** Sampling Frequency:  $F_S = 1$  GSPS; Input Frequency  $F_{IN} = 995$  MHz; -3 dB Full Scale; ENOB = 6.6; SINAD = 40.8 dB; SNR = 44 dB; THD = -48 dBc; SFDR = -50 dBc; Gray or Binary Output Coding

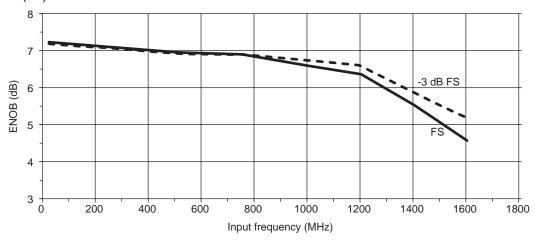

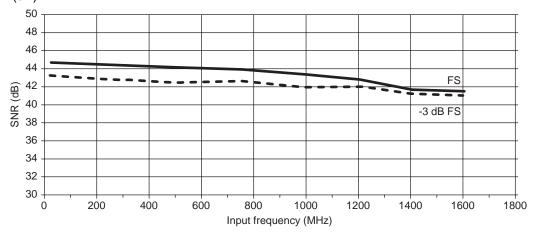

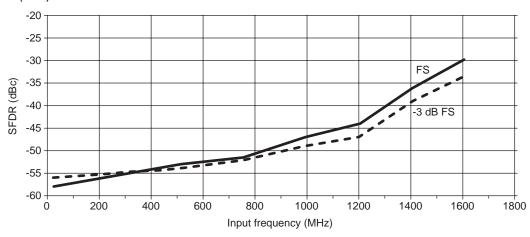

Dynamic Performance Versus Analog Input Frequency  $F_S = 1$  GSPS,  $F_{IN} = 0$  up to 1600 MHz, Full Scale input ( $F_S$ ),  $F_S$  -3 dB

Clock duty cycle 50/50, Binary/Gray output coding, fully differential or single-ended analog and clock inputs.

Figure 15. ENOB (dB)

Figure 16. SNR (dB)

Figure 17. SFDR (dBc)

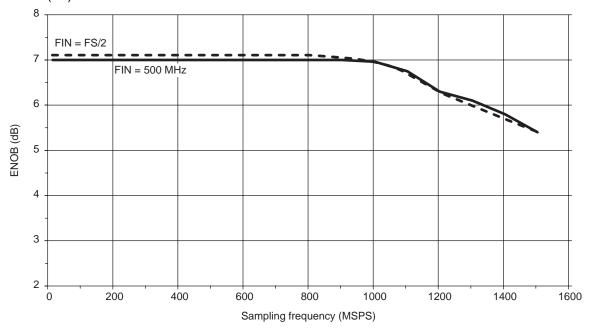

Effective Number of Bits (ENOB) Versus Sampling Frequency

Analog Input Frequency:  $F_{IN} = 495$  MHz and Nyquist conditions ( $F_{IN} = F_{S}/2$ ) Clock duty cycle 50/50, Binary output coding

Figure 18. ENOB (dB)

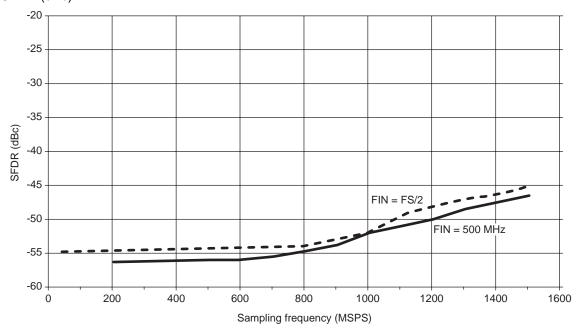

SFDR Versus Sampling Frequency

Analog Input Frequency:  $F_{IN} = 495$  MHz and Nyquist conditions ( $F_{IN} = F_{S}/2$ )

Clock duty cycle 50/50, Binary output coding

Figure 19. SFDR (dBc)

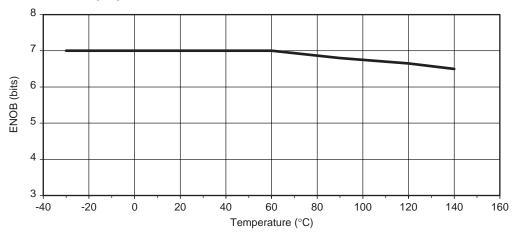

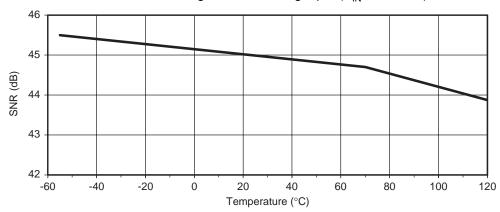

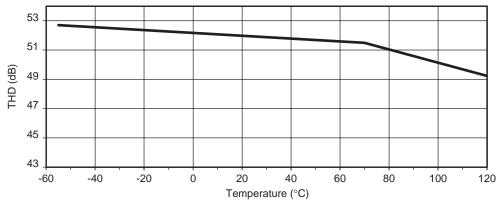

### TS8388BF ADC Performances Versus Junction Temperature

**Figure 20.** Effective Number of Bits Versus Junction Temperature  $F_S = 1$  GSPS;  $F_{IN} = 500$  MHz; Duty Cycle = 50%

**Figure 21.** Signal to Noise Ratio Versus Junction Temperature  $F_S = 1$  GSPS;  $F_{IN} = 507$  MHz; Differential Clock; Single-ended Analog Input ( $V_{IN} = -1$  dBFs)

**Figure 22.** Total Harmonic Distorsion Versus Junction Temperature  $F_S = 1$  GSPS;  $F_{IN} = 507$  MHz; Differential Clock; Single-ended Analog Input ( $V_{IN} = -1$  dBFs)

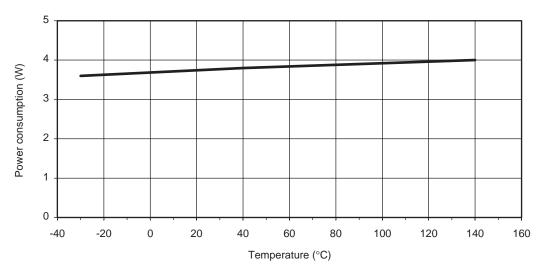

**Figure 23.** Power Consumption Versus Junction Temperature  $F_S = 1$  GSPS;  $F_{IN} = 500$  MHz; Duty Cycle = 50%

# Typical Full Power Input Bandwidth

Figure 24. 1.5 GHz at -3 dB (-2 dBm Full Power Input)

# **ADC Step** Response

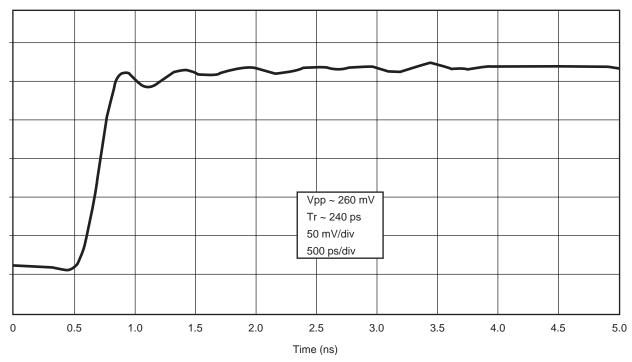

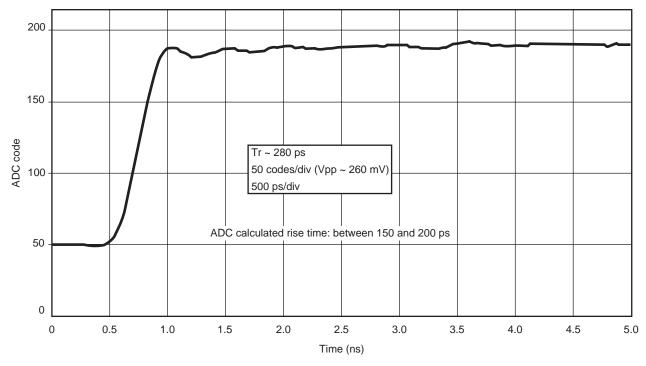

Test pulse input characteristics: 20% to 80% input full scale and rise time ~ 200 ps.

Note: This step response was obtained with the TSEV8388B chip on-board (device in die form).

Figure 25. Test Pulse Digitized with 20 GHz DSO

Figure 26. Same Test Pulse Digitized with TS8388BF ADC

Note: Ripples are due to the test setup (they are present on both measurements).

### TS8388BF Main Features

# Timing Information

## Timing Value for TS8388BF

Timing values as defined in Table 3 on page 4 are advanced data, issued from electric simulations and first characterizations results fitted with measurements.

Timing values are given at CQFP68 package inputs/outputs, taking into account package internal controlled impedance traces propagation delays, gullwing pin model, and specified termination loads.

Propagation delays in  $50/75\Omega$  impedance traces are NOT taken into account for TOD and TDR.

Apply proper derating values corresponding to termination topology.

The min/max timing values are valid over the full temperature range in the following conditions:

- Specified Termination Load (Differential output Data and Data Ready): 50Ω resistor in parallel with 1 standard ECLinPS register from Motorola (i.e.: 10E452) Typical ECLinPS inputs shows a typical input capacitance of 1.5 pF (including package and ESD protections).

- If addressing an output Dmux, take care if some Digital outputs do not have the same termination load and apply corresponding derating value given below.

- Output Termination Load derating values for TOD and TDR:

- ~ 35 ps/pF or 50 ps per additional ECLinPS load.

- Propagation time delay derating values have also to be applied for TOD and TDR:

- ~ 6 ps/mm (155 ps/inch) for TSEV8388B Evaluation Board.

- Apply proper time delay derating value if a different dielectric layer is used.

# Propagation Time Considerations

TOD and TDR Timing values are given from pin to pin and DO NOT include the additional propagation times between device pins and input/output termination loads. For the TSEV8388B Evaluation Board, the propagation time delay is 6 ps/mm (155 ps/inch) corresponding to 3.4 (at 10 GHz) dielectric constant of the RO4003 used for the Board.

If a different dielectric layer is used (for instance Teflon), please use appropriate propagation time values.

TD does NOT depend on propagation times because it is a differential data (TD is the time difference between Data Ready output delay and digital Data output delay).

TD is also the most straightforward data to measure, again because it is differential: TD can be measured directly onto termination loads, with matched Oscilloscopes probes.

# TOD-TDR Variation Over Temperature

Values for TOD and TDR track each other over temperature (1% variation for TOD-TDR per 100°C temperature variation).

Therefore TOD-TDR variation over temperature is negligible. Moreover, the internal (on-chip) and package skews between each Data TODs and TDR effect can be considered as negligible.

Consequently, minimum values for TOD and TDR are never more than 100 ps apart. The same is true for the TOD and TDR maximum values.

#### In other terms:

- If TOD is at 1150 ps, TDR will not be at 1620 ps (maximum time delay for TDR).

- If TOD is at 1660 ps, TDR will not be at 1110 ps (minimum time delay for TDR).

However, external TOD-TDR values may be dictated by total digital datas skews between every TODs (each digital data) and TDR: MCM Board, bonding wires and output lines lengths differences, and output termination impedance mismatches.

The external (on board) skew effect has NOT been taken into account for the specification of the minimum and maximum values for TOD-TDR.

#### **Principle of Operation**

The Analog input is sampled on the rising edge of external clock input (CLK, CLKB) after TA (aperture delay) of typically 250 ps. The digitized data is available after 4 clock periods latency (pipeline delay (TPD)), on clock rising edge, after 1360 ps typical propagation delay TOD.

The Data Ready differential output signal frequency (DR, DRB) is half the external clock frequency, that is it switches at the same rate as the digital outputs.

The Data Ready output signal (DR, DRB) switches on external clock falling edge after a propagation delay TDR of typically 1320 ps.

A Master Asynchronous Reset input command DRRB (ECL compatible single-ended input) is available for initializing the differential Data Ready output signal (DR, DRB). This feature is mandatory in certain applications using interleaved ADCs or using a single ADC with demultiplexed outputs. Actually, without Data Ready signal initialization, it is impossible to store the output digital datas in a defined order.

### Principle of Data Ready Signal Control by DRRB Input Command

# Data Ready Output Signal Reset

The Data Ready signal is reset on falling edge of DRRB input command, on ECL logical low level (-1.8V). DRRB may also be tied to  $V_{EE} = -5V$  for Data Ready output signal Master Reset. So long DRRB remains at logical low level, (or tied to  $V_{EE} = -5V$ ), the Data Ready output remains at logical zero and is independent of the external free running encoding clock.

The Data Ready output signal (DR, DRB) is reset to logical zero after TRDR = 920 ps typical.

TRDR is measured between the -1.3V point of the falling edge of DRRB input command and the zero crossing point of the differential Data Ready output signal (DR, DRB).

The Data Ready Reset command may be a pulse of 1 ns minimum time width.

# Data Ready Output Signal Restart

The Data Ready output signal restarts on DRRB command rising edge, ECL logical high levels (-0.8V). DRRB may also be Grounded, or is allowed to float, for normal free running Data Ready output signal.

The Data Ready signal restart sequence depends on the logical level of the external encoding clock, at DRRB rising edge instant:

- The DRRB rising edge occurs when external encoding clock input (CLK, CLKB) is LOW: The Data Ready output first rising edge occurs after half a clock period on the clock falling edge, after a delay time TDR = 1320 ps already defined hereabove.

- The DRRB rising edge occurs when external encoding clock input (CLK, CLKB) is HIGH:

The Data Ready output first rising edge occurs after one clock period on the clock falling edge, and a delay TDR = 1320 ps.

Consequently, as the analog input is sampled on clock rising edge, the first digitized data corresponding to the first acquisition (N) after Data Ready signal restart (rising edge) is always strobed by the third rising edge of the data ready signal.

The time delay (TD1) is specified between the last point of a change in the differential output data (zero crossing point) to the rising or falling edge of the differential Data Ready signal (DR, DRB) (zero crossing point).

For normal initialization of Data Ready output signal, the external encoding clock signal frequency and level must be controlled. It is reminded that the minimum encoding clock sampling rate for the ADC is 10 MSPS and consequently the clock cannot be stopped.

One single pin is used for both DRRB input command and die junction temperature monitoring. Pin denomination will be DRRB/DIOD. On the former version denomination was DIOD. Temperature monitoring and Data Ready control by DRRB is not possible simultaneously.

# Analog Inputs (V<sub>IN</sub>) (V<sub>INB</sub>)

The analog input Full Scale range is 0.5V peak to peak (Vpp), or -2 dBm into the  $50\Omega$  termination resistor.

In differential mode input configuration, that means 0.25V on each input, or  $\pm 125$  mV around 0V. The input common mode is GROUND.

The typical input capacitance is 3 pF for TS8388B in CQFP package.

The input capacitance is mainly due to the package. The ESD protections are not connected (but present) on the inputs.

# Differential Inputs Voltage Span

Figure 27. Differiential Inputs Voltage Span

#### Differential Versus Single-ended Analog Input Operation

The TS8388BF can operate at full speed in either differential or single-ended configuration.

This is explained by the fact the ADC uses a high input impedance differential preamplifier stage, (preceding the Sample and hold stage), which has been designed in order to be entered either in differential mode or single-ended mode.

This is true so long as the out-of-phase analog input pin  $V_{INB}$  is  $50\Omega$  terminated very closely to one of the neighboring shield ground pins (52, 53, 58, 59) which constitute the local ground reference for the inphase analog input pin ( $V_{IN}$ ).

Thus the differential analog input preamplifier will fully reject the local ground noise (and any capacitively and inductively coupled noise) as common mode effects.

In typical single-ended configuration, enter on the  $(V_{IN})$  input pin, with the inverted phase input pin  $(V_{INB})$  grounded through the  $50\Omega$  termination resistor.

In single-ended input configuration, the in-phase input amplitude is 0.5V peak to peak, centered on 0V (or -2 dBm into  $50\Omega$ ). The inverted phase input is at ground potential through the  $50\Omega$  termination resistor.

However, dynamic performances can be somewhat improved by entering either analog or clock inputs in differential mode.

#### Typical Single-ended Analog Input Configuration

Figure 28. Typical Single-ended Analog Input Configuration

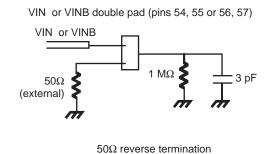

# Clock Inputs (CLK) (CLKB)

The TS8388BF can be clocked at full speed without noticeable performance degradation in either differential or single-ended configuration.

This is explained by the fact the ADC uses a differential preamplifier stage for the clock buffer, which has been designed in order to be entered either in differential or single-ended mode.

Recommended sinewave generator characteristics are typically -120 dBc/Hz phase noise floor spectral density, at 1 kHz from carrier, assuming a single tone 4 dBm input for the clock signal.

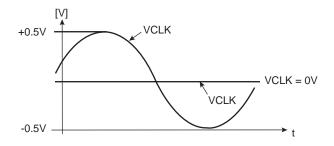

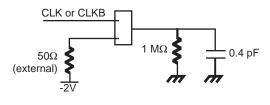

Single-ended Clock Input (Ground Common Mode) Although the clock inputs were intended to be driven differentially with nominal -0.8V/-1.8V ECL levels, the TS8388BF clock buffer can manage a single-ended sinewave clock signal centered around 0V. This is the most convenient clock input configuration as it does not require the use of a power splitter.

No performance degradation (i.e.: due to timing jitter) is observed in this particular single-ended configuration up to 1.2 GSPS Nyquist conditions ( $F_{IN} = 600 \text{ MHz}$ ).

This is true so long as the inverted phase clock input pin is  $50\Omega$  terminated very closely to one of the neighboring shield ground pins, which constitutes the local Ground reference for the inphase clock input.

Thus the TS8388BF differential clock input buffer will fully reject the local ground noise (and any capacitively and inductively coupled noise) as common mode effects. Moreover, a very low phase noise sinewave generator must be used for enhanced jitter performance.

The typical inphase clock input amplitude is 1V peak to peak, centered on 0V (ground) common mode. This corresponds to a typical clock input power level of 4 dBm into the  $50\Omega$  termination resistor. Do not exceed 10 dBm to avoid saturation of the preamplifier input transistors.

The inverted phase clock input is grounded through the  $50\Omega$  termination resistor.

**Figure 29.** Single-ended Clock Input (Ground common mode): VCLK Common Mode = 0V; VCLKB = 0V; 4 dBm Typical Clock Input Power Level (into 50Ω termination resistor)

CLK or CLKB

1 M $\Omega$ (external)

0.4 pF

$50\Omega$  reverse termination

CLK or CLKB double pad (pins 37, 38 or 39, 40)

Note: Do not exceed 10 dBm into the  $50\Omega$  termination resistor for single clock input power level.

# Differential ECL Clock Input

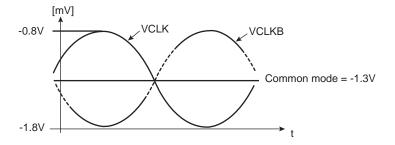

The clock inputs can be driven differentially with nominal -0.8V/-1.8V ECL levels.

In this mode, a low phase noise sinewave generator can be used to drive the clock inputs, followed by a power splitter (hybrid junction) in order to obtain 180 degrees out of phase sinewave signals. Biasing tees can be used for offseting the common mode voltage to ECL levels.

Note: As the biasing tees propagation times are not matching, a tunable delay line is required in order to ensure the signals to be 180 degrees out of phase especially at fast clock rates in the GSPS range.

Figure 30. Differential Clock Inputs (ECL Levels)

CLK or CLKB double pad (pins 37, 38 or 39, 40)

$50\Omega$  reverse termination

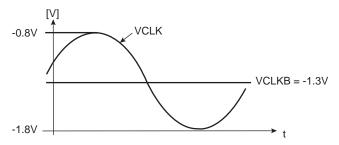

# Single-ended ECL Clock Input

In single-ended configuration enter on CLK (resp. CLKB) pin, with the inverted phase Clock input pin CLKB (respectively CLK) connected to -1.3V through the  $50\Omega$  termination resistor.

The inphase input amplitude is 1V peak to peak, centered on -1.3V common mode.

**Figure 31.** Single-ended Clocl Input (ECL): VCLK Common Mode = -1.3V; VCLKB = -1.3V

# Noise Immunity Information

Circuit noise immunity performance begins at design level.

Efforts have been made on the design in order to make the device as insensitive as possible to chip environment perturbations resulting from the circuit itself or induced by external circuitry (Cascode stages isolation, internal damping resistors, clamps, internal (on-chip) decoupling capacitors).

Furthermore, the fully differential operation from analog input up to the digital outputs provides enhanced noise immunity by common mode noise rejection.

Common mode noise voltage induced on the differential analog and clock inputs will be canceled out by these balanced differential amplifiers.

Moreover, proper active signals shielding has been provided on the chip to reduce the amount of coupled noise on the active inputs.

The analog inputs and clock inputs of the TS8388BF device have been surrounded by ground pins, which must be directly connected to the external ground plane.

### **Digital Outputs**

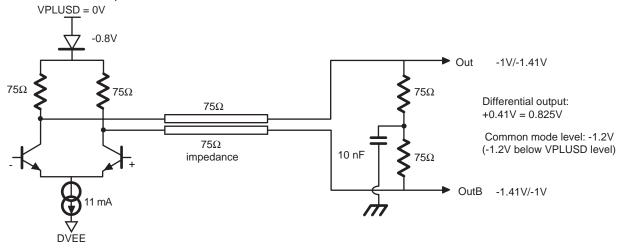

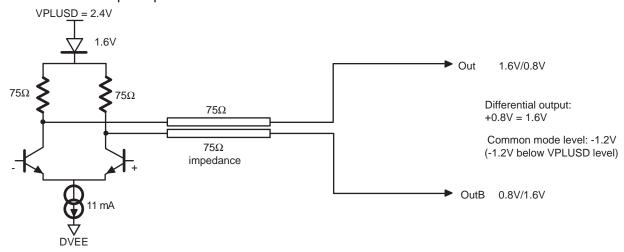

The TS8388BF differential output buffers are internally  $75\Omega$  loaded. The  $75\Omega$  resistors are connected to the digital ground pins through a -0.8V level shift diode (see Figure 32, Figure 33, Figure 34 on page 30).

The TS8388BF output buffers are designed for driving  $75\Omega$  (default) or  $50\Omega$  properly terminated impedance lines or coaxial cables. An 11 mA bias current flowing alternately into one of the  $75\Omega$  resistors when switching ensures a 0.825V voltage drop across the resistor (unterminated outputs).

The  $V_{PLUSD}$  positive supply voltage allows the adjustment of the output common mode level from -1.2V ( $V_{PLUSD}$  = 0V for ECL output compatibility) to +1.2V ( $V_{PLUSD}$  = 2.4V for LVDS output compatibility).

Therefore, the single-ended output voltages vary approximately between -0.8V and -1.625V, (outputs unterminated), around -1.2V common mode voltage.

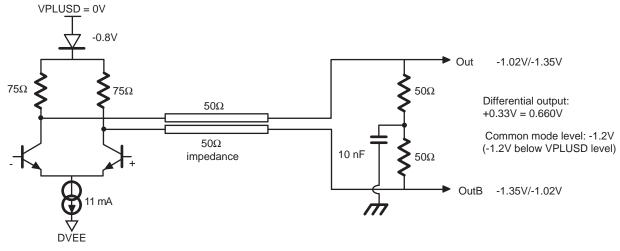

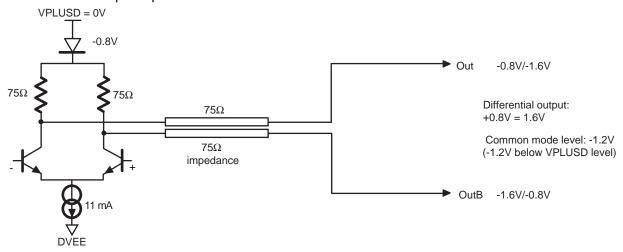

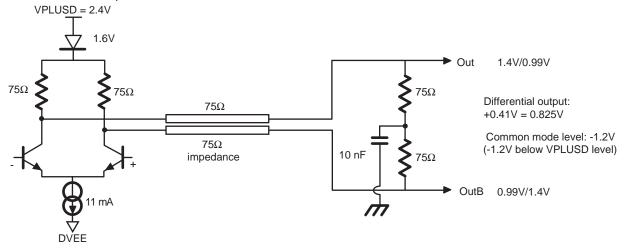

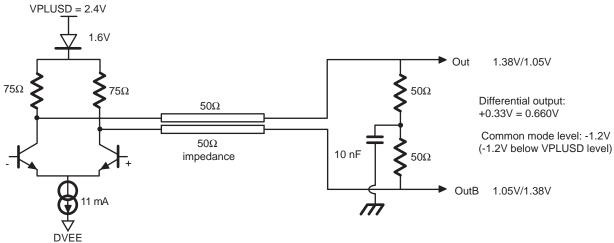

Three possible line driving and back-termination scenarios are proposed (assuming  $V_{PLUSD} = 0V$ ):

- 1.  $75\Omega$  impedance transmission lines,  $75\Omega$  differentially terminated (Figure 32): Each output voltage varies between -1V and -1.42V (respectively +1.4V and +1V), leading to  $\pm 0.41V = 0.825V$  in differential, around -1.21V (respectively +1.21V) common mode for  $V_{PLUSD} = 0V$  (respectively 2.4V).

- 2.  $50\Omega$  impedance transmission lines,  $50\Omega$  differentially termination (Figure 33): Each output voltage varies between -1.02V and -1.35V (respectively +1.38V and +1.05V), leading to  $\pm 0.33$ V = 660 mV in differential, around -1.18V (respectively +1.21V) common mode for  $V_{PLUSD}$  = 0V (respectively 2.4V).

- 3.  $75\Omega$  impedance open transmission lines (Figure 34): Each output voltage varies between -1.6V and -0.8V (respectively +0.8V and +1.6V), which are true ECL levels, leading to  $\pm 0.8V = 1.6V$  in differential, around -1.2V (respectively +1.2V) common mode for  $V_{PLUSD} = 0V$  (respectively 2.4V). Therefore, it is possible to drive directly high input impedance storing registers, without terminating the  $75\Omega$  transmission lines. In time domain, that means that the incident wave will reflect at the  $75\Omega$  transmission line output and travel back to the generator (i.e.: the  $75\Omega$  data output buffer).

Note: This is no longer true if a  $50\Omega$  transmission line is used, as the latter is not matching the buffer  $75\Omega$  output impedance.

As the buffer output impedance is  $75\Omega$ , no back reflection will occur.

Each differential output termination length must be kept identical. It is recommended to decouple the midpoint of the differential termination with a 10 nF capacitor to avoid common mode perturbation in case of slight mismatch in the differential output line lengths.

Too large mismatches (keep < a few mm) in the differential line lengths will lead to switching currents flowing into the decoupling capacitor leading to switching ground noise.

The differential output voltage levels ( $75\Omega$  or  $50\Omega$  termination) are not ECL standard voltage levels, however it is possible to drive standard logic ECL circuitry like the ECLinPS logic line from Motorola<sup>®</sup>.

At sampling rates exceeding 1 GSPS, it may be difficult to trigger the HP16500 or any other Acquisition System with digital outputs. It becomes necessary to regenerate digital data and Data Ready by means of external amplifiers, in order to be able to test the TS8388BF at its optimum performance conditions.

#### **Differential Output Loading Configurations (Levels for ECL Compatibility)**

Figure 32. Differential Output:  $75\Omega$  Terminated

Figure 33. Differential Output:  $50\Omega$  Terminated

Figure 34. Differential Output: Open Loaded

#### **Differential Output Loading Configurations (Levels for LVDS Compatibility)**

Figure 35. Differential Output:  $75\Omega$  Terminated

Figure 36. Differential Output:  $50\Omega$  Terminated

Figure 37. Differential Output: Open Loaded

#### **Out of Range Bit**

An Out of Range (OR, ORB) bit is provided that goes to logical high state when the input exceeds the positive full scale or falls below the negative full scale.

When the analog input exceeds the positive full scale, the digital output datas remain at high logical state, with (OR, ORB) at logical one.

When the analog input falls below the negative full scale, the digital outputs remain at logical low state, with (OR, ORB) at logical one again.

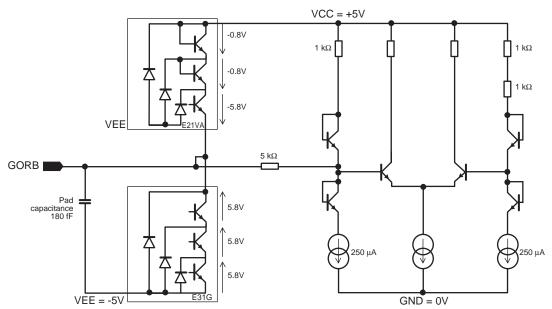

# Gray or Binary Output Data Format Select

The TS8388BF internal regeneration latches indecision (for inputs very close to latches threshold) may produce errors in the logic encoding circuitry and leading to large amplitude output errors.

This is due to the fact that the latches are regenerating the internal analog residues into logical states with a finite voltage gain value (Av) within a given positive amount of time  $\Delta(t)$ :

Av =  $\exp(\Delta(t)/\tau)$ , with  $\tau$  the positive feedback regeneration time constant.

The TS8388BF has been designed for reducing the probability of occurrence of such errors to approximately 10<sup>-13</sup> (targeted for the TS8388BF at 1 GSPS).

A standard technique for reducing the amplitude of such errors down to  $\pm$  1 lsb consists of outputting the digital datas in Gray code format. Though the TS8388BF has been designed for featuring a Bit Error Rate of  $10^{-13}$  with a binary output format, it is possible for the user to select between the Binary or Gray output data format, in order to reduce the amplitude of such errors when occurring, by storing Gray output codes.

Digital Datas format selection:

- BINARY output format if GORB is floating or V<sub>CC</sub>.

- GRAY output format if GORB is connected to ground (0V).

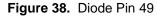

#### Diode Pin 49

One single pin is used for both DRRB input command and die junction monitoring. The pin denomination is DRRB/DIOD. Temperature monitoring and Data Ready control by DRRB is not possible simultaneously.

(See "Principle of Data Ready Signal Control by DRRB Input Command" on page 24 for Data Ready Reset input command).

The operating die junction temperature must be kept below 145°C, therefore an adequate cooling system has to be set up. The diode mounted transistor measured Vbe value versus junction temperature is given below.

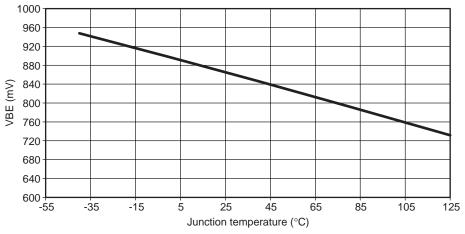

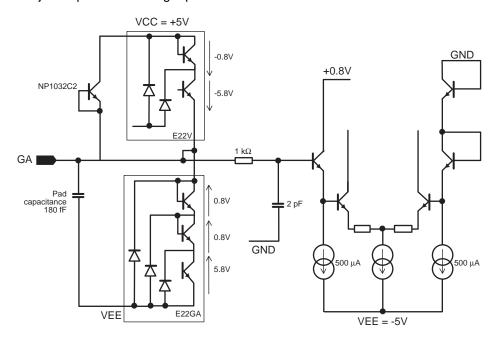

# ADC Gain Control Pin 60

The ADC gain is adjustable by the means of the pin 60 (input impedance is 1 M $\Omega$  in parallel with 2 pF).

The gain adjust transfer function is given below.

Figure 39. ADC Gain Control Pin 60

Note: For more information, please refer to the document "DEMUX and ADCs Application Notes".

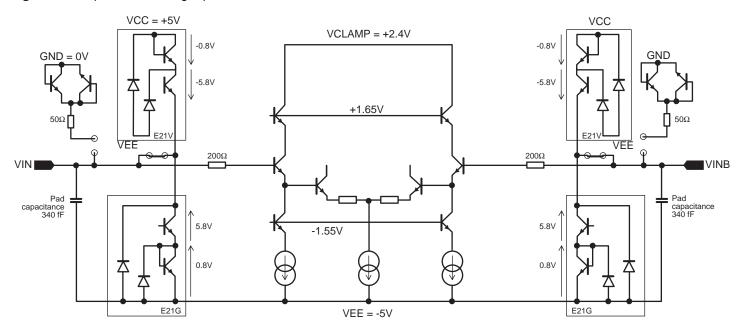

# Equivalent Input/Output Schematics

Figure 40. Equivalent Analog Input Circuit and ESD Protections

Note: The ESD protection equivalent capacitance is 150 fF.

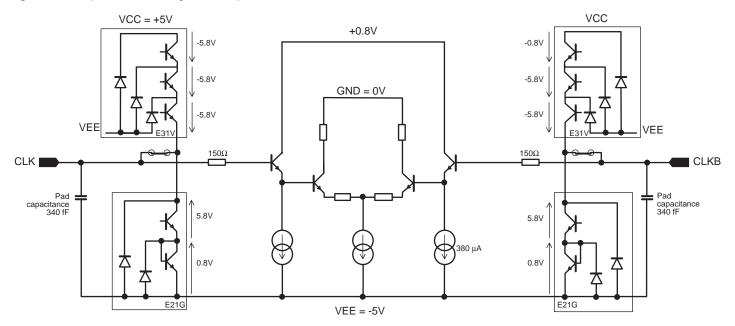

Figure 41. Equivalent Analog Clock Input Circuit and ESD Protections

Note: The ESD protection equivalent capacitance is 150 fF.

VPLUSD = 0V to 2.4V -5.8V -5.8V VEE E01\ E01V VEE OUTB OUT 5.8V 5.8V Pad capacitance 180 fF Pad capacitance 180 fF 0.8V 0.8V 0.8V 0.8V DVEE = -5VVEE = -5V VEE = -5V

Figure 42. Equivalent Data Output Buffer Circuit and ESD Protections

Note: The ESD protection equivalent capacitance is 150 fF.

Figure 43. ADC Gain Adjust Equivalent Analog Input Circuit and ESD Protections

Note: The ESD protection equivalent capacitance is 150 fF.

**Figure 44.** GORB Equivalent Input Schematic and ESD Protections GORB: Gray or Binary Select Input; Floating or Tied to VCC -> Binary

Note: The ESD protection equivalent capacitance is 150 fF.

**Figure 45.** DRRB Equivalent Input Schematic and ESD Protections

Actual Protection Range: 6.6V above VEE, in fact stress above GND are clipped by the CB diode used for Tj monitoring

Note: The ESD protection equivalent capacitance is 150 fF.

TSEV8388BF:

Device Evaluation Board For complete specification, see separate TSEV8388B document.

# General Description

The TSEV8388BF Evaluation Board (EB) is a board which has been designed in order to facilitate the evaluation and the characterization of the TS8388BF device up to its 1.5 GHz full power bandwidth at up to 1 GSPS in the military temperature range.

The high speed of the TS8388BF requires careful attention to circuit design and layout to achieve optimal performance.

This four metal layer board with internal ground plane has the adequate functions in order to allow a quick and simple evaluation of the TS8388BF ADC performances over the temperature range.

The TSEV8388BF Evaluation Board is very straightforward as it only implements the TS8388BF ADC, SMA connectors for input/output accesses and a 2.54 mm pitch connector compatible with HP16500C high frequency probes.

The board also implements a de-embedding fixture in order to facilitate the evaluation of the high frequency insertion loss of the input microstrip lines, and a die junction temperature measurement setting.