TMPZ84C112A

TMPZ84C112AN-6 / AF-6

T-49-19-07

# 1. OUTLINE AND FEATURES

The TMPZ84C112A is a high-performance, low power consumption 8-bit microcomputer created with Toshiba CMOS silicon technology.

The TMPZ84C112A consists of a Toshiba CMOS TMPZ84C00A core with built-in input/output ports, timer and a 256-byte RAM. The TMPZ84C112A is available in a 64-pin shrink dual inline package or a 64-pin flat package and is extremely effective in promoting system miniaturization and low current consumption.

The CPU is fully Z80 compatible and can thus be used with existing software resources and development tools. It is possible to set only the built-in CPU to high impedance with the  $\overline{BUSREQ/EV}$  pin used for debugging to enable real time development by connecting a Z80 in-circuit emulator with the TMPZ84C112A mounted on the target PCB.

- The TLCS-Z80 CPU has built-in input/output ports (21 or 23 depending on the mode), a one-channel free-running timer and a 256-byte RAM.

- Wide operating frequency range : DC to 6.144MHz

- Wide operating voltage range : 4.5V to 5.5V

- Wide operating temperature range:  $-10 \,^{\circ}\text{C}$  to  $+70 \,^{\circ}\text{C}$ .

- Three (23 bit maximum) built-in input/output ports.

Ports PA, PB: each nibble can be set for input or output.

Port PC: each bit can be set for input or output.

- Built-in 256-byte RAM, two types of program mapping.

- Compact 64-pin shrink dual inline package (TMPZ84C112AN-6) or compact 64-pin flat package (TMPZ84C112AF-6).

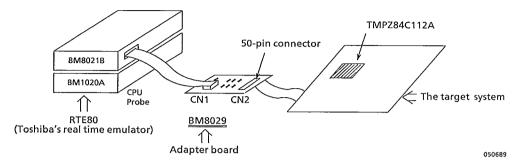

- The Toshiba RTE80 real time emulator and commercially available Z80 ICE (In-Circuit Emulator) can be used.

- A Toshiba adaptor board (BM8029) can be used.

Note: Z80 is a trademark of Zilog Inc., U.S.A.

TMPZ84C112A

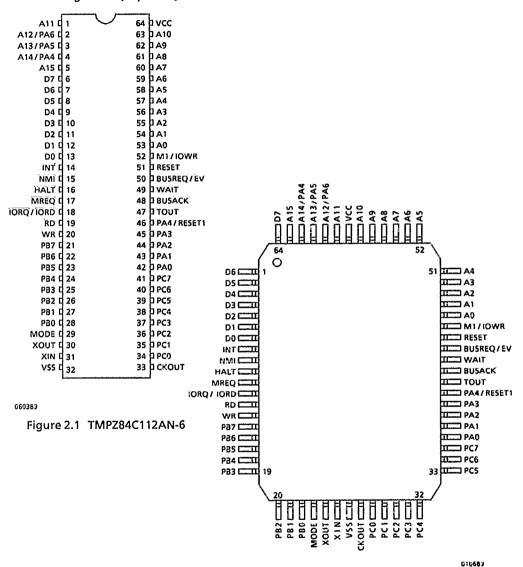

### 2. PIN ASSIGNMENT AND FUNCTIONS

#### 2.1 Pin Assignment (Top View)

Figure 2.2 TMPZ84C112AF-6

# TMPZ84C112A

# 2.2 Pin Names and Functions

(1/3)

|                               | Q'ty     | <u> </u>                                      | FUNCTION (1/3)                                                                                                                                                                                                                                                                               |                                                                                                                              |  |  |  |  |  |

|-------------------------------|----------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| PIN                           | (Number) | TYPE                                          | MODE PIN = "0" (MODE 0)                                                                                                                                                                                                                                                                      | MODE PIN = "1" (MODE 1)                                                                                                      |  |  |  |  |  |

| D0~D7                         | 8        | Input/Output<br>3-State                       | An 8-bit bi-directional data bus.<br>High impedance output is possible                                                                                                                                                                                                                       | using the BUSREQ/EV pin.                                                                                                     |  |  |  |  |  |

| A0~A11<br>A15                 | 13       | Output<br>3-State                             | A 13-address bus.<br>Used to set addresses for memory of<br>The refresh addresses are output t<br>High impedance output is possible                                                                                                                                                          | o the lower 7 bits during refresh.                                                                                           |  |  |  |  |  |

| A12/PA6<br>A13/PA5<br>A14/PA4 | 3        | Output<br>3-State/<br>Input/Output<br>3-State | address bus.                                                                                                                                                                                                                                                                                 | Functions as bit 4 ~ bit 6 of PA (port A).                                                                                   |  |  |  |  |  |

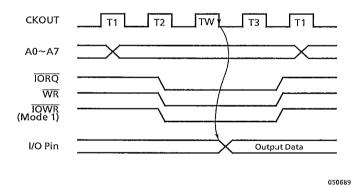

| M1/IOWR                       | 1        | Output<br>3-State                             | This signal indicates machine cycle 1. "0" is output together with the MREQ signal during the op code fetch cycle. "0" is output together with the IORQ signal during the interrupt acknowledge cycle.                                                                                       | "0" is output when both the Z80 CPU TORQ and WR signals are "0". That is, "0" is output during output instruction execution. |  |  |  |  |  |

|                               | 1        |                                               | High impedance output is possible                                                                                                                                                                                                                                                            | using the BUSREQ/EV pin.                                                                                                     |  |  |  |  |  |

| IORQ<br>/IORD                 | 1        | 1 Output<br>3-State                           | The input/output request signal.  "0" is output during input/ output operations.  "0" is also output together with the M1 signal during the interrupt acknowledge cycle.  "0" is output when both the CPU loRQ and RD signals are That is, "0" is output during input instruction execution. |                                                                                                                              |  |  |  |  |  |

|                               |          |                                               | High impedance output is possible using the BUSREQ/EV pin.                                                                                                                                                                                                                                   |                                                                                                                              |  |  |  |  |  |

| RD                            | 1        | Ouput<br>3-State                              | The read signal. This signal reports when the CPU input/output. High impedance output is possible                                                                                                                                                                                            | · .                                                                                                                          |  |  |  |  |  |

| WR                            | 1        | Output<br>3-State                             | The write signal. This signal reports when the CPU input/output. High impedance output is possible                                                                                                                                                                                           | -                                                                                                                            |  |  |  |  |  |

| MREQ                          | 1        | Output<br>3-State                             | The memory request signal. This signal reports the memory access cycle. "0" is output during the memory refresh cycle to report that memory is being refreshed. High impedance output is possible using the BUSREQ/EV pin.                                                                   |                                                                                                                              |  |  |  |  |  |

| HALT                          | 1        | Output                                        | enters halt status.                                                                                                                                                                                                                                                                          | 0" is output when the CPU executes the HALT instruction and                                                                  |  |  |  |  |  |

010689

TMPZ84C112A

(2/3)

| <del></del>    |                  |                                   | FUNC                                                                                                                                                                                                                                                                                                                                                                                                                                                           | (2/3)                                                                         |  |  |  |  |

|----------------|------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| PIN            | Q'ty<br>(Number) | TYPE                              | MODE PIN = "0" ( MODE 0)                                                                                                                                                                                                                                                                                                                                                                                                                                       | MODE PIN = "1" (MODE 1)                                                       |  |  |  |  |

| ЙМÏ            | 1                | Input                             | The non-maskable interrupt reque<br>This interrupt request has a h<br>interrupts. Interrupt enable/disabl                                                                                                                                                                                                                                                                                                                                                      | st signal.<br>ligher priority than maskable                                   |  |  |  |  |

| ĪNT            | 1                | Input                             | The maskable interrupt request sig<br>Interrupt enable/disable can be set                                                                                                                                                                                                                                                                                                                                                                                      |                                                                               |  |  |  |  |

| WAIT           | 1                | Input                             | The wait request signal. This signal reports to the CPU input/output is not ready to transf                                                                                                                                                                                                                                                                                                                                                                    |                                                                               |  |  |  |  |

| RESET          | 1                | Input                             | A reset signal.<br>The TMPZ84C112A internal reset signal.                                                                                                                                                                                                                                                                                                                                                                                                      | A reset signal.<br>The TMPZ84C112A internal CPU-<br>only reset signal.        |  |  |  |  |

| BUSREQ /<br>EV | 1                | Input                             | This signal has two meanings.  BUSREQ signal: The bus request signal. This signal sets the CPU address bus, data bus, MREQ, IORQ, RD, WR and IORD to high impedance output.  EV signal: This signal is used during development to set HALT, M1 and IOWR to high impedance output. This signal becomes valid when the BUSREQ/EV pin is latched at "0" during RESET pin rise.  Normally, the BUSREQ/EV pin is used fixed at "0" during evaluation (development). |                                                                               |  |  |  |  |

| BUSACK         | 1                | Output                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                | CQ signal is received and the CPU<br>I signal are at high impedance in        |  |  |  |  |

| PA0~PA3        | 4                | Input/Output<br>3-State           | A general-purpose input/output<br>nibble can be set for either input c<br>Output is latched.                                                                                                                                                                                                                                                                                                                                                                   | port (port A) with which each or output by program.                           |  |  |  |  |

| PA4/<br>RESET1 | 1                | Input/Output<br>3-State<br>/Input | Bit 4 of port A.                                                                                                                                                                                                                                                                                                                                                                                                                                               | A resetsignal.<br>This signal resets all but the<br>TMPZ84C112A internal CPU. |  |  |  |  |

| PBO~PB7        | 8                | Input/Output<br>3-State           | A general-purpose input/output p<br>can be set for either input or output<br>Output is latched.                                                                                                                                                                                                                                                                                                                                                                | oort (port B) each nibble of which ut by program.                             |  |  |  |  |

| PC0~PC7        | 8                | Input/Output<br>3-State           | A general-purpose input/output port (port C) each nibble of which can be set for either input or output by program. Output is latched.                                                                                                                                                                                                                                                                                                                         |                                                                               |  |  |  |  |

| ΤΟΌΤ           | 1                | Output                            | The 15-bit free-running timer out differs depending on the external                                                                                                                                                                                                                                                                                                                                                                                            | tput pin. The output pulse width<br>ly connected pin (TMPZ84C112A).           |  |  |  |  |

| MODE           | 1                | Input                             | TMPZ84C112A mode setting input. MODE pin = "0": mode 0 is set. MODE pin = "1": mode 1 is set.                                                                                                                                                                                                                                                                                                                                                                  |                                                                               |  |  |  |  |

010567

# TMPZ84C112A

(3/3)

| PIN         | Q'ty     | TYPE            | FUNC                                                                                                                             | FUNCTION                                  |  |  |  |  |  |

|-------------|----------|-----------------|----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|--|--|

| FIIN        | (Number) | 1175            | MODE PIN = "0" (MODE 0)                                                                                                          | MODE PIN = "1" (MODE 1)                   |  |  |  |  |  |

| XIN<br>XOUT | 2        | Input<br>Output | The oscillator connecting pin. Connect an oscillator with a TMPZ84C112A operating clock (sy                                      | frequency double that of the stem clock). |  |  |  |  |  |

| CKOUT       | 1        | Output          | The single-phase clock output. Divides by two and outputs t connected to the XIN, XOUT pins. Used for clock input to other perip | he frequency of the oscillator            |  |  |  |  |  |

| VCC         | 1        |                 | The power supply pin ( + 5V).                                                                                                    |                                           |  |  |  |  |  |

| VSS         | 1        |                 | The GND pin (0V).                                                                                                                |                                           |  |  |  |  |  |

010689

TMPZ84C112A

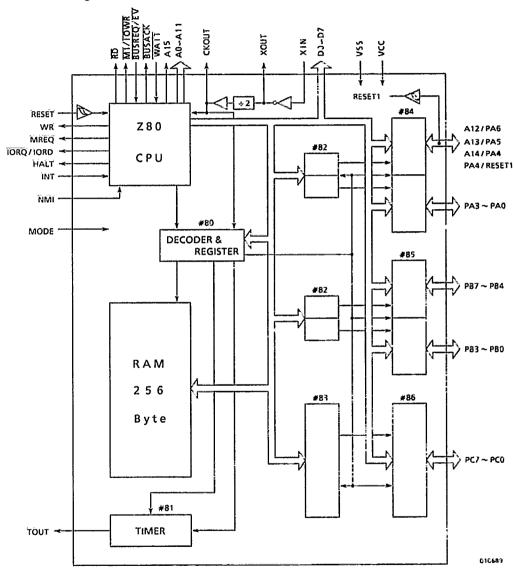

# 3. FUNCTION DESCRIPTION

# 3.1 Block Diagram

Figure 3.1.1 TMPZ84C112AN-6 / AF-6 Block Diagram

# EZOT

### TOSHIBA

TMPZ84C112A

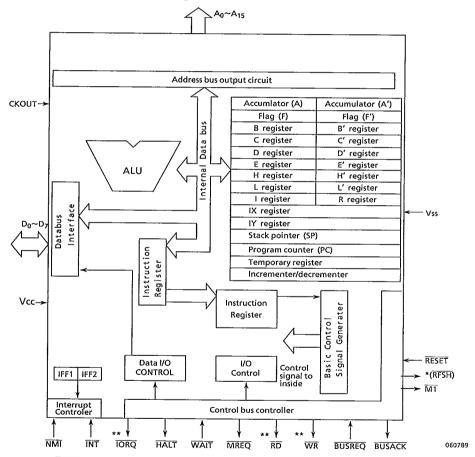

#### 3.2 CPU Operation

The following is an explanation of the system configuration and functions of the CPU of the TMPZ84C112A.

This CPU is fully compatible with the CMOS Z80MPU (TMPZ84C00A) of the TLCS-Z80 series, but the  $\overline{RFSH}$  signal is not connected to an external pin.

As concerns the details, please refer to be chapter of TMPZ84C00A.

### 3.2.1 Block Diagram of The CPU

Figure 3.2.1 shows the block diagram of the CPU.

<sup>\*</sup> The RFSH signal is not connected to an external pin.

Figure 3.2.1 Block Diagram of The CPU

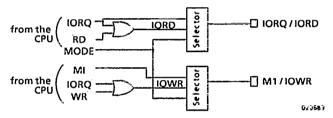

<sup>\*\*</sup> During mode 1: The  $\overline{IORD}$  signal is created from the  $\overline{IORQ}$  signal and  $\overline{RD}$  signal and connected to an external pin.

TMPZ84C112A

# • External Pin Signals for Different Modes

The signals output to external pins by the TMPZ84C112A by means of mode control using the MODE pin differ as shown in Figure 3.2.20.

| Mode<br>Pin        | Mode 0<br>(MODE = 0) | Mode 1<br>(MODE = 1) |  |  |

|--------------------|----------------------|----------------------|--|--|

| A12/PA6<br>A14/PA4 | A12<br>~<br>A14      | PA6<br>~<br>PA4      |  |  |

| IORQ / IORD        | IORQ                 | IORD                 |  |  |

| M1/IOWR            | M1                   | IOWR                 |  |  |

| PA4/RESET1         | PA4                  | RESET1               |  |  |

020689

Figure 3.2.20 External Signal at Each Mode

TMPZ84C112A

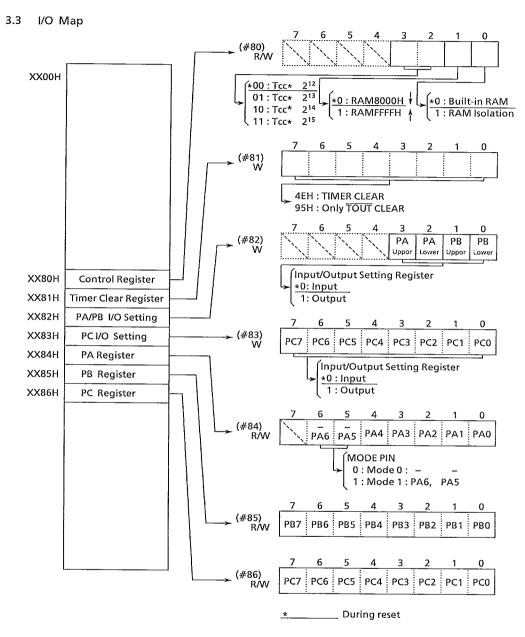

Figure 3.3.1 I/O Map

020689

TMPZ84C112A

#### TOSHIBA

# 3.4 Input/Output Register Operation

#### 3.4.1 Control Register

| 7 | 6 | 5 | 4        | 3   | 2   | 11  | 0   |  |

|---|---|---|----------|-----|-----|-----|-----|--|

|   |   |   |          |     | mer |     |     |  |

|   |   |   | <u> </u> | Ser | ung | MAP | 1/E |  |

020689

- Fixed at address 80 in the input/output area (accessed by the input/output instruction).

- Both read and write are possible.

- The upper 4 bits are '0000' when read.

# (1) Bit 0 (RAM I/E) {built-in RAM/RAM isolation}

0: built-in RAM (built-in RAM used)

1 : RAM isolation (built-in RAM not used)

-During reset Mode 0: performed by the RESET pin.

Mode 1: performed by the RESETI pin.

• This bit (RAM I/E) functions in conjunction with the setting of the MODE pin of the external input pin. That is, this bit is effective only when the MODE pin input is "0" (mode 0) and determines whether or not the built-in RAM is used. This bit is not effective when the MODE pin input is "1" (mode 1) and the built-in RAM is used, regardless of its settings.

(2) Bit 1 (RAM MAP) {specifies mapping of the built-in RAM}

0: the built-in RAM is assigned to an area starting at address 8000H of the memory map, that is, from address 8000H to address 80FFH.

1: the built-in RAM is assigned to an area ending at address FFFFH of the memory map, that is, from address FF00H to address FFFFH.

-During reset Mode 0: performed by the RESET pin.

Mode 1: performed by the RESET1 pin.

• This bit (RAM MAP) functions in conjunction with the setting of the MODE pin of the external input pin and bit 0 (RAM I/E) at address 80H.

When the MODE pin input is "1" (mode 1), the built-in RAM is assigned from address 8000H to address 80FFH of the memory map, regardless of the setting of this bit and bit 0 at address 80H.

When the MODE pin input is "0" (mode 0), settings are valid only when bit 0 (RAM I/E) at address 80H is "0" (built-in RAM). When bit 0 (RAM MAP) is assigned from address 8000H to address 80FFH; when bit 1 (RAM MAP) is "1", it is assigned from address FF00H to address FFFFH. When bit 0 (RAM I/E) at address 80H is "1" (RAM isolation), however, the built-in RAM is ineffective.

Table 3.4.1 shows these relationships.

TMPZ84C112A

Table 3.4.1 Relationship between the MODE pin, the RAM map bit (#80 (1)) and the RAM I/E (#80 (0)) bit

|                                                     | <del></del> |        |                 |         |                    |           |  |

|-----------------------------------------------------|-------------|--------|-----------------|---------|--------------------|-----------|--|

|                                                     | MOD         | E PIN  | RAM<br>#80      |         | RAM 1/E<br>#80 <0> |           |  |

|                                                     | "0"         | "1"    | "0"             | "1"     | "0"                | "1"       |  |

|                                                     | Mode 0      | Mode 1 | 8000H Î         | FFFFH↑  | Built-in           | Isolation |  |

| ① <u>Mode 1</u>                                     |             |        |                 |         |                    |           |  |

| Built-in RAM fixed<br>at addresses<br>8000H~80FFH.  | 1 (Mo       | de 1)  | >               | •       | ×                  |           |  |

| ② <u>Mode 0</u>                                     |             |        |                 |         |                    |           |  |

| Built-in RAM mapped<br>to addresses<br>8000H~80FFH. | 0 (Mo       | de 0)  | 0 (8000Н        | ~80FFH) | 0 (Built-in)       |           |  |

| ③ <u>Mode 0</u>                                     |             |        |                 | į       |                    |           |  |

| Built-in RAM mapped<br>to addresses<br>FF00H~FFFFH. | 0 (Mo       | de 0)  | 1 (FF00H~FFFFH) |         | 0 (Built-in)       |           |  |

| <b>④</b> <u>Mode 0</u>                              |             |        |                 |         |                    |           |  |

| No built-in RAM<br>(no access of built-in<br>RAM).  | 0 (Mo       | de 0)  | ×               |         | 1 (Isolation)      |           |  |

× : This bit is not effective

060789

Note: When MODE pin=1 (mode 1), pins A14/PA4~A12/PA6 are used as PA4~PA6; therefore, RAM addresses A14~A12 are not decoded, thus creating a shadow RAM.

TMPZ84C112A

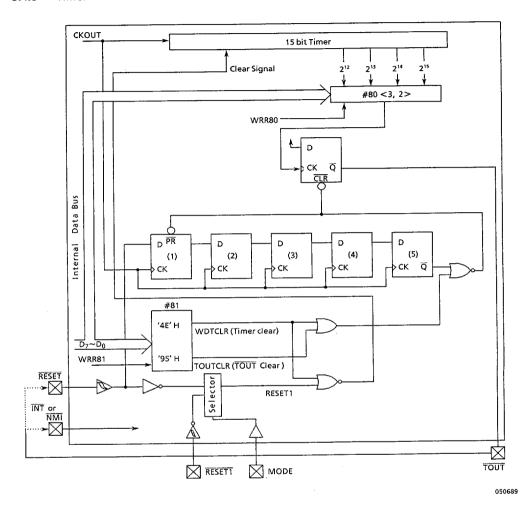

# (3) Bit 3, Bit 2 (Timer Setting)

| Bit 3 | $\underline{\mathrm{Bit} 2}$ |                                                                                          |                                                 |

|-------|------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------|

| 0     | <u>0</u><br>1                | : $\frac{\text{Tcc}}{\text{Tcc}} * 2^{12}$<br>: $\frac{\text{Tcc}}{\text{Tcc}} * 2^{13}$ |                                                 |

| 1     | 0                            | : $Tcc * 2^{14}$                                                                         |                                                 |

| 1     | 1                            | $\frac{1}{2}$ Tcc * $2^{15}$                                                             |                                                 |

|       |                              | - During reset                                                                           | Mode $0$ : Reset by the $\overline{RESET}$ pin. |

|       |                              |                                                                                          | Mode 1: Reset by the $\overline{RESET1}$ pin.   |

This register sets the number of 15-bit timer output stages.

Timer output is connected to the  $\overline{TOUT}$  pin.

When the MODE pin is set to mode 1, this bit is reset by the  $\overline{RESET1}$  pin.

Table 3.4.2 shows the relationship between operating frequency and timer output time.

Table 3.4.2 Operating Frequency and  $\overline{TOUT}$  Output Time

| Operating<br>Frequency<br>(CKOUT Output<br>Frequency) | bit 3  | bit 2 | bit 3 bit 2 |     | bit 3 bit 2 |    | bit 3 bit 2 |   |

|-------------------------------------------------------|--------|-------|-------------|-----|-------------|----|-------------|---|

|                                                       | 0      | 0     | 0           | 1   | 1           | 0  | 1           | 1 |

|                                                       | 212    |       | 2           | 213 |             | 14 | 215         |   |

| Tcc = 3.25MHz                                         | 1.25ms |       | 2.51ms      |     | 5.03ms      |    | 10.06ms     |   |

| Tcc = 4.0MHz                                          | 1.02ms |       | 2.05ms      |     | 4.1ms       |    | 8.2ms       |   |

| Tcc = 6.0MHz                                          | 0.68ms |       | 1.37ms      |     | 2.74ms      |    | 5.47ms      |   |

050689

TMPZ84C112A

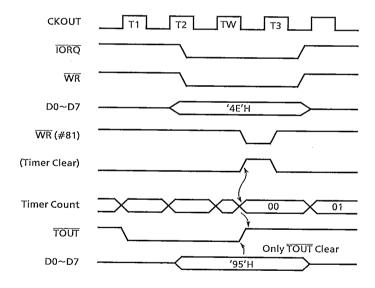

### 3.4.2 Timer Clear Command Register

|        |         | 0                                            | 1        | 2       | 3                                            | 4        | 5 | 6 | 7 |   |

|--------|---------|----------------------------------------------|----------|---------|----------------------------------------------|----------|---|---|---|---|

|        | #81 [W] |                                              |          |         |                                              |          |   |   |   |   |

| 140289 | 1       | <u>:                                    </u> | <u>:</u> | <u></u> | <u>.                                    </u> | <u>:</u> |   | : | Ь | 1 |

- Fixed at address 81H in the input/output area (accessed by the output instruction).

- Only write is possible.

- $\bullet$  There is no influence from the  $\overline{RESET}$  or  $\overline{RESET1}$  pins.

- (1) Bit 7~Bit 0 (Timer Clear Command Register)

- Used to clear the built-in 15-bit timer with software.

The built-in timer is cleared and starts counting again from "0" when the data '4EH' is written to address 81H in the input/output area.

This clear command sets the TOUT pin to "H" level.

- The TOUT pin can only be set to "H" level without clearing the built-in timer by writing the data '95H' to address 81H in the input/output area.

050689

Figure 3.4.1 Clear Timing of the Timer Counter

TMPZ84C112A

3.4.3 Port A (PA), Port B (PB) Input/Output Setting Register

| 7 | 6 |   | 5 | 4 | 3     | 2     | 1     | 0     |          |

|---|---|---|---|---|-------|-------|-------|-------|----------|

|   |   |   |   |   | PA    | PA    | PB    | PB    | #82 [ W] |

|   |   | 1 |   |   | Upper | Lower | Üpper | Lower |          |

050689

- Fixed at address 82H in the input/output area (accessed by the output instruction).

- Only write is possible.

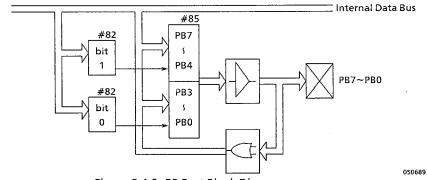

- (1) Bit 1~Bit 0 (PB7~PB0 Input/Output Control)

These bits set each nibble of the port B (PB7 $\sim$ PB0) upper bits (PB7 $\sim$ PB4) and lower bits (PB3 $\sim$ PB0) for input or output.

Bit 0: sets PB3~PB0 (lower) input/output.

Bit 1: sets PB7~PB4 (upper) input/output.

0: sets input mode

1: sets output mode

-During reset Mode 0: performed by the RESET pin.

Mode 1: performed by the RESET1 pin.

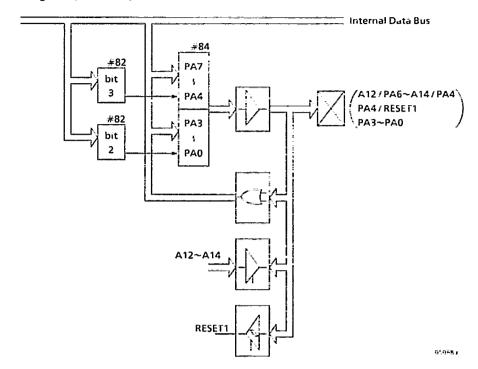

(2) Bit 3~Bit 2 (PA6~PA0 input/Output Control)

These bits set each nibble of the port A (PA6~PA0) upper bits (PA6~PA4) and lower bits (PA3~PA0) for input or output.

Bit 2: sets PA3~PA0 (lower) input/output.

Bit 3: sets PA6~PA4 (upper) input/output.

MODE pin="0" (mode 0)

: PA4 only

MODE pin = "1" (mode 1)

: PA6~PA4

0: sets input mode

1: sets output mode

During reset Mode 0: performed by the  $\overline{\text{RESET}}$  pin.

Mode 1: performed by the RESET1 pin.

TMPZ84C112A

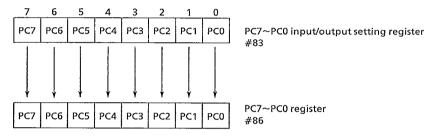

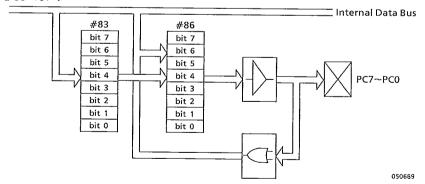

3.4.4 Port C (PC) Input/Output Setting Register

|   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |         |

|---|-----|-----|-----|-----|-----|-----|-----|-----|---------|

| - | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | #83 [W] |

- Fixed at address 83H in the input/output area (accessed by the output instruction).

- Only write is possible.

- (1) Bit 7~Bit 0 (PC7~PC0 Input/Output Control)

This register sets each bit of port C (PC7~PC0) for input or output.

The bits of the PC7~PC0 input/output setting register and PC7~PC0 register have a one-to-one correspondence. (Each bit can be set for input or output.)

0: sets input mode

1: sets output mode

-During reset Mode 0: performed by the RESET pin.

Mode 1: performed by the RESET1 pin.

TMPZ84C112A

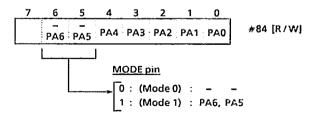

### 3.4.5 Port A Register (PA7~PA0)

Figure 3.4.2 PA Port Block Diagram

- Fixed at address 84H in the input/output area (accessed by the input/output instruction).

- Both read and write are possible.

- The port A register is cleared to zero (0) by the reset operation.

Mode 0: performed by the RESET pin.

Mode 1: performed by the RESET1 pin.

TMPZ84C112A

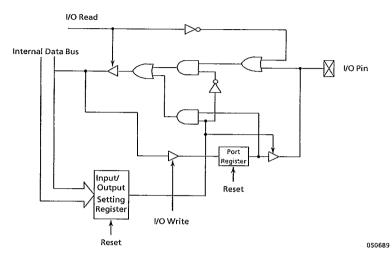

### (1) Bit 3~Bit 0 (PA3~PA0 Register)

This is PA3~PA0 Register.

Figure 3.4.3 I/O Port Logic

#### Mode 0

- The RESET pin clears the input/output setting register to zero (0) and sets pins PA3~PA0 to the input mode.

- The RESET pin clears the PA3~PA0 port register to zero (0).

### Mode 1 (no influence from the RESET pin)

- The RESET1 pin clears the input/output setting register to zero (0) and sets pins PA3~PA0 to the input mode.

- The RESET1 pin clears the PA3~PA0 port register to zero (0).

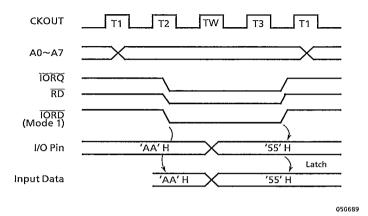

#### Input/output operation

- The input/output pin status can be read by executing the input instruction at the input mode setting.

- The port register contents can be read by executing the input instruction at the output mode setting.

- When "1" is written to the port register and then the input/output setting register is set to output to switch the input/output pin mode from input to output and to output "1", the previous data will not be output and no spikes will be generated in the port.

- The input/output setting of PA3~PA0 is determined by PA lower input/output setting register #82<2>.

TMPZ84C112A

#### (2) Bit 6~Bit 4 (PA6~PA4)

The PA6~PA4 register.

Figure 3.4.2 shows the input/output section block diagram and Figure 3.4.3 shows the input/output port logic circuit.

# Mode 0

- The RESET pin clears the input/output setting register to zero (0) and sets pin PA4 to the input mode.

- The RESET pin clears the PA4 port register to zero (0).

# Mode 1 (no influence from the RESET pin)

- The RESET1 pin clears the input/output setting register to zero (0) and sets pins PA6~PA4 to the input mode.

- The RESET1 pin clears the PA6~PA4 port register to zero (0).

# Input/output operation

- The input/output pin status can be read by executing the input instruction at the input mode setting.

- The port register contents can be read by executing the input instruction at the output mode setting.

- When "1" is written to the port register and then the input/output setting register is set to output to switch the input/output pin mode from input to output and to output "1", the previous data will not be output and no spike will be generated in the port.

- The input/output setting of PA6~PA4 is determined by PA upper input/output setting register #82<3>.

- The number of PA ports differs depending on the MODE pin status.

#### MODE pin = "0" (Mode 0)

| 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|---|---|---|-----|-----|-----|-----|-----|

|   |   |   | PA4 | PA3 | PA2 | PA1 | PA0 |

- The 5-bit port for PA4~PA0.

- Data input to bit 7 bit 5 by the input instruction are indeterminate.

#### MODE pin = "1" (Mode 1)

| 7 | _ 6 | _ 5 | 4   | 3   | 2   | 1_  | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|

|   | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PAO |

- The 7-bit port for PA6~PA0.

- Data input to bit 7 by the input instruction are indeterminate. Figure 3.4.4 shows the port input timing cycle chart and Figure 3.4.5 shows the output timing chart.

Figure 3.4.4 Input Cycle

Figure 3.4.5 Output Cycle

TMPZ84C112A

# 3.4.6 Port B Register (PB7~PB0)

| 7   | 6   | 5   | 4   | . 3 | 2   | 1   | 0   |           |

|-----|-----|-----|-----|-----|-----|-----|-----|-----------|

| РВ7 | PB6 | PB5 | PB4 | РВ3 | PB2 | PB1 | РВ0 | #85 [R/W] |

- Fixed at address 85H in the input/output area (accessed by the input/output instruction).

- Both read and write are possible.

Figure 3.4.6 shows the input/output section block diagram and Figure 3.4.3 shows the input/output port logic circuit.

# Mode 0

- The RESET pin clears the input/output setting register to zero (0) and sets pins PB7~PB0 to the input mode.

- The RESET pin clears the PB7~PB0 port register to zero (0).

#### Mode 1 (no influence from the RESET pin)

- The RESET1 pin clears the input/output setting register to zero (0) and sets pins PB7~PB0 to the input mode.

- The RESET1 pin clears the PB7~PB0 port register to zero (0).

#### Input/output operation

- The input/output pin status can be read by executing the input instruction at the input mode setting.

- The port register contents can be read by executing the input instruction at the output mode setting.

- When "1" is written to the port register and then the input/output setting register is set to output to switch the input/output pin mode from input to output and to output "1", the previous data will not be output and no spike will be generated in the port.

- The input/output settings for PB3~PB0 are determined by PB lower input/output setting register #82<0>; the input/output settings for PB7~PB4 are determined by PB upper input/output setting register #82<1>.

Figure 3.4.6 PB Port Block Diagram

TMPZ84C112A

# 3.4.7 Port C Register (PC7~PC0)

| 7   | 6   | 5   | 4   | . 3 | 2   | 1   | 0   |           |

|-----|-----|-----|-----|-----|-----|-----|-----|-----------|

| PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 | #86 [R/W] |

• Fixed at address 86H in the input/output area (accessed by the input/output instruction).

54E D

• Both read and write are possible.

Figure 3.4.7 shows the input/output section block diagram and Figure 3.4.3 shows the input/output port logic circuit.

# Mode 0

- The RESET pin clears the input/output setting register to zero (0) and sets pins PC7~PC0 to the input mode.

- The RESET pin clears the PC7~PC0 port register to zero (0).

# $\underline{\text{Mode }}1$ (no influence from the $\overline{\text{RESET}}$ pin)

- The RESET1 pin clears the input/output setting register to zero (0) and sets pins PC7~PC0 to the input mode.

- The RESET1 pin clears the PC7~PC0 port register to zero (0).

#### Input/output operation

- The input/output pin status can be read by executing the input instruction at the input mode setting.

- The port register contents can be read by executing the input instruction at the output mode setting.

- When "1" is written to the port register and then the input/output setting register is set to output to switch the input/output pin mode from input to output and to output "1", the previous data will not be output and no spike will be generated in the port.

- The input/output settings for PC7~PC0 are given a one-to-one correspondence to the PC port bits by the PC7~PC0 input/output setting registers #83<7> ~#83<0>.

Figure 3.4.7 PC Port Block Diagram

#### 3.4.8 Timer

Figure 3.4.8 Timer Logic

This is a 15-bit free-running timer which counts in synchronization with the rise of the CKOUT signal. Any of the stage 12~stage 15 timer outputs can be selected by the timer selection register (#80<3,2> and output to the TOUT pin.

(2)

#### TOSHIBA

TMPZ84C112A

### TOUT pin operation

This timer cannot be enabled or disabled by software. That is, this timer is always enabled.

The  $\overline{\text{TOUT}}$  pin outputs a "0" level signal after the time (2<sup>12</sup>, 2<sup>13</sup>, 2<sup>14</sup>, 2<sup>15</sup>) selected with the timer selection register (#80<2,3> has elapsed.

As shown below, there are two output pulse widths, depending on the method of connecting the  $\overline{\text{TOUT}}$  pin.

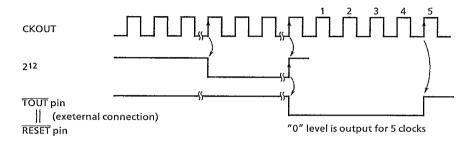

# (1) With the TOUT Pin Connected to the RESET Pin

Figure 3.4.9 TOUT Output Timing (1)

Figure 3.4.9 TOOT Output Timing (1)

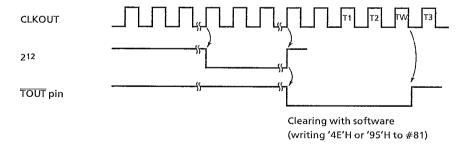

With the  $\overline{\text{TOUT}}$  pin connected to other than the  $\overline{\text{RESET}}$  pin

The "0" level output continues until cleared by software (writing '4E'H or '95'H to the timer clear command register (#81)) or a reset is caused by the  $\overline{RESET}$  pin (mode 0) or  $\overline{RESET1}$  pin (mode 1).

Writing '4E' H: the TOUT pin and the 15-stage timer are cleared.

Writing '95' H: only the TOUT pin is cleared.

060589

050689

Figure 3.4.10 TOUT Output Timing (2)

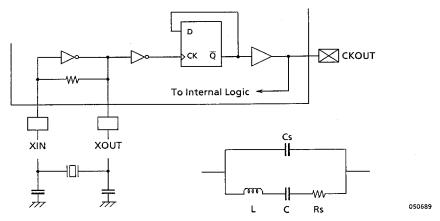

#### 3.4.9 Clock Generation

A stable clock signal can be output to the output pin (CKOUT) and built-in devices by connecting an oscillator with double the operating frequency between XIN and XOUT.

Figure 3.4.11 (a) Crystal Connection

Figure 3.4.11 (b) Oscillator Equivalent Circuit

Note: CKOUT wiring caution

The drive capacity of the 112A CKOUT output is greater than that of the other output pins to enable high-speed operation. Consequently, distortion occurs in the output waveform when long wiring is connected to the CKOUT pin and due to the L component of the wiring and capacitor discharge.

Note that CKOUT signal waveform distortion can result in system misoperation.

(1) When using a crystal oscillator, use the Tokyo Denpa MR8000-C20 (oscillation frequency: 8MHz) or MR12000-C20 (oscillation frequency: 12MHz) which have the following characteristics.

Oscillation Frequency f:8MHz Crystal oscillator "MR8000-C20"  $CS \! \leq \! 4PF \\ RS \! \leq \! 30\Omega$   $CIN \! = \! 22pF \ COUT \! = \! 33pF$

f:12Hz

Crystal oscillator "MR12000-C20"  $\text{CS} \hspace{-0.05cm} \leq \hspace{-0.05cm} 4PF \\ \text{RS} \hspace{-0.05cm} \leq \hspace{-0.05cm} 25\Omega \\ \text{CIN} \hspace{-0.05cm} = \hspace{-0.05cm} \text{COUT} \hspace{-0.05cm} = \hspace{-0.05cm} 33pF$

TMPZ84C112A

(2) For the ceramic oscillator, use the Murata's CSA8.00 MT100 (oscillation frequency 8 MHz) or CSA12.0MT100 (oscillation frequency 12MHz) or the equivalent:

Oscillation ferquency

f:8MHz

CIN = COUT = 30pF

f:12MHz

CIN = COUT = 30pF

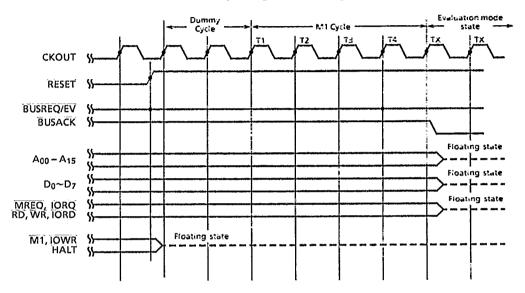

# 3.4.10 Evaluator Functions

The TMPZ84C112A has a pin (BUSREQ/EV pin) which can isolate the CPU so that it can function as an evaluator chip. This pin makes it possible to electrically isolate the built-in CPU (with high impedance) and perform emulations by receiving signals from an ICE (In-Circuit Emulator).

In this case, after the  $\overline{BUSREQ/EV}$  pin is set to "0" and a reset is applied with the  $\overline{RESET}$  pin, the built-in CPU executes one machine cycle and becomes electrically isolated. After that, all sections of the device except the CPU are operated by instructions from the ICE CPU.

Table 3.4.3 shows the signal names for the isolated CPU and Figure 3.4.12 shows the signal timing.

Table 3.4.3 Isolated Pin Names

| Isolation timing<br>condition<br>BUSREQ/EV = 0 | Isolated pin name                               |

|------------------------------------------------|-------------------------------------------------|

| RESET signal rise                              | M1/IOWR, HALT pins                              |

| After 1 machine cycle                          | Pins A00~A15, D0~D7, RD,<br>WR, MREQ, IORQ/IORD |

050689

Note: Caution is required because the BUSACK pin cannot be isolated.

In other words, the emulation mode or normal mode (the built-in Z80 operates) is determined at the rise of the  $\overline{RESET}$  signal input to the TMPZ84C112A. That is, inputting "0" to the  $\overline{BUSREQ/EV}$  pin sets the evaluation mode and inputting "1" sets the normal mode.

The built-in CPU of the TMPZ84C112A is thus set to high impedance and the mode and status in which operation is performed by an external Z80 CPU are called "evaluation mode" and "inactive status". The mode and status in which the built-in Z80 CPU of the TMPZ84C112A operates are called "normal mode" and "active status".

The electrical characteristics in 4. and the timing in 5. are called, respectively, "active status" and "inactive status".

The signal which sets pins M1/IOWR and HALT to high impedance status is made effective by latching the BUSREQ/EV pin signal to "0" with the RESET pin rise signal. Because of that, fix the BUSREQ/EV pin at "0" level when developing systems to be used in the evaluation status.

Due to the above, do not heedlessly change the RESET pin signal in any status.

Figure 3.4.12 Evaluation Timing

The status in which the CPU is electrically isolated by high impedance is also called "inactive status", and the electrical characteristics and timing are indicated in the "inactive status" part.

TOSHIBA (UC/UP)

TMPZ84C112A

Figure 3.4.13 shows the method of using an adaptor board (BM8029) to interface with the target system.

Figure 3.4.13 Typical connection

(For details, refer to the BM8029 instruction manual.)

The following is a simple explanation concern-ing the adaptor board (BM8029) and target PCB.

(a) Since the TMPZ84C112A in the target system is used as the emulator LSI and an emulator is also used, the built-in CPU is replaced by the emulator by releasing all buses (using high impedance).

The emulator interface circuit can isolate the emulator using a switch in the BM8029, thus making the adaptor board operate independently. Functionally, independent operation is equivalent to that of the TMPZ84C112A.

TMPZ84C112A

The BM8029 internal connections are shown in the table below.

CN1: ICE Connections (40-pin DIP socket)

| (40-pin bir socket) |     |     |             |  |  |  |  |

|---------------------|-----|-----|-------------|--|--|--|--|

| Signal name         | Pin | no. | Signal name |  |  |  |  |

| A11                 | 1   | 40  | A10         |  |  |  |  |

| A12                 | 2   | 39  | A9          |  |  |  |  |

| A13                 | 3   | 38  | A8          |  |  |  |  |

| A14                 | 4   | 37  | A7          |  |  |  |  |

| A15                 | 5   | 36  | A6          |  |  |  |  |

| CLK                 | 6   | 35  | A5          |  |  |  |  |

| D4                  | 7   | 34  | A4          |  |  |  |  |

| D3                  | 8   | 33  | A3          |  |  |  |  |

| D5                  | 9   | 32  | A2          |  |  |  |  |

| D6                  | 10  | 31  | A1          |  |  |  |  |

| VCC                 | 11  | 30  | A0          |  |  |  |  |

| D2                  | 12  | 29  | GND         |  |  |  |  |

| D7                  | 13  | 28  | RFSH        |  |  |  |  |

| D0                  | 14  | 27  | M1          |  |  |  |  |

| D1                  | 15  | 26  | RESET       |  |  |  |  |

| INT                 | 16  | 25  | BUSREQ      |  |  |  |  |

| NMI                 | 17  | 24  | WAIT        |  |  |  |  |

| HALT                | 18  | 23  | BUSACK      |  |  |  |  |

| MREQ                | 19  | 22  | WR          |  |  |  |  |

| IORQ                | 20  | 21  | RD          |  |  |  |  |

CN2: Target System Connections (50-pin connector)

| Signal name      | Pın         | no. | Signal name |

|------------------|-------------|-----|-------------|

| *3 U·BUSACK      | 1           | 2   | BUSACK      |

| NC               | 3           | 4   | WAIT        |

| ∗3 U·BUSREO/U·EV | 3<br>5<br>7 | 6   | BUSREQU/EV  |

| NC               |             | 8   | RESET       |

|                  | 9           | 10  | -1 TEST1    |

| M1/iOWR          | 11          | 12  | OA          |

| l NC             | 13          | 14  | A2          |

| A1               | 15          | 16  | A4          |

| A3               | 17          | 18  | A6          |

| A5               | 19          | 20  | A8          |

| A7               | 21          | 22  | A10         |

| A9               | 23          | 24  | A11         |

| VCC              | 25          | 26  | •2 A13      |

|                  | 27          | 28  | A15         |

| *2 A12           | 29          | 30  | D7          |

| •2 A14           | 31          | 32  | D5          |

| NC               | 33          | 34  | D3          |

| D6               | 35          | 36  | D1          |

| D4               | 37          | 38  | •1 TEST2    |

| D2               | 39          | 40  | NMI         |

|                  | 41          | 42  | MREQ        |

| D0               | 43          | 44  | ∗3 U·RD     |

| INT              | 45          | 46  | NC          |

| HALT             | 47          | 48  | MODE        |

| IORQ/IORD        | 49          | 50  | CLK OUT     |

|                  |             |     | <del></del> |

150289

- \*1: The TEST1 and TEST2 pins are used for tests, so do not connect anything to them.

- \*2 : Do not connect anything toA12-A14when the TMPZ84C112A is operating in mode 1.

- \*3: The U-RD, U-BUSREQ/U-EV and U-BUSACK signals are used by the customer.

#### Figure 3.4.4 (a) BM8029 Pin Connection Table

(d) For target system connection, a 50-pin connector is available for direct connection to the pins of the TMPZ84C112A in the target system.

The target system can be connected by soldering directly to the TMPZ84C112A signals or by using a connector. Select in accordance with the amount of space on the target system board.

TMPZ84C112A

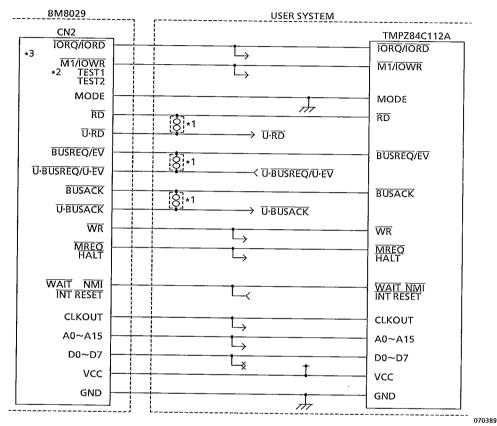

(e) Figure 3.4.13 shows connection to the adaptor board (BM8029) when the TMPZ84C112A is used in mode 0.

\* The symbols ->, -< and -X indicate connection to devices in the user system other than the TMPZ84C112A.

\*1:Connect when the adaptor board is not connected.

\*2:The TEST1 and TEST2 pins are not connected to anything.

$\star$ 3:The  $\overline{IORO/IORD}$  and  $\overline{M1/IOWR}$  pins operate as the  $\overline{IORO}$  and  $\overline{M1}$  pins in mode 0.

Figure 3.4.13 Typical Mode 0 Connection

TMPZ84C112A

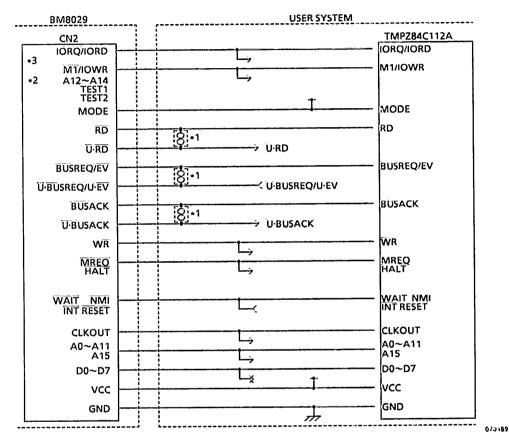

(f) Figure 3.4.14 shows connection to the adaptor board (BM8029) when the TMPZ84C112A is used in mode 1.

<sup>\*</sup> The symbols ->, -< and -X indicate connection to devices in the user system other than the TMPZ84C112A.

Figure 3.4.14 Typical Mode 1 Connection

<sup>\*1:</sup>Short when the adaptor board is not connected.

<sup>\*2:</sup>The A12 - A14, TEST1 and TEST2 pins are not connected to anything.

<sup>\*3:</sup> The IORO/IORD and M1/IOWR pins operate as the IORD and IOWR pins in mode1.

TMPZ84C112A

The evaluation mode (active status) or normal mode (active status) (the built-in Z80 operates) is determined at the rise of the RESET signal input to the TMPZ84C112A. That is, inputting "0" to the BUSREQ/EV pin sets the inactive status and inputting "1" sets the active status.

Inactive status:

used when developing a system which operates the Z80 CPU of

the I.C.E.

Active status

operates the built-in Z80 CPU.

Mode 0/mode 1 can be set using the MODE pin in any status.

Table 3.4.5 shows the various states and their conditions for the TMPZ84C112A.

Table 3.4.5 TMPZ84C112A Status

| Status<br>Condition                         | Inactive | status | Active status |        |  |  |

|---------------------------------------------|----------|--------|---------------|--------|--|--|

| BUSREQ/EV pin status at the RESET pin rise. | (        | )      |               | 1      |  |  |

| MODE pin status                             | Mode 0   | Mode 1 | Mode 0        | Mode 1 |  |  |

| WODE phristatus                             | 0        | 1      | 0             | 1      |  |  |

The following is a simple description of the development of a system using the TMPZ84C112A.

The following reference materials and development tools are available.

- 1. 8-bit microcomputer, TLCS-Z80 Development System Manual.

- 2. Adaptor board (BM8029) BM8029 Instruction Manual.

**TMPZ84C112A**

16925.6

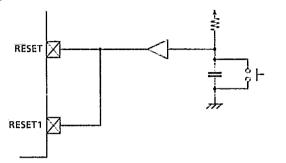

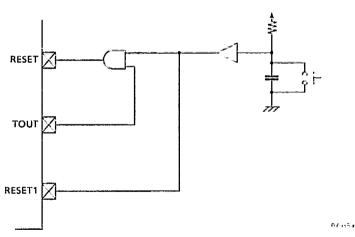

# 3.4.11 Using the RESET and RESET1 Pins

MODE pin = "1" (Mode 1)

[Example]

Figure 3.4.15 Example 1

MODE pin = "1" (Mode 1)

[Example]

Figure 3.4.16 Example 2

When MODE pin ="0" (mode 0), the PA4/RESET1 pin becomes PA4.

TMPZ84C112A

#### **ELECTRICAL CHARACTERISTICS** 4.

#### 4.1 MAXIMUM RATINGS

| SYMBOL              | ITEM                          | RATING                    | UNIT |

|---------------------|-------------------------------|---------------------------|------|

| V <sub>CC</sub>     | Supply Voltage                | -0.5~+7.0                 | V    |

| ViN                 | Input Voltage                 | -0.5~V <sub>CC</sub> +0.5 |      |

| PD                  | Power Dissipation (Ta = 85°C) | 250                       | mV   |

| T <sub>SOLDER</sub> | Soldering Temperature (10sec) | 260                       | °C   |

| T <sub>STG</sub>    | Storage Temperature           | -55~150                   | °C   |

| T <sub>OPR</sub>    | Operating Temperature         | -10~70                    | °C   |

090689

# 4.2 DC ELECTRICAL CHARACTERISTICS

$T_{OPR} = -10^{\circ}C \sim 70^{\circ}C, V_{CC} = 5V \pm 10\%, V_{SS} = 0V$

| SYMBOL           | ITEM                                                      | TEST CONDITI                                                                                                 | ON                | MIN.                  | TYP. | MAX.                  | UNIT |

|------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|------|-----------------------|------|

| V <sub>ILC</sub> | Low level Clock input voltage<br>(During external input)  |                                                                                                              |                   | -0.3                  | _    | 0.6                   | V    |

| V <sub>IHC</sub> | High level Clock input voltage<br>(During external input) |                                                                                                              |                   | V <sub>CC</sub> – 0.6 | _    | V <sub>CC</sub> + 0.3 | V    |

| V <sub>ILS</sub> | Input Low level voltage<br>(RESET, RESET1)                | V <sub>CC</sub> ≥ 4.5V                                                                                       |                   | 0                     | _    | V <sub>CC</sub> *0.25 | V    |

| V <sub>IHS</sub> | Input High level voltage<br>(RESET, RESET1)               | V <sub>CC</sub> ≥ 4.5V                                                                                       |                   | V <sub>CC</sub> *0.75 | _    | V <sub>CC</sub>       | V    |

| V <sub>IL1</sub> | Input Low level voltage (MODE)                            |                                                                                                              | -                 | 0                     | _    | V <sub>CC</sub> *0.3  | V    |

| V <sub>IH1</sub> | Input High level voltage (MODE)                           |                                                                                                              |                   | V <sub>CC</sub> *0.7  | -    | Vcc                   | V    |

| V <sub>IL</sub>  | Input Low level voltage                                   |                                                                                                              |                   | -0.5                  | _    | 0.6                   | V    |

| VIHE             | Input High level voltage                                  |                                                                                                              |                   | 2.3                   | _    | Vcc                   | V    |

| V <sub>OL</sub>  | Output Low voltage                                        | I <sub>OL</sub> = 2.0mA                                                                                      |                   | _                     |      | 0.4                   | V    |

| V <sub>OH1</sub> | Output High voltage ( I )                                 | l <sub>OH</sub> = - 1.6mA                                                                                    |                   | 2.4                   | _    |                       | V    |

| V <sub>OH2</sub> | Output High voltage (II)                                  | $I_{OH} = -250 \mu A$                                                                                        |                   | V <sub>CC</sub> - 0.8 |      | _                     | V    |

| l <sub>LI</sub>  | Input Leakage Current                                     | $V_{SS} \leq V_{IN} \leq V_{CC}$                                                                             |                   | _                     | _    | ± 10                  | μΑ   |

| l <sub>LO</sub>  | 3-State Output Leakage Current in Flat                    | $V_{SS} + 0.4 \le V_{OUT} \le$                                                                               | € V <sub>CC</sub> | _                     | _    | ± 10                  | μΑ   |

| I <sub>CC1</sub> | Power supply Current                                      | V <sub>CC</sub> = 5V<br>f <sub>CLK</sub> = (Note 1)<br>V <sub>IHC</sub> = V <sub>IH</sub> = V <sub>IH1</sub> | 4MHz              |                       | 10   | 20                    | mA   |

| 501              |                                                           | $= V_{HS} = V_{CC} - 0.2V$<br>$V_{ILC} = V_{IL} = V_{IL1}$<br>$= V_{LS} = 0.2V$                              | 6.144<br>MHz      | _                     | 15   | 25                    | mA   |

Note 1:  $f_{CLK} = 1/T_{CC}$  (MIN)

090689

#### TMPZ84C112A

# 4.3 AC Electrical Characteristics (Active State 1/3)

TOPR=-10°C~70°C, VCC=5V±10°2, VSS=0V

| No. | SYMBOL           | PARAMETER                                              | CKO<br>4M |      | CKOUT =<br>6.144MHZ |     | UNIT |

|-----|------------------|--------------------------------------------------------|-----------|------|---------------------|-----|------|

|     |                  |                                                        | MIN.      | MAX. | MIN.                | MAX |      |

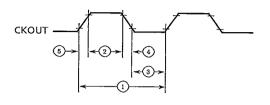

| 1   | T <sub>C</sub> C | Clock Cycle Time                                       | 250       | DC   | 162                 | DC  | ns   |

| 2   | TwCh             | Clock Pulse Width (High)                               | 110       | DC   | 65                  | DC  | ns   |

| 3   | TwCl             | Clock Pulse Width (Low)                                | 110       | DC   | 65                  | DC  | ns   |

| 4   | TfC              | Cock Fall Time                                         |           | 30   |                     | 20  | ns   |

| 5   | TrC              | Clock Rise Time                                        | _         | 30   | _                   | 20  | ns   |

| 6   | TdCr (A)         | Clock ↑ to Address Valid Delay                         |           | 110  | _                   | 90  | ns   |

| 7   | TdA (MREQf)      | Address Valid to MREQ 1 Delay                          | 65        |      | 35                  | -   | ns   |

| 8   | TdCf (MREQf)     | Clock J to MREQ J Delay                                |           | 85   | _                   | 70  | ns   |

| 9   | TdCr (MREQr)     | Clock ↑ to MREQ ↑ Delay                                |           | 85   | –                   | 70  | ns   |

| 10  | TwMREQh          | MREQ Pulse Width (High)                                | 110       | -    | 65                  | _   | ns   |

| 11  | TwMREQI          | MREQ Pulse Width (Low)                                 | 220       |      | 135                 | -   | ns   |

| 12  | TdCf (MREQr)     | Clock ↓ to MREQ ↑ Delay                                | _         | 85   | -                   | 70  | ns   |

| 13  | TdCf (RDf)       | Clock 1 to RD 1 Delay                                  | _         | 95   |                     | 80  | ns   |

| 14  | TdCr (RDr)       | Clock † to RD † Delay                                  | -         | 85   | _                   | 70  | ns   |

| 15  | TsD (Cr)         | Data Setup Time to Clock ?                             | 35        | _    | 30                  |     | ns   |

| 16  | ThD (RDr)        | Data Hold Time to RD ↑                                 | 0         |      | 0                   | _   | ns   |

| 17  | TsWAIT (Cf)      | WAIT Setup Time to Clock 1                             | 70        |      | 60                  | -   | ns   |

| 18  | ThWAIT (Cf)      | WAIT Hold Timer after Clock !                          | 10        | -    | 10                  |     | ns   |

| 19  | TdCr (M1f)       | Clock ↑ to M1 ↓ Delay                                  | -         | 100  | _                   | 80  | ns   |

| 20  | TdC r(M1r)       | Clock ↑ to M1 ↑ Delay                                  | -         | 100  | _                   | 80  | ns   |

| 21  | TdCf (RDr)       | Clock ↓ to RD ↑ Delay                                  |           | 85   | _                   | 70  | ns   |

| 22  | TdCr (RDf)       | Clock ↑ to RD ↓ Delay                                  | -         | 85   | _                   | 70  | ns   |

| 23  | TsD (Cf)         | Data Setup to Clock 1 during M2,<br>M3, M4 or M5 Cycle | 50        | _    | 40                  | _   | ns   |

| 24  | TdA (IORQf)      | Address Stable prior IORQ 1                            | 180       | -    | 110                 | -   | ns   |

| 25  | TdCr (IORQf)     | Clock ↑ to IORQ ↓ Delay                                | _         | 75   | _                   | 65  | ns   |

| 26  | TdCf (IORQr)     | Clock ↓ to IORQ ↑ Delay                                | _         | 85   | _                   | 70  | пѕ   |

| 27  | TdD (WRf)        | Data Stable Prior to WR J                              | 80        |      | 25                  |     | ns   |

| 28  | TdCf (WRf)       | Clock 1 to WR 1 Delay                                  | -         | 80   | -                   | 70  | ns   |

| 29  | TwWR             | WR Pulse Width                                         | 220       |      | 135                 |     | ns   |

6.01669

TMPZ84C112A

# AC Electrical Characeristics (Active State 2/3)

| No. | SYMBOL         | PARAMETER                                                         | CKOUT =<br>4MHZ |      | CKOUT =<br>6.144MHZ |      | UNIT |

|-----|----------------|-------------------------------------------------------------------|-----------------|------|---------------------|------|------|

|     |                | :                                                                 | MIN.            | MAX. | MIN.                | MAX. |      |

| 30  | TdCf (WRr)     | Clock ↓ to WR ↑ Delay                                             | -               | 80   | _                   | 70   | ns   |

| 31  | TdD (WRf)      | Data Stable Prior to WR ↓                                         | -10             | _    | -55                 | -    | ns   |

| 32  | TdCr (WRf)     | Clock ↑ to WR ↓ Dealy                                             |                 | 65   | _                   | 60   | ns   |

| 33  | TdWRr (D)      | Data Stable from WR↑                                              | 60              |      | 30                  | -    | ns   |

| 34  | TdCf (HALT)    | Clock↓to HALT↑or↓                                                 | _               | 300  | _                   | 260  | ns   |

| 35  | TwNMI          | NMI Pulse Width                                                   | 120             | _    | 120                 | -    | ns   |

| 36  | TsBUSREQ (Cr)  | BUSREQ Setup Time to Clock↑                                       | 50              | _    | 50                  | -    | ns   |

| 37  | ThBUSREQ (Cr)  | BUSREQ Hold Time after CLock ↑                                    | 10              | -    | 10                  | -    | ns   |

| 38  | TdCr (BUSACKf) | Clock ↑ to BUSACK ↓ Delay                                         | _               | 100  | _                   | 90   | ns   |

| 39  | TdCf (BUSACKr) | Clock ↓ to BUSACK ↑ Delay                                         | _               | 100  | -                   | 90   | ns   |

| 40  | TdCr (Dz)      | Clock ↑ to Data Float Delay                                       | _               | 90   | -                   | 80   | ns   |

| 41  | TdCr (CTz)     | Clock ↑ to Control Outputs Float<br>Delay (MREQ, IORQ, RD and WR) | _               | 80   |                     | 70   | ns   |

| 42  | TdCr (Az)      | Clock ↑ to Address Float Delay                                    | _               | 90   | _                   | 80   | ns   |

| 43  | TdCr (A)       | MREQ ↑, IORQ ↑, RD ↑, and WR ↑ to Address Hold Time               | 80              | _    | 35                  | _    | ns   |

| 44  | TsRESET (Cr)   | RESET to Clock↑Setup Time                                         | 60              |      | 60                  | _    | ns   |

| 45  | ThRESET (Cr)   | RESET to Clock↑ Hold Time                                         | 10              |      | 10                  |      | ns   |

| 46  | TsINTf (Cr)    | INT to Clock ↑ Setup Time                                         | 80              | -    | 70                  | _    | ns   |

| 47  | TsINTr (Cr)    | INT to Clock ↑ Hold Time                                          | 10              | -    | 10                  | _    | ns   |

| 48  | TdM1f (IORQf)  | M1   to   IORQ   Delay                                            | 565             |      | 365                 | _    | ns   |

| 49  | TdCf (IORQf)   | Clock j to IORQ j Delay                                           | _               | 85   | _                   | 70   | ns   |

| 50  | TdCr (IORQr)   | Clock ↑ to IORQ ↑ Delay                                           | -               | 85   |                     | 70   | ns   |

| 51  | TdCf (D)       | Clock J. Data Valid Delay                                         | _               | 150  | _                   | 130  | ns   |

| 52  | TdCf (POUT)    | Clock 🕽 to Port Data Delay                                        |                 | 400  |                     | 300  | ns   |

| 53  | TSPIN (IORDf)  | Port Input Setup Time to <del>IORQ</del> , RD↓                    | 0               | _    | 0                   | _    | ns   |

| 54  | Th PIN         | Port Input Hold Time to IORQ,<br>RD↑                              | 0               | -    | 0                   | _    | ns   |

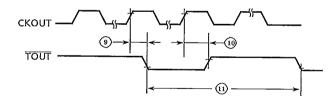

| 55  | TdC (TOUTf)    | Clock ↑ to TOUT ↓ Delay                                           | _               | 240  | -                   | 160  | ns   |

| 56  | Td (TOUTr)     | Clock↑to TOUT↑ Delay                                              |                 |      |                     | 165  | ns   |

090689

TMPZ84C112A

# AC Electrical Characeristics (Active State 3/3)

| No. | SYMBOL       | PARAMETER                   |                                                                                                                                                  | CKOUT =<br>4MHZ |                                                                                                      | CKOUT =<br>6.144MHZ |    |

|-----|--------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------|---------------------|----|

|     |              |                             | MIN.                                                                                                                                             | MAX.            | MIN.                                                                                                 | MAX.                |    |

| 57  | Τετουττ      | TOUT Cycle < #80 < 3, 2 > > | Typ. T1 * 2 <sup>1</sup> / <sub>4</sub> |                 | Typ.<br>T1 * 2 <sup>14</sup><br>T1 * 2 <sup>13</sup><br>T1 * 2 <sup>14</sup><br>T1 * 2 <sup>15</sup> |                     | ns |

| 58  | Tdcr(IOWRf)  | Clock † to IOWR J Delay     | _                                                                                                                                                | 80              |                                                                                                      | 70                  | ns |

| 59  | Tdcf (IOWRf) | Clock J to IOWR ↑ Delay     | _                                                                                                                                                | 90              | -                                                                                                    | 75                  | ns |

| 60  | Tdcr (IORDf) | Clock † to IORD ! Delay     | -                                                                                                                                                | 90              | -                                                                                                    | 75                  | ns |

| 61  | Tdcf (IORDf) | Clock J to IORD † Delay     | -                                                                                                                                                | 90              | -                                                                                                    | 75                  | ns |

Note 1: AC Test condition (1) VCC=5V±10%, VIH=2.4V, VIL=0.4V, VIHC=VCC-0.6V, VILC=0.6V, VOH=2.2V, VOL=0.8V والمقوسون

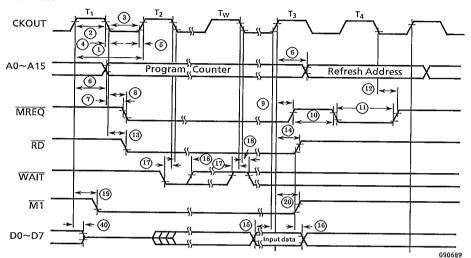

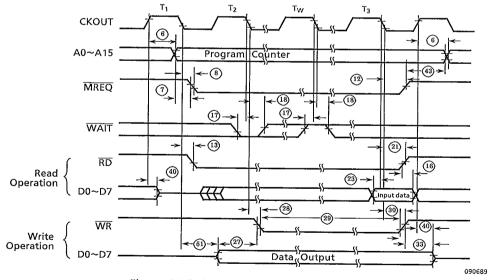

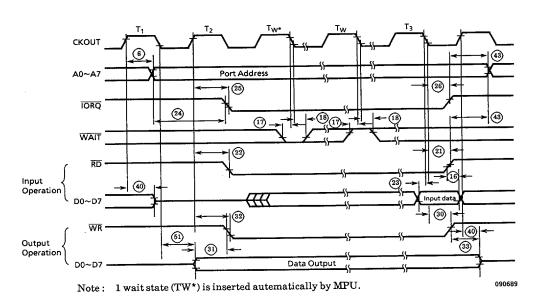

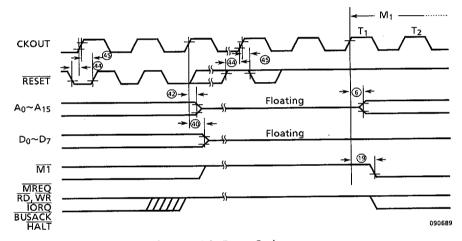

# 4.4 Timing Diagram (Active State)

Figure 4.4.1 to 4.4.9 show the basic timing of respective operations. Numbers shown in the Figures correspond with those in the AC ELECTRICAL CHARACTERISTICS Table in 4.3.

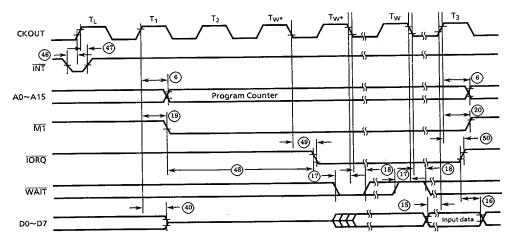

Figure 4.4.1 OP-Code Fetch Cycle

Figure 4.4.2 Memory Read/Write Cycle

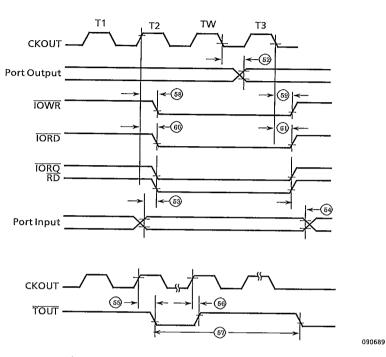

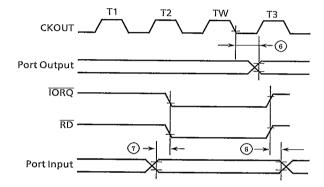

Figure 4.4.3 Input/Output Cycle

Note 1: TL is the final state of the preceding instruction.

Note 2: 2 wait state (TW\*) is inserted automatically by MPU.

090689

Figure 4.4.4 Interrupt Request/Acknowledge Cycle

TMPZ84C112A

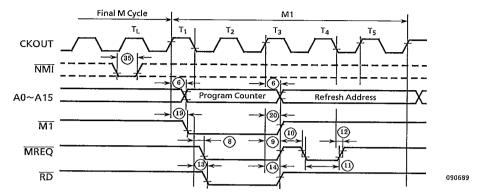

Note: NMI is asynchronous input but in order to assure the positive response in the following cycle, NMI trailing edge signal must be generated keeping abreast of the leading edge of preceding TL state.

Figure 4.4.5 Non-Maskable Interrupt Request Cycle

Note 1: TL is the final state of any machine cycle.

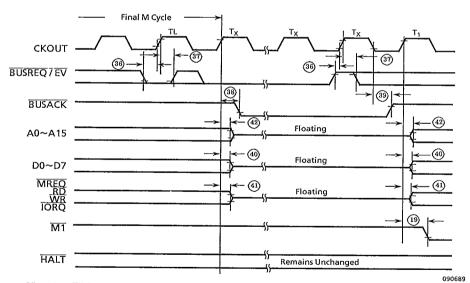

Note 2: TX is optional clock used by requested peripheral LSI.

Figure 4.4.6 Bus Request/Acknowledge Cycle

TMPZ84C112A

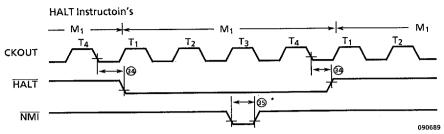

Note:  $\overline{INT}$  signal is also used for releasing from the halt state.

Figure 4.4.7 HALT Acknowledge Cycle

Figure 4.4.8 Reset Cycle

Figure 4.4.9 Input/Output Timing

TMPZ84C112A

# 4.5 AC ELECTRICAL CHARACTERISTICS (Inactive State)

$T_{OPR} = -10^{\circ}C \sim 70^{\circ}C, \ V_{CC} = 5V \pm 10\%, \ V_{SS} = 0V$

| No. | SYMBOL        | PARAMETER                                                                              | CKOUT = 4MHz                                                                             |      | CKOUT = 6.144MHZ                                                                         |      | UNIT |

|-----|---------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------|------|------|

|     |               |                                                                                        | MIN.                                                                                     | MAX. | MIN.                                                                                     | MAX. | ONT  |

| 1   | TcC (OUT)     | Clock Cycle Time (Output)                                                              | 250                                                                                      | DC   | 162                                                                                      | DC   | ns   |

| 2   | TwCh (OUT)    | Clock Pulse Width (High Output)                                                        | 110                                                                                      | DC   | 65                                                                                       | DC   | ns   |

| 3   | Twcl (OUT)    | Clock Pulse Width (Low Output)                                                         | 110                                                                                      | DC   | 65                                                                                       | DC   | ns   |

| 4   | TfC (OUT)     | Clock Fall Time (Output)                                                               | _                                                                                        | 30   |                                                                                          | 20   | ns   |

| . 5 | TrC (OUT)     | Clock Rise Time (Output)                                                               | _                                                                                        | 30   |                                                                                          | 20   | ns   |

| 6   | TdCf (POUT)   | Clock ↓ to Port Data Delay                                                             | _                                                                                        | 400  |                                                                                          | 300  | ns   |

| 7   | TSPIN (IORDf) | Port Input Setup Time to $\overline{IORQ}$ , $\overline{RD}\downarrow$                 | 0                                                                                        | _    | 0                                                                                        | _    | ns   |

| 8   | Th PIN        | Port Input Hold Time to $\overline{IORQ}$ , $\overline{RD} \uparrow$                   | 0                                                                                        |      | 0                                                                                        | -    | ns   |

| 9   | TdC (TOUTf)   | Clock ↑ to TOUT ↓ Delay                                                                |                                                                                          | 240  |                                                                                          | 160  | ns   |

| 10  | Td (TOUTr)    | Clock ↑ to TOUT ↑ Delay                                                                | -                                                                                        | 250  |                                                                                          | 165  | ns   |

| 11  | тстоитт       | TOUT Cycle < #80 < 3, 2 >><br>Mode 0 : 00<br>Mode 1 : 01<br>Mode 2 : 10<br>Mode 3 : 11 | Typ. T1 * 2 <sup>12</sup> T1 * 2 <sup>13</sup> T1 * 2 <sup>14</sup> T1 * 2 <sup>15</sup> |      | Typ. T1 * 2 <sup>12</sup> T1 * 2 <sup>13</sup> T1 * 2 <sup>14</sup> T1 * 2 <sup>15</sup> |      | ns:  |

090689

$\label{eq:Note 1: AC Test condition (1) VCC = 5V \pm 10\%,} $$ VIH = 2.4V, VIL = 0.4V, VIHC = VCC-0.6V $$ VILC = 0.6V, VOH = 2.2V, VOL = 0.8V $$$

TMPZ84C112A

# 4.6 AC Timing Diagram (Inactive State)

090689

Figure 4.6.1 Input/Output Timing

TMPZ84C112A

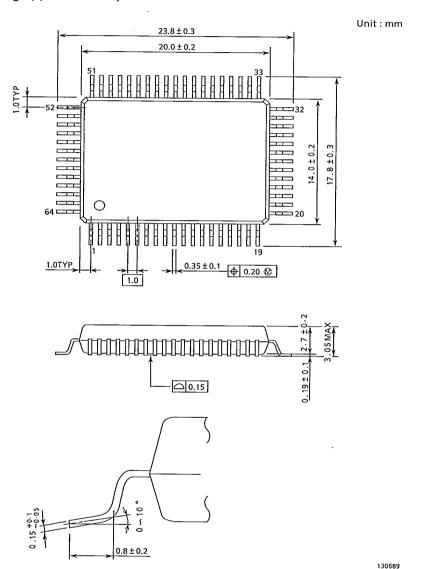

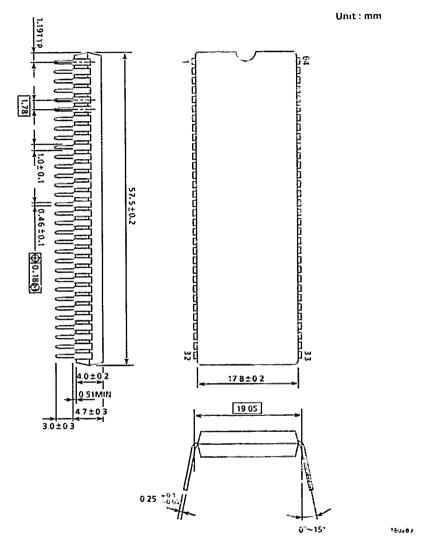

# 5. EXTERNAL DIMENSIONS

# TMPZ84C112AN-6

5.1 DIP Package (SDIP64-P-750)

Note: All the leads are located within  $\pm 0.25$ mm from their theoretical positions with respect to No.1 and No.64 leads.

### TMPZ84C112A

# 5.2 QFP Package (QFP64-P-1420A)