# PRELIMINARY PRODUCT INFORMATION

# MOS INTEGRATED CIRCUIT $\mu$ PD161831

# 240/244-OUTPUT TFT-LCD SOURCE DRIVER WITH TIMING GENERATOR (COMPATIBLE WITH 64-GRAY SCALES)

#### **DESCRIPTION**

The  $\mu$ PD161831 is a source driver for LIPS TFTs with on-chip timing generator and featuring 240/244 outputs. Data input as 6-bit x 3-dot digital data is output as 64  $\gamma$ -corrected values using an internal D/A converter, achieving 260,000-color (full-color) display.

#### **FEATURES**

- CMOS level input

- 240/244 outputs (R, G, B output)

- Input of 6 bits (gray-scale data) by 3 dots

- Capable of outputting 64 values by means of 5 external power modules and a D/A converter

- Output dynamic range: Vss + 0.05 V to Vs 0.05 V

- High-speed data transfer: fclk = 20 MHz MAX. (during 2-times data transfer when operating at Vcc = 2.5 V. During 1-time data transfer 10 MHz MAX.)

- High-speed data transfer: fclk = 16 MHz MAX. (during 2-times data transfer when operating at Vcc = 2.2 V. During 1-time data transfer 8 MHz MAX.)

- On-chip power supplies (driver power supply, gate top power supply, gate bottom power supply)

- Logic power supply voltage (Vcc): 2.2 to 3.6 V

- DC/DC reference power supply (VDC): 2.5 to 3.6 V

- On-chip timing generator (Outputs R, G, B switching signal to panel. Outputs gate control signal.)

- On-chip 8-bit serial interface (applied to SPI)

#### ORDERING INFORMATION

| Part Number | Package |

|-------------|---------|

| μPD161831P  | Chip    |

**Remark** Purchasing the above chip entail the exchange of documents such as a separate memorandum or product quality, so please contact one of our sales representatives.

The information contained in this document is being issued in advance of the production cycle for the device. The parameters for the device may change before final production or NEC Corporation, at its own discretion, may withdraw the device prior to its production.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

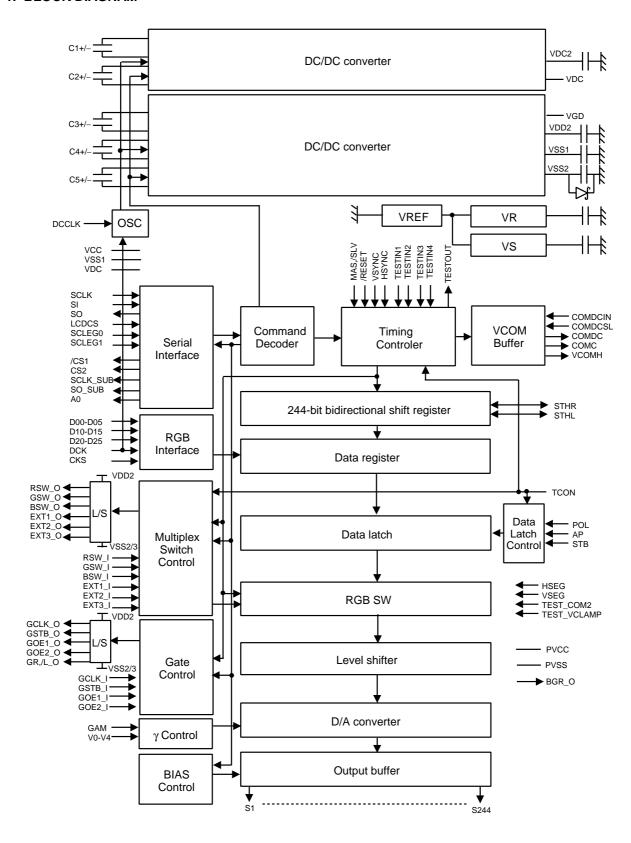

#### \* 1. BLOCK DIAGRAM

Remark /xxx indicates active low signal.

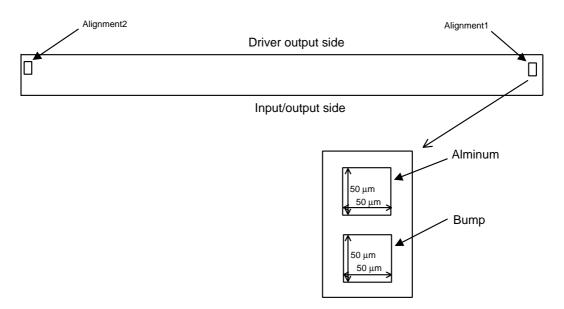

# 2. PIN CONFIGURATION (Pad Layout)

Chip size: T.B.D.

Bump size: INPUT/VCOM/TEST/DUMMY: 50 x 75  $\mu$ m<sup>2</sup>

OUTPUT: 35 x 100  $\mu$ m<sup>2</sup>

Remark T.B.D.: To be determined.

Alignment Mark (Unit: μm)

|            |                 | X Coordinate | Y Coordinate |

|------------|-----------------|--------------|--------------|

| Alignment1 | Aluminum (core) | 10768.0      | 441.0        |

|            | Bump (core)     | 10768.0      | 366.0        |

| Alignment2 | Aluminum (core) | -10768.0     | 441.0        |

|            | Bump (core)     | -10768.0     | 366.0        |

**Remark** The figures are rounded off in 0.5  $\mu$ m units.

Table 2-1. Pad Layout (1/2)

| No.      | PAD Name       | X [μm]              | Υ [μm]           | No.        | PAD Name     | X [μm]             | Y [μm]           | No.        | PAD Name     | X [μm]               | Υ [μm]           | No.        | PAD Name       | X [μm]               | Υ [μm]           |

|----------|----------------|---------------------|------------------|------------|--------------|--------------------|------------------|------------|--------------|----------------------|------------------|------------|----------------|----------------------|------------------|

| 1        | Dummy          | 10797.00            | 594.99           | 71         | S178         | 5820.00            | 594.99           | 141        | S108         | 1620.00              | 594.99           | 211        | S38            | -2580.00             | 594.99           |

| 2        | Dummy          | 10737.00            | 594.99           | 72         | S177         | 5760.00            | 594.99           | 142        | S107         | 1560.00              | 594.99           | 212        | S37            | -2640.00             | 594.99           |

| <u>3</u> | Dummy<br>Dummy | 10677.00<br>9840.00 | 594.99<br>594.99 | 73<br>74   |              | 5700.00<br>5640.00 | 594.99<br>594.99 | 143        | S106<br>S105 | 1500.00<br>1440.00   | 594.99<br>594.99 | 213<br>214 | S36<br>S35     | -2700.00<br>-2760.00 | 594.99<br>594.99 |

| 5        | S244           | 9780.00             | 594.99           | 75         |              | 5580.00            | 594.99           | 145        | S103         | 1380.00              | 594.99           | 215        | S34            | -2820.00             | 594.99           |

| 6        | S243           | 9720.00             | 594.99           | 76         |              | 5520.00            | 594.99           | 146        | S103         | 1320.00              | 594.99           | 216        |                | -2880.00             | 594.99           |

| 7        | S242           | 9660.00             | 594.99           | 77         | S172         | 5460.00            | 594.99           | 147        | S102         | 1260.00              | 594.99           | 217        | S32            | -2940.00             | 594.99           |

| 8        | S241           | 9600.00             | 594.99           | 78         |              | 5400.00            | 594.99           | 148        | S101         | 1200.00              | 594.99           | 218        |                | -3000.00             | 594.99           |

| 9        | S240           | 9540.00             | 594.99           | 79         |              | 5340.00            | 594.99           | 149        | S100         | 1140.00              | 594.99           | 219        | S30            | -3060.00             | 594.99           |

| 10       | S239           | 9480.00             | 594.99           | 80         |              | 5280.00            | 594.99           | 150        | S99          | 1080.00              | 594.99           | 220        | S29            | -3120.00             | 594.99           |

| 11<br>12 | S238<br>S237   | 9420.00<br>9360.00  | 594.99<br>594.99 | 81<br>82   | S168<br>S167 | 5220.00<br>5160.00 | 594.99<br>594.99 | 151<br>152 | S98<br>S97   | 1020.00<br>960.00    | 594.99<br>594.99 | 221<br>222 | S28<br>S27     | -3180.00<br>-3240.00 | 594.99<br>594.99 |

| 13       | S236           | 9300.00             | 594.99           | 83         | S166         | 5100.00            | 594.99           | 153        | S96          | 900.00               | 594.99           | 223        | S26            | -3300.00             | 594.99           |

| 14       | S235           | 9240.00             | 594.99           | 84         |              | 5040.00            | 594.99           | 154        | S95          | 840.00               | 594.99           | 224        | S25            | -3360.00             | 594.99           |

| 15       | S234           | 9180.00             | 594.99           | 85         |              | 4980.00            | 594.99           | 155        | S94          | 780.00               | 594.99           | 225        | S24            | -3420.00             | 594.99           |

| 16       | S233           | 9120.00             | 594.99           | 86         |              | 4920.00            | 594.99           | 156        | S93          | 720.00               | 594.99           | 226        | S23            | -3480.00             | 594.99           |

| 17       | S232           | 9060.00             | 594.99           | 87         | S162         | 4860.00            | 594.99           | 157        | S92          | 660.00               | 594.99           | 227        | S22            | -3540.00             | 594.99           |

| 18<br>19 | S231<br>S230   | 9000.00<br>8940.00  | 594.99<br>594.99 | 88<br>89   |              | 4800.00<br>4740.00 | 594.99<br>594.99 | 158<br>159 | S91<br>S90   | 600.00<br>540.00     | 594.99<br>594.99 | 228<br>229 | S21<br>S20     | -3600.00<br>-3660.00 | 594.99<br>594.99 |

| 20       | S229           | 8880.00             | 594.99           | 90         | S159         | 4680.00            | 594.99           | 160        | S89          | 480.00               | 594.99           | 230        | S19            | -3720.00             | 594.99           |

| 21       | S228           | 8820.00             | 594.99           | 91         | S158         | 4620.00            | 594.99           | 161        | S88          | 420.00               | 594.99           | 231        | S18            | -3780.00             | 594.99           |

| 22       | S227           | 8760.00             | 594.99           | 92         | S157         | 4560.00            | 594.99           | 162        | S87          | 360.00               | 594.99           | 232        | S17            | -3840.00             | 594.99           |

| 23       | S226           | 8700.00             | 594.99           | 93         | S156         | 4500.00            | 594.99           | 163        | S86          | 300.00               | 594.99           | 233        | S16            | -3900.00             | 594.99           |

| 24       | S225           | 8640.00             | 594.99           | 94         |              | 4440.00            | 594.99           | 164        | S85          | 240.00               | 594.99           | 234        | S15            | -3960.00             | 594.99           |

| 25<br>26 | S224<br>S223   | 8580.00<br>8520.00  | 594.99<br>594.99 | 95<br>96   |              | 4380.00<br>4320.00 | 594.99<br>594.99 | 165<br>166 | S84<br>S83   | 180.00<br>120.00     | 594.99<br>594.99 | 235<br>236 | S14<br>S13     | -4020.00<br>-4080.00 | 594.99<br>594.99 |

| 27       | S222           | 8460.00             | 594.99           | 97         | S152         | 4260.00            | 594.99           | 167        | S82          | 60.00                | 594.99           | 237        | S12            | -4140.00             | 594.99           |

| 28       | S221           | 8400.00             | 594.99           | 98         |              | 4200.00            | 594.99           | 168        | S81          | 0.00                 | 594.99           | 238        | S11            | -4200.00             | 594.99           |

| 29       | S220           | 8340.00             | 594.99           | 99         | S150         | 4140.00            | 594.99           | 169        | S80          | -60.00               | 594.99           | 239        |                | -4260.00             | 594.99           |

| 30       | S219           | 8280.00             | 594.99           | 100        | S149         | 4080.00            | 594.99           | 170        | S79          | -120.00              | 594.99           | 240        | S9             | -4320.00             | 594.99           |

| 31       | S218           | 8220.00             | 594.99           | 101        | S148         | 4020.00            | 594.99           | 171<br>172 | S78          | -180.00              | 594.99           | 241        | S8             | -4380.00             | 594.99           |

| 32       | S217<br>S216   | 8160.00<br>8100.00  | 594.99<br>594.99 | 102        | S147<br>S146 | 3960.00<br>3900.00 | 594.99<br>594.99 | 173        | S77<br>S76   | -240.00<br>-300.00   | 594.99<br>594.99 | 242<br>243 | S7<br>S6       | -4440.00<br>-4500.00 | 594.99<br>594.99 |

| 34       | S215           | 8040.00             | 594.99           | 103        | S145         | 3840.00            | 594.99           | 174        | S75          | -360.00              | 594.99           | 244        | S5             | -4560.00             | 594.99           |

| 35       | S214           | 7980.00             | 594.99           | 105        | S144         | 3780.00            | 594.99           | 175        | S74          | -420.00              | 594.99           | 245        |                | -4620.00             | 594.99           |

| 36       | S213           | 7920.00             | 594.99           | 106        |              | 3720.00            | 594.99           | 176        | S73          | -480.00              | 594.99           | 246        |                | -4680.00             | 594.99           |

| 37       | S212           | 7860.00             | 594.99           | 107        | S142         | 3660.00            | 594.99           | 177        | S72          | -540.00              | 594.99           | 247        | S2             | -4740.00             | 594.99           |

| 38<br>39 | S211<br>S210   | 7800.00<br>7740.00  | 594.99<br>594.99 | 108<br>109 | S141<br>S140 | 3600.00<br>3540.00 | 594.99<br>594.99 | 178<br>179 | S71<br>S70   | -600.00<br>-660.00   | 594.99<br>594.99 | 248<br>249 | S1<br>Dummy    | -4800.00<br>-4860.00 | 594.99<br>594.99 |

| 40       | S210           | 7680.00             | 594.99           | 110        | S139         | 3480.00            | 594.99           | 180        | S69          | -720.00              | 594.99           | 250        | Dummy          | -4920.00             | 594.99           |

| 41       | S208           | 7620.00             | 594.99           | 111        | S138         | 3420.00            | 594.99           | 181        | S68          | -780.00              | 594.99           | 251        | Dummy          | -4980.00             | 594.99           |

| 42       | S207           | 7560.00             | 594.99           | 112        | S137         | 3360.00            | 594.99           | 182        | S67          | -840.00              | 594.99           | 252        | Dummy          | -5040.00             | 594.99           |

| 43       | S206           | 7500.00             | 594.99           | 113        |              | 3300.00            | 594.99           | 183        | S66          | -900.00              | 594.99           | 253        | Dummy          | -5100.00             | 594.99           |

| 44       | S205           | 7440.00             | 594.99           | 114        | S135         | 3240.00            | 594.99           | 184        | S65          | -960.00              | 594.99           | 254        | Dummy          | -5160.00             | 594.99           |

| 45<br>46 | S204<br>S203   | 7380.00<br>7320.00  | 594.99<br>594.99 | 115<br>116 |              | 3180.00<br>3120.00 | 594.99<br>594.99 | 185<br>186 | S64<br>S63   | -1020.00<br>-1080.00 | 594.99<br>594.99 | 255<br>256 | Dummy<br>Dummy | -5220.00<br>-5280.00 | 594.99<br>594.99 |

| 47       | S202           | 7260.00             | 594.99           | 117        | S132         | 3060.00            | 594.99           | 187        | S62          | -1140.00             | 594.99           | 257        | Dummy          | -5340.00             | 594.99           |

| 48       | S201           | 7200.00             | 594.99           | 118        |              | 3000.00            | 594.99           | 188        | S61          | -1200.00             | 594.99           | 258        | Dummy          | -5400.00             | 594.99           |

| 49       | S200           | 7140.00             | 594.99           | 119        |              | 2940.00            | 594.99           | 189        | S60          | -1260.00             | 594.99           | 259        | Dummy          | -5460.00             | 594.99           |

| 50       | S199           | 7080.00             | 594.99           | 120        | S129         | 2880.00            | 594.99           | 190        | S59          | -1320.00             | 594.99           | 260        | Dummy          | -5520.00             | 594.99           |

| 51<br>52 | S198<br>S197   | 7020.00<br>6960.00  | 594.99<br>594.99 | 121<br>122 | S128<br>S127 | 2820.00<br>2760.00 | 594.99<br>594.99 | 191<br>192 | S58<br>S57   | -1380.00<br>-1440.00 | 594.99<br>594.99 | 261<br>262 | Dummy<br>Dummy | -5580.00<br>-5640.00 | 594.99<br>594.99 |

| 53       | S197<br>S196   | 6900.00             | 594.99           | 123        | S127<br>S126 | 2700.00            | 594.99           | 192        | S56          | -1440.00             | 594.99           | 262        | Dummy          | -5700.00             | 594.99           |

| 54       | S195           | 6840.00             | 594.99           | 124        |              | 2640.00            | 594.99           | 194        | S55          | -1560.00             | 594.99           | 264        | Dummy          | -5760.00             | 594.99           |

| 55       | S194           | 6780.00             | 594.99           | 125        | S124         | 2580.00            | 594.99           | 195        | S54          | -1620.00             | 594.99           | 265        | Dummy          | -5820.00             | 594.99           |

| 56       | S193           | 6720.00             | 594.99           | 126        |              | 2520.00            | 594.99           | 196        | S53          | -1680.00             | 594.99           | 266        |                | -5880.00             | 594.99           |

| 57       | S192           | 6660.00             | 594.99           | 127        | S122         | 2460.00            | 594.99           | 197        | S52          | -1740.00             | 594.99           | 267        | Dummy          | -5940.00             | 594.99           |

| 58<br>59 | S191<br>S190   | 6600.00<br>6540.00  | 594.99<br>594.99 | 128<br>129 |              | 2400.00<br>2340.00 | 594.99<br>594.99 | 198<br>199 | S51<br>S50   | -1800.00<br>-1860.00 | 594.99<br>594.99 | 268<br>269 |                | -6000.00<br>-6060.00 | 594.99<br>594.99 |

| 60       | S189           | 6480.00             | 594.99           | 130        |              | 2280.00            | 594.99           | 200        | S49          | -1920.00             | 594.99           | 270        |                | -6120.00             | 594.99           |

| 61       | S188           | 6420.00             | 594.99           | 131        | S118         | 2220.00            | 594.99           | 201        | S48          | -1980.00             | 594.99           | 271        | Dummy          | -6180.00             | 594.99           |

| 62       | S187           | 6360.00             | 594.99           | 132        | S117         | 2160.00            | 594.99           | 202        | S47          | -2040.00             | 594.99           | 272        |                | -6240.00             | 594.99           |

| 63       | S186           | 6300.00             | 594.99           | 133        |              | 2100.00            | 594.99           | 203        | S46          | -2100.00             | 594.99           | 273        |                | -6300.00             | 594.99           |

| 64       | S185           | 6240.00             | 594.99           | 134        |              | 2040.00            | 594.99           | 204        | S45          | -2160.00             | 594.99           | 274        |                | -6360.00             | 594.99           |

| 65<br>66 | S184<br>S183   | 6180.00<br>6120.00  | 594.99<br>594.99 | 135<br>136 | S114<br>S113 | 1980.00<br>1920.00 | 594.99<br>594.99 | 205<br>206 | S44<br>S43   | -2220.00<br>-2280.00 | 594.99<br>594.99 | 275<br>276 |                | -6420.00<br>-6480.00 | 594.99<br>594.99 |

| 67       | S182           | 6060.00             | 594.99           | 137        | S113         | 1860.00            | 594.99           | 207        | S42          | -2340.00             | 594.99           | 277        |                | -6540.00             | 594.99           |

| 68       | S181           | 6000.00             | 594.99           | 138        |              | 1800.00            | 594.99           | 208        | S41          | -2400.00             | 594.99           | 278        |                | -6600.00             | 594.99           |

| 69       | S180           | 5940.00             | 594.99           | 139        | S110         | 1740.00            | 594.99           | 209        | S40          | -2460.00             | 594.99           | 279        | Dummy          | -6660.00             | 594.99           |

| 70       | S179           | 5880.00             | 594.99           | 140        | S109         | 1680.00            | 594.99           | 210        | S39          | -2520.00             | 594.99           | 280        | Dummy          | -6720.00             | 594.99           |

| _        | <u></u>        |                     | _                | _          |              |                    |                  | ·          |              |                      |                  | _          | ·              |                      |                  |

$\mu$ PD161831

Table 2-1. Pad Layout (2/2)

| No.                      | PAD Name                 | X[µm]                | Y[μm]              |

|--------------------------|--------------------------|----------------------|--------------------|

| 281                      | Dummy                    | -6780.00             | 594.99             |

| 282                      | Dummy                    | -6840.00             | 594.99             |

| 283                      | BSW_O                    | -6900.00             | 594.99             |

| 284                      | BSW_O                    | -6960.00             | 594.99             |

| 285                      | GSW_O                    | -7080.00             | 594.99             |

| 286                      | GSW_O                    | -7140.00             | 594.99             |

| 287                      | RSW_O                    | -7260.00             | 594.99             |

| 288                      | RSW_O                    | -7320.00             | 594.99             |

| 289                      | EXT3_O                   | -7440.00             | 594.99             |

| 290                      | EXT3_O                   | -7500.00             | 594.99             |

| 291                      | EXT2_O                   | -7620.00             | 594.99             |

| 292                      | EXT2_O                   | -7680.00             | 594.99             |

| 293                      | EXT1_O                   | -7800.00             | 594.99             |

| 294                      | EXT1_O                   | -7860.00             | 594.99             |

| 295                      | VSS2                     | -7980.00             | 594.99             |

| 296                      | VSS2                     | -8040.00             | 594.99             |

| 297                      | VSS2                     | -8100.00             | 594.99             |

| 298                      | VSS2                     | -8160.00             | 594.99             |

| 299                      | VSS1                     | -8280.00             | 594.99             |

| 300                      | VSS1                     | -8340.00             | 594.99             |

| 301                      | VSS1                     | -8400.00             | 594.99             |

| 302                      | VSS1                     | -8460.00             | 594.99             |

| 303                      | VDD2                     | -8580.00             | 594.99             |

| 304                      | VDD2                     | -8640.00             | 594.99             |

| 305                      | VDD2                     | -8700.00             | 594.99             |

| 306                      | VDD2                     | -8760.00             | 594.99             |

| 307                      | G0E2_0                   | -8880.00             | 594.99             |

| 308                      | G0E2_0                   | -8940.00             | 594.99             |

| 309                      | G0E2_0                   | -9000.00             | 594.99             |

| 310                      | G0E2_0                   | -9060.00             | 594.99             |

| 311                      | G0E1_0                   | -9180.00             | 594.99             |

| 312                      | G0E1_0                   | -9240.00             | 594.99             |

| 313                      | GR/L_O                   | -9360.00             | 594.99             |

| 314                      | GR/L_O                   | -9420.00             | 594.99             |

| 315                      | GCLK_O                   | -9540.00             | 594.99             |

| 316                      | GCLK_O                   | -9600.00             | 594.99             |

| 317                      | GSTB_O                   | -9720.00             | 594.99             |

| 318                      | GSTB_O                   | -9780.00             | 594.99             |

| 319                      | Dummy                    | -9840.00             | 594.99             |

| 320                      | Dummy                    | -10677.00            | 594.99             |

| 321                      | Dummy                    | -10737.00            | 594.99             |

| 322                      | Dummy                    | -10797.00            | 594.99             |

| 323                      | Dummy                    | -10788.00            | -607.50            |

| 324                      | Dummy                    | -10688.01            | -607.50            |

| 325                      | Dummy                    | -10588.02            | -607.50            |

| 326                      | Dummy                    | -9879.99             | -607.50            |

| 327                      | VSS                      | -9780.00             | -607.50            |

| 328                      | VSS                      | -9705.00             | -607.50            |

| 329                      | VSS                      | -9630.00             | -607.50            |

| 330                      | VSS                      | -9555.00             | -607.50            |

| 331                      | VSS                      | -9480.00             | -607.50            |

| 332                      | VS                       | -9380.01             | -607.50            |

| 333                      | VS                       | -9305.01             | -607.50            |

| 334                      | VS                       | -9230.01             | -607.50            |

| 335                      | VS                       | -9155.01             | -607.50            |

| 336                      | VS                       | -9080.01             | -607.50            |

| 337                      | VGD                      | -8980.02             | -607.50            |

| 338                      | VGD                      | -8905.02             | -607.50            |

| 339                      | VGD                      | -8830.02             | -607.50            |

| 340                      | VGD                      | -8755.02             | -607.50            |

| 341                      | VR                       | -8655.03             | -607.50            |

| 342                      | VR                       | -8580.03             | -607.50            |

| 343                      | VR                       | -8505.03             | -607.50            |

|                          | VR                       | -8430.03             | -607.50            |

| 344                      |                          |                      | -607.50            |

|                          | VDC                      | -8330.04             | 0000               |

| 344                      |                          | -8330.04<br>-8255.04 | -607.50            |

| 344<br>345               | VDC                      |                      |                    |

| 344<br>345<br>346        | VDC<br>VDC<br>VDC<br>VDC | -8255.04             | -607.50            |

| 344<br>345<br>346<br>347 | VDC<br>VDC<br>VDC        | -8255.04<br>-8180.04 | -607.50<br>-607.50 |

|            |             | iabi                 | e 2–1. P |

|------------|-------------|----------------------|----------|

| No.        | PAD Name    | X[µm]                | Y[µm]    |

| 351        | VDC         | -7880.04             | -607.50  |

| 352        | VDC2        | -7780.05             | -607.50  |

| 353        | VDC2        | -7705.05             | -607.50  |

| 354        | VDC2        | -7630.05             | -607.50  |

| 355        | VDC2        | -7555.05             | -607.50  |

| 356        | VDC2        | -7480.05             | -607.50  |

| 357        | VDC2        | -7405.05             | -607.50  |

| 358        | VDC2        | -7330.05             | -607.50  |

| 359        | C1+         | -7230.06             | -607.50  |

| 360        | C1+         | -7155.06             | -607.50  |

| 361        | C1+         | -7080.06             | -607.50  |

| 362        | C1+         | -7005.06             | -607.50  |

| 363        | C1+         | -6930.06             | -607.50  |

| 364        | C1+         | -6855.06             | -607.50  |

| 365        | C1+         | -6780.06             | -607.50  |

| 366        | C1-         | -6680.07             | -607.50  |

| 367        | C1-         | -6605.07             | -607.50  |

| 368        | C1-         | -6530.07             | -607.50  |

| 369        | C1-         | -6455.07             | -607.50  |

| 370        | C1-         | -6380.07             | -607.50  |

| 371        | C1-         | -6305.07             | -607.50  |

| 372        | C1-<br>C1-  | -6230.07             | -607.50  |

| 373        | C1-<br>C2+  | -6230.07<br>-6130.08 | -607.50  |

| 374        | C2+         | -6055.08             | -607.50  |

| 375        | C2+         | -5980.08             | -607.50  |

| 376        | C2+         | -5905.08             | -607.50  |

| -          |             | -5830.08             | -607.50  |

| 377<br>378 | C2+<br>C2+  | -5755.08             | -607.50  |

| 379        | C2+         | -5680.08             | -607.50  |

| 380        | C2-         | -5580.09             | -607.50  |

| 381        | C2-         | -5505.09             | -607.50  |

|            | _           |                      |          |

| 382        | C2-<br>C2-  | -5430.09             | -607.50  |

| 383        | C2-         | -5355.09             | -607.50  |

| 384        |             | -5280.09             | -607.50  |

| 385        | C2-<br>~    | -5205.09             | -607.50  |

| 386        | C2-         | -5130.09             | -607.50  |

| 387        | C3+         | -5030.10             | -607.50  |

| 388        | C3+         | -4955.10             | -607.50  |

| 389        | C3+         | -4880.10             | -607.50  |

| 390        | <u>ය</u>    | -4780.11             | -607.50  |

| 391        | <u>ය</u>    | -4705.11             | -607.50  |

| 392        | <u>ය</u>    | -4630.11             | -607.50  |

| 393        | C4+         | -4530.12             | -607.50  |

| 394        | C4+         | -4455.12             | -607.50  |

| 395        | C4+         | -4380.12             | -607.50  |

| 396        | C4-         | -4280.13             | -607.50  |

| 397        | C4-         | -4205.13             | -607.50  |

| 398        | C4-         | -4130.13             | -607.50  |

| 399        | C5+         | -4030.14             | -607.50  |

| 400        | C5+         | -3955.14             | -607.50  |

| 401        | C5+         | -3880.14             | -607.50  |

| 402        | C5-         | -3780.15             | -607.50  |

| 403        | C5-         | -3705.15             | -607.50  |

| 404        | C5-         | -3630.15             | -607.50  |

| 405        | DOOLK       | -3530.16             | -607.50  |

| 406        | VDD2        | -3430.17             | -607.50  |

| 407        | VDD2        | -3355.17             | -607.50  |

| 408        | VSS1        | -3255.18             | -607.50  |

| 409        | VSS1        | -3180.18             | -607.50  |

| 410        | VSS2        | -3080.19             | -607.50  |

| 411        | VSS2        | -3005.19             | -607.50  |

| 412        | TEST_VOLAMP | -2905.20             | -607.50  |

| 413        | TEST_VOLAMP | -2830.20             | -607.50  |

| 414        | TEST_COM2   | -2730.21             | -607.50  |

| 415        | TEST_COM2   | -2655.21             | -607.50  |

| 416        | BGR_O       | -2555.22             | -607.50  |

| 417        | MVS         | -2455.23             | -607.50  |

| 418        | MVS         | -2380.23             | -607.50  |

| 419        | Dummy       | -2280.24             | -607.50  |

| 420        | Dummy       | -2180.25             | -607.50  |

|            | -aniny      | 2100.20              | wi.30    |

| No.        | PAD Name       | X[µm]                | Y[µm]              |

|------------|----------------|----------------------|--------------------|

| 421        | Dummy          | -2080.26             | -607.50            |

| 422        | Dummy          | -1980.27             | -607.50            |

| 423        | Dummy          | -1880.28             | -607.50            |

| 424        | Dummy          | -1780.29             | -607.50            |

| 425<br>426 | Dummy          | -1680.30             | -607.50            |

| _          | Dummy          | -1580.31<br>-1480.32 | -607.50            |

| 427<br>428 | VCC            |                      | -607.50            |

| 428        | VCC            | -1405.32<br>-1330.32 | -607.50<br>-607.50 |

| 430        | VCC            | -1255.32             | -607.50            |

| 431        | VSS            | -1155.33             | -607.50            |

| 432        | VSS            | -1080.33             | -607.50            |

| 433        | VSS            | -1005.33             | -607.50            |

| 434        | VSS            | -930.33              | -607.50            |

| 435        | VSS            | -855.33              | -607.50            |

| 436        | STHR           | -755.34              | -607.50            |

| 437        | GOE2 I         | -655.35              | -607.50            |

| 438        | GOE1 I         | -555.36              | -607.50            |

| 439        | GSTB I         | -455.37              | -607.50            |

| 440        | GCLK_I         | -355.38              | -607.50            |

| 441        | STB            | -255.39              | -607.50            |

| 442        | AP             | -155.40              | -607.50            |

| 443        | POL            | -55.41               | -607.50            |

| 444        | TCON           | 44.58                | -607.50            |

| 445        | PVCC           | 144.57               | -607.50            |

| 446        | OSEL           | 244.56               | -607.50            |

| 447        | VCSEL          | 344.55               | -607.50            |

| 448        | GAM            | 444.54               | -607.50            |

| 449        | MAS/SLV        | 544.53               | -607.50            |

| 450        | SCLEG1         | 644.52               | -607.50            |

| 451        | SCLEG0         | 744.51               | -607.50            |

| 452        | CKS            | 844.50               | -607.50            |

| 453        | HSEG           | 944.49               | -607.50            |

| 454        | VSEG           | 1044.48              | -607.50            |

| 455        | PVSS           | 1144.47              | -607.50            |

| 456        | EXT3_I         | 1244.46              | -607.50            |

| 457        | EXT2_I         | 1344.45              | -607.50            |

| 458        | EXT1_I         | 1444.44              | -607.50            |

| 459        | BSW_I          | 1544.43              | -607.50            |

| 460        | GSW_I          | 1644.42              | -607.50            |

| 461<br>462 | RSW_I          | 1744.41<br>1844.40   | -607.50            |

| 463        | Dummy          | 1944.39              | -607.50<br>-607.50 |

| 464        | Dummy<br>Dummy | 2044.38              | -607.50            |

| 465        | Dummy          | 2144.37              | -607.50            |

| 466        | Durmy          | 2244.36              | -607.50            |

| 467        | /RESET         | 2344.35              | -607.50            |

| 468        | A0             | 2444.34              | -607.50            |

| 469        | CS2            | 2544.33              | -607.50            |

| 470        | CS1            | 2644.32              | -607.50            |

| 471        | SCLK_SUB       | 2744.31              | -607.50            |

| 472        | SOSUB          | 2844.30              | -607.50            |

| 473        | LCDCS          | 2944.29              | -607.50            |

| 474        | LCDCS          | 3019.29              | -607.50            |

| 475        | SCLK           | 3119.28              | -607.50            |

| 476        | SCLK           | 3194.28              | -607.50            |

| 477        | SI             | 3294.27              | -607.50            |

| 478        | SI             | 3369.27              | -607.50            |

| 479        | SO             | 3469.26              | -607.50            |

| 480        | <del>\$0</del> | 3544.26              | -607.50            |

| 481        | VSYNC          | 3644.25              | -607.50            |

| 482        | HSYNC          | 3744.24              | -607.50            |

| 483        | HSYNC          | 3819.24              | -607.50            |

| 484        | DOK            | 3919.23              | -607.50            |

| 485        | DOK            | 3994.23              | -607.50            |

| 486        | Dummy          | 4094.22              | -607.50            |

| 487        | Dummy          | 4194.21              | -607.50            |

| 488        | Dummy          | 4294.20              | -607.50            |

|            | Dummy          | 4394.19              | -607.50            |

| 489<br>490 |                |                      | -607.50            |

| No.        | PAD Name           | X[µm]              | Y[µm]              |

|------------|--------------------|--------------------|--------------------|

| 491        | D25                | 4594.17            | -607.50            |

| 492        | D23                | 4694.16            | -607.50            |

| 493        | D23                | 4794.15            | -607.50            |

| 494        | D22                | 4894.14            | -607.50            |

| 495        | D21                | 4994.13            | -607.50            |

| 496        | D20                | 5094.12            | -607.50            |

| 497        | D15                | 5194.11            | -607.50            |

| 498        | D14                | 5294.10            | -607.50            |

| 499        | D13                | 5394.09            | -607.50            |

| 500        | D12                | 5494.08            | -607.50            |

| 501        | D11                | 5594.07            | -607.50            |

| 502        | D10                | 5694.06            | -607.50            |

| 503        | D05                | 5794.05            | -607.50            |

| 504        | D04                | 5894.04            | -607.50            |

| 505        | D03                | 5994.03            | -607.50            |

| 506        | D02                | 6094.02            | -607.50            |

| 507        | D01                | 6194.01            | -607.50            |

| 508        | D00                | 6294.00            | -607.50            |

| 509        | STHL               | 6393.99            | -607.50            |

| 510        | STHL               | 6468.99            | -607.50            |

| 511        | TESTOUT            | 6568.98            | -607.50            |

| 512        | TESTINA<br>TESTINA | 6668.97<br>6768.96 | -607.50<br>-607.50 |

| 513<br>514 |                    | 6868.95            | -607.50            |

| 515        | TESTIN2<br>TESTINI | 6968.94            | -607.50            |

| 516        | V4                 | 7068.93            | -607.50            |

| 517        | V4<br>V4           | 7143.93            | -607.50            |

| 518        | V3                 | 7243.92            | -607.50            |

| 519        | V3                 | 7318.92            | -607.50            |

| 520        | V2                 | 7418.91            | -607.50            |

| 521        | V2                 | 7493.91            | -607.50            |

| 522        | V1                 | 7593.90            | -607.50            |

| 523        | V1                 | 7668.90            | -607.50            |

| 524        | V0                 | 7768.89            | -607.50            |

| 525        | V0                 | 7843.89            | -607.50            |

| 526        | Dummy              | 7943.88            | -607.50            |

| 527        | Dummy              | 8043.87            | -607.50            |

| 528        | Dummy              | 8143.86            | -607.50            |

| 529        | Dummy              | 8243.85            | -607.50            |

| 530        | Dummy              | 8343.84            | -607.50            |

| 531        | Dummy              | 8443.83            | -607.50            |

| 532        | Dummy<br>COMDCSL   | 8543.82            | -607.50            |

| 533        |                    | 8643.81            | -607.50            |

| 534<br>535 | COMPON             | 8743.80<br>8818.80 | -607.50<br>-607.50 |

| 536        | VCOMH              | 8918.79            | -607.50            |

| 537        | VCOMH              | 8993.79            | -607.50            |

| 538        | VCOMH              | 9068.79            | -607.50            |

| 539        | VCOMH              | 9143.79            | -607.50            |

| 540        | COMDC              | 9243.78            | -607.50            |

| 541        | COMDC              | 9318.78            | -607.50            |

| 542        | COMC               | 9418.77            | -607.50            |

| 543        | COMC               | 9493.77            | -607.50            |

| 544        | COMC               | 9568.77            | -607.50            |

| 545        | COMC               | 9643.77            | -607.50            |

| 546        | COMC               | 9718.77            | -607.50            |

| 547        | Dummy              | 9818.76            | -607.50            |

| 548        | Dummy              | 10588.02           | -607.50            |

| 549        | Dummy              | 10688.01           | -607.50            |

| 550        | Dummy              | 10788.00           | -607.50            |

# 3. PIN FUNCTIONS

# 3.1 Source Driver Control Pins

(1/2)

| Pin Symbol                         | Pin Name                           | Pin Number | I/O    | Description                                                                                                     |

|------------------------------------|------------------------------------|------------|--------|-----------------------------------------------------------------------------------------------------------------|

| S <sub>1</sub> to S <sub>244</sub> | Driver output                      | 248 to 5   | Output | The D/A converted 64-gray-scale analog voltage is output.                                                       |

|                                    |                                    |            |        | OSEL = L: S1 to S244                                                                                            |

|                                    |                                    |            |        | OSEL = H: S <sub>3</sub> to S <sub>242</sub>                                                                    |

| OSEL                               | Driver output count                | 446        | Input  | The output count can be selected. When OSEL = H, the unused                                                     |

|                                    | switching                          |            |        | pins S <sub>1</sub> , S <sub>2</sub> , S <sub>243</sub> , S <sub>244</sub> always become Hi-Z (high impedance). |

|                                    |                                    |            |        | OSEL = L: 244 outputs                                                                                           |

|                                    |                                    |            |        | OSEL = H: 240 outputs                                                                                           |

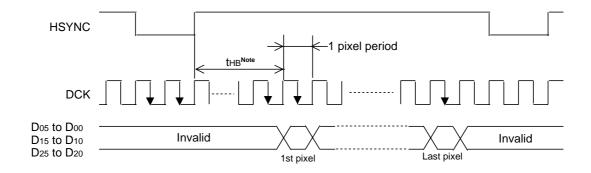

| DCK                                | Dot clock                          | 484, 485   | Input  | Dot clock signal                                                                                                |

| CKS                                | Dot clock inversion                | 452        | Input  | Inverts the active level of the dot clock.                                                                      |

|                                    |                                    |            |        | CKS = L: Low active                                                                                             |

|                                    |                                    |            |        | CKS = H: High active                                                                                            |

| HSYNC                              | Horizontal sync signal             | 482, 483   | Input  | Horizontal sync signal input pin.                                                                               |

|                                    |                                    |            |        | Do not input a width wider than the horizontal period as the width of                                           |

|                                    |                                    |            |        | the HSYNC active level.                                                                                         |

| VSYNC                              | Vertical sync signal               | 481        | Input  | Vertical sync signal input pin.                                                                                 |

| HSEG                               | HSYNC polarity selection           | 453        | Input  | Selects the active level of the HSYNC signal.                                                                   |

|                                    |                                    |            |        | HSEG = L: Low active                                                                                            |

|                                    |                                    |            |        | HSEG = H: High active                                                                                           |

| VSEG                               | VSYNC polarity selection           | 454        | Input  | Selects the active level of the VSYNC signal.                                                                   |

|                                    |                                    |            |        | VSEG = L: Low active                                                                                            |

|                                    |                                    |            |        | VSEG = H: High active                                                                                           |

| D <sub>00</sub> to D <sub>05</sub> | Display data input                 | 508 to 503 | Input  | The display data is input with a width of 18 bits, the gray scale data                                          |

| D <sub>10</sub> to D <sub>15</sub> |                                    | 502 to 497 |        | (6 bits) by 3 dots (1 pixels).                                                                                  |

| D <sub>20</sub> to D <sub>25</sub> |                                    | 496 to 491 |        | Dxo: LSB, Dxs: MSB                                                                                              |

| SCLK                               | Serial clock input                 | 475, 476   | Input  | Clock pin of serial interface.                                                                                  |

| SO                                 | Serial data output                 | 479, 480   | Output | Data output pin of serial interface.                                                                            |

| SI                                 | Serial data input                  | 477, 478   | Input  | Data input pin of serial interface.                                                                             |

| LCDCS                              | Serial interface chip select       | 473, 474   | Input  | Chip select pin of serial interface.                                                                            |

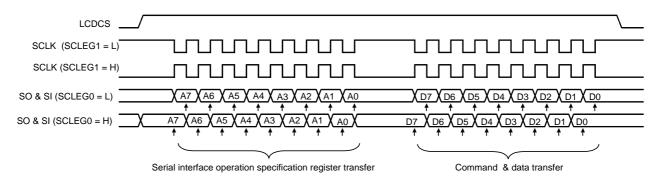

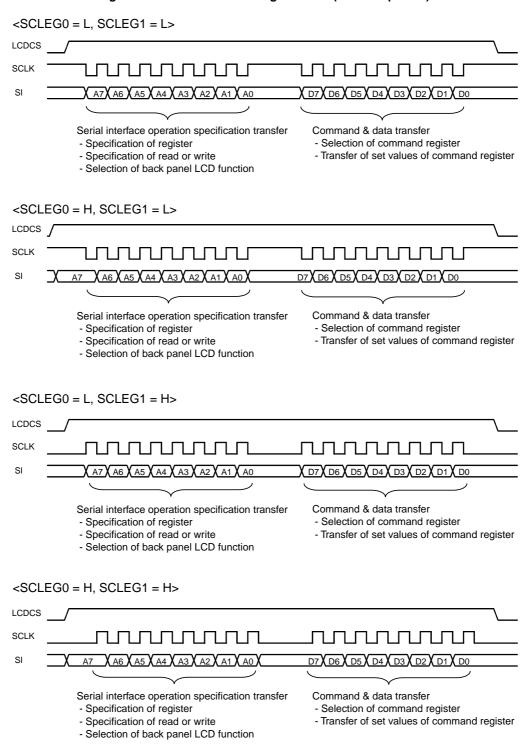

| SCLEG0,                            | Serial clock mode                  | 451,       | Input  | Mode select pin of serial clock. For details, refer to 4. REGISTERS                                             |

| SCLEG1                             | selection                          | 450        |        | for explanation in serial interface .                                                                           |

| VCSEL                              | COM amplitude output               | 447        | Input  | Fixes the VCOM output to L. When not using the VCOM output,                                                     |

|                                    | fixing signal                      |            |        | set VCSEL to L.                                                                                                 |

|                                    |                                    |            |        | VCSEL = L: VCOM output fixed to L                                                                               |

|                                    |                                    |            |        | VCSEL = H: VCOM signal output in accordance with POL signal                                                     |

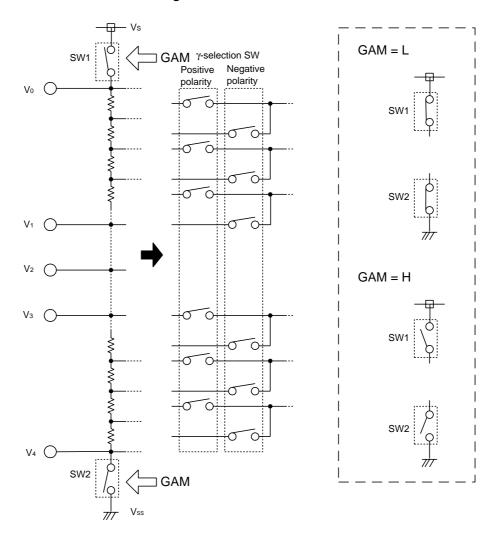

| GAM                                | External $\gamma$ -usage selection | 448        | Input  | When the $\gamma$ -correction power supply is input externally, switch                                          |

|                                    |                                    |            |        | GAM to H. If two or more chips are used, be sure to input the $\gamma$ -                                        |

|                                    |                                    |            |        | correction power supply externally.                                                                             |

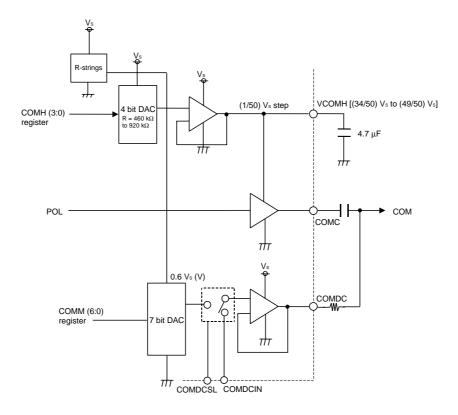

|                                    |                                    |            |        | Figure 3–1 shows VCOM application example.                                                                      |

|                                    |                                    |            |        | GAM = L: External $\gamma$ -correction power supply not input                                                   |

|                                    |                                    |            |        | GAM = H: External $\gamma$ -correction power supply input                                                       |

(2/2)

| Pin Symbol                     | Pin Name                                    | Pin Name   | I/O    | Description                                                                                                                                                                                                                                                                  |

|--------------------------------|---------------------------------------------|------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAS, /SLV                      | Master slave control                        | 449        | Input  | When the timing generator is used and 2 chips are connected in cascade, selects use either as master IC or slave IC.  When the timing generator is not used, either leave this pin or input a high level.  MAS, /SLV = L: Use as slave  MAS, /SLV = H: Use as master         |

| V <sub>0</sub> -V <sub>4</sub> | $\gamma$ -corrected power supplies          | 525 to 516 | Input  | These pins input the $\gamma$ -corrected power supplies from outside, the relationship below must be observed. Also, be sure to stabilize the gray-scale-level power supply during gray-scale voltage output. $V_{SS} \leq V_4 \leq V_3 \leq V_2 \leq V_1 \leq V_0 \leq V_S$ |

| VCOMH                          | Amplitude voltage                           | 536 to 539 | Output | Outputs the voltage set with the amplitude voltage adjustment D/A converter.                                                                                                                                                                                                 |

| COMC                           | Square wave signal output                   | 542 to 546 | Output | Outputs the square wave signal obtained through common modulation of V <sub>P-P</sub> voltage 0 V-VCOMH.                                                                                                                                                                     |

| COMDC                          | Common center voltage output                | 540, 541   | Output | Outputs the common center voltage.                                                                                                                                                                                                                                           |

| COMDCIN                        | Common center voltage external input        | 534, 535   | Input  | Input pin used to input the common center voltage from external.  Valid when COMDCSL = H.                                                                                                                                                                                    |

| COMDCSL                        | Common center voltage external input switch | 533        | Input  | Inputs a H level as the common voltage when the voltage input from the COMDCIN pin is used.                                                                                                                                                                                  |

| TCON                           | Timing generator use/non-use selection      | 444        | Input  | This pin is used to select whether or not to use the timing generator.  TCON = L: Timing generator used  TCON = H: Timing generator not used                                                                                                                                 |

| /RESET                         | Reset                                       | 467        | Input  | Reset pin. This is the active low signal.                                                                                                                                                                                                                                    |

Figure 3–1. VCOM Application Example

# 3.2 Gate Scan Control Pins

| Pin Symbol | Pin Name         | Pin Name   | I/O    | Description                                                                                                                                                                   |

|------------|------------------|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GCLK_O     | Gate CLK output  | 315, 316   | Output | Pin for CLK output to the gate control circuit.                                                                                                                               |

| GSTB_O     | Gate STB output  | 317, 318   | Output | Pin for strobe signal fed to gate control circuit                                                                                                                             |

| GOE1_O     | Gate OE1 output  | 311, 312   | Output | Pin for OE1 output to gate control circuit                                                                                                                                    |

| GOE2_O     | Gate OE2 output  | 307 to 310 | Output | Pin for OE2 output to gate control circuit                                                                                                                                    |

| GCLK_I     | Gate CLK input   | 440        | Input  | Input the CLK signal to the gate control circuit, when the timing generator function is not used. The signal input to this pin is output from the GCLK_O via a level shifter. |

| GSTB_I     | Gate STB input   | 439        | Input  | Input the STB signal to the gate control circuit, when the timing generator function is not used. The signal input to this pin is output from the GSTB_O via a level shifter. |

| GOE1_I     | Gate OE1 input   | 438        | Input  | Input the OE1 signal to the gate control circuit, when the timing generator function is not used. The signal input to this pin is output from the GOE1_O via a level shifter. |

| GOE2_I     | Gate OE2 input   | 437        | Input  | Input the OE2 signal to the gate control circuit, when the timing generator function is not used. The signal input to this pin is output from the GOE2_O via a level shifter. |

| GR,/L_O    | Gate R,/L output | 313, 314   | Output | Pin that outputs R,/L to the gate control circuit.                                                                                                                            |

# 3.3 Control Pin for Multiplex Switch, etc.

| Pin Symbol | Pin Name          | Pin Name | I/O    | Description                                                                    |

|------------|-------------------|----------|--------|--------------------------------------------------------------------------------|

| RSW_O      | Multiplex control | 287, 288 | Output | Output pin that controls the multiplex switch on the panel.                    |

| GSW_O      | signal output     | 285, 286 | Output |                                                                                |

| BSW_O      |                   | 283, 284 | Output |                                                                                |

| EXT1_O     | Extension control | 293, 294 | Output | Extension output pin that controls the circuit on the panel.                   |

| EXT2_O     | signal output     | 291, 292 | Output |                                                                                |

| EXT3_O     |                   | 289, 290 | Output |                                                                                |

| RSW_I      | Multiplex control | 461      | Input  | Pin for inputting the signal that controls the multiplex switch on the panel,  |

|            | signal input      |          |        | when the timing generator function is not used. The signal input to this pin   |

|            |                   |          |        | is output from the RSW_O pin via a level shifter.                              |

| GSW_I      |                   | 460      | Input  | Pin for inputting the signal that controls the multiplex switch on the panel,  |

|            |                   |          |        | when the timing generator function is not used. The signal input to this pin   |

|            |                   |          |        | is output from the GSW_O pin via a level shifter.                              |

| BSW_I      |                   | 459      | Input  | Pin for inputting the signal that controls the multiplex switch on the panel,  |

|            |                   |          |        | when the timing generator function is not used. The signal input to this pin   |

|            |                   |          |        | is output from the BSW_O pin via a level shifter.                              |

| EXT1_I     | Extension control | 458      | Input  | Pin for inputting the extension signal that controls the circuit on the panel, |

|            | signal input      |          |        | when the timing generator function is not used. The signal input to this pin   |

|            |                   |          |        | is output from the EXT1_O pin via the level shifter.                           |

| EXT2_I     |                   | 457      | Input  | Pin for inputting the extension signal that controls the circuit on the panel, |

|            |                   |          |        | when the timing generator function is not used. The signal input to this pin   |

|            |                   |          |        | is output from the EXT2_O pin via the level shifter.                           |

| EXT3_I     |                   | 456      | Input  | Pin for inputting the extension signal that controls the circuit on the panel, |

|            |                   |          |        | when the timing generator function is not used. The signal input to this pin   |

|            |                   |          |        | is output from the EXT3_O pin via the level shifter.                           |

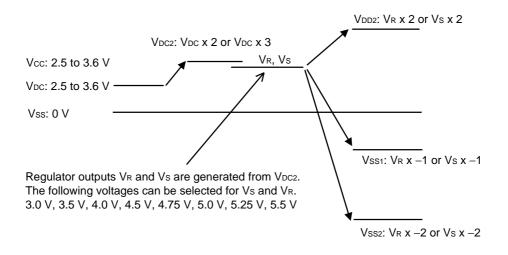

3.4 Power Supply Function Control Pin

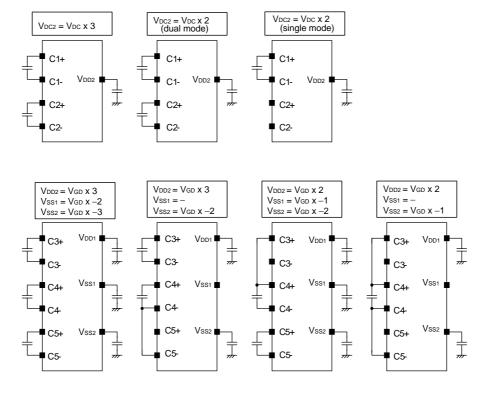

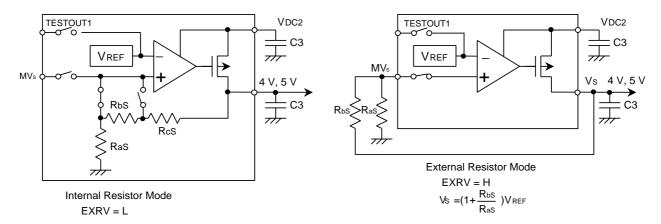

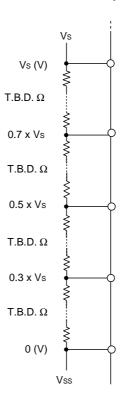

Pin Symbol Pin Name Pin Name I/O Description C1+/-.C2+/-. Booster capacitor 359 to 404 Connect the boost capacitor of the DC/DC converter to this pin. C3+/-,C4+/-, connection Booster ratio is difference on the way of using condenser connection. C5+/-For details, refer to figure 3-3. V<sub>DC2</sub> DC/DC converter 352 to 358 DC/DC converter boost output (VDC x 2 or VDC x 3). This output is the Vs and output VR amplifier power supply. The VDC2 boot step is selected with the VCD2 bit.  $V_{CD2}$  bit = 0:  $V_{DC}$  x 2  $V_{CD2}$  bit = 1:  $V_{DC}$  x 3 ۷s Source power 336 to 332 Source voltage output pin. supply output The Vs output voltage can be changed through the VSEL0 to VSEL2. MVs 417, 418 External Input An external resistance can be input to set any output voltage. EXRV bit = 0: Leave open (Internal resistor selection) resistance input EXRV bit = 1: Connect external resistor. VR 341 to 344 Reference power Gate reference power supply output pin. supply output The VR output voltage can be changed through the VRSEL to VRSEL2 setting.  $V_{DD2}$ DC/DC converter 303 to 306, DC/DC converter boost output (VgD x 2) 406, 407 output Vss1 DC/DC converter 299 to 302. DC/DC converter boost output (VgD x -1) output 408 to 411 Vss2 DC/DC converter 295 to 298 DC/DC converter boost output (VgD x -2) output VDC Reference power 345 to 351 Extension pin used to control circuit on panel. supply input for source power supply voltage  $V_{\text{GD}}$ Reference power 337 to 340 Extension pin used to control circuit on panel. supply input for gate power supply voltage **DCCLK** 405 Boost clock Input Pin used to input boost clock of DC/DC converter. input

Figure 3-2. DC/DC Converter Boost Configuration

9

# Figure 3-3. Relationship between Condenser Connection for Booster and Booster Ratio

Figure 3-4. Vs, Amp. Circuit Configuration

3.5 Control Pins when Timing Generator Function Not Used, and Other Pins

| 010 001141011 | 1110 1111011 111111111 | ,        |       | 1101 000u, una outoi i mo                                                              |

|---------------|------------------------|----------|-------|----------------------------------------------------------------------------------------|

| Pin Symbol    | Pin Name               | Pin Name | I/O   | Description                                                                            |

| STHR          | Right shift start      | 436      | I/O   | Start pulse I/O pin during cascade connection. When an H level is read at              |

|               | pulse I/O              |          |       | the rising edge of CLK, fetching of display data starts.                               |

| STHL          | Left shift start       | 509, 510 | I/O   | In the case of right shift, STHR = input and STHL = output.                            |

|               | pulse I/O              |          |       | In the case of left shift, STHL = input and STHR = output.                             |

| STB           | Latch input            | 441      | Input | This is the timing signal at which the contents of the data register are               |

|               |                        |          |       | latched. When an H level is read at the rising edge of CLK, the contents of            |

|               |                        |          |       | the data register are latched and transferred to the D/A converter, and an             |

|               |                        |          |       | analog voltage is output according to the display data. Even after STB                 |

|               |                        |          |       | fetch, do not stop CLK because the internal operation is performed using               |

|               |                        |          |       | CLK. At the rising edge of STB, the content of the shift register are                  |

|               |                        |          |       | cleared. After one pulse is input at startup, the operation becomes normal.            |

|               |                        |          |       | At the rising edge of STB, the output switch is switched OFF. For the STB              |

|               |                        |          |       | input timing, refer to 5. TIMING GENERATOR NON-USE FUNCTION.                           |

| AP            | Output SW              | 442      | Input | Switches the BIAS circuit ON/OFF and the output switch and amplifier ON.               |

|               | ON/OFF                 |          |       | The period during which AP is H is the amplifier circuit setting period and            |

|               |                        |          |       | the liquid crystal drive period. At the falling edge of AP, the amplifier output       |

|               |                        |          |       | and output switch go ON and liquid crystal driving starts.                             |

|               |                        |          |       | At the rising edge of STB, the output switch is switched to OFF ad the                 |

|               |                        |          |       | output becomes Hi-Z.                                                                   |

| POL           | Polarity               | 443      | Input | Inverts the output polarity. At the siring edge of RSEL, the polarity inversion        |

|               | inversion signal       |          |       | signal data is fetched internally. The $\gamma$ -resistor is switched according to the |

|               |                        |          |       | positive and negative polarity.                                                        |

|               |                        |          |       | POL = L: Negative polarity (common high output)                                        |

|               |                        |          |       | POL = H: Positive polarity (common low output)                                         |

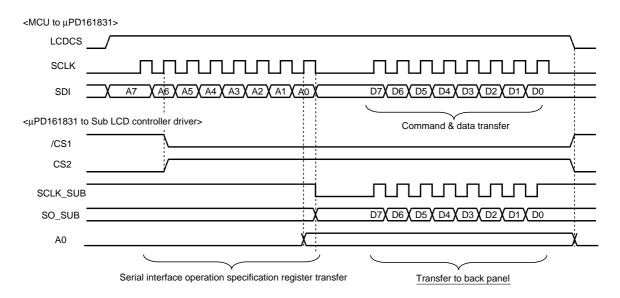

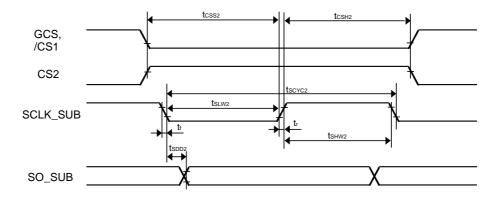

# 3.6 Back Panel I CD Controller Driver Control Pins

| Pin Symbol | Pin Name                                  | Pin Name | I/O    | Description                                                             |

|------------|-------------------------------------------|----------|--------|-------------------------------------------------------------------------|

| /CS1       | Back panel LCD chip select                | 470      | Output | Active-low chip select signal to the back panel LCD controller driver.  |

| CS2        | Back panel LCD chip select                | 469      | Output | Active-high chip select signal to the back panel LCD controller driver. |

| SCLK_SUB   | Serial clock to<br>the back panel<br>LCD  | 471      | Output | Back panel LCD serial data output.                                      |

| SO_SUB     | Outputs serial data to the back panel LCD | 472      | Output | Outputs serial data to the back panel LCD controller driver.            |

| A0         | Back panel LCD data/command control       | 468      | Output | Controls data/command to the back panel LCD controller driver.          |

# 3.7 Other Control Pins

| Pin Symbol         | Pin Name                   | Pin Name                                                                                         | I/O    | Description                                          |

|--------------------|----------------------------|--------------------------------------------------------------------------------------------------|--------|------------------------------------------------------|

| TESTIN1 to TESTIN4 | TEST input                 | 515 to 512                                                                                       | Input  | Keep this pin low-level or leave it open.            |

| TESTOUT            | TEST output                | 511                                                                                              | Output | Leave this pin open.                                 |

| TEST_COM2          | TEST output                | 414, 415                                                                                         | Output | Leave this pin open.                                 |

| TEST_VCLAMP        | TEST output                | 412, 413                                                                                         | Output | Leave this pin open.                                 |

| BGR_O              | Hand cap regulator output  | 416                                                                                              | Output | Leave this pin open.                                 |

| PVcc               | Power supply for pull-up   | 445                                                                                              | -      | This is pull-up power supply for mode setting pin.   |

| PVss               | Power supply for pull-down | 456                                                                                              | _      | This is pull-down power supply for mode setting pin. |

| Vcc                | Logic supply voltage       | 427 to 430                                                                                       | _      | 2.2 to 3.6 V                                         |

| Vss                | Driver ground              | 327 to 331.<br>431 to 435                                                                        | -      | Grounding                                            |

| Dummy              | Dummy                      | 1 to 4,<br>249 to 282,<br>319 to 326,<br>419 to 426,<br>462 to 466,<br>486 to 490,<br>526 to 532 | -      | Dummy pin                                            |

Caution To avoid latch-up failure, the sequence when turning on the power must be  $Vcc \rightarrow logic$  input  $\rightarrow$  booster voltage for rising  $\rightarrow$  gray-scale power supply ( $V_0$ - $V_4$ ), and the reverse sequence when turning off the power. Follow this sequence during shift periods as well.

#### 4. REGISTERS

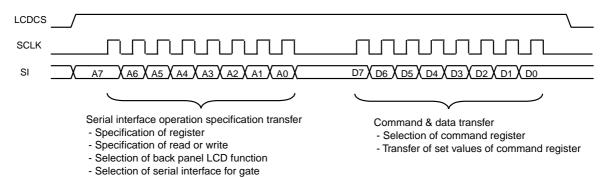

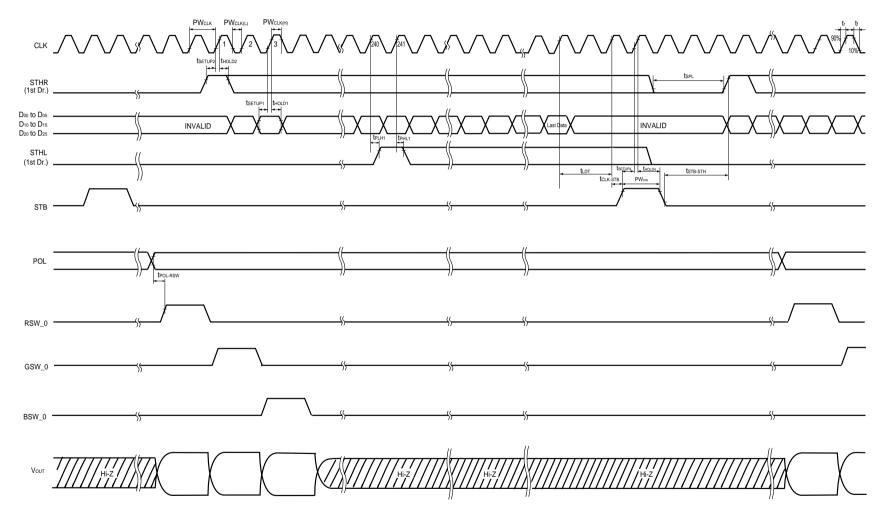

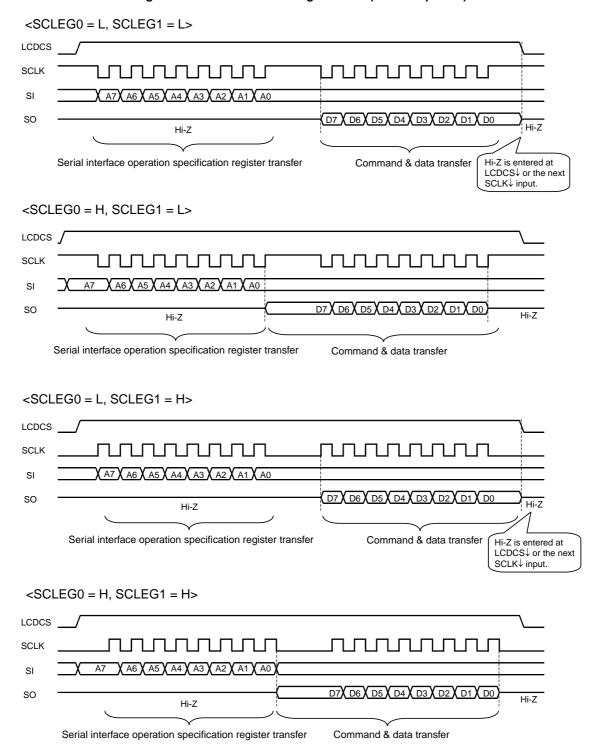

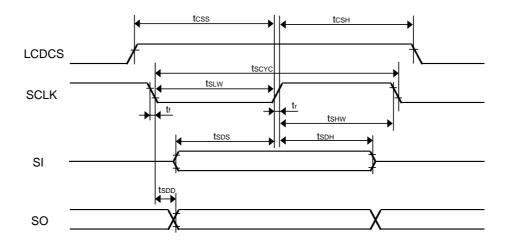

The  $\mu$ PD161831 can set a horizontal period and vertical period by using registers. The serial interface is used to specify a register and set values to it. Figure 4–1 shows a simplified timing chart of the serial interface.

Figure 4-1. Timing Chart of Serial Interface

This serial interface has an 8-bit configuration. Note that it is accessed twice in 8-bit units to set a register.

The first 8-bit data (A7 to A0 in figure 4–1) is transferred to the "serial interface operation specification register".

The serial interface operation specification register specifies the transfer operation of the next 8 bits (D7 to D0 in figure 4–1). The second 8-bit data selects a command register or transfers the set value of the command register.

In addition, while writing a setup in command register with the 8-bit transfer + 8-bit (A7 to A0 + D7 to D0) which selects command register or transferring of 8 bit + 8-bit transfer of readings (A7 to A0 + D7 to D0) (a total of 32 bits), continue making chip select (LCDCS) active.

Table 4–1 indicates the function of the serial interface operation specification register. Table 4–2 shows the register number and register name of each command register. Tables 4–3 and 4–5 to 4–24 describe the function of each command register.

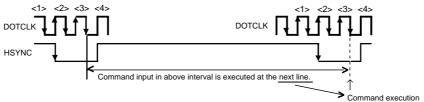

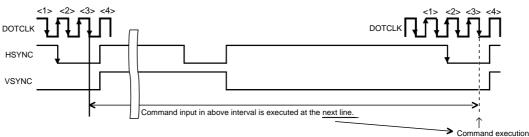

When the timing generator is used, there are three execution patterns for each command: Immediate execution following setting, execution at the line following that where command was set, and execution at the frame following that where command was set. In the case of execution at the next line and execution at the next frame, the concrete command execution timing is as follows.

However, when the timing generator is not used, commands are executed at the first falling edge of DCK following command transmission.

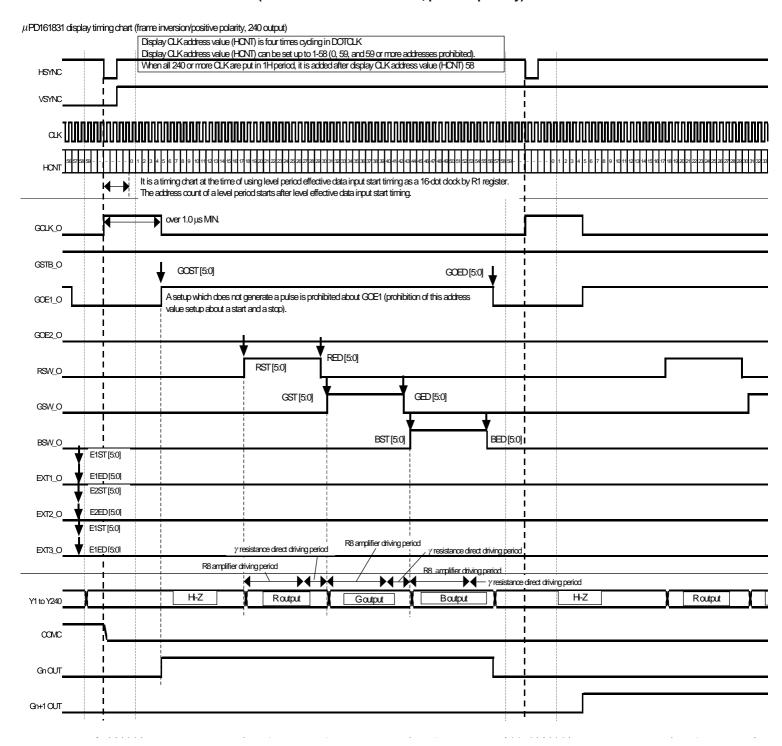

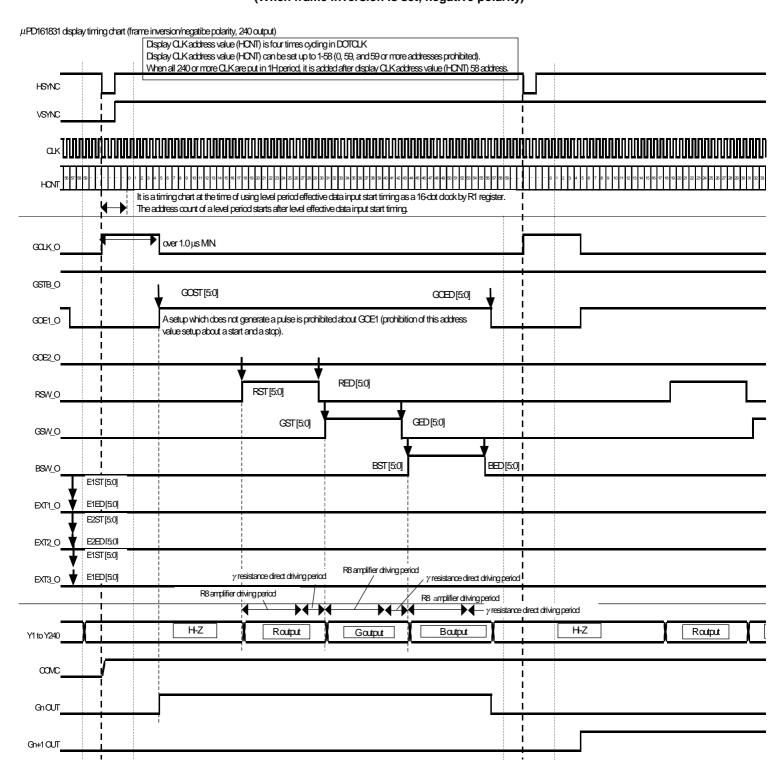

• Execution from next line following command input (HSYNC, DOTCLK = low active)

• Execution from next frame following command input (VSYNC, HSYNC, DOTCLK = low active)

# 4.1 Serial Interface Operation Specification Register

Table 4–1 shows the function of the serial interface operation specification register.

Table 4-1. Function of Serial Interface Operation Specification Register (A7 to A0)

| No. | Bit Name          | Function                                                                                               |

|-----|-------------------|--------------------------------------------------------------------------------------------------------|

| A7  | _                 | -                                                                                                      |

| A6  | μPD161831/back    | This bit specifies whether data D7 to D0 are data for a register of the $\mu$ PD161831 or data for the |

|     | panel LCD select  | back panel LCD. If D7 to D0 are data for the back panel LCD, the chip select pins for the back         |

|     |                   | panel LCD (/CS1 = L, CS2 = H) are asserted, and data D7 to D0 are output to SUB_SO along               |

|     |                   | with the clock output by SCLK_SUB.                                                                     |

|     |                   | 0: D7 to D0 are data for a $\mu$ PD161831 register.                                                    |

|     |                   | 1: D7 to D0 are data for the back panel LCD controller driver.                                         |

| A5  | Read/write select | This bit selects whether the transfer of data D7 to D0 is for a read operation or a write operation.   |

|     |                   | Note, however, that in a read operation, only the registers of the $\mu$ PD161831 can be read.         |

|     |                   | For the timing chart of the read operation, refer to 5. TIMING GENERATOR NON-USE                       |

|     |                   | FUNCTION.                                                                                              |

|     |                   | 0: D7 to D0 are for a write operation.                                                                 |

|     |                   | 1: D7 to D0 are for a read operation.                                                                  |

| A4  | _                 | -                                                                                                      |

| А3  | _                 | -                                                                                                      |

| A2  | _                 | _                                                                                                      |

| A1  | _                 | -                                                                                                      |