# ASSP **COMMUNICATION CONTROL SCSI-2 PROTOCOL CONTROLLER MB86603**

#### DESCRIPTION

The MB86603 is a SCSI-2 protocol controller (SPC) that facilitates interface control between the host computer (medium/small) and peripheral devices. The specifications conform to the SCSI-2 standard but have an improved baud rate and extended functions.

The MB86603 supports high-speed synchronous transfer, wide transfer (16 bits), the MPU/DMA stand-alone system bus, and programmable commands, to enable configuration of high-performance systems.

The MB86603 (SPC hereafter) is applicable to both single-end and differential transmissions and has a driver/receiver that can drive single-end heavy current (48 mA).

It can also have the phase-to-phase sequence control function to reduce the program overhead of the host MPU. For the abbreviations in this data sheet, see the next page.

#### **FEATURES**

#### **SCSI Bus Interface**

- · Operable as initiator and target

- Two types of data transfer

- Synchronous transfer: Max. 20 Mbytes/s, max. 32 offsets, 32-level baud rate

- Asynchronous transfer: Max. 10 Mbytes/s

- Transfer parameters (transfer mode, baud rate, transfer offset for 15 connected devices)

- Single-end and differential transmissions Driver/receiver capable of driving 48-mA single-end heavy current

- Tristate bidirectional buffers for transfer control signals (REQ, ACK)

#### **Transfer Operation**

#### Automatic response to selection/reselection

Prespecified receiving performed automatically at selection or reselection Initiator: Automatically responds to reselection from target and operable until message received Target: Automatically responds to selection from initiator and can operate until command received

#### • Automatic receiving

Initiator: Can automatically receive information for new phase to which target shifted Target: Can perform automatic receiving in response to attention condition generated by initiator

- 64-byte data register (FIFO) for data phase

- Two (send-only and receive-only) 32-byte memory data buffers for message, command, and status phases

- 16-bit transfer block and 24-bit transfer byte registers enabling 1Tbyte transfer (1Tbyte: 16 Mbytes x 64 Kblocks)

- Independent data transfer bus enabling microprocessor to operate during data transfer

- Selection between parity through and generate

#### System Bus Interface

- 16-bit MPU/DMA stand-alone system bus

- Direct connection with 68 series/80 series 16-bit MPUs

- Two types of transfer Program transfer DMA transfer (burst mode)

#### Commands

- Sequential command for sequential operation and programmable command for programming, including ordinary commands

- Command queuing

Commands can be tagged in the command phase for continuous issuing.

• 512-byte memory as command program memory and command queue buffer

#### Others

- CMOS

- System clock frequency: 12 MHz to 32 MHz

- +5 V single power supply

SCSI-2: Enhanced Small Computer System Interface ANSI: American National Standard Institute SPC: SCSI-2 Protocol Controller MPU: Micro-Processing Unit DMA: Direct Memory Access FIFO: First-In First-Out ID: Identifier (identification number assigned to each device connected to SCSI bus) 80 series: General term for MPU based on command system of 8080A developed by Intel

68 series: General term for MPU developed by Motorola

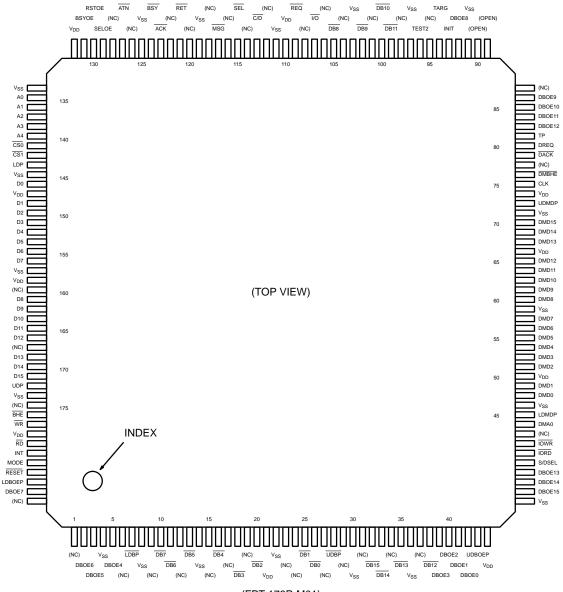

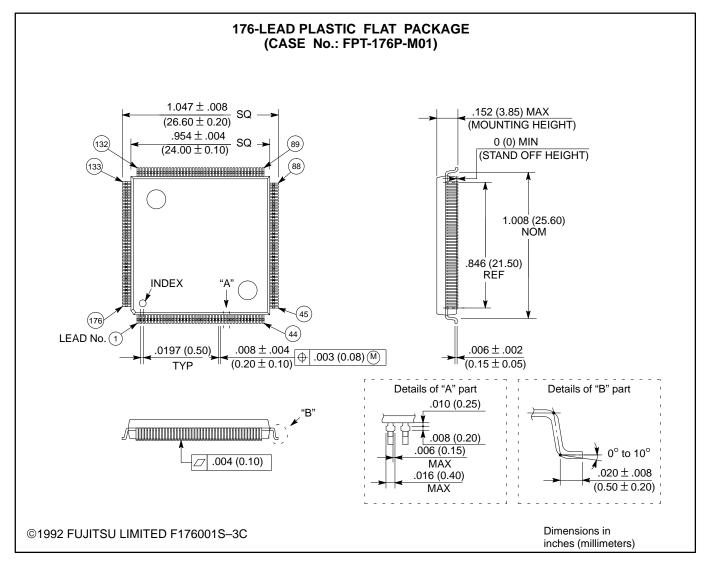

# **PIN ASSIGNMENT**

(FPT-176P-M01)

3

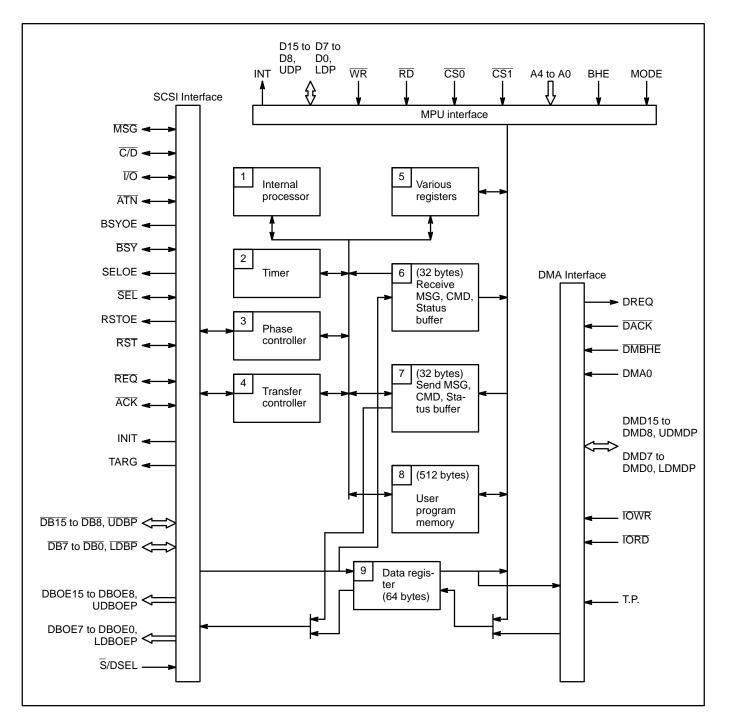

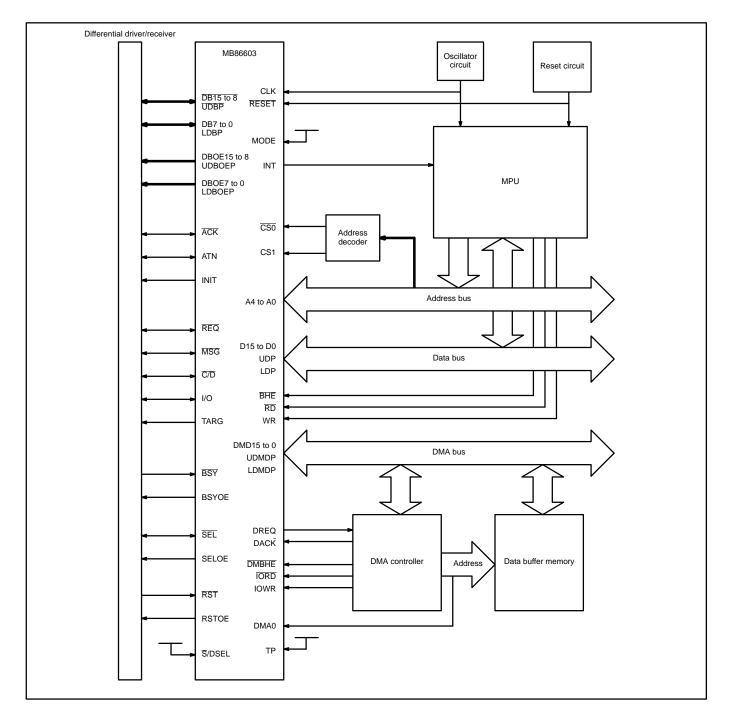

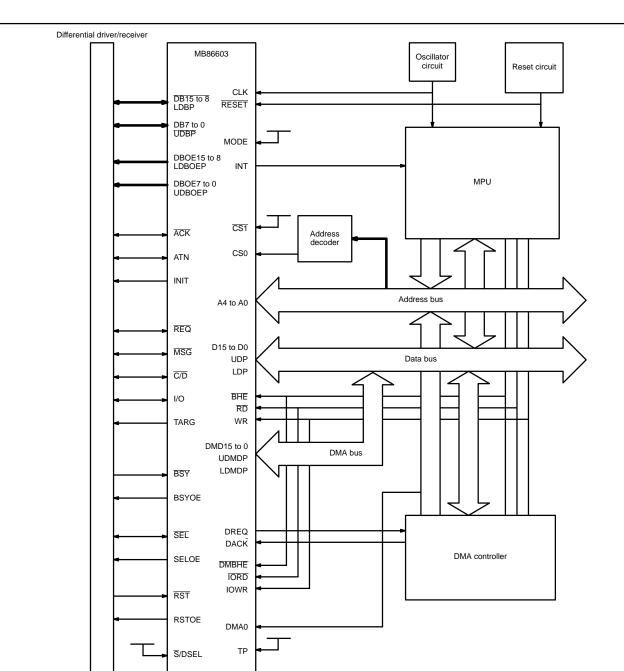

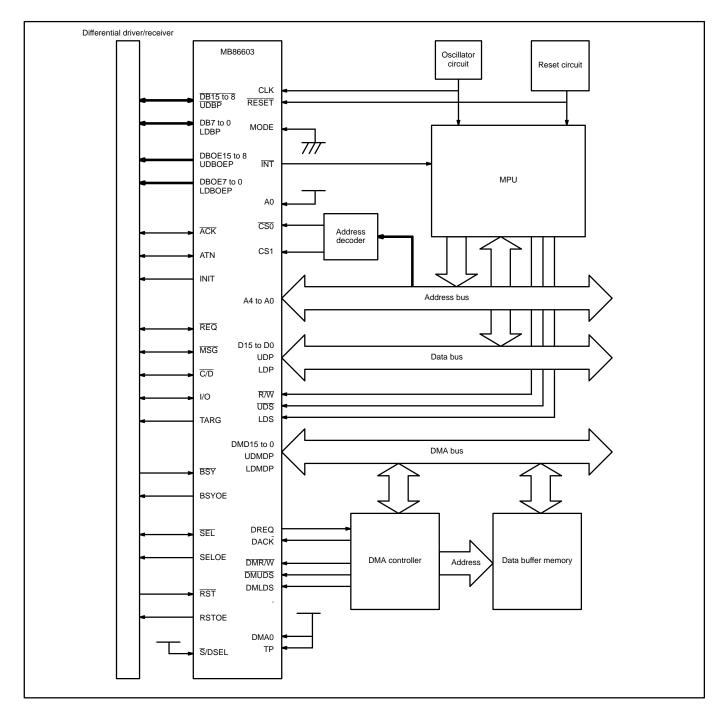

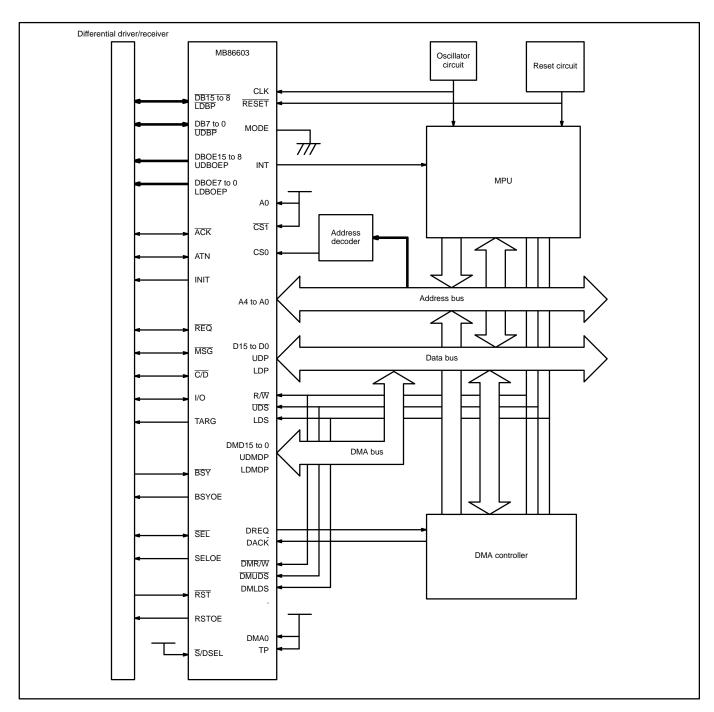

# **BLOCK DIAGRAM**

# **BLOCK DESCRIPTION**

#### 1. Internal processor (sequensor)

This processor provides sequence control between each phase.

#### 2. Timer

This timer manages timing specified by the SCSI and the following timing.

- REQ/ACK assertion time for data at asynchronous transfer

- Selection/reselection retry time

- Selection/reselection timeout time

- REQ/ACK timeout time during transfer

Asynchronous transfer (target): Time required for initiator to assert ACK signal after asserting REQ signal Asynchronous transfer (initiator): Time required for target to negate REQ signal after asserting ACK signal Synchronous transfer (target only): Time required for target to send REQ signal and then receive ACK signal for setting offset to 0 from initiator

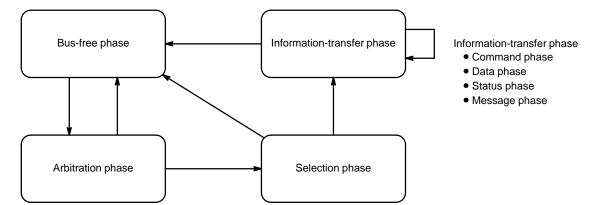

### 3. Phase Controller

This controller controls the arbitration, selection/reselection, data in/out, command, status, and message in/out phases executed on the SCSI bus.

# 4. Transfer Controller

This controller controls the information (data, command, status, message) transfer phase executed on the SCSI bus.

There are two transfer types for executing the information transfer phase.

- Asynchronous transfer: Control by interlocking REQ and ACK signals

- Synchronous transfer: Control with maximum of 32-byte offset value in data in/out phase

There are two types of modes depending on the data movement as follows:

- Program transfer: Performed via MPU interface using data registers

- DMA transfer: Performed via DMA interface using DREQ and DACK pins

At synchronous transfer, the transfer parameters (transfer mode, minimum cycle period of REQ or ACK signal sent from SPC in synchronous transfer, and maximum REQ/ACK offset value in synchronous transfer) can be saved for each ID and automatically set when the data phase is started. The transfer byte count is determined by block length x number of blocks.

#### 5. Various Registers

The main registers are as follows:

- Command register

This register specifies each command with an 8-bit code.

If the user program is used, the starting address of the program assigned to the user program memory is specified.

- Nexus status register

This register indicates the chip's operating condition, linked partner's ID, and data register status.

- SCSI control signal status register This register indicates the status of the SCSI control signals.

- Interrupt status register This register indicates the interrupt status with an 8-bit code.

- Command step register

This register indicates the execution status of each command with an 8-bit step code.

Referencing the interrupt status register and this register permits analysis of error causes.

- Group 6/7 command-length setting register This register sets the group 6/7 command length not defined in the SCSI standard. Setting this register permits group 6/7-command length decisions.

# 6. Receive MSG, CMD, Status Buffer (RECEIVE MCS Buffer)

This is a 32-byte receive-only information buffer that holds the message, command, and status information received from the SCSI bus.

# 7. Send MSG, CMD, Status Buffer (SEND MCS Buffer)

This is a 32-byte send-only information buffer that holds the message, command, and status information sent on the SCSI bus.

# 8. User Program Memory

This is a 512-byte program memory that stores programmable commands. It consists of two 256-byte banks.

# 9. Data Register

This is a 64-byte FIFO-type data register that holds data when the data phase is executed on the SCSI bus.

# **PIN DESCRIPTION**

### 1. SCSI Interface

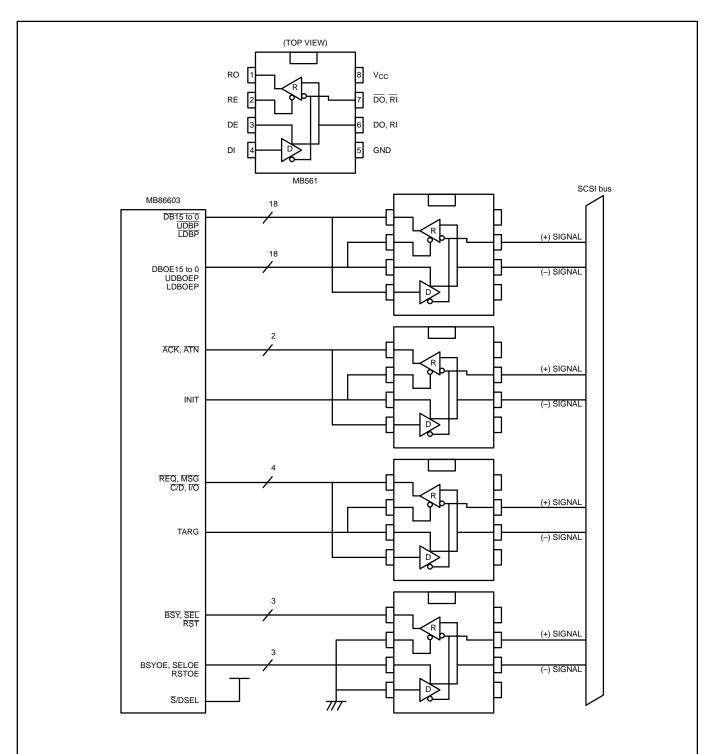

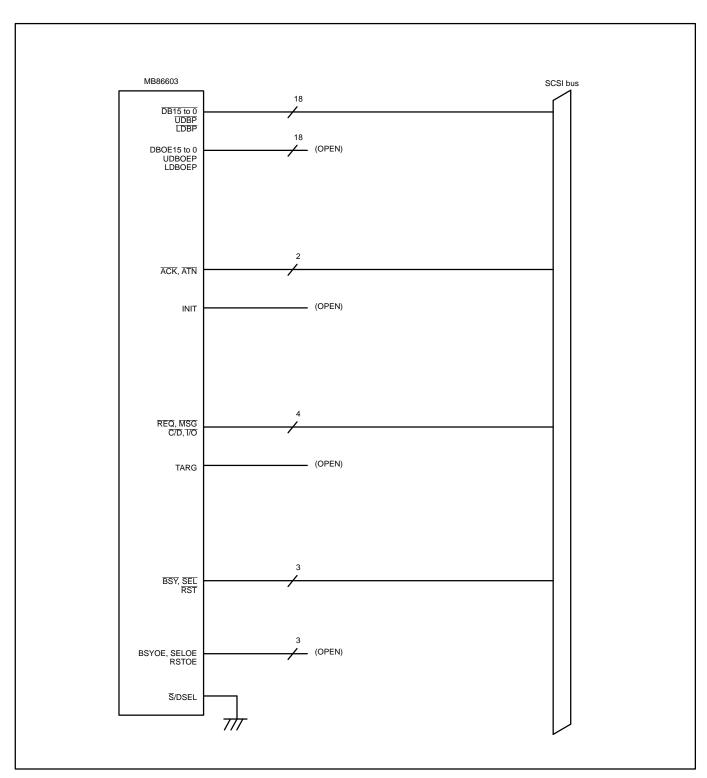

There are two types of SCSI interface corresponding to two types of transmission systems; each type operates differently.

| Pin No. | Pin Symbol | Pin Name           | I/O | Function                                                                                                                                                                                                                                                                           |

|---------|------------|--------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 109     | REQ        | Request            | I/O | This is used for transfer request signals from the target to the initiator in the information-transfer phase.<br>The input signal is used as a data transfer sequence timing control signal.<br>The signal is Active Low.                                                          |

| 123     | ACK        | Acknowledge        | I/O | This is used for response signals from the initiator to the target in response to the REQ signal in the information-transfer phase.<br>The input signal is used as a data transfer sequence timing control signal.<br>The signal is Active Low.                                    |

| 127     | ATN        | Attention          | I/O | This is used for request signals for the message-transfer phase from the ini-<br>tiator to the target.<br>The signal is Active Low.                                                                                                                                                |

| 117     | MSG*       | Message            | I/O | This is used for signals specifying the type of information transmitted on the data bus.<br>The signal is Active Low and goes Low when specifying the message phase.                                                                                                               |

| 113     | C/D*       | Controll/Date      | I/O | This is used for signals for specifying the type of information transmitted on the data bus.<br>The signal is Active Low and goes Low when specifying the command, status, and message phases.                                                                                     |

| 107     | 1/0*       | Input/Output       | I/O | This is used for signals for specifying the transfer direction of information transferred on the data bus.<br>The signal is Active Low. At Low, information is transferred from the target to the initiator. At High, information is transferred from the initiator to the target. |

| 124     | BSY        | Busy               | I/O | This indicates that the SCSI bus is busy.<br>In the arbitration phase, this pin is used for signals requesting bus acquisition.<br>The signal is Active Low.                                                                                                                       |

| 115     | SEL        | Select             | I/O | This is used for input of signals that are output and detected by the initiator<br>and target in the selection phase (the initiator selects the target) and reselec-<br>tion phase (the target reselects the initiator).<br>The signal is Active Low.                              |

| 121     | RST        | Reset              | I/O | This is used for output of reset signals to other SCSI devices and for input of reset signals from other SCSI devices.<br>The signal is Active Low.                                                                                                                                |

| 131     | BSYOE**    | Busy Output Enable | 0   | This is used for output control of BSY signals.<br>In the differential mode, this pin should be used for control signals for the exter-<br>nal differential driver/receiver.<br>The signal is Active High.                                                                         |

(Continued)

#### MB86603

| Pin No.                                                                                 | Pin Symbol                                                       | Pin Name                                                                                                                                                       | I/O | Function                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 129                                                                                     | SELOE**                                                          | Select<br>Output Enable                                                                                                                                        | 0   | This is used for output control of SEL signals.<br>In the differential mode, this pin should be used for control signals for the exter-<br>nal differential driver/receiver.<br>The signal is Active High.                                      |

| 130                                                                                     | RSTOE**                                                          | Reset<br>Output Enable                                                                                                                                         | 0   | This is used for output control of RST signals.<br>In the differential mode, this pin should be used for control signals for the exter-<br>nal differential driver/receiver.<br>The signal is Active High.                                      |

| 32, 33, 35<br>38, 99,<br>100, 102,<br>105, 28,<br>10, 11, 13<br>16, 18, 20<br>25, 26, 7 | DB15 to<br>DB8,<br>UDBP,<br>DB7 to<br>DB0,<br>LDBP               | Data Bus 15 to<br>Data Bus 8,<br>Upper Data Bus Par-<br>ity,<br>Data Bus 7 to<br>Data Bus 0,<br>Lower Data Bus Parity                                          | I/O | These are bidirectional SCSI data buses made up of 2-byte data and each odd parity bit of the upper/lower byte.                                                                                                                                 |

| 46, 47, 48<br>84, 85, 86<br>87, 92, 43,<br>175, 2, 3,<br>5, 39, 40,<br>41, 42,<br>174   | DBOE15 to<br>DBOE8,<br>UDBOEP,<br>DBOE7 to<br>DBOE0,<br>LDBOEP** | Data Bus 15 to 8<br>Output Enable,<br>Upper Data Bus Out-<br>put Enable Parity,<br>Data Bus 7 to 0<br>Output Enable, Lower<br>Data Bus Output<br>Enable Parity | 0   | These are used for output control of DB15 to DB8, UDBP, DB7 to DB0, LDBP<br>signals.<br>In the differential mode, these pins should be used for control signals for the<br>external differential driver/receiver.<br>The signal is Active High. |

| 93                                                                                      | INIT** ***                                                       | Initiator                                                                                                                                                      | 0   | These are used for signals for indicating the operation or connection condi-<br>tion of the SPC.<br>These pins should be used for control signals for the external differential driver/                                                         |

| 94                                                                                      | TARG** ***                                                       | Target                                                                                                                                                         | 0   | receiver.<br>The signal is Active High.                                                                                                                                                                                                         |

| 49                                                                                      | S/DSEL**                                                         | Single-End<br>Differential<br>Select                                                                                                                           | I   | This is used for input of signals for selecting the chip operation mode.<br>SINGLE-ENDED: Enter –0.<br>DIFFERENTIAL: Enter –1.                                                                                                                  |

\*The correspondence between the  $\overline{C/D}$ ,  $\overline{C/D}$ ,  $\overline{I/O}$  signals and phase is given on the next page.

\*\*For the connection example of the external differential driver/receiver circuit, see SYSTEM CONFIGURATION, 5.

\*\*\*The operation or connection condition of the SPC is given on the next page.

Note: I/O pins for the SCSI interface can be connected directly to the single-end SCSI bus.

| Phase Name        | MSG  | C/D | 1/0 | Transfer Direction |        |  |

|-------------------|------|-----|-----|--------------------|--------|--|

| Phase Name        | WISG | C/D | 1/0 | Initiator          | Target |  |

| Data-out phase    | Н    | Н   | Н   | $\rightarrow$      |        |  |

| Data-in phase     | н    | н   | L   | ←                  |        |  |

| Command phase     | н    | L   | н   | $\rightarrow$      |        |  |

| Status phase      | н    | L   | L   | ←                  |        |  |

| Message-out phase | L    | L   | н   | $\rightarrow$      |        |  |

| Message-in phase  | L    | L   | L   | ←                  |        |  |

| INIT | TARG | Condition                                                 |

|------|------|-----------------------------------------------------------|

| L    | L    | Not connected to SCSI                                     |

| L    | Н    | Executing reselection phase or in connection as target    |

| н    | L    | Executing reselection phase or in connection as initiator |

### 2. MPU Interface

| Pin No.                   | Pin Symbol* | Pin Name                                  | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|-------------|-------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 139                       | CS0         | Chip<br>Select 0                          | I   | This is used for signals for the MPU to select the SPC as the I/O device.<br>The signal is Active Low.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 140                       | CS1         | Chip<br>Select 1                          | I   | This is used for select signals for the MPU to input and output DMA-bus data via the SPC.<br>The signal is Active Low.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 163 to 161,<br>159 to 155 | D15 to D8   | Data 15 to Data 8                         | I/O | These are used for the upper-byte and parity-bit signals of the data bus.<br>When the CS0 input is valid, these pins serve as I/O ports for the registers in the SPC.                                                                                                                                                                                                                                                                                                                                                   |

| 164                       | UDP         | Upper Data Parity                         |     | When the $\overline{\text{CS1}}$ input is valid, these pins serve as data I/O ports for the DMA bus.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 151 to 145,<br>143        | D7 to D0    | Data 7 to Data 0                          | I/O | These are used for lower-byte and parity-bit signals of the data bus.<br>When the $\overline{CS0}$ input is valid, these pins serve as I/O ports for the registers in the SPC.                                                                                                                                                                                                                                                                                                                                          |

| 141                       | LDP         | Lower Data Parity                         |     | When the $\overline{\text{CS1}}$ input is valid, these pins serve as data I/O ports for the DMA bus.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 138 to 134                | A4 to A0    | Address 4 to<br>Address 0                 | I   | These are used to input addresses for selecting the internal register.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 170                       | RD (R/W)    | Read (Read/Write)                         | I   | In the 80-series mode, this is used for input of signals (IORD or RD) for the read operation from the SPC to the MPU. The signal is Active Low.<br>In the 68-series mode, this is used for input of control signals (R/W) for the read and write operations from the MPU to the SPC.<br>The signal is Active High at the read operation and Active Low at the write operation.                                                                                                                                          |

| 168                       | WR (LDS)    | Write (Lower Data<br>Strobe)              | I   | In the 80-series mode, this is used for input of signals (IOWR or WR) for the write operation from the MPU to the SPC.<br>In the 68-series mode, this is used for input of LDS signals output by the MPU when the lower bytes of the data bus are valid.<br>The signal is Active Low in both modes.                                                                                                                                                                                                                     |

| 167                       | BHE (UDS)   | Bus High Enable<br>(Upper Data<br>Strobe) | I   | In the 80-series mode, this is used for input of BHE signals output by the MPU when the upper bytes of the data bus are valid.<br>In the 68-series mode, this is used for input of UDS signals output by the MPU when the upper bytes of the data bus are valid.<br>The signal is Active Low in both modes.                                                                                                                                                                                                             |

| 171                       | INT (INT)   | Interrupt Request                         | 0   | This is used for output of interrupt request signals.In the 80-series mode, the signal is Active High.In the 68-series mode, the signal is Active Low.When SPC BSY = 1 (bit 6 of SPC status register = 1), this signal is not active.Therefore, this signal becomes inactive when a command is issued to the SPC at active, or when the SPC BSY goes to 1 after automatically starting the operation.This signal becomes inactive as soon as the first interrupt code is read, even if more than one interrupt is held. |

| 172                       | MODE        | Mode                                      | I   | This is used to input signals specifying the type of MPU and DMA buses.<br>A High level is input in the 80-series mode.<br>A Low level is input in the 68-series mode.                                                                                                                                                                                                                                                                                                                                                  |

\*The pin symbols in parentheses are the ones when the MODE input is Low.

#### 3. DMA Interface

Like the MPU interface, the DMA interface has input/output signals for the 68 series and 80 series.

| Pin No.               | Pin Symbol*      | Pin Name                                      | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

|-----------------------|------------------|-----------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 82                    | DREQ             | DMA Request                                   | 0   | This is used for output of DMA transfer request signals to the DMA controller.<br>A request is made for data transfer between the SPC and the memory over the<br>DMA bus.<br>The signal is Active High.                                                                                                                                                                                                                                   |  |  |  |  |

| 81                    | DACK             | DMA Acknowledge                               | I   | This is used for input of DMA acknowledge signals from the DMA controller.<br>When this input pin is active, the DMA cycle (read/write) is executed.<br>The signal is Active Low.                                                                                                                                                                                                                                                         |  |  |  |  |

| 74 to 72, 70<br>to 66 | DMD15 to<br>DMD8 | DMA Data 15 to<br>DMA Data 8                  | I/O | These are used for input and output of the upper-byte and parity signals o<br>DMA data bus.<br>When the CS1 input is valid, these pins are connected directly to the MPU b<br>These are used for input and output of the lower-byte and parity signals o<br>DMA data bus.<br>When the CS1 input is valid, these pins are connected directly to the MPU b<br>In the 80-series mode, this is used for input of signals (IORD or RD) for out |  |  |  |  |

| 76                    | UDMDP            | Upper DMA<br>Data Parity                      |     | when the CST input is valid, these pins are connected directly to the MPU bus.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 64 to 59,<br>57, 56   | DMD7 to<br>DMD0  | DMA Data 7 to<br>DMA Data 0                   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 54                    | LDMDP            | Lower DMA<br>Data Parity                      |     | when the CST input is valid, these pins are connected directly to the MPO bus.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 50                    | IORD<br>(DMR/W)  | I/O Read (DMA<br>Read/Write)                  | I   | In the 80-series mode, this is used for input of signals (IORD or RD) for output-<br>ting data from the SPC to the DMA bus.<br>The signal is Active Low.<br>In the 68-series mode, this is used for input of control signals (DMR/W) for input-<br>ting and outputting data from the DMA controller to the SPC.<br>The signal is Active High for output and Active Low for input.                                                         |  |  |  |  |

| 51                    | IOWR<br>(DMLDS)  | I/O Write (DMA<br>Lower Data Strobe)          | I   | In the 80-series mode, this is used for input of signals (IOWR or WR) for input-<br>ting data from the DMA bus to the SPC.<br>In the 68-series mode, this is used for input of LDS signals output by the DMA<br>controller when the lower bytes of the DMA data bus are valid.<br>The signal is Active Low in both modes.                                                                                                                 |  |  |  |  |

| 79                    | DMBHE<br>(DMUDS) | DMA Bus<br>High Enable<br>(Upper Data Strobe) | I   | In the 80-series mode, this is used for input of BHE signals output by the DMA controller when the upper bytes of the DMA data bus are valid.<br>In the 68-series mode, this is used for input of UDS signals output by the DMA controller when the upper bytes of the DMA data bus are valid.<br>The signal is Active Low in both modes.                                                                                                 |  |  |  |  |

| 53                    | DMA0             | DMA Address 0                                 | I   | In the 80-series mode, this is used for input of address data A0 signals output by the DMA controller.<br>In the 68-series mode, this is connected to the power supply (VDD).                                                                                                                                                                                                                                                             |  |  |  |  |

| 83                    | TP               | Transfer<br>Permission                        | I   | This is used for input of DMA transfer permission signals.<br>When this signal is active, the SPC performs the DMA transfer.<br>When this signal becomes inactive during DMA transfer, transfer is temporarily<br>stopped at the block boundary.<br>The signal is Active High.                                                                                                                                                            |  |  |  |  |

\*The pin symbols in parentheses are the ones when the MODE input is Low.

| MB86603 |

|---------|

|---------|

# 4. Others

| Pin No.                                                                                                                                                                                                                                     | Pin Symbol      | Pin Name         | I/O | Function                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 173                                                                                                                                                                                                                                         | RESET           | Reset            | I   | This is used for input of system-reset signals.<br>At input, the reset signals must be kept active for four or more clock cycles.<br>The signal is Active Low. |

| 78                                                                                                                                                                                                                                          | CLK             | Clock            | I   | This is used for input of clock pulse signals.<br>The clock frequency ranges from 12 MHz to 32 MHz.                                                            |

| 21, 44, 58,<br>71, 77,<br>110, 132,<br>144, 153,<br>169                                                                                                                                                                                     | V <sub>DD</sub> | Power Supply     | _   | These are used for the +5 V power supply.                                                                                                                      |

| 4, 8, 14,<br>22, 30, 36,<br>45, 55, 65,<br>75, 91, 97,<br>103, 111,<br>119, 125,<br>133, 142,<br>152, 165                                                                                                                                   | V <sub>SS</sub> | Ground           | _   | These are used for grounding.                                                                                                                                  |

| 96                                                                                                                                                                                                                                          | TEST2           | Test             | I   | Must be grounded                                                                                                                                               |

| 89, 90                                                                                                                                                                                                                                      | (OPEN)          | (Open)           | —   | Must be open. Do not connect.                                                                                                                                  |

| $\begin{array}{c} 1,  6,  9,  12 \\ 15,  17,  19 \\ 23,  24,  27 \\ 29,  31,  34 \\ 37,  52,  80 \\ 88,  95,  98 \\ 101,  104 \\ 106,  108, \\ 112,  114, \\ 116,  118, \\ 120,  122, \\ 126,  128, \\ 154,  160, \\ 166,  176 \end{array}$ | (NC)            | (Non Connection) | _   | Not connected internally. As a general rule, do not connect.                                                                                                   |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                     | Symbol          | Rating                                         | Unit |

|-------------------------------|-----------------|------------------------------------------------|------|

| Supply voltage*               | V <sub>DD</sub> | V <sub>SS</sub> – 0.5 to +6.0                  | V    |

| Input voltage*                | VI              | V <sub>SS</sub> – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Output voltage*               | Vo              | V <sub>SS</sub> – 0.5 to V <sub>DD</sub> + 0.5 | V    |

| Operating ambient temperature | Тор             | -25 to + 85                                    | °C   |

| Storage temperature           | Tstg            | -40 to + 125                                   | °C   |

\*The voltages are based on  $V_{SS}$  (= 0 V).

Note: Permanent device damage may occur if the above ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **RECOMMENDED OPERATING CONDITIONS**

|                               | Paramete        |                    | Symbol          | R               | Unit |      |      |    |

|-------------------------------|-----------------|--------------------|-----------------|-----------------|------|------|------|----|

|                               | Faiamete        |                    | Symbol          | Min.            | Тур. | Max. | onit |    |

| Supply voltage*               | Supply voltage* |                    |                 |                 |      |      | 5.25 | V  |

|                               | Non-SCSI p      | ing                | RESET           |                 | 2.4  | _    | —    | V  |

| High-level input voltage*     | N011-3031 p     | 1115               | Others          | V <sub>IH</sub> | 2.2  | _    | —    | V  |

|                               | SCSI pins       |                    |                 | 2.0             | _    | —    | V    |    |

| Low-level input voltage*      |                 |                    |                 | V <sub>IL</sub> | _    | _    | 0.8  | V  |

|                               | Non-SCSI p      | ins                |                 | _               | _    | -2.0 | mA   |    |

| High lovel output ourrept**   | SCSI pins       | In single-end mode | REQ, ACK        | I <sub>ОН</sub> | _    | _    | -8.0 | mA |

| High-level output current**   |                 |                    | Others          |                 | _    | _    | —    | mA |

|                               | In differentia  | l mode             |                 | _               | _    | -8.0 | mA   |    |

| Non-SCSI pins                 |                 |                    |                 |                 | _    | _    | +3.2 | mA |

| Low-level output current**    | SCSI pins       |                    | I <sub>OL</sub> |                 | _    | +48  | mA   |    |

| Operating ambient temperature | 9               |                    |                 | T <sub>A</sub>  | 0    | _    | +70  | °C |

\*The voltages are based on V<sub>SS</sub> (= 0 V). \*\*SCSI pins can be UDBP, DB15, to DB8, LDBP, DB7 to DB0, BSY, SEL, RST, ATN, REQ, ACK, MSG, C/D, and I/D pins.

Note: The recommended operating conditions are the recommended values for assuring normal logic operation of the LSI. Requirements in electrical characteristics (DC and AC characteristics) are assured within the range of the recommended operating conditions.

# **ELECTRICAL CHARACTERISTICS**

### 1. DC Characteristics

| $(V_{DD} = 5 V \pm 5\%, V_{SS} = 0 V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C$ |

|----------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------|

|                                | Symbol     | Measurement          | Requirements    |                            | Unit                                        |                 |      |      |

|--------------------------------|------------|----------------------|-----------------|----------------------------|---------------------------------------------|-----------------|------|------|

|                                | Parameter  |                      |                 |                            |                                             |                 | Max. | Unit |

|                                | Non-SCSI p | ing                  | RESET           |                            |                                             | 2.4             | —    | V    |

| High-level input voltage*      | Non-SCSI p | ins                  | Others          | V <sub>IH</sub>            | —                                           | 2.2             | —    | V    |

|                                | SCSI pins  |                      | -               | ]                          |                                             | 2.0             | —    | V    |

| Low-level input voltage        |            |                      |                 | V <sub>IL</sub>            | _                                           | _               | 0.8  | V    |

| SCSI-pin input hysteresis      |            |                      |                 | V <sub>HW</sub>            | _                                           | 0.2             | —    | V    |

|                                | Non-SCSI p | ins                  |                 | I <sub>OH</sub> = -2.0 mA  | 4.2                                         | V <sub>DD</sub> | V    |      |

| High-level output voltage*     | SCSI pins  | In single-end mode   | REQ, ACK        | V <sub>OH</sub>            | I <sub>OH</sub> = -8.0 mA                   | 2.5             | —    | V    |

| High-level output voltage      |            |                      | Others          |                            | _                                           | _               | —    | V    |

|                                |            | In differential mode |                 |                            | I <sub>OL</sub> = -8.0 mA                   | 2.5             | —    | V    |

|                                | Non-SCSI p | ins                  |                 | I <sub>OL</sub> = +3.2 mA  | V <sub>SS</sub>                             | 0.4             | V    |      |

| Low-level output voltage       | SCSI pins  |                      | V <sub>OL</sub> | I <sub>OL</sub> = +3.2 mA  | V <sub>SS</sub>                             | 0.4             | V    |      |

|                                |            |                      |                 | I <sub>OL</sub> = +48.0 mA | _                                           | 0.5             | V    |      |

| Input leakage current          |            |                      |                 | ILI                        | $V_{IN} = 0$ to $V_{DD}$                    | -10             | +10  |      |

| Input/output leakage current** |            |                      |                 |                            | $V_{IN} = 0$ to $V_{DD}$                    | -10             | +10  | μΑ   |

| Supply voltage                 |            |                      |                 | I <sub>DD</sub>            | Output open<br>Clock: 32 MHz<br>(operating) | _               | 70   | mA   |

\*SCSI pins can be UDBP, DB15, to DB8, LDBP, DB7 to DB0, BSY, SEL, RST, ATN, REQ, ACK, MSG, C/D, and I/D pins.

\*\*These are leakage currents when the output impedance of tristate-output and bidirectional bus pins is high.

# 2. Pin Capacitance

|                              |           |                  |                                      |        |      | (·A  | 120 0) |

|------------------------------|-----------|------------------|--------------------------------------|--------|------|------|--------|

| Parameter                    |           | Symbol           | Measurement                          | Requir | Unit |      |        |

|                              |           | Symbol           | Conditions                           | Min.   | Max. | Onit |        |

| Input-pin capacitance        |           |                  | C <sub>IN</sub>                      |        | _    | 16   | pF     |

| Output-pin capacitance       |           | C <sub>OUT</sub> | $V_{DD} = V_{IN} = 0 V$<br>f = 1 MHz | —      | 16   | pF   |        |

|                              | ance      | Non-SCSI pins    | C <sub>I/O</sub>                     |        |      | 16   | pF     |

| Input/output-pin capacitance | SCSI pins | 01/0             |                                      | _      | 32   | pF   |        |

$(T_{A} = +25^{\circ}C)$

$(V_{DD} = 5 V \pm 5\%, V_{SS} = 0 V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C)$

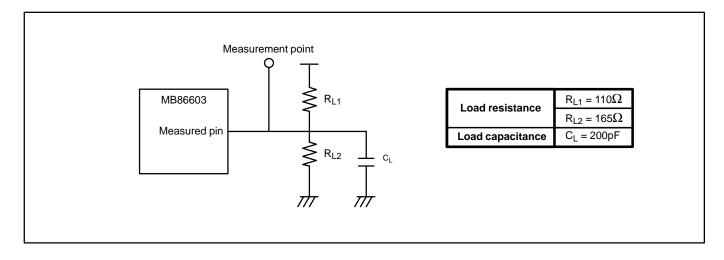

# 3. Loading Conditions for Measurement of AC Characteristics

### (1) Non-SCSI pins

Measurement point

MB86603

INT

60pF

Measured pin

CL

INT

60pF

D15 to D8, UDP, D7 to D0,LDP, DMD15 to DMD8, UDMDP, DMD7 to DMD0, LDMDP

85pF

#### (2) SCSI pins

### 4. AC Characteristics

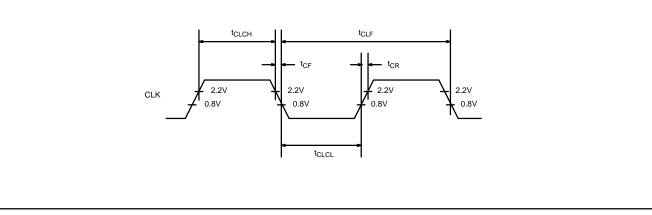

# (1) System clock

| Parameter                   | Symbol -          | Limits |      |       | Unit |

|-----------------------------|-------------------|--------|------|-------|------|

|                             |                   | Min.   | Тур. | Max.  | Onit |

| Clock frequency             | t <sub>CLF</sub>  | 31.25  | _    | 83.26 |      |

| Clock pulse duration (Low)  | tCLCL             | 10.0   |      | —     |      |

| Clock pulse duration (High) | t <sub>CLCH</sub> | 10.0   |      | —     | ns   |

| Clock pulse rise time       | t <sub>CR</sub>   |        | -    | 10.0  |      |

| Clock pulse fall time       | t <sub>CF</sub>   | _      |      | 10.0  |      |

Clock signal

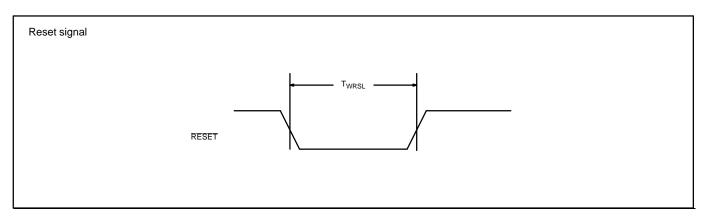

#### (2) System reset

| Parameter                           | Symbol            | Limits            |      |      | Unit |

|-------------------------------------|-------------------|-------------------|------|------|------|

| Falanielei                          |                   | Min.              | Тур. | Max. | Onit |

| Reset (RESET) pulse duration at Low | t <sub>WRSL</sub> | 4t <sub>CLF</sub> | _    | —    | ns   |

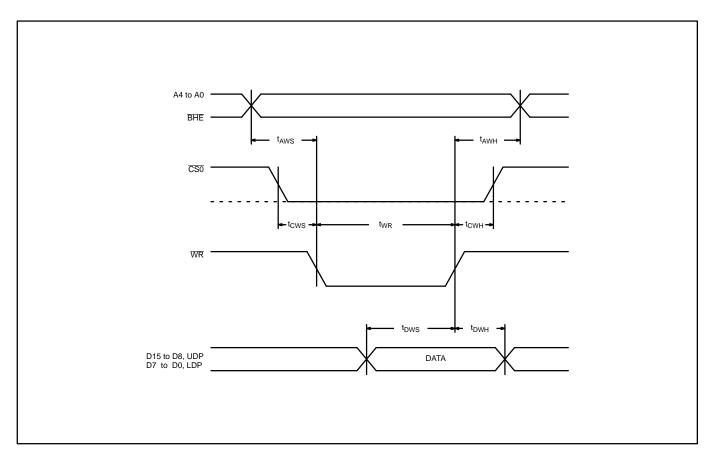

#### (3) MPU Interface (80 Series)

Register write timing

| Parameter                          | Symbol           | Lin  | Unit |       |

|------------------------------------|------------------|------|------|-------|

| Falanietei                         |                  | Min. | Max. | Offic |

| Address (A4 to A0), BHE setup time | t <sub>AWS</sub> | 40   | _    |       |

| Address (A4 to A0) hold time       | t <sub>AWH</sub> | 20   |      |       |

| CS0 setup time                     | t <sub>CWS</sub> | 20   | _    |       |

| CS0 hold time                      | t <sub>CWH</sub> | 10   | _    | ns    |

| Data setup time                    | t <sub>DWS</sub> | 40   | _    |       |

| Data hold time                     | t <sub>DWH</sub> | 20   | _    |       |

| WR pulse duration at Low           | t <sub>WR</sub>  | 70   | _    |       |

#### MB86603

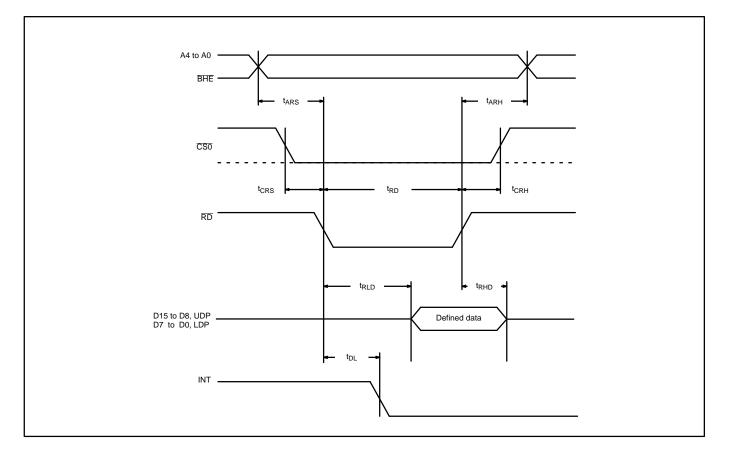

• Register read timing

| Parameter                                                      | Symbol           | Lin  | Unit |      |

|----------------------------------------------------------------|------------------|------|------|------|

|                                                                |                  | Min. | Max. | Onic |

| Address (A4 to A0), BHE setup time                             | t <sub>ARS</sub> | 40   | _    |      |

| Address (A4 to A0) hold time                                   | t <sub>ARH</sub> | 20   |      |      |

| CS0 setup time                                                 | t <sub>CRS</sub> | 20   |      |      |

| CS0 hold time                                                  | t <sub>CRH</sub> | 10   | _    |      |

| $\overline{RD}$ set Low $\rightarrow$ data output defined time | t <sub>RLD</sub> | —    | 70   | ns   |

| $\overline{RD}$ set High $ ightarrow$ data output disable time | t <sub>RHD</sub> | 5    | _    |      |

| RD pulse duration at Low                                       | t <sub>RD</sub>  | 70   | _    |      |

| INT signal clear time                                          | t <sub>DL</sub>  | _    | 50   |      |

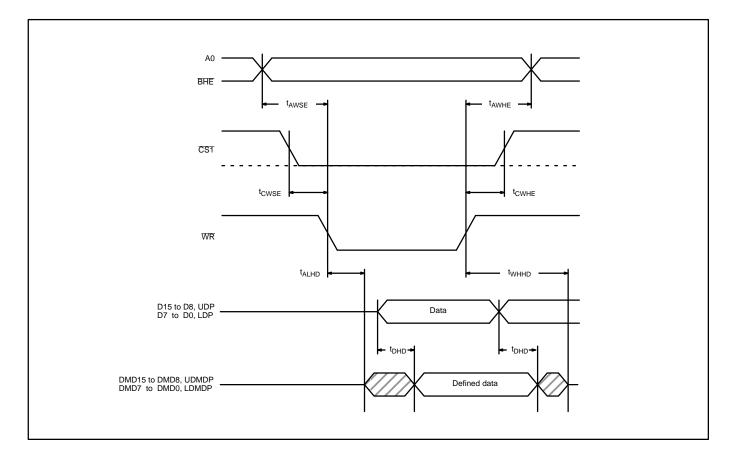

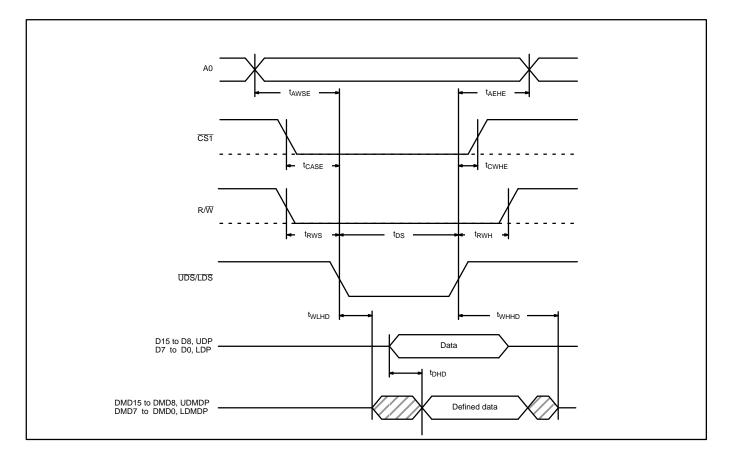

#### • Register write timing (for external access)

| Parameter                                                                    | Symbol            | Lin  | Unit |      |

|------------------------------------------------------------------------------|-------------------|------|------|------|

| Farameter                                                                    |                   | Min. | Max. | Onit |

| Address (A0), BHE setup time                                                 | tAWSE             | 40   | _    |      |

| Address (A0), BHE hold time                                                  | t <sub>AWHE</sub> | 20   |      |      |

| CS1 setup time                                                               | tCWSE             | 20   | _    |      |

| CS1 hold time                                                                | tCWHE             | 10   | _    | ns   |

| $\overline{\mathrm{WR}}$ set Low $\rightarrow$ DMA bus output delay time     | t <sub>WLHD</sub> | —    | 70   |      |

| $\overline{\mathrm{WR}}$ set High $ ightarrow$ DMA bus output undefined time | t <sub>WHHD</sub> | 5    | _    |      |

| MPU data bus $\rightarrow$ DMA bus output delay time                         | t <sub>DHD</sub>  | _    | 40   |      |

#### MB86603

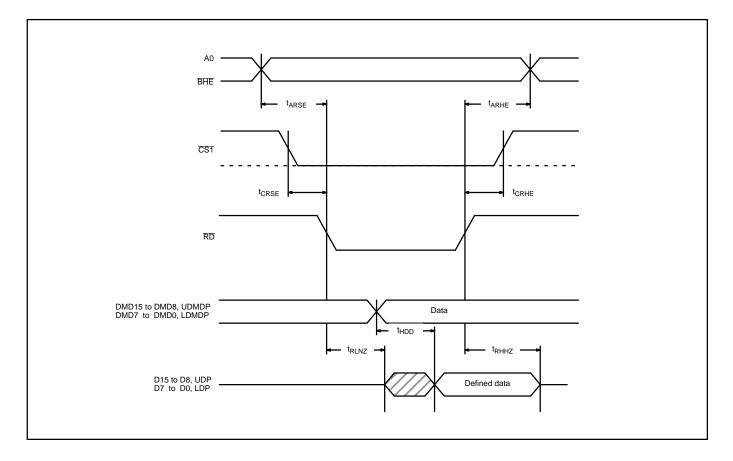

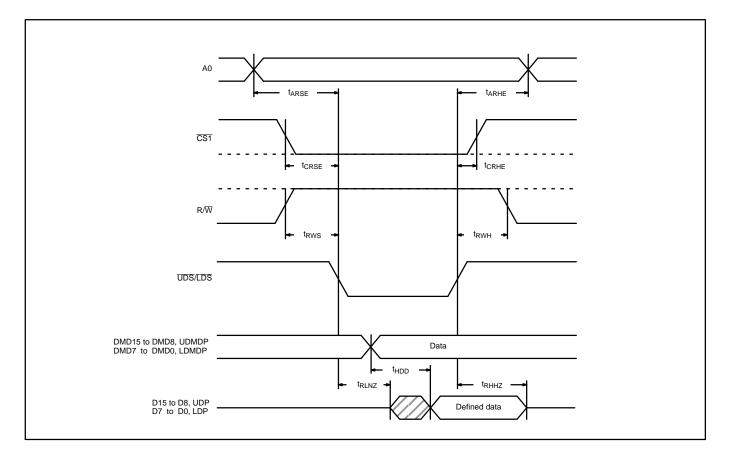

• Register read timing (for external access)

| Parameter                                                                      | Symbol            | Lin  | Unit |       |

|--------------------------------------------------------------------------------|-------------------|------|------|-------|

| Falameter                                                                      |                   | Min. | Max. | Offic |

| Address (A0), BHE setup time                                                   | tARSE             | 40   | _    |       |

| Address (A0), BHE hold time                                                    | t <sub>ARHE</sub> | 20   |      |       |

| CS1 setup time                                                                 | tCRSE             | 20   |      |       |

| CS1 hold time                                                                  | t <sub>CRHE</sub> | 10   | _    | ns    |

| $\overline{\text{RD}}$ set Low $\rightarrow$ MPU data bus output enable time   | t <sub>RLNZ</sub> | _    | 70   |       |

| $\overline{\text{RD}}$ set High $\rightarrow$ MPU data bus output disable time | t <sub>RHHZ</sub> | 5    |      |       |

| DMA bus $\rightarrow$ MPU data bus output delay time                           | t <sub>HDD</sub>  | _    | 40   |       |

# (4) MPU Interface (68 Series)

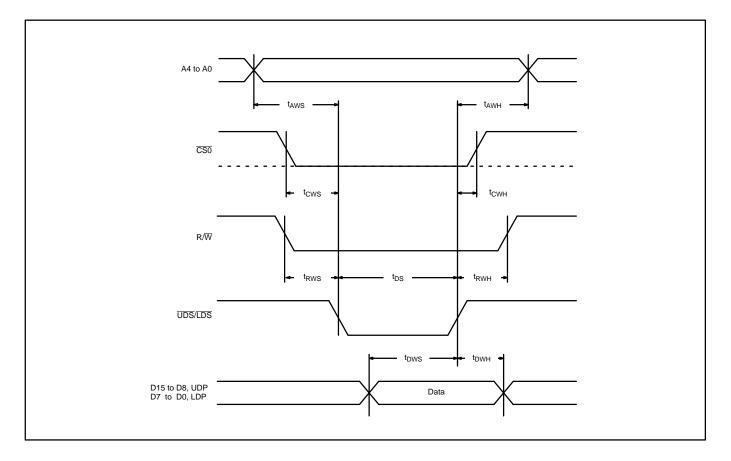

Register write timing

| Parameter                     | Symbol           | Lin  | Unit |       |

|-------------------------------|------------------|------|------|-------|

|                               |                  | Min. | Max. | Offic |

| Address (A4 to A0) setup time | t <sub>AWS</sub> | 40   | —    |       |

| Address (A4 to A0) hold time  | t <sub>AWH</sub> | 20   | —    |       |

| CS0 setup time                | t <sub>CWS</sub> | 20   | —    |       |

| CS0 hold time                 | t <sub>CWH</sub> | 10   | —    |       |

| Data setup time               | t <sub>DWS</sub> | 40   | _    | ns    |

| Data hold time                | t <sub>DWH</sub> | 20   | _    |       |

| UDS/LDS pulse duration at Low | t <sub>DS</sub>  | 70   | _    |       |

| R/W setup time                | t <sub>RWS</sub> | 20   |      |       |

| R/₩ hold time                 | t <sub>RWH</sub> | 20   |      |       |

#### MB86603

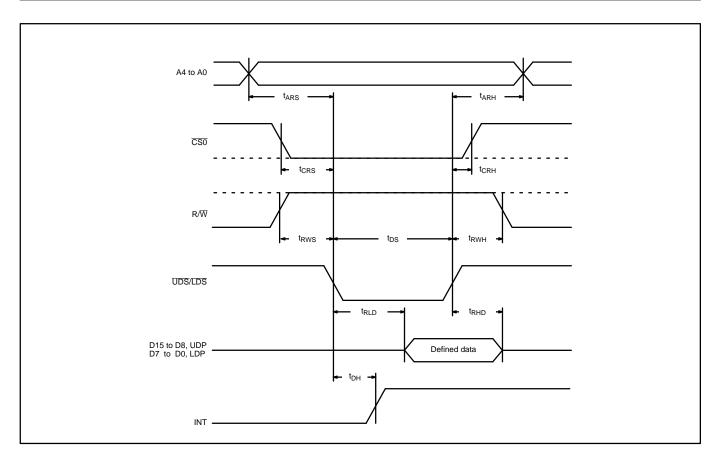

Register read timing

| Parameter                     | Symbol           | Lin  | Unit |      |

|-------------------------------|------------------|------|------|------|

| Farameter                     | Symbol           | Min. | Max. | Unit |

| Address (A4 to A0) setup time | t <sub>ARS</sub> | 40   | _    |      |

| Address (A4 to A0) hold time  | t <sub>ARH</sub> | 20   |      |      |

| CS0 setup time                | t <sub>CRS</sub> | 20   |      |      |

| CS0 hold time                 | t <sub>CRH</sub> | 10   |      |      |

| Data output defined time      | t <sub>RLD</sub> | —    | 70   | ns   |

| Data output disable time      | t <sub>RHD</sub> | 5    | _    | 115  |

| UDS/LDS pulse duration at Low | t <sub>DS</sub>  | 70   | —    |      |

| R/W setup time                | t <sub>RWS</sub> | 20   | _    |      |

| R/W hold time                 | t <sub>RWH</sub> | 20   |      |      |

| INT signal clear time         | t <sub>DH</sub>  | _    | 50   |      |

#### • Register write timing (for external access)

| Parameter                                                                                          | Symbol            | Lin  | Unit |      |

|----------------------------------------------------------------------------------------------------|-------------------|------|------|------|

| Falameter                                                                                          |                   | Min. | Max. | Onit |

| Address (A0) setup time                                                                            | t <sub>AWSE</sub> | 40   | _    |      |

| Address (A0) hold time                                                                             | t <sub>AWHE</sub> | 20   | _    |      |

| CS1 setup time                                                                                     | t <sub>CWSE</sub> | 20   | _    |      |

| CS1 hold time                                                                                      | t <sub>CWHE</sub> | 10   | _    |      |

| $\overline{\text{UDS}}/\overline{\text{LDS}}$ set Low $\rightarrow$ DMA bus output delay time      | t <sub>WLHD</sub> | —    | 70   | ns   |

| $\overline{\text{UDS}}/\overline{\text{LDS}}$ set High $\rightarrow$ DMA bus output undefined time | t <sub>WHHD</sub> | 5    | —    |      |

| MPU data bus $\rightarrow$ DMA bus output delay time                                               | t <sub>DHD</sub>  | —    | 40   |      |

| R/W setup time                                                                                     | t <sub>RWS</sub>  | 20   | —    |      |

| R/W hold time                                                                                      | t <sub>RWH</sub>  | 20   | _    |      |

#### MB86603

• Register read timing (for external access)

| Parameter                                                                                             | Symbol            | Lin  | Unit |       |

|-------------------------------------------------------------------------------------------------------|-------------------|------|------|-------|

| Falantetei                                                                                            | Symbol            | Min. | Max. | Offic |

| Address (A0) setup time                                                                               | t <sub>ARSE</sub> | 40   | _    |       |

| Address (A0) hold time                                                                                | t <sub>ARHE</sub> | 20   |      |       |

| CS1 setup time                                                                                        | tCRSE             | 20   |      |       |

| CS1 hold time                                                                                         | t <sub>CRHE</sub> | 10   | —    |       |

| $\overline{\text{UDS}}/\overline{\text{LDS}}$ set Low $\rightarrow$ MPU data bus output enable time   | t <sub>RLNZ</sub> | —    | 70   | ns    |

| $\overline{\text{UDS}}/\overline{\text{LDS}}$ set High $\rightarrow$ MPU data bus output disable time | t <sub>RHHZ</sub> | 5    | —    |       |

| DMA bus $\rightarrow$ MPU data bus output delay time                                                  | t <sub>HDD</sub>  | —    | 40   |       |

| R/W setup time                                                                                        | t <sub>RWS</sub>  | 20   | _    |       |

| R/W hold time                                                                                         | t <sub>RWH</sub>  | 20   | _    |       |

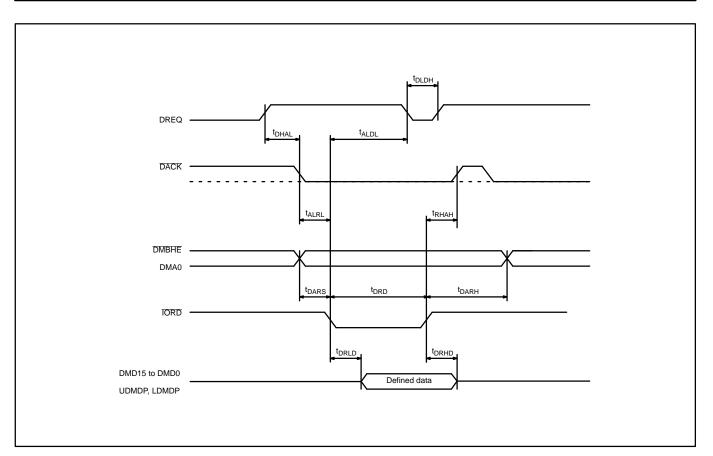

#### (5) DMA Interface

#### DMA access timing

The time regulations are not applicable in the following cases:

- During SCSI input and when data buffer EMPTY, or when one byte held

- During SCSI output and when data buffer FULL, or when 63 bytes held

- When parity error detected (target)

- When error stopping transfer occurs in SCSI interface

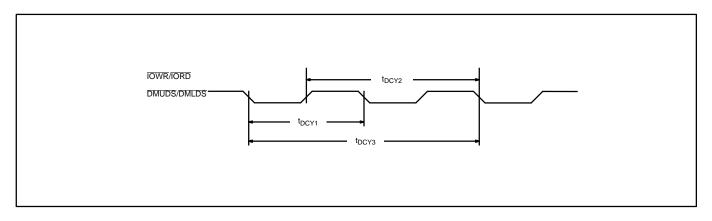

#### [Burst mode (for 80 series and 68 series)]

• Access cycle time

| Parameter           | Symbol -          | Lin               | Unit |      |

|---------------------|-------------------|-------------------|------|------|

|                     |                   | Min.              | Max. | Onit |

| Access cycle time 1 | t <sub>DCY1</sub> | 2t <sub>CLF</sub> | _    |      |

| Access cycle time 2 | t <sub>DCY2</sub> | 3t <sub>CLF</sub> | _    | ns   |

| Access cycle time 3 | t <sub>DCY3</sub> | 4t <sub>CLF</sub> | _    |      |

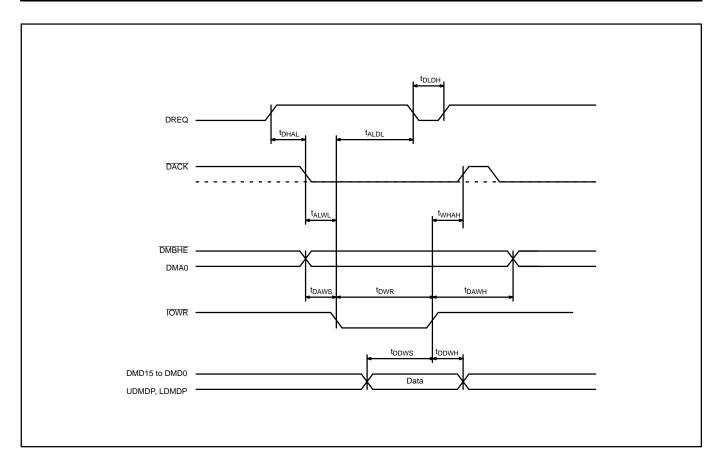

#### [Burst mode for 80 series]

Write timing

| Parameter                                                                       | Symbol            | Lin  | nits | Unit |

|---------------------------------------------------------------------------------|-------------------|------|------|------|

| Parameter                                                                       | Symbol            | Min. | Max. | Unit |

| DREQ set High $\rightarrow \overline{\text{DACK}}$ set Low                      | t <sub>DHAL</sub> | 0    | _    |      |

| $\overline{\text{IOWR}}$ set Low $\rightarrow$ DREQ set Low                     | t <sub>ALDL</sub> | —    | 35   |      |

| DREQ set Low $\rightarrow$ DREQ set High                                        | t <sub>DLDH</sub> | 0    | _    |      |

| $\overline{\text{DACK}}$ set Low $\rightarrow \overline{\text{IOWR}}$ set Low   | t <sub>ALWL</sub> | 0    | _    |      |

| DMBHE, DMA0 setup time                                                          | t <sub>DAWS</sub> | 20   |      | ns   |

| IOWR pulse duration at Low                                                      | t <sub>DWR</sub>  | 40   |      | 115  |

| $\overline{\text{IOWR}}$ set High $\rightarrow \overline{\text{DACK}}$ set High | t <sub>WHAH</sub> | 0    |      |      |

| DMBHE, DMA0 hold time                                                           | t <sub>DAWH</sub> | 20   |      |      |

| Input data setup time                                                           | t <sub>DDWS</sub> | 30   |      |      |

| Input data hold time                                                            | t <sub>DDWH</sub> | 10   |      |      |

#### • Read timing

| Parameter                                                                       | Symbol            | Lin  | nits | Unit  |

|---------------------------------------------------------------------------------|-------------------|------|------|-------|

| Farameter                                                                       | Symbol            | Min. | Max. | Offic |

| DREQ set High $\rightarrow \overline{\text{DACK}}$ set Low                      | t <sub>DHAL</sub> | 0    | _    |       |

| $\overline{\text{IORD}}$ set Low $\rightarrow$ DREQ set Low                     | t <sub>ALDL</sub> | —    | 35   |       |

| DREQ set Low $\rightarrow$ DREQ set High                                        | t <sub>DLDH</sub> | 0    | _    |       |

| $\overrightarrow{DACK}$ set Low $\rightarrow \overrightarrow{IORD}$ set Low     | t <sub>ALRL</sub> | 0    | _    |       |

| DMBHE, DMA0 setup time                                                          | t <sub>DARS</sub> | 20   | _    | ns    |

| IODR pulse duration at Low                                                      | t <sub>DRD</sub>  | 40   | _    | 115   |

| $\overline{\text{IODR}}$ set High $\rightarrow \overline{\text{DACK}}$ set High | t <sub>RHAH</sub> | 0    | _    |       |

| DMBHE, DMA0 hold time                                                           | t <sub>DARH</sub> | 20   | _    |       |

| Data output defined time                                                        | t <sub>DRLD</sub> |      | 40   |       |

| Data output hold time                                                           | t <sub>DRHD</sub> | 5    |      |       |

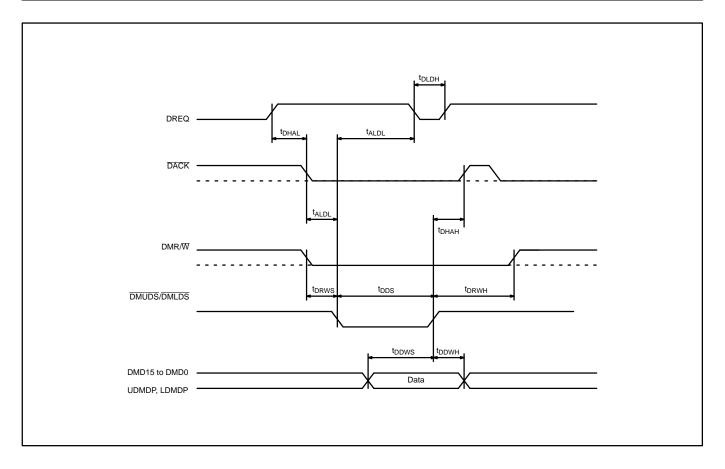

#### [Burst mode for 68 series]

Write timing

| Parameter                                                                                     | Symbol            | Lin  | nits | Unit  |

|-----------------------------------------------------------------------------------------------|-------------------|------|------|-------|

| Farameter                                                                                     | Symbol            | Min. | Max. | Offic |

| DREQ set High $\rightarrow$ DACK set Low                                                      | t <sub>DHAL</sub> | 0    | _    |       |

| DMUDS/DMLDS set Low → DREQ set Low                                                            | t <sub>ALDL</sub> | —    | 35   |       |

| DREQ set Low $\rightarrow$ DREQ set High                                                      | t <sub>DLDH</sub> | 0    | _    |       |

| DACK set Low → DMUDS/DMLDS set Low                                                            | t <sub>ALDL</sub> | 10   | _    |       |

| DMR/W setup time                                                                              | t <sub>DRWS</sub> | 20   | _    | ns    |

| DMUDS/DMLDS pulse duration at Low                                                             | t <sub>DDS</sub>  | 40   | _    | 115   |

| $\overline{\text{DMUDS}/\text{DMLDS}}$ set High $\rightarrow \overline{\text{DACK}}$ set High | t <sub>DHAH</sub> | 0    | _    |       |

| DMR/W hold time                                                                               | t <sub>DRWH</sub> | 20   | —    |       |

| Input data setup time                                                                         | t <sub>DDWS</sub> | 30   | _    |       |

| Input data hold time                                                                          | t <sub>DDWH</sub> | 10   |      |       |

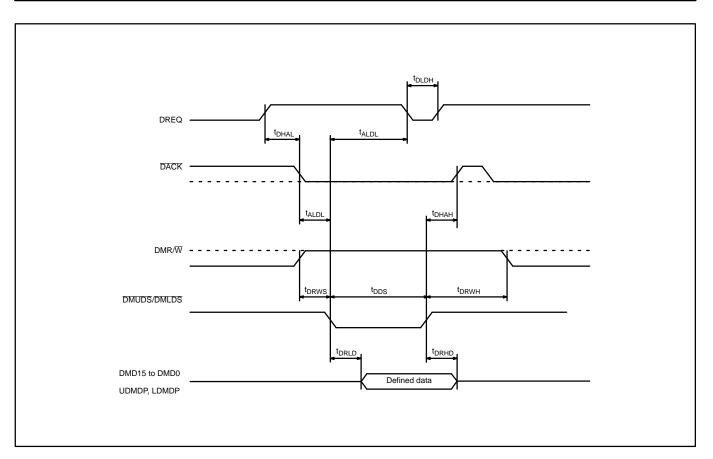

#### • Read timing

| Parameter                                                                                     | Symbol            | Lin  | nits | Unit |

|-----------------------------------------------------------------------------------------------|-------------------|------|------|------|

| Falameter                                                                                     | Symbol            | Min. | Max. | Onit |

| DREQ set High $\rightarrow \overline{\text{DACK}}$ set Low                                    | t <sub>DHAL</sub> | 0    | _    |      |

| DMUDS/DMLDS set Low → DREQ set Low                                                            | t <sub>ALDL</sub> | —    | 35   |      |

| DREQ set Low $\rightarrow$ DREQ set High                                                      | t <sub>DLDH</sub> | 0    | —    |      |

| DACK set Low → DMUDS/DMLDS set Low                                                            | t <sub>ALDL</sub> | 10   | _    |      |

| DMR/W setup time                                                                              | t <sub>DRWS</sub> | 20   | —    | ns   |

| DMUDS/DMLDS pulse duration at High                                                            | t <sub>DDS</sub>  | 40   | _    | 115  |

| $\overline{\text{DMUDS}/\text{DMLDS}}$ set High $\rightarrow \overline{\text{DACK}}$ set High | t <sub>DHAH</sub> | 0    | _    |      |

| DMR/W hold time                                                                               | t <sub>DRWH</sub> | 20   | _    |      |

| Output data defined time                                                                      | t <sub>DRLD</sub> |      | 40   |      |

| Output data hold time                                                                         | t <sub>DRHD</sub> | 5    |      |      |

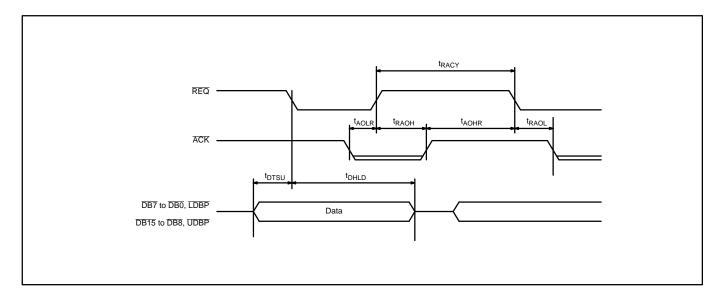

#### (6) SCSI Interface (Initiator)

#### [Asynchronous transfer mode]

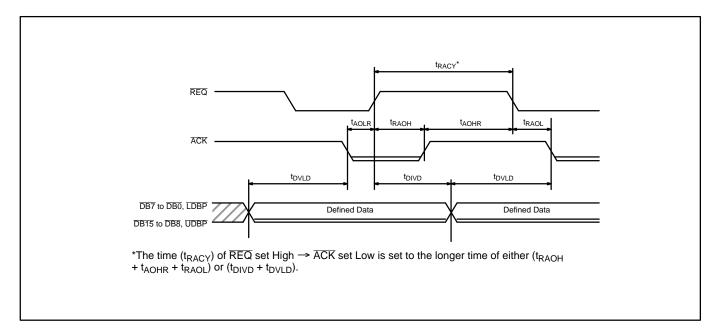

Input timing (target → initiator)

| Parameter                                                                      | Symbol            | Lin  | Unit                   |      |

|--------------------------------------------------------------------------------|-------------------|------|------------------------|------|

| Falanetei                                                                      | Symbol            | Min. | Max.                   | Onit |

| $\overline{ACK}$ set Low $\rightarrow \overline{REQ}$ set High                 | t <sub>AOLR</sub> | 0    | _                      |      |

| $\overline{REQ}$ set High $\rightarrow \overline{ACK}$ set High                | t <sub>RAOH</sub> | _    | 60                     |      |

| $\overline{ACK}$ set High $\rightarrow \overline{REQ}$ set Low                 | t <sub>AOHR</sub> | 10   | _                      |      |

| Data bus defined $\rightarrow \overline{\text{REQ}}$ set Low                   | t <sub>DTSU</sub> | 10   | _                      | ns   |

| $\overline{REQ}$ set Low $\rightarrow$ data bus hold time                      | t <sub>DHLD</sub> | 20   | _                      |      |

| $\overline{REQ} \text{ set Low} \rightarrow \overline{ACK} \text{ set Low}$    | t <sub>RAOL</sub> |      | 40                     |      |

| $\overline{REQ} \text{ set High} \rightarrow \overline{ACK} \text{ set Low}^*$ | t <sub>RACY</sub> |      | 3t <sub>CLF</sub> + 40 |      |

\*The time  $(t_{RACY})$  of  $\overline{REQ}$  set High  $\rightarrow \overline{ACK}$  set Low is set to the longer time compared to  $(t_{RAOH} + t_{AOHR} + t_{RAOL})$ .

Note: The input timing regulations are not applicable in the following cases.

- When data register FULL in data phase

- When last byte transferred

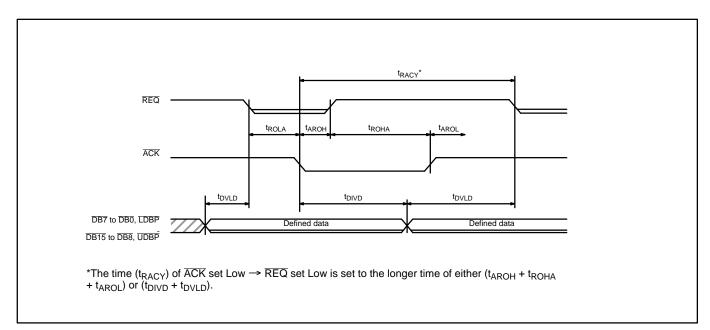

#### Output timing (initiator → target)

| Parameter                                                                    | Symbol            | Limits                  |      | Unit  |

|------------------------------------------------------------------------------|-------------------|-------------------------|------|-------|

| Falameter                                                                    | Symbol            | Min.                    | Max. | Offic |

| $\overline{\text{ACK}}$ set Low $\rightarrow \overline{\text{REQ}}$ set High | t <sub>AOLR</sub> | 0                       | —    |       |

| $\overline{REQ}$ set High $\rightarrow \overline{ACK}$ set High              | t <sub>RAOH</sub> | —                       | 60   |       |

| $\overline{\text{ACK}}$ set High $\rightarrow \overline{\text{REQ}}$ set Low | t <sub>AOHR</sub> | 10                      | _    | ns    |

| Data bus output defined $\rightarrow \overline{\text{ACK}}$ set Low*         | t <sub>DVLD</sub> | S●t <sub>CLF</sub> - 10 | _    | 115   |

| $\overline{REQ}$ set High $\rightarrow$ data bus hold time                   | t <sub>DIVD</sub> | 2t <sub>CLF</sub>       |      |       |

| $\overline{REQ} \text{ set Low} \rightarrow \overline{ACK} \text{ set Low}$  | t <sub>RAOL</sub> | _                       | 40   |       |

\*The value of S varies with the setting condition of the asynchronous setup time register (address 23).

Note: The output timing regulations are not applicable when the data register is EMPTY in the data phase.

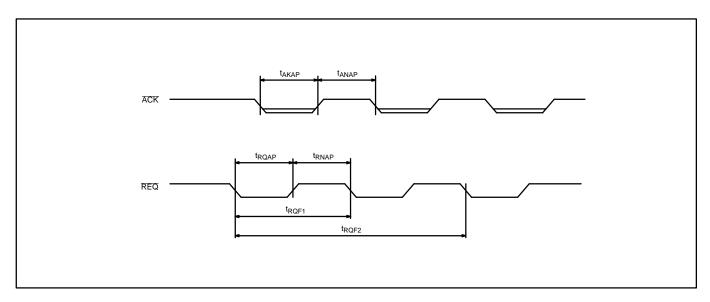

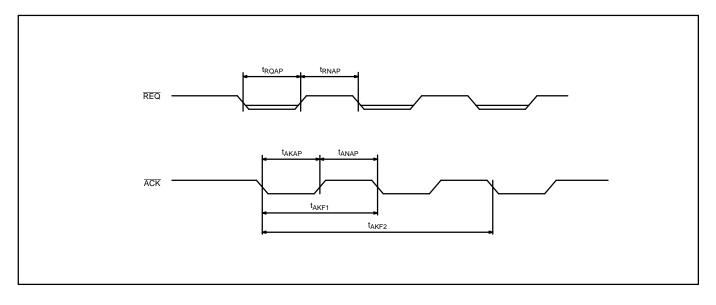

#### [Synchronous transfer mode]

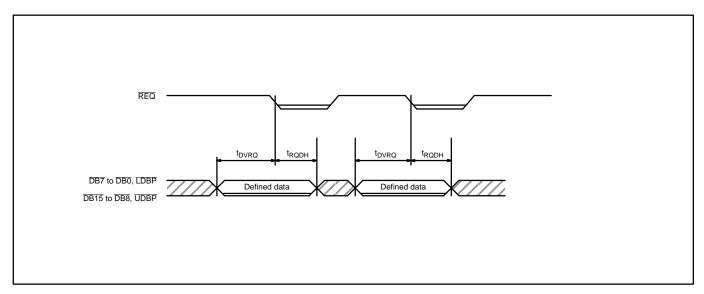

• REQ/ACK signal synchronization

| Parameter                | Symbol            | Lin                     | nits | Unit |

|--------------------------|-------------------|-------------------------|------|------|

| Falantetei               | Symbol            | Min.                    | Max. | onn  |

| ACK Assertion Period*    | t <sub>AKAP</sub> | A●t <sub>CLF</sub> – 3  | _    |      |

| ACK Negation Period*     | t <sub>ANAP</sub> | $N \bullet t_{CLF} - 3$ | _    |      |

| REQ Assertion Period     | t <sub>RQAP</sub> | 20                      | _    | ns   |

| REQ Negation Period      | t <sub>RNAP</sub> | 20                      | _    | 115  |

| REQ input cycle time (1) | t <sub>RQF1</sub> | 1t <sub>CLF</sub>       | _    |      |

| REQ input cycle time (2) | t <sub>RQF2</sub> | 3t <sub>CLF</sub>       | _    |      |

\*The values of A and N vary with the setting condition of the transfer period register (address 13).

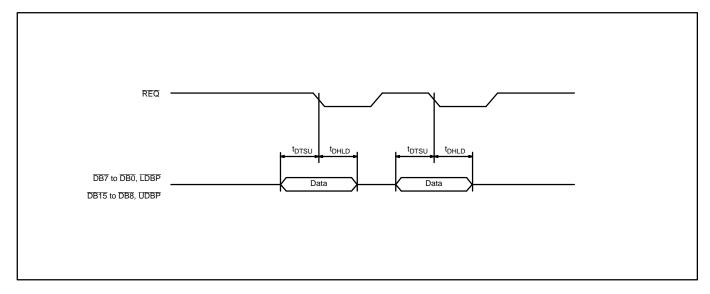

#### Input timing (target → initiator)

| Parameter                                                 |                   |      | nits | Unit  |

|-----------------------------------------------------------|-------------------|------|------|-------|

| Farameter                                                 | Symbol            | Min. | Max. | Offic |

| Data bus defined $\rightarrow \overline{REQ}$ set Low     | t <sub>DTSU</sub> | 10   | _    | nc    |

| $\overline{REQ}$ set Low $\rightarrow$ data bus hold time | t <sub>DHLD</sub> | 20   | _    | ns    |

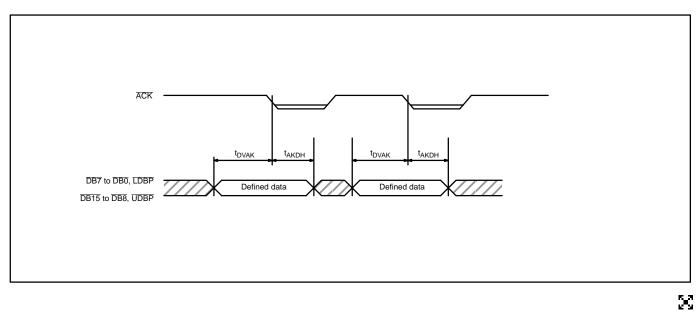

#### • Output timing (initiator $\rightarrow$ target)

| Parameter                                                         | Symbol            | Limits                 |      | Unit  |

|-------------------------------------------------------------------|-------------------|------------------------|------|-------|

| raiainetei                                                        | Symbol            | Min.                   | Max. | Offic |

| Data bus defined $\rightarrow \overline{ACK}$ set Low*            | t <sub>DVAK</sub> | N●t <sub>CLF</sub> – 5 | —    | ns    |

| $\overline{\text{ACK}}$ set Low $\rightarrow$ data bus hold time* | t <sub>AKDH</sub> | A●t <sub>CLF</sub> – 5 | _    | 115   |

\*The values of A and N vary with the setting condition of the transfer period register (address 13).

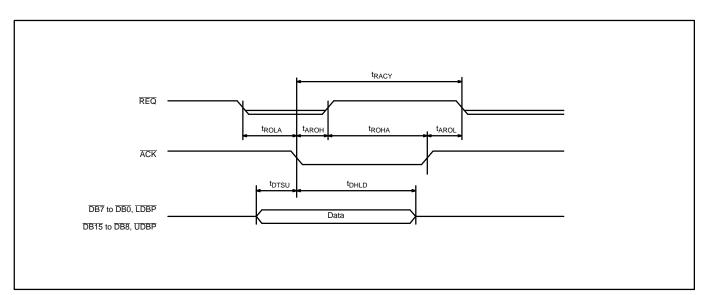

#### (7) SCSI Interface (Target)

#### [Asynchronous transfer mode]

Input timing (initiator → target)

| Parameter                                                                    | Symbol            | Lin  | Unit                   |      |

|------------------------------------------------------------------------------|-------------------|------|------------------------|------|

| Falanetei                                                                    | Symbol            | Min. | Max.                   | Onit |

| $\overline{REQ} \text{ set Low} \rightarrow \overline{ACK} \text{ set Low}$  | t <sub>RDLA</sub> | 0    | —                      |      |

| $\overline{\text{ACK}}$ set Low $\rightarrow \overline{\text{REQ}}$ set High | t <sub>AKOH</sub> | _    | 60                     |      |

| $\overline{REQ}$ set High $\rightarrow \overline{ACK}$ set Low               | t <sub>ROHA</sub> | 0    | —                      |      |

| Data bus defined $\rightarrow \overline{\text{ACK}}$ set Low                 | t <sub>VTSU</sub> | 10   | —                      | ns   |

| $\overline{\text{ACK}}$ set Low $\rightarrow$ data bus hold time             | <sup>t</sup> DHLD | 20   | —                      |      |

| $\overline{\text{ACK}}$ set High $\rightarrow \overline{\text{REQ}}$ set Low | t <sub>AROL</sub> | —    | 40                     |      |

| $\overline{ACK}$ set Low $\rightarrow \overline{REQ}$ set Low*               | t <sub>RACY</sub> | _    | 3t <sub>CLF</sub> + 40 |      |

\*The time ( $t_{RACY}$ ) of  $\overrightarrow{ACK}$  set Low  $\rightarrow \overrightarrow{REQ}$  set Low is set to the longer time compared with ( $t_{AROH} + t_{ROHA} + t_{AROL}$ ).

Note: The input timing regulations are not applicable when the data register is FULL in the data phase.

#### Output timing (target → initiator)

| Parameter                                                                    | Symbol            | Lin                     | nits | Unit  |

|------------------------------------------------------------------------------|-------------------|-------------------------|------|-------|

| Farameter                                                                    | Symbol            | Min.                    | Max. | Offic |

| $\overline{REQ}$ set Low $\rightarrow \overline{ACK}$ set Low                | t <sub>ROLA</sub> | 0                       | —    |       |

| $\overline{\text{ACK}}$ set Low $\rightarrow \overline{\text{REQ}}$ set High | t <sub>AROH</sub> | —                       | 60   |       |

| $\overline{REQ}$ set High $\rightarrow \overline{ACK}$ set High              | t <sub>ROHA</sub> | 0                       | _    | ns    |

| Data bus output defined $\rightarrow \overline{\text{REQ}}$ set Low*         | t <sub>DVLD</sub> | S●t <sub>CLF</sub> – 10 |      | 115   |

| $\overline{\text{ACK}}$ set Low $\rightarrow$ data bus hold time             | t <sub>DIVD</sub> | 2t <sub>CLF</sub>       | _    |       |

| $\overline{\text{ACK}}$ set High $\rightarrow \overline{\text{REQ}}$ set Low | t <sub>AROL</sub> | _                       | 40   |       |

\*The value of S varies with the setting condition of the asynchronous setup time register (address 23).

Note: The output timing regulations are not applicable when the data register is EMPTY in the data phase.

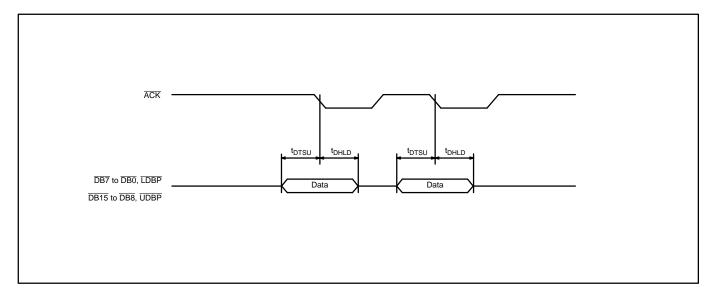

#### [Synchronous transfer mode]

• REQ/ACK signal synchronization

| Parameter                | Symbol            | Lin                     | Unit |      |

|--------------------------|-------------------|-------------------------|------|------|

| Falanetei                | Symbol            | Min.                    | Max. | Onit |

| REQ Assertion Period*    | t <sub>RQAP</sub> | A●t <sub>CLF</sub> – 3  | —    |      |

| REQ Negation Period*     | t <sub>RNAP</sub> | $N \bullet t_{CLF} - 3$ | —    |      |

| ACK Assertion Period     | t <sub>AKAP</sub> | 20                      | —    | ns   |

| ACK Negation Period      | t <sub>ANAP</sub> | 20                      | —    | 115  |

| ACK input cycle time (1) | t <sub>AKF1</sub> | 1t <sub>CLF</sub>       | _    |      |

| ACK input cycle time (2) | t <sub>AKF2</sub> | 3t <sub>CLF</sub>       | _    |      |

\*The values of A and N vary with the setting condition of the transfer period register (address 13).

#### Input timing (initiator → target)

| Parameter                                                        | Symbol            | Lin  | nits     | Unit |

|------------------------------------------------------------------|-------------------|------|----------|------|

| raiainetei                                                       | Symbol            | Min. | in. Max. |      |

| Data bus defined $\rightarrow \overline{ACK}$ set Low            | t <sub>dtsu</sub> | 10   | —        | ns   |

| $\overline{\text{ACK}}$ set Low $\rightarrow$ data bus hold time | t <sub>DHLD</sub> | 20   | _        | 115  |

#### ● Output timing (target → initiator)

| Parameter                                                     | Symbol            | Lin                    | nits | Unit |  |

|---------------------------------------------------------------|-------------------|------------------------|------|------|--|

| ralameter                                                     | Symbol            | Min.                   | Max. | Unit |  |