# 21143 PCI/CardBus 10/100 Ethernet LAN Controller

**Networking Silicon**

# **Preliminary Datasheet**

## **Product Features**

- Fully compliant with Revision 2.1 of the *PCI Local Bus Specification* and with Revision 1.0 of the *PCI Bus Power Management Interface Specification*.

- Fully compliant with Revision 1.0 of the Advanced Configuration and Power Interface (ACPI) Specification and with Revision 1.0 of the Network Device Class Power Management Specification, under the OnNow Architecture for Microsoft's PC 97 Hardware Design Guide and PC 98 System Design Guide.

- Supports IEEE 802.3 with full Auto-Negotiation algorithm of full-duplex and half-duplex operation for 10 Mb/s and 100 Mb/s (NWAY).

- Supports IEEE 802.3 and ANSI 8802-3 Ethernet standards.

- Supports direct memory access (DMA) and has direct interface to both the CardBus\* and PCI local bus.

- Provides glueless 32-bit PCI bus master interface.

- Contains large independent receive and transmit FIFOs.

- Contains internal PCS and scrambler/ descrambler for MII/SYM interface for 100BASE-TX.

- Contains onchip integrated AUI port and a 10BASE-T transceiver.

- Supports autodetection between 10BASE-T, AUI, and MII/SYM ports.

- Provides an upgradable boot ROM interface up to 256KB.

- Supports remote wake-up-LAN and Magic Packet\* with the SecureON<sup>TM</sup> password option.

- Supports PCI/CardBus clock speed frequency from dc to 33 MHz; network operation with PCI clock from 20 MHz to 33 MHz.

- Implements low-power management with two power-saving modes (sleep and snooze).

- Implements low-power, 3.3-V CMOS technology.

**Notice:** This document contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

Order Number: 278073-001 November 1998

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 21143 PCI/CardBus 10/100 Ethernet LAN Controller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

# **Contents**

| 1.0 | 21143 | OVERVIEW                                                          | 1  |

|-----|-------|-------------------------------------------------------------------|----|

|     | 1.1   | General Description                                               | 2  |

|     | 1.2   | Microarchitecture                                                 |    |

| 2.0 | PINOU | т                                                                 | 5  |

|     | 2.1   | Signal Reference Tables                                           | 7  |

|     | 2.2   | Signal Reference Tables                                           |    |

|     | 2.3   | Pin Tables                                                        |    |

|     | 2.4   | Signal Grouping by Function                                       |    |

| 3.0 | ELEC1 | TRICAL AND ENVIRONMENTAL SPECIFICATIONS                           | 19 |

|     | 3.1   | Voltage Limit Ratings                                             | 19 |

|     | 3.2   | Temperature Limit Ratings                                         | 19 |

|     | 3.3   | Power Specifications                                              | 20 |

|     | 3.4   | PCI Bus and CardBus Electrical Parameters                         | 20 |

|     |       | 3.4.1 PCI and CardBus I/O Voltage Specifications                  |    |

|     |       | 3.4.2 System Bus Reset                                            |    |

|     |       | 3.4.3 PCI and CardBus Clock Specifications                        |    |

|     |       | 3.4.4 Other PCI and CardBus Signals                               |    |

|     | 3.5   | AUI and Twisted-Pair DC Specifications                            |    |

|     | 3.6   | Serial Interface Attachment Specifications                        |    |

|     |       | 3.6.1 Serial Clock Timing                                         |    |

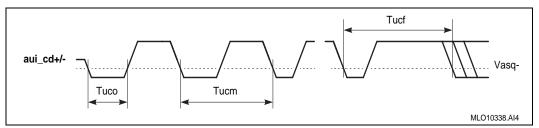

|     |       | 3.6.2 Internal SIA Mode AUI Timing—Transmit                       |    |

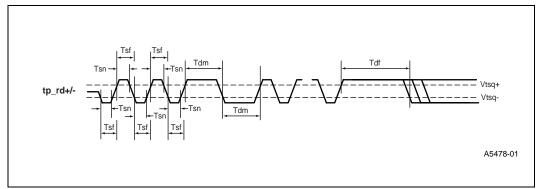

|     |       | 3.6.3 Internal SIA Mode AUI Timing—Receive                        |    |

|     |       | 3.6.5 Internal SIA Mode ADI Tirring—Collision                     |    |

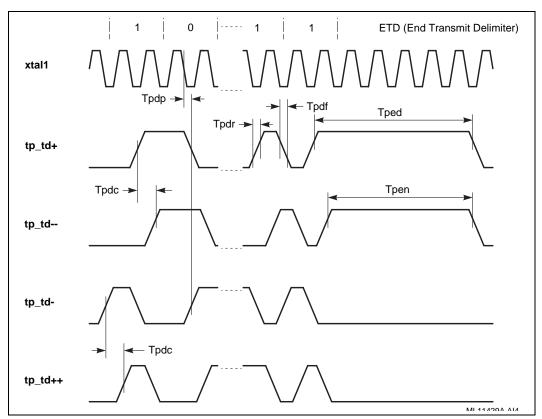

|     |       | 3.6.6 Internal SIA Mode 10BASE-T Interface Timing—Transmit        |    |

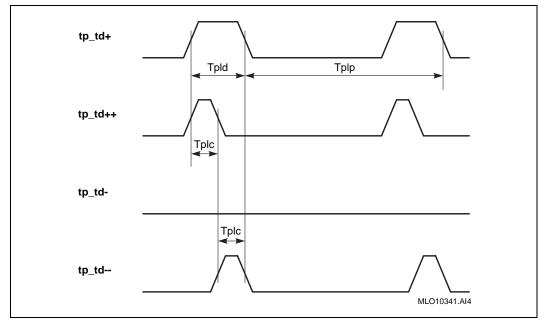

|     |       | 3.6.7 Internal SIA Mode 10BASE-T Interface Timing—Idle Link Pulse |    |

|     | 3.7   | MII Interface Specifications                                      |    |

|     | 3.8   | MII/SYM Port Timing                                               |    |

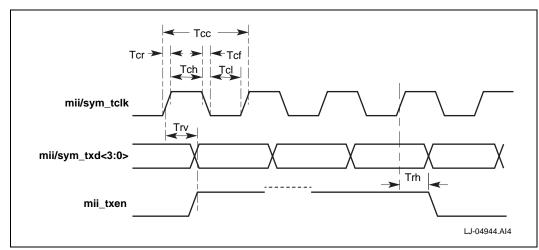

|     |       | 3.8.1 MII/SYM 10/100-Mb/s and 10-Mb/s Timing—Transmit             |    |

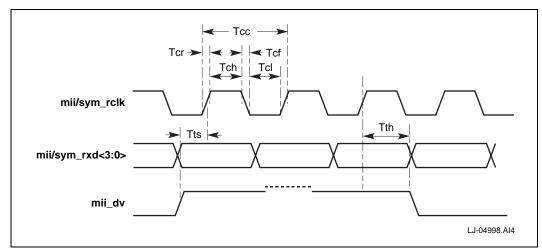

|     |       | 3.8.2 MII/SYM 10/100-Mb/s Timing—Receive                          |    |

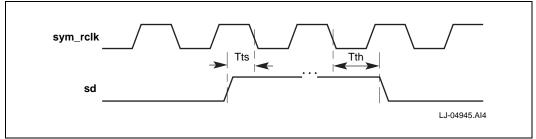

|     |       | 3.8.3 SYM 10/100-Mb/s Timing—Signal Detect                        |    |

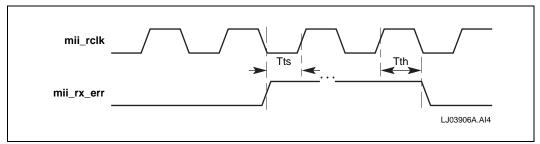

|     |       | 3.8.4 MII 10/100-Mb/s Timing—Receive Error                        | 35 |

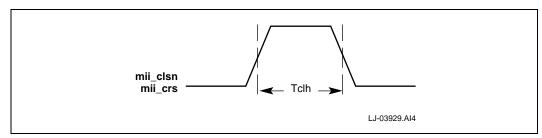

|     |       | 3.8.5 MII 10/100-Mb/s Timing—Carrier Sense and Collision          | 36 |

|     | 3.9   | Boot ROM and Serial ROM Port Specification                        |    |

|     | 3.10  |                                                                   | 37 |

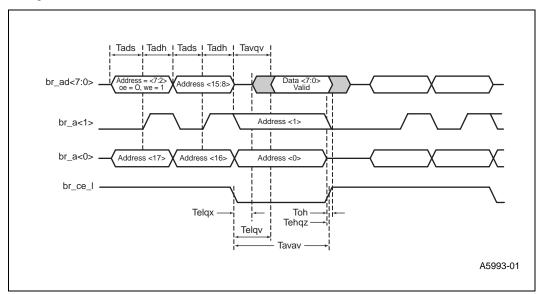

|     |       | 3.10.1 Boot ROM Read Timing                                       |    |

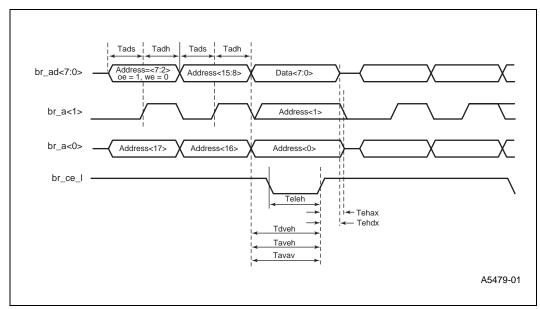

|     |       | 3.10.2 Boot ROM Write Timing                                      |    |

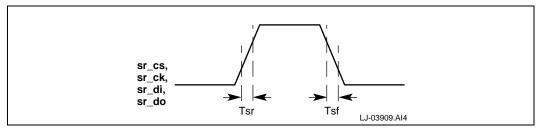

|     |       | Serial ROM Port Timing                                            |    |

|     |       | External Register Timing                                          |    |

|     | 3.13  | Joint Test Action Group—Test Access Port                          |    |

|     |       | 3.13.1 JTAG DC Specifications                                     |    |

|     |       | •                                                                 |    |

| 4.0 | MECH  | ANICAL SPECIFICATIONS                                             | 43 |

## 1.0 21143 Overview

The Intel 21143 PCI/CardBus\* 10/100-Mb/s Ethernet LAN Controller (21143) supports the peripheral component interconnect (PCI) bus or CardBus. It provides a direct interface connection to the PCI bus and adapts easily to the CardBus and most other standard buses. The 21143 software interface and data structures are optimized to minimize the host CPU load and to allow for maximum flexibility in the buffer descriptor management. The 21143 contains large onchip FIFOs, so no additional onboard memory is required. The 21143 also provides an upgradable boot ROM interface.

In addition to the features listed on the title pages, the following features are also supported by the 21143:

#### **PCI and CardBus Features:**

- Supports PCI and CardBus interfaces.

- Supports PCI/CardBus clock control through clkrun.

- Supports CardBus cstschg pin and Status Changed registers.

- Supports automatic loading of subvendor ID and CardBus card information structure (CIS) pointer from serial ROM to configuration registers.

- Supports storage of CardBus card information structure (CIS) in the serial ROM or the expansion ROM.

- Supports the advanced PCI/CardBus read multiple, read line, and write and invalidate commands.

- Supports an unlimited PCI/CardBus burst.

#### **Host Interface Features:**

- Includes a powerful onchip direct memory access (DMA) with programmable burst size, providing low CPU utilization.

- Supports early interrupt on transmit and receive.

- Supports interrupt mitigation on transmit and receive.

- Supports big or little endian byte ordering for buffers and descriptors.

- Implements unique, patented intelligent arbitration between DMA channels to minimize underflow and overflow.

- Contains large independent receive and transmit FIFOs.

#### **Network Side Features:**

- Supports three network ports: 10BASE-T (10 Mb/s), AUI (10 Mb/s), and MII/SYM (10/100 Mb/s).

- Contains a variety of flexible address filtering modes.

- Implements signal-detect filtering to avoid false detection of link with 100BASE-TX symbol interfaces.

- Enables automatic detection and correction of 10BASE-T receive polarity.

- Supports autodetection between 10BASE-T, AUI, and MII/SYM ports.

- Offers a unique, patented solution to Ethernet capture-effect problem.

- Supports full-duplex operation on both MII/SYM and 10BASE-T ports.

- Provides internal and external loopback capability on all network ports.

- Supports IEEE 802.3 and ANSI 8802-3 Ethernet standards.

#### **Other Features:**

- Provides MicroWire\* interface for serial ROM (1K and 4K EEPROM).

- Provides LED indications for various network activity.

- Implements test-access port (JTAG-compatible) with boundary-scan pins.

- Contains a 4-bit, general-purpose programmable register and corresponding I/O pins with the ability to generate interrupts from two general-purpose pins.

# 1.1 General Description

The 21143 is an Ethernet LAN controller for both 100-Mb/s and 10-Mb/s data rates, which provides a direct interface to the peripheral component interconnect (PCI) local bus or the CardBus. The 21143 interfaces to the host processor by using onchip command and status registers (CSRs) and a shared host memory area, set up mainly during initialization. This minimizes processor involvement in the 21143 operation during normal reception and transmission.

The 21143 is optimized for low power PCI/CardBus based systems and supports two types of power-management mechanisms. The main mechanism is based upon the OnNow architecture, which is required for PC 97 and PC 98. The alternative mechanism is based upon the older remote wake-up-LAN mechanism.

Large FIFOs allow the 21143 to efficiently operate in systems with longer latency periods. Bus traffic is also minimized by filtering out received runt frames and by automatically retransmitting collided frames without a repeated fetch from the host memory.

The 21143 provides three network ports: a 10BASE-T 10-Mb/s port, an attachment unit interface (AUI) 10-Mb/s port, and a media-independent/symbol interface (MII/SYM) 10/100-Mb/s port. The 10BASE-T port provides a direct Ethernet connection to the twisted-pair (TP) interface. The AUI port provides a direct Ethernet connection to the AUI.

The MII/SYM port supports two operational modes:

- MII mode—A full implementation of the MII standard

- SYM mode—Symbol interface to an external 100-Mb/s front-end decoder (ENDEC). In this mode the 21143 uses an onchip physical coding sublayer (PCS) and a scrambler/descrambler circuit to enable a low-cost 100BASE-T implementation.

The 21143 is capable of functioning in a full-duplex environment for the MII/SYM and 10BASE-T ports. The 21143 provides an upgradable boot ROM interface.

### 1.2 Microarchitecture

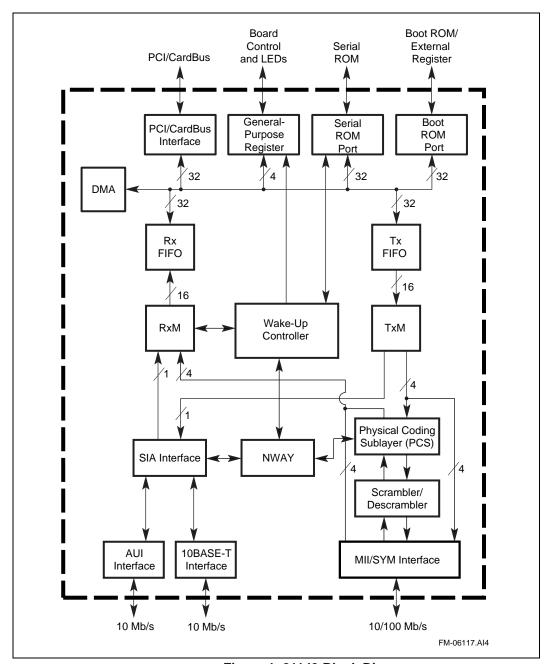

The following list describes the 21143 hardware components, and Figure 1 shows a block diagram of the 21143:

- PCI/CardBus interface—Includes all interface functions to the PCI and CardBus bus; handles

all interconnect control signals; and executes DMA and I/O transactions

- Boot ROM port—Provides an interface to perform read and write operations to the boot ROM; supports accesses to bytes or longwords (32-bit); and provides the ability to connect an external 8-bit register to the boot ROM port

- Serial ROM port—Provides a direct interface to a MicroWire ROM for storage of the Ethernet address and system parameters

- General-purpose register—Enables software use for input or output functions and LEDs

- DMA—Contains independent receive and transmit controllers; handles data transfers between CPU memory and onchip memory

- FIFOs—Contains independent FIFOs for receive and transmit; supports automatic packet deletion on receive (runt packets or after a collision) and packet retransmission after a collision on transmit

- TxM—Handles all CSMA/CD<sup>1</sup> MAC<sup>2</sup> transmit operations, and transfers data from transmit FIFO to the ENDEC for transmission

- RxM—Handles all CSMA/CD MAC receive operations, and transfers the network data from the ENDEC to the receive FIFO

- SIA interface—Performs 10-Mb/s physical layer network operations; implements the AUI and 10BASE-T functions, including the Manchester encoder and decoder functions

- NWAY—Implements the IEEE 802.3 Auto-Negotiation algorithm

- Physical coding sublayer—Implements the encoding and decoding sublayer of the 100BASE-TX (CAT5) specification, including the squelch feature

- Scrambler/descrambler—Implements the twisted-pair physical layer medium dependent (TP-PMD) scrambler/descrambler scheme for 100BASE-TX

- Three network interfaces—An AUI interface, a 10BASE-T interface, and an MII/SYM interface provide a full MII signal interface and direct interface to the 100-Mb/s ENDEC for CAT5

- Wake-up-controller—Enables power-management control compliant with the ACPI and remote power-up capabilities using the remote wake-up-LAN mechanism

<sup>1.</sup> Carrier-sense multiple access with collision detection.

Media access control.

Figure 1. 21143 Block Diagram

# 2.0 Pinout

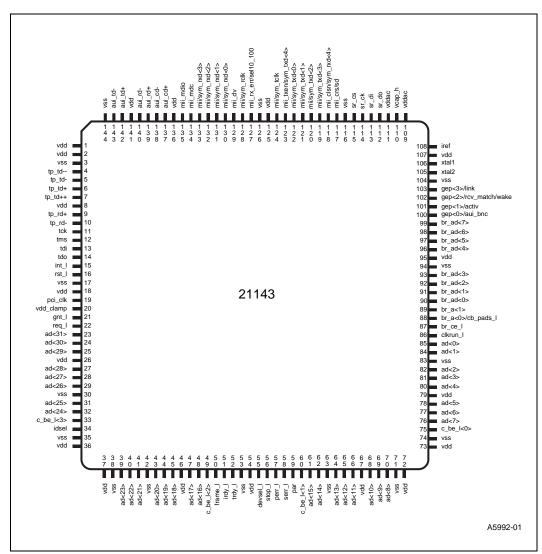

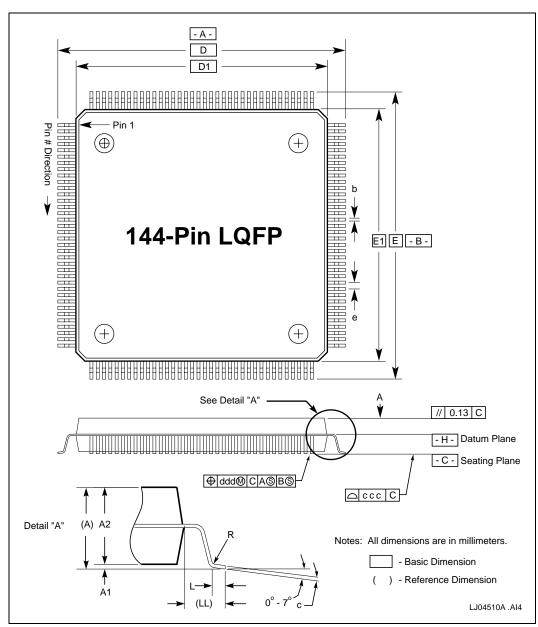

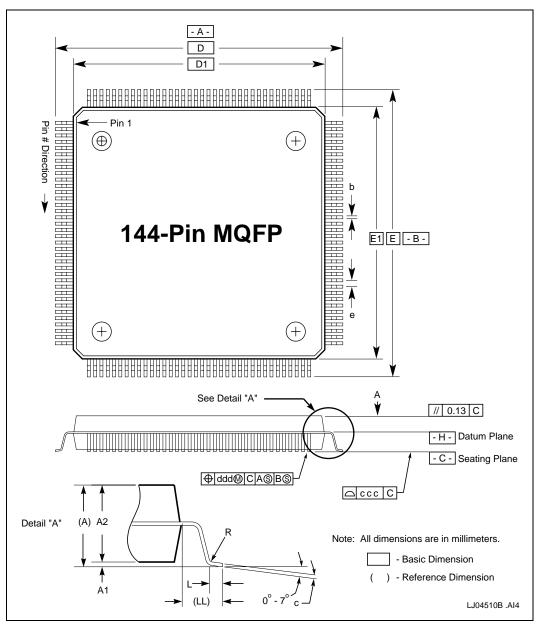

The 21143 is offered in two package styles: a 144-pin low-profile quad flat pack (LQFP) and a 144-pin metric quad flat pack (MQFP). The tables in this section provide a description of the pins and their respective signal definitions.

Table 1 lists the tables in this section. Figure 2 shows the 21143 pinout for both the LQFP and MQFP package types

**Table 1. Index to Pinout Tables**

| For this information           | Refer to |

|--------------------------------|----------|

| Logic signals                  | Table 2  |

| Power pins                     | Table 3  |

| Functional signals description | Table 4  |

| Input pins                     | Table 5  |

| Output pins                    | Table 6  |

| Input/output pins              | Table 7  |

| Open drain pins                | Table 8  |

| Signal functions               | Table 9  |

6

Figure 2. 21143 Pinout Diagram (Top View)

# 2.1 Signal Reference Tables

Table 2 provides an alphabetical list of the 21143 logic names and their pin numbers. Table 3 provides a list of the 21143 power pin numbers.

Table 2. Logic Signals (Sheet 1 of 2)

| Signal  | Pin<br>Number | Signal                        | Pin<br>Number | Signal               | Pin<br>Number |

|---------|---------------|-------------------------------|---------------|----------------------|---------------|

| ad<0>   | 85            | aui_rd-                       | 140           | mii_mdc              | 134           |

| ad<1>   | 84            | aui_rd+                       | 139           | mii_mdio             | 135           |

| ad<2>   | 82            | aui_td-                       | 143           | mii/sym_rclk         | 128           |

| ad<3>   | 81            | aui_td+                       | 142           | mii_rx_err/sel10_100 | 127           |

| ad<4>   | 80            | br_a<0>/<br>cb_pads_l         | 88            | mii/sym_rxd<0>       | 130           |

| ad<5>   | 78            | br_a<1>                       | 89            | mii/sym_rxd<1>       | 131           |

| ad<6>   | 77            | br_ad<0>                      | 90            | mii/sym_rxd<2>       | 132           |

| ad<7>   | 76            | br_ad<1>                      | 91            | mii/sym_rxd<3>       | 133           |

| ad<8>   | 70            | br_ad<2>                      | 92            | mii/sym_tclk         | 124           |

| ad<9>   | 69            | br_ad<3>                      | 93            | mii/sym_txd<0>       | 122           |

| ad<10>  | 68            | br_ad<4>                      | 96            | mii/sym_txd<1>       | 121           |

| ad<11>  | 66            | br_ad<5>                      | 97            | mii/sym_txd<2>       | 120           |

| ad<12>  | 65            | br_ad<6>                      | 98            | mii/sym_txd<3>       | 119           |

| ad<13>  | 64            | br_ad<7>                      | 99            | mii_txen/sym_txd<4>  | 123           |

| ad<14>  | 62            | br_ce_l                       | 87            | par                  | 59            |

| ad<15>  | 61            | c_be_l<0>                     | 75            | pci_clk              | 19            |

| ad<16>  | 48            | c_be_l<1>                     | 60            | perr_l               | 57            |

| ad<17>  | 47            | c_be_l<2>                     | 49            | req_I                | 22            |

| ad<18>  | 45            | c_be_l<3>                     | 33            | rst_l                | 16            |

| ad<19>  | 44            | clkrun_l                      | 86            | serr_l               | 58            |

| ad<20>  | 43            | devsel_l                      | 55            | sr_ck                | 114           |

| ad<21>  | 41            | frame_I                       | 50            | sr_cs                | 115           |

| ad<22>  | 40            | gep<0>/<br>aui_bnc            | 100           | sr_di                | 113           |

| ad<23>  | 39            | gep<1>/activ                  | 101           | sr_do                | 112           |

| ad<24>  | 32            | gep<2>/<br>rcv_match/<br>wake | 102           | stop_l               | 56            |

| ad<25>  | 31            | gep<3>/link                   | 103           | tck                  | 11            |

| ad<26>  | 29            | gnt_l                         | 21            | tdi                  | 13            |

| ad<27>  | 28            | idsel                         | 34            | tdo                  | 14            |

| ad<28>  | 27            | int_l                         | 15            | tms                  | 12            |

| ad<29>  | 25            | irdy_l                        | 51            | tp_rd-               | 10            |

| ad<30>  | 24            | iref                          | 108           | tp_rd+               | 9             |

| ad<31>  | 23            | mii_clsn/<br>sym_rxd<4>       | 118           | tp_td-               | 5             |

| aui_cd- | 138           | mii_crs/sd                    | 117           | tp_td                | 4             |

| _       |               |                               |               |                      |               |

| Signal   | Pin<br>Number | Signal | Pin<br>Number | Signal | Pin<br>Number |

|----------|---------------|--------|---------------|--------|---------------|

| tp_td+ + | 7             | trdy_l | 52            | vcap_h | 110           |

| xtal1    | 106           | xtal2  | 105           | _      | _             |

**Table 3. Power Pins**

| Signal                   | Pin Number                                                              | Signal    | Pin Number                                                                 |

|--------------------------|-------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------|

| vdd (3.3 V)              | 1, 2, 8, 18, 26, 36, 37, 46, 54, 67, 72, 73, 79, 95, 107, 125, 136, 141 | vss (GND) | 3, 17, 30, 35, 38,<br>42, 53, 63, 71, 74,<br>83, 94, 104, 116,<br>126, 144 |

| vddac (3.3 V)            | 109, 111                                                                | _         | _                                                                          |

| vdd_clamp (5 V or 3.3 V) | 20                                                                      | _         | _                                                                          |

# 2.2 Signal Reference Tables

The functional grouping of each pin is listed in Section 2.4.

The following terms describe the 21143 pinout:

· Address phase

Address and appropriate bus commands are driven during this cycle.

• Data phase

Data and the appropriate byte enable codes are driven during this cycle.

\_1

All pin names with the \_l suffix are asserted low.

The following pins in Table 4 have an internal pull-up:

tms tdi br\_ce\_l sr\_do mii/sym\_tclk

Pin sr\_cs has an internal pull-down.

Table 4 uses the following abbreviations:

I = Input O = Output I/O = Input/output O/D = Open drain P = Power

Table 4 provides a functional description of each of the 21143 signals. These signals are listed alphabetically.

Table 4. Functional Description of 21143 Signals (Sheet 1 of 6)

| Signal                | Туре       | Pin Number                                                                                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ad<31:0>              | I/O        | 23, 24, 25, 27,<br>28, 29, 31, 32,<br>39, 40, 41, 43,<br>44, 45, 47, 48,<br>61, 62, 64, 65,<br>66, 68, 69, 70,<br>76, 77, 78, 80,<br>81, 82, 84, 85 | 32-bit PCI address and data lines. Address and data bits are multiplexed on the same pins. During the first clock cycle of a transaction, the address bits contain a physical address (32 bits). During subsequent clock cycles, these same lines contain 32 bits of data. A 21143 bus transaction consists of an address phase followed by one or more data phases. The 21143 supports both read and write bursts (in master operation only). Little and big endian byte ordering can be used.                                          |

| aui_cd-               | I          | 138                                                                                                                                                 | Attachment unit interface receive collision differential negative data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| aui_cd+               | I          | 137                                                                                                                                                 | Attachment unit interface receive collision differential positive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| aui_rd-               | I          | 140                                                                                                                                                 | Attachment unit interface receive differential negative data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| aui_rd+               | I          | 139                                                                                                                                                 | Attachment unit interface receive differential positive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| aui_td-               | 0          | 143                                                                                                                                                 | Attachment unit interface transmit differential negative data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| aui_td+               | 0          | 142                                                                                                                                                 | Attachment unit interface transmit differential positive data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| br_a<0>/<br>cb_pads_l | 0          | 88                                                                                                                                                  | Boot ROM address line bit 0. In a 256KB configuration, this pin also carries in two consecutive address cycles, boot ROM address bits 16 and 17.  This pin also determines the type of signals to use for the PCI/ CardBus* output pins, either PCI or CardBus. By default, this pin selects PCI signaling. To select CardBus signaling, this pin must be connected to a pull-down resistor.                                                                                                                                             |

| br_a<1>               | 0          | 89                                                                                                                                                  | Boot ROM address line bit 1. This pin also latches the boot ROM address and control lines by the two external latches.                                                                                                                                                                                                                                                                                                                                                                                                                   |

| br_ad<7:0>            | I/O        | 90, 91, 92, 93,<br>96, 97, 98, 99                                                                                                                   | Boot ROM address and data multiplexed lines bits 7 through 0. In two consecutive address cycles, these lines contain the boot ROM address pins 7 through 2, oe_I and we_I in the first cycle; and these lines contain boot ROM address pins 15 through 8 in the second cycle. During the data cycle, bits 7 through 0 contain data.                                                                                                                                                                                                      |

| br_ce_l               | 0          | 87                                                                                                                                                  | Boot ROM or external register chip enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| c_be_l<3:0>           | 1/0        | 33, 49, 60, 75                                                                                                                                      | Bits 0 through 3 of the bus command and byte enable lines. Bus command and byte enable are multiplexed on the same PCI pins.  During the address phase of the transaction, these 4 bits provide the bus command.  During the data phase, these 4 bits provide the byte enable. The byte enable determines which byte lines carry valid data. For example, bit 0 applies to byte 0, and bit 3 applies to byte 3.                                                                                                                          |

| clkrun_l              | I/O<br>O/D | 86                                                                                                                                                  | PCI/CardBus clock run indication. The host system asserts this signal to indicate normal operation of the clock. The host system deasserts clkrun_I when the clock is going to be stopped or slowed down to a nonoperational frequency.  If the clock is needed by the 21143, the 21143 asserts clkrun_I, requesting normal clock operation to be maintained or restored. Otherwise, the 21143 allows the system to stop the clock. If this pin is not connected to the PCI/CardBus bus, it should be connected to a pull-down resistor. |

Table 4. Functional Description of 21143 Signals (Sheet 2 of 6)

| Signal                        | Туре | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| devsel_l                      | I/O  | 55         | Device select is asserted by the target of the current bus access. When the 21143 is the initiator of the current bus access, it expects the target to assert devsel_I within 5 bus cycles, confirming the access. If the target does not assert devsel_I within the required bus cycles, the 21143 aborts the cycle. To meet the timing requirements, the 21143 asserts this signal in a medium speed (within 2 bus cycles).                                                                                                                    |

| frame_I                       | I/O  | 50         | The frame_I signal is driven by the bus master to indicate the beginning and duration of an access. The frame_I signal asserts to indicate the beginning of a bus transaction. While frame_I is asserted, data transfers continue. The frame_I signal deasserts to indicate that the next data phase is the final data phase transaction.                                                                                                                                                                                                        |

|                               |      |            | This pin can be configured by software to be:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                               |      |            | <ul> <li>A general-purpose pin that performs either input or output<br/>functions. This general-purpose pin can provide an interrupt<br/>when functioning as an input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

| gep<0>/                       |      |            | A control pin that provides an AUI (10BASE5) or BNC (10BASE2) select line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| aui_bnc                       | I/O  | D 100      | This control pin is mainly used to enable the external BNC transceiver in 10BASE2 mode. When set, the 10BASE5 mode is selected. When reset, the 10BASE2 mode is selected.                                                                                                                                                                                                                                                                                                                                                                        |

|                               |      |            | NOTE: This control pin is internally forced to the aui_bnc function when the 21143 is in remote wake-up-LAN mode.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                               |      |            | This pin can be configured by software to be:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| gep<1>/activ                  | I/O  | 101        | <ul> <li>A general-purpose pin that performs either input or output<br/>functions. This general-purpose pin can provide an interrupt<br/>when functioning as an input.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                |

|                               |      |            | A status pin that provides an LED that indicates either receive or transmit activity.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                               |      |            | This pin can be configured by software to be:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                               |      |            | A general-purpose pin that performs either input or output functions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                               |      |            | A status pin that provides an LED that indicates a receive packet<br>has passed address recognition.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| gep<2>/<br>rcv_match/<br>wake | I/O  | 102        | If the PME_Enable bit (Funco_HwOptions<3>) in the serial ROM is set, this pin is forced to function as a wake-up event pin that can be connected to pin pme# of the PCI connector or pin cstschg of the CardBus connector. When the 21143 is in remote wake-up-LAN mode, this pin is used as an indicator that a Magic Packet* has been successfully detected. When this pin is in a wake function, bit MiscHwOptions<1> in the serial ROM determines the polarity. The PME function takes precedence over the Magic Packet indication function. |

|                               |      |            | This pin can be configured by software to be:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| gep<3>/link                   | I/O  | I/O 103    | <ul> <li>A general-purpose pin that performs either input or output<br/>functions. When configured as an input pin in OnNow mode, this<br/>pin functions as link status. When used with an MII PHY device,<br/>this pin should be connected to the MII PHY link indication pin<br/>(the 21143 interprets link-pass when this pin is high). This pin<br/>should not be left unconnected if it is configured as an input in<br/>D1, D2 or D3 power states.</li> </ul>                                                                              |

|                               |      |            | <ul> <li>A status pin that provides an LED to indicate:         <ul> <li>Network link integrity state for 10BASE-T or 100BASE-TX if</li> <li>Func1_Hw_Options&lt;8&gt; is cleared in the SROM.</li> <li>Both network activity and network link integrity state if</li> <li>Func1_Hw_Options&lt;8&gt; is set in the SROM.</li> </ul> </li> </ul>                                                                                                                                                                                                  |

Table 4. Functional Description of 21143 Signals (Sheet 3 of 6)

| Signal                   | Туре  | Pin Number | Description                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                               |

|--------------------------|-------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| gnt_l                    | I     | 21         | Bus grant asserts to indicate to the 21143 that access to the bus is granted.                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                               |

| idsel                    | I     | 34         | Initialization device select asserts to indicate that the host is issuing a configuration cycle to the 21143.                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                               |

| int_l                    | O/D   | 15         | Interrupt request asserts when one of the appropriate bits of CSR5 sets and causes an interrupt, provided that the corresponding mask bit in CSR7 is not asserted. Interrupt request deasserts by writing a 1 into the appropriate CSR5 bit.                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                               |

|                          |       |            | If more than one interrupt bit is asserted in CSR5 and the host does not clear all input bits, the 21143 deasserts int_l for one cycle to support edge-triggered systems.                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                               |

| iref                     | I     | 108        | Current reference input for the analog phase-locked loop logic.                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                               |

|                          |       |            | Initiator ready indicates the bus master's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                               |

| irdy_l                   | I/O   | 51         | A data phase is completed on any rising edge of the clock when both irdy_l and target ready trdy_l are asserted. Wait cycles are inserted until both irdy_l and trdy_l are asserted together.                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                               |

|                          |       |            | When the 21143 is the bus master, it asserts irdy_I during write operations to indicate that valid data is present on the 32-bit ad lines. During read operations, the 21143 asserts irdy_I to indicate that it is ready to accept data.                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                               |

|                          |       |            | In MII mode (CSR6<18>=1, CSR6<23>=0), this pin functions as the collision detect. When the external physical layer protocol (PHY) device detects a collision, it asserts this pin.                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                               |

| mii_clsn/<br>sym_rxd<4>  | .   1 | I          | 118                                                                                                                                                                                                                                                                                                                                                                                                                    | In SYM mode (CSR6<18>=1, CSR6<23>=1), this pin functions as receive data. This line along with the four receive lines (sym_rxd<3:0>) provides five parallel data lines in symbol form. This data is controlled by an external physical layer medium-dependent (PMD) device and should be synchronized to the sym_rclk signal. |

|                          |       | 447        | In MII mode this pin functions as the carrier sense and is asserted by the PHY when the media is active.                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                               |

| mii_crs/sd               | '     | 117        | In SYM mode this pin functions as the signal detect indication. It is controlled by an external PMD device.                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                               |

| mii_dv                   | I     | 129        | Data valid is asserted by an external PHY when receive data is present on the mii_rxd lines and is deasserted at the end of the packet. This signal should be synchronized with the mii_rclk signal.                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                               |

| mii_mdc                  | 0     | 134        | MII management data clock is sourced by the 21143 to the PHY devices as a timing reference for the transfer of information on the mii_mdio signal.                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                               |

| mii_mdio                 | I/O   | 135        | MII management data input/output transfers control information and status between the PHY and the 21143.                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                               |

| mii/sym_rclk             | I     | 128        | Supports either the 25-MHz or 2.5-MHz receive clock. This clock is recovered by the PHY.                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                               |

| mii_rx_err/<br>sel10_100 | I/O   | 127        | When used with an MII PHY device (CSR6<18>=1, CSR6<23>=0), this pin functions as receive error input. It is asserted when a data decoding error is detected by an external PHY device. This signal is synchronized to mii_rclk and can be asserted for a minimum of one receive clock. When asserted during a packet reception, it sets the cyclic redundancy check (CRC) error bit in the receive descriptor (RDES0). |                                                                                                                                                                                                                                                                                                                               |

|                          |       |            | When used with a SYM PHY device (CSR6<23>=1), this pin functions as select 10/100 output. The signal sel10_100 equals 1 when the 21143 is in 100-Mb/s SYM mode (CSR6<18>=1) and equals 0 when the 21143 is in 10BASE-T/AUI mode (CSR6<18>=0).                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                               |

Table 4. Functional Description of 21143 Signals (Sheet 4 of 6)

| Signal               | Туре | Pin Number            | Description                                                                                                                                                                                                                                                                                                                    |

|----------------------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| mii/<br>sym_rxd<3:0> | I    | 130, 131,<br>132,133, | Four parallel receive data lines. This data is driven by an external PHY that attached the media and should be synchronized with the mii_rclk signal.                                                                                                                                                                          |

| mii/sym_tclk         | 1    | 124                   | Supports the 25-MHz or 2.5-MHz transmit clock supplied by the external PMD device. This clock should always be active.                                                                                                                                                                                                         |

| mii/<br>sym_txd<3:0> | 0    | 119, 120, 121,<br>122 | Four parallel transmit data lines. This data is synchronized to the assertion of the mii_tclk signal and is latched by the external PHY on the rising edge of the mii_tclk signal.                                                                                                                                             |

| mii_txen/            |      |                       | In MII mode (CSR6<18>=1, CSR6<23>=0), this pin functions as transmit enable. It indicates that a transmission is active on the MII port to an external PHY device.                                                                                                                                                             |

| sym_txd<4>           | 0    | 123                   | In SYM mode, this pin functions as transmit data. This line along with the four data transmit lines (sym_txd<3:0>) provides five parallel data lines in symbol form. The data is synchronized to the rising edge of the sym_tclk signal.                                                                                       |

|                      |      |                       | Parity is calculated by the 21143 as an even parity bit for the 32-bit ad and 4-bit c_be_I lines.                                                                                                                                                                                                                              |

| par                  | I/O  | 59                    | During address and data phases, parity is calculated on all the ad and c_be_l lines whether or not any of these lines carry meaningful information.                                                                                                                                                                            |

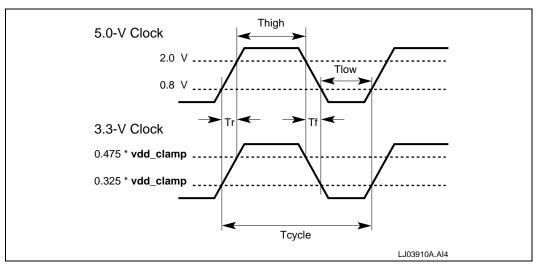

| pci_clk              | I    | 19                    | The clock provides the timing for the 21143 related PCI bus transactions. All the bus signals are sampled on the rising edge of pci_clk. The supported range of the clock frequency is 20 MHz to 33 MHz.                                                                                                                       |

|                      |      |                       | Parity error asserts when a data parity error is detected.                                                                                                                                                                                                                                                                     |

|                      |      |                       | The 21143 asserts perr_l when a data parity error is detected in either a master-read or a slave-write operation.                                                                                                                                                                                                              |

| perr_I               | I/O  | 57                    | When the 21143 is the bus master and a parity error is detected, the 21143 asserts both CSR5 bit 13 (fatal bus error) and CFCS bit 24 (data parity report). Next, it completes the current data burst transaction, then stops operation. After the host clears the fatal error bit in CSR5, the 21143 continues its operation. |

| req_l                | 0    | 22                    | Bus request is asserted by the 21143 to indicate to the bus arbiter that it wants to use the bus.                                                                                                                                                                                                                              |

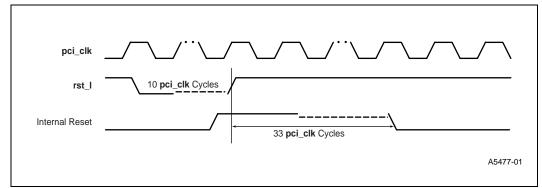

| rst_l                | I    | 16                    | Resets the 21143 to its initial state. This signal must be asserted for at least 10 active PCI clock cycles. When in the reset state, all PCI output pins are put into tristate and all PCI O/D signals are floated.                                                                                                           |

| serr_l               | O/D  | 58                    | If an address parity error is detected and CFCS bit 8 (serr_l enable) is enabled, 21143 asserts both serr_l (system error) and CFCS bit 30 (signal system error).                                                                                                                                                              |

|                      |      |                       | When an address parity error is detected, system error asserts two clocks after the failing address.                                                                                                                                                                                                                           |

| sr_ck                | 0    | 114                   | Serial ROM clock signal. This pin provides a serial clock output for the serial ROM.                                                                                                                                                                                                                                           |

| sr_cs                | 0    | 115                   | Serial ROM chip-select signal. This pin provides a chip select for the serial ROM.                                                                                                                                                                                                                                             |

| sr_di                | 0    | 113                   | Serial ROM data-in signal. This pin serially shifts the write data from the 21143 to the serial ROM device.                                                                                                                                                                                                                    |

| sr_do                | 1    | 112                   | Serial ROM data-out signal. This pin serially shifts the read data from the serial ROM device to the 21143.                                                                                                                                                                                                                    |

Table 4. Functional Description of 21143 Signals (Sheet 5 of 6)

| Signal             | Туре | Pin Number                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------|------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| stop_l             | I/O  | 56                                                                                  | Stop indicator indicates that the current target is requesting the bus master to stop the current transaction.  The 21143 responds to the assertion of stop_I when it is the bus master, either to disconnect, retry, or abort.                                                                                                                                                                                                                                                                                        |

| tck                | ı    | 11                                                                                  | JTAG clock shifts state information and test data into and out of the 21143 during JTAG test operations.                                                                                                                                                                                                                                                                                                                                                                                                               |

|                    |      |                                                                                     | If the JTAG port is unused, this pin should be connected to vss.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| tdi                | I    | 13                                                                                  | JTAG data in is used to serially shift test data and instructions into the 21143 during JTAG test operations.                                                                                                                                                                                                                                                                                                                                                                                                          |

| tdo                | 0    | 14                                                                                  | JTAG data out is used to serially shift test data out of the 21143 during JTAG test operations.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| tms                | ı    | 12                                                                                  | JTAG test mode select controls the state operation of JTAG testing in the 21143.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| tp_rd-             | I    | 10                                                                                  | Twisted-pair negative differential receive data from the twisted-pair lines.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| tp_rd+             | I    | 9                                                                                   | Twisted-pair positive differential receive data from the twisted-pair lines.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| tp_td-<br>tp_td    | 0    | 5<br>4                                                                              | Twisted-pair negative differential transmit data. The positive and negative differential transmit data outputs are combined resistively outside the 21143 with equalization to compensate for intersymbol interference on the twisted-pair medium.                                                                                                                                                                                                                                                                     |

| tp_td+<br>tp_td+ + | 0    | 6<br>7                                                                              | Twisted-pair positive differential transmit data. The positive and negative differential transmit data outputs are combined resistively outside the 21143 with equalization to compensate for intersymbol interference on the twisted-pair medium.                                                                                                                                                                                                                                                                     |

| trdy_l             | I/O  | 52                                                                                  | Target ready indicates the target agent's ability to complete the current data phase of the transaction.  A data phase is completed on any clock when both trdy_I and irdy_I are asserted. Wait cycles are inserted until both irdy_I and trdy_I are asserted together.  When the 21143 is the bus master, target ready is asserted by the bus slave on the read operation, which indicates that valid data is present on the ad lines. During a write cycle, it indicates that the target is prepared to accept data. |

| vcap_h             | I    | 110                                                                                 | Capacitor input for analog phase-locked loop logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| vdd                | Р    | 1, 2, 8, 18, 26,<br>36, 37, 46, 54,<br>67, 72, 73, 79,<br>95, 107, 125,<br>136, 141 | 3.3-V supply input. These pins should be connected to the auxiliary power, if such power exists. Otherwise, these pins should be connected to the main power.                                                                                                                                                                                                                                                                                                                                                          |

| vddac              | Р    | 109, 111                                                                            | Supplies +3.3-V input for analog phase-locked loop logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

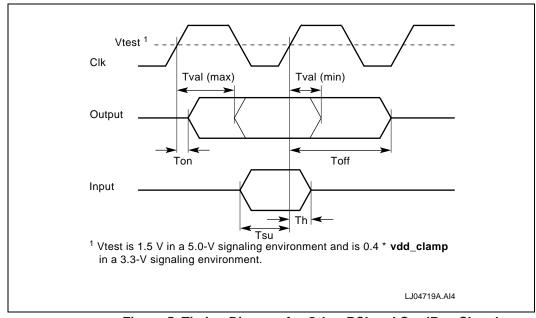

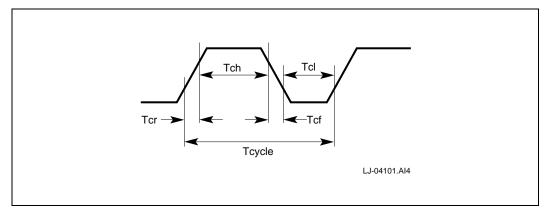

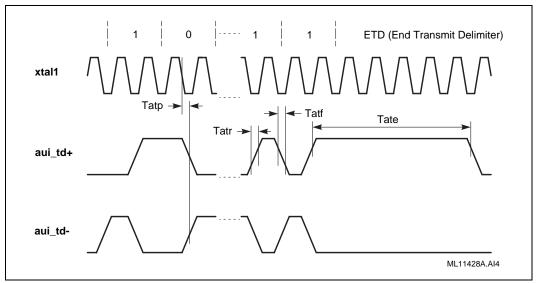

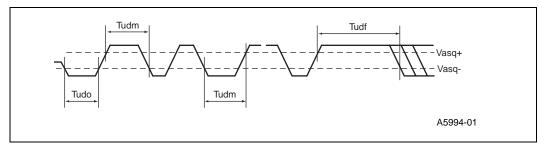

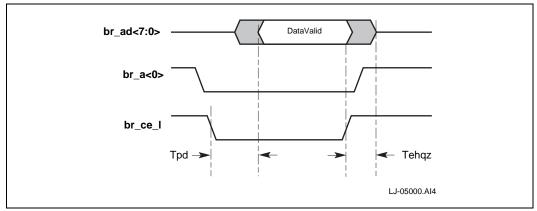

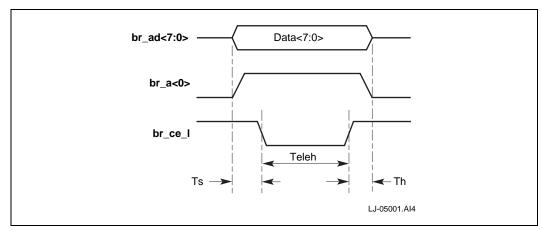

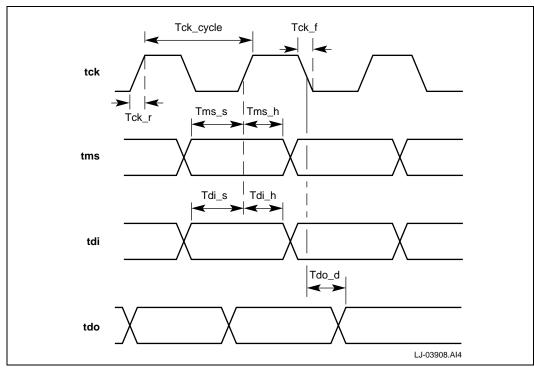

|                    |      |                                                                                     | Supplies +5-V or +3.3-V reference for clamp logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |