# W83697SF WINBOND I/O

## **W83697SF Data Sheet Revision History**

|    | Pages | Dates    | Version | Version | Main Contents          |

|----|-------|----------|---------|---------|------------------------|

|    |       |          |         | on Web  |                        |

| 1  | n.a.  | 04/16/01 | 0.50    | 0.50    | First published        |

| 2  | 111   | 04/27/01 | 0.51    | 0.51    | Update the Top Marking |

| 3  |       | 12/16/02 | 1.0     | 1.0     | New Update             |

| 4  |       |          |         |         |                        |

| 5  |       |          |         |         |                        |

| 6  |       |          |         |         |                        |

| 7  |       |          |         |         |                        |

| 8  |       |          |         |         |                        |

| 9  |       |          |         |         |                        |

| 10 |       |          |         |         |                        |

Please note that all data and specifications are subject to change without notice. All the trade marks of products and companies mentioned in this data sheet belong to their respective owners.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.

## **TABLE OF CONTENT**

| GENERAL DESCRIPTION                                                                      | 1  |

|------------------------------------------------------------------------------------------|----|

| PIN CONFIGURATION FOR 697SF                                                              | 6  |

| 1. PIN DESCRIPTION                                                                       | 7  |

| 1.1 LPC INTERFACE                                                                        | 9  |

| 1.2 FDC INTERFACE                                                                        | 9  |

| 1.3 MULTI-MODE PARALLEL PORT                                                             | 11 |

| 1.4 SERIAL PORT INTERFACE                                                                | 16 |

| 1.5 INFRARED PORT                                                                        |    |

| 1.6 FLASH ROM INTERFACE                                                                  |    |

| 1.7 GENERAL PURPOSE I/O PORT                                                             |    |

| 1.8 SMART CARD INTERFACE                                                                 |    |

| 1.9 PWM & GENERAL PURPOSE I/O PORT 8                                                     |    |

| 1.10 GAME PORT & MIDI PORT.                                                              |    |

| 1.11 POWER PINS                                                                          | 20 |

| 2. SMART CARD READER INTERFACE (SCR)                                                     | 21 |

| 2.1 FEATURES                                                                             | 21 |

| 2.2 REGISTER FILE                                                                        | 22 |

| 2.3 SMART CARD ID NUMBER (BASE ADDRESS + 2 WHEN BDLAB = 1, FIXED AT 70H)                 |    |

| 2.4 FUNCTIONAL DESCRIPTION                                                               |    |

| 2.5 INITIALIZATION                                                                       |    |

| 2.6 ACTIVATION.                                                                          |    |

| 2.7 ANSWER-TO-RESET                                                                      |    |

| 2.8 DATA TRANSFER                                                                        |    |

| 2.9 COLD RESET AND WARM RESET                                                            |    |

| 2.10 POWER STATES                                                                        |    |

| 2.11 DISABLED STATE                                                                      |    |

| 2.12 ACTIVE STATE                                                                        |    |

| 2.13 IDLE STATE                                                                          |    |

| 2.14 POWER DOWN STATE                                                                    | 41 |

| 3. CONFIGURATION REGISTER                                                                | 42 |

| 3.1 PLUG AND PLAY CONFIGURATION                                                          |    |

| 3.2 COMPATIBLE PNP                                                                       |    |

| 3.2.1 Extended Function Registers                                                        |    |

| 3.2.2 Extended Functions Enable Registers (EFERs)                                        |    |

| 3.2.3 Extended Function Index Registers (EFIRs), Extended Function Data Registers(EFDRs) |    |

| 3.3 CONFIGURATION SEQUENCE                                                               | 43 |

# W83697SF

| 3.3.1 Enter the extended function mode             | 43 |

|----------------------------------------------------|----|

| 3.3.2 Configurate the configuration registers      | 43 |

| 3.3.3 Exit the extended function mode              |    |

| 3.3.4 Software programming example                 | 44 |

| 3.4 CHIP (GLOBAL) CONTROL REGISTER                 |    |

| 3.5 LOGICAL DEVICE 0 (FDC)                         | 51 |

| 3.6 LOGICAL DEVICE 1 (PARALLEL PORT)               | 55 |

| 3.7 LOGICAL DEVICE 2 (UART A)                      | 56 |

| 3.8 LOGICAL DEVICE 3 (UART B)                      |    |

| 3.9 LOGICAL DEVICE 7 (GAME PORT AND GPIO PORT 1)   |    |

| 3.10 LOGICAL DEVICE 8 (MIDI PORT AND GPIO PORT 5)  |    |

| 3.11 LOGICAL DEVICE 9 (GPIO PORT 2 ~ GPIO PORT 4 ) |    |

| 3.12 LOGICAL DEVICE A (ACPI)                       |    |

| 3.13 LOGICAL DEVICE B (PWM)                        |    |

| 3.14 LOGICAL DEVICE C (SMART CARD)                 |    |

| 3.15 LOGICAL DEVICE D (GPIO PORT 6)                |    |

| 3.16 LOGICAL DEVICE E (GPIO PORT 7)                |    |

| 3.17 LOGICAL DEVICE F (GPIO PORT 8)                | 72 |

| 4. SPECIFICATIONS                                  | 74 |

| 4.1 ABSOLUTE MAXIMUM RATINGS                       | 74 |

| 4.2 DC CHARACTERISTICS                             |    |

| 5. APPLICATION CIRCUITS                            |    |

|                                                    |    |

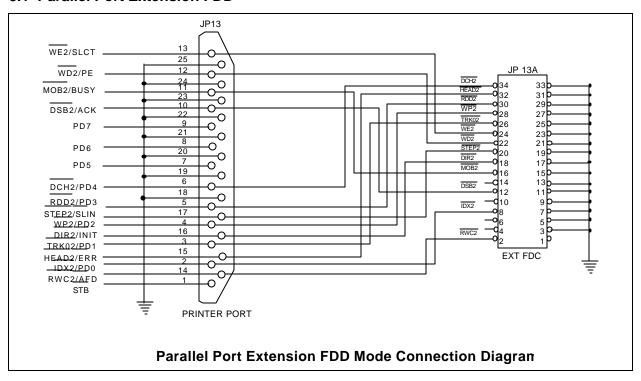

| 5.1 PARALLEL PORT EXTENSION FDD.                   | _  |

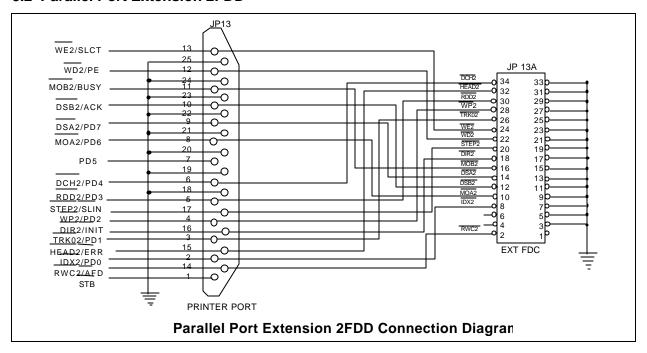

| 5.2 PARALLEL PORT EXTENSION 2FDD                   |    |

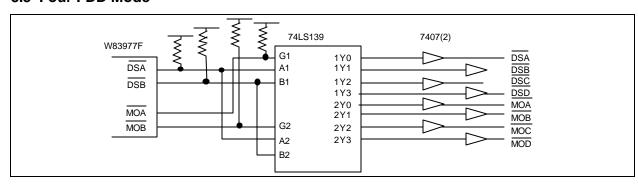

| 5.3 FOUR FDD MODE                                  | 83 |

| 6. ORDERING INSTRUCTION                            | 84 |

| 7. HOW TO READ THE TOP MARKING                     | 84 |

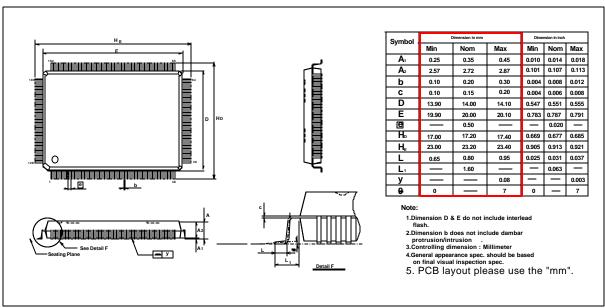

| 8. PACKAGE DIMENSIONS                              | 85 |

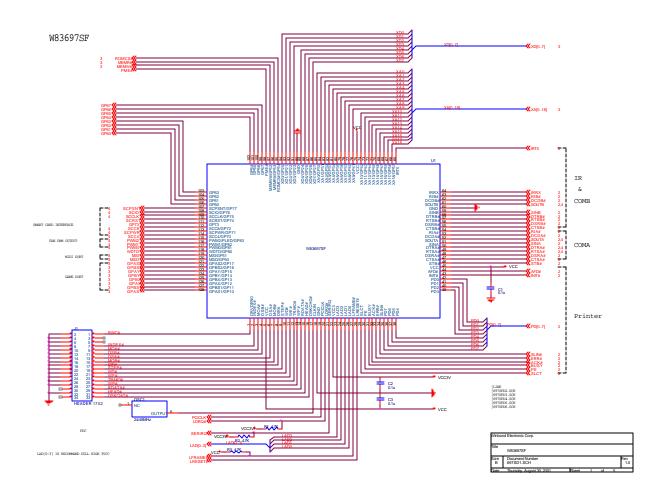

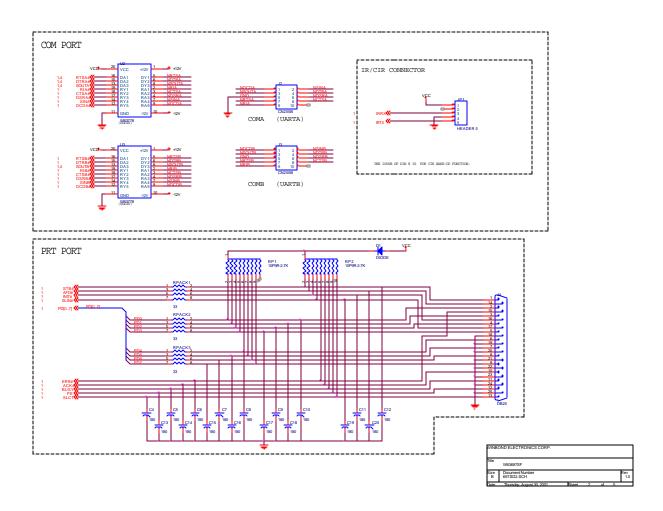

| APPENDIX A · DEMO CIRCUIT                          | 86 |

|                                                    |    |

#### **GENERAL DESCRIPTION**

The W83697SF is evolving product from Winbond's most popular I/O family. They feature a whole new interface, namely LPC (Low Pin Count) interface, which will be supported in the new generation chipset. This interface as its name suggests is to provide an economical implementation of I/O's interface with lower pin count and still maintains equivalent performance as its ISA interface counterpart. Approximately 40 pin counts are saved in LPC I/O comparing to ISA implementation. With this additional freedom, we can implement more devices on a single chip as demonstrated in W83697SF's integration of Game Port and MIDI Port. It is fully transparent in terms of software which means no BIOS or device driver update is needed except chip-specific configuration.

As Smart Card application is gaining more and more attention, W83697SF also implements a smart card reader interface featuring Smart wake-up function. This smart card reader interface fully meets the ISO7816 and PC/SC (Personal @mputer/Smart Card Workgroup) standards. W83697SF provides a minimum external components and lowest cost solution for smart card applications.

The disk drive adapter functions of W83697SF include a floppy disk drive controller compatible with the industry standard 82077/ 765, data separator, write pre-compensation circuit, decode logic, data rate selection, clock generator, drive interface control logic, and interrupt and DMA logic. The wide range of functions integrated onto the W83697SF greatly reduces the number of components required for interfacing with floppy disk drives. The W83697SF supports four 360K, 720K, 1.2M, 1.44M, or 2.88M disk drives and data tranSFer rates of 250 Kb/s, 300 Kb/s, 500 Kb/s, 1 Mb/s, and 2 Mb/s.

The W83697SF provides two high-speed serial communication ports (UARTs), one of which supports serial Infrared communication. Each UART includes a 16-byte send/receive FIFO, a programmable baud rate generator, complete modem control capability, and a processor interrupt system. Both UARTs provide legacy speed with baud rate up to 115.2k bps and also advanced speed with baud rates of 230k, 460k, or 921k bps which support higher speed modems. In addition, the W83697SF provides IR functions: IrDA 1.0 (SIR for 1.152K bps) and TV remote IR (Consumer IR, supporting NEC, RC-5, extended RC-5, and RECS-80 protocols).

The W83697SF supports one PC-compatible printer port (SPP), Bi-directional Printer port (BPP) and also Enhanced Parallel Port (EPP) and Extended Capabilities Port (ECP). Through the printer port interface pins, also available are: Extension FDD Mode and Extension 2FDD Mode allowing one or two external floppy disk drives to be connected.

The configuration registers support mode selection, function enable/disable, and power down function selection. Furthermore, the configurable PnP features are compatible with the plug-and-play feature demand of Windows 95/98<sup>TM</sup>, which makes system resource allocation more efficient than ever.

The W83697SF provides a set of flexible I/O control functions to the system designer through a set of General Purpose I/O ports. These GPIO ports may serve as simple I/O or may be individually configured

to provide a predefined alternate function. General Purpose Port 1 is designed to be functional even in power down mode (VCC is off).

The W83697SF is made to fully comply with Microsoft<sup>a</sup> PC98 and PC99 Hardware Design Guide, and meet the requirements of ACPI.

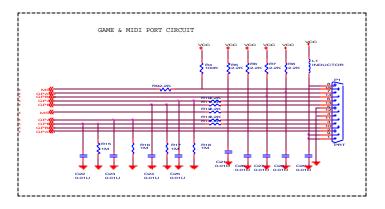

The W83697SF contains a game port and a MIDI port. The game port is designed to support 2 joysticks and can be applied to all standard PC game control devices, They are very important for a entertainment or consumer computer.

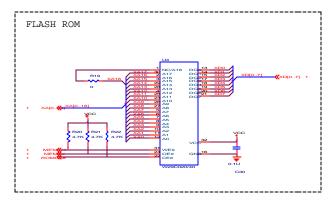

The W83697SF provides Flash ROM interface. That can support up to 4M legacy flash ROM.

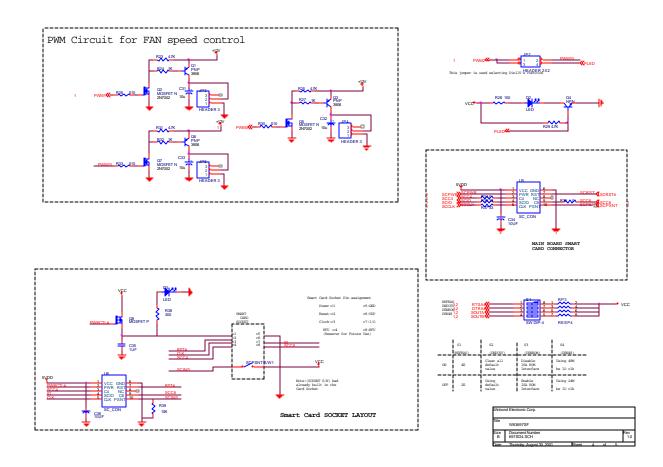

**Moreover, W83697SF support 3 sets PWM Fan Speed Control,** which are very important for a highend computer system to work stably and properly.

#### **FEATURES**

#### General

- Meet LPC Spec. 1.1

- Support LDRQ#(LPC DMA), SERIRQ (serial IRQ)

- Include all the features of Winbond I/O W83877TF

- Integrate Smart Card functions

- Compliant with Microsoft PC98/PC99 Hardware Design Guide

- Support DPM (Device Power Management), ACPI

- Programmable configuration settings

- Single 24 or 48 MHz clock input

#### **FDC**

- Compatible with IBM PC AT disk drive systems

- Variable write pre-compensation with track selectable capability

- Support vertical recording format

- DMA enable logic

- 16-byte data FIFOs

- Support floppy disk drives and tape drives

- Detects all overrun and underrun conditions

- Built-in address mark detection circuit to simplify the read electronics

- FDD anti-virus functions with software write protect and FDD write enable signal (write data signal was forced to be inactive)

- Support up to four 3.5-inch or 5.25-inch floppy disk drives

- Completely compatible with industry standard 82077

- 360K/720K/1.2M/1.44M/2.88M format; 250K, 300K, 500K, 1M, 2M bps data transfer rate

- Support 3-mode FDD, and its Win95/98 driver

#### **UART**

- Two high-speed 16550 compatible UARTs with 16-byte send/receive FIFOs

- MIDI compatible

- Fully programmable serial-interface characteristics:

- --- 5, 6, 7 or 8-bit characters

- --- Even, odd or no parity bit generation/detection

- --- 1, 1.5 or 2 stop bits generation

- Internal diagnostic capabilities:

- --- Loop-back controls for communications link fault isolation

- --- Break, parity, overrun, framing error simulation

- Programmable baud generator allows division of 1.8461 MHz and 24 MHz by 1 to (2<sup>16</sup>-1)

- Maximum baud rate up to 921k bps for 14.769 MHz and 1.5M bps for 24 MHz

#### Infrared

- Support IrDA version 1.0 SIR protocol with maximum baud rate up to 115.2K bps

- Support SHARP ASK-IR protocol with maximum baud rate up to 57,600 bps

- Support Consumer IR with Wake-Up function.

#### **Parallel Port**

- Compatible with IBM parallel port

- Support PS/2 compatible bi-directional parallel port

- Support Enhanced Parallel Port (EPP) Compatible with IEEE 1284 specification

- Support Extended Capabilities Port (ECP) Compatible with IEEE 1284 specification

- Extension FDD mode supports disk drive B; and Extension 2FDD mode supports disk drives A and B through parallel port

- Enhanced printer port back-drive current protection

#### **Game Port**

- Support two separate Joysticks

- Support every Joystick two axes (X,Y) and two buttons (S1,S2) controllers

#### **MIDI Port**

- The baud rate is 31.25 Kbaud

- 16-byte input FIFO

- 16-byte output FIFO

#### Flash ROM Interface

Support up to 4M flash ROM

#### **General Purpose I/O Ports**

- 60 programmable general purpose I/O ports

- General purpose I/O ports can serve as simple I/O ports, watch dog timer output, power LED output, infrared I/O pins, suspend LED output, Beep output

- Functional in power down mode

#### **Smart Card Reader Interface**

- ISO7816 protocol compliant

- PC/SC T=0, T=1 compliant

#### **Fan Speed Control**

3 Sets PWM Fan Speed Control

#### **Package**

128-pin PQFP

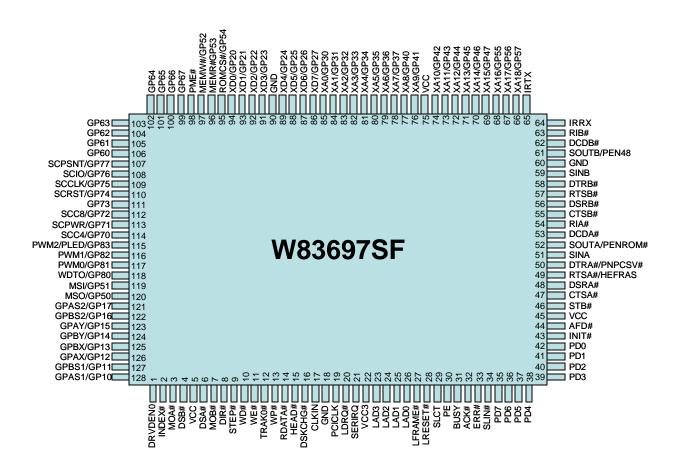

#### **PIN CONFIGURATION FOR 697SF**

## 1. PIN DESCRIPTION

Note: Please refer to Section 10.2 DC CHARACTERISTICS for details

| PIN DESCRIPTION                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------|

| TTL level bi-directional pin with 8mA source-sink capability                                                                   |

| TTL level bi-directional pin with 12mA source-sink capability                                                                  |

| TTL level bi-directional pin with 24 mA source-sink capability                                                                 |

| 3.3V TTL level bi-directional pin with 12mA source-sink capability                                                             |

| TTL level Schmitt-trigger bi-directional pin with 12mA source-sink capability                                                  |

| TTL level Schmitt-trigger bi-directional pin with 24mA source-sink capability                                                  |

| 3.3V TTL level Schmitt-trigger bi-directional pin with 24mA source-sink capability                                             |

| TTL level bi-directional pin and open-drain output with 12mA sink capability                                                   |

| TTL level bi-directional pin and open-drain output with 24mA sink capability                                                   |

| CMOS level bi-directional pin and open-drain output with 24mA sink capability                                                  |

| Bi-directional pin with analog input and open-drain output with 24mA sink capability                                           |

| TTL level Schmitt-trigger bi-directional pin and open-drain output with 12mA sink capability                                   |

| TTL level Schmitt-trigger bi-directional pin and open-drain output with 24mA sink capability                                   |

| CMOS level Schmitt-trigger bi-directional pin and open-drain output with 12mA sink capability                                  |

| CMOS level Schmitt-trigger bi-directional pin and open-drain output with 16mA sink capability                                  |

| CMOS level Schmitt-trigger bi-directional pin and open-drain output with 24mA sink capability                                  |

| CMOS level Schmitt-trigger bi-directional pin with internal pull down resistor and open-drain output with 12mA sink capability |

| CMOS level Schmitt-trigger bi-directional pin with internal pull up resistor and open-drain output with 12mA sink capability   |

| Output pin with 4 mA source-sink capability                                                                                    |

| Output pin with 8 mA source-sink capability                                                                                    |

| Output pin with 12 mA source-sink capability                                                                                   |

| Output pin with 16 mA source-sink capability                                                                                   |

| Output pin with 24 mA source-sink capability                                                                                   |

| 3.3V output pin with 12 mA source-sink capability                                                                              |

| 3.3V output pin with 24 mA source-sink capability                                                                              |

| Open-drain output pin with 12 mA sink capability                                                                               |

| Open-drain output pin with 24 mA sink capability                                                                               |

|                                                                                                                                |

| OD <sub>12p3</sub> | 3.3V open-drain output pin with 12 mA sink capability               |

|--------------------|---------------------------------------------------------------------|

| INt                | TTL level input pin                                                 |

| IN <sub>tp3</sub>  | 3.3V TTL level input pin                                            |

| INtd               | TTL level input pin with internal pull down resistor                |

| IN <sub>tu</sub>   | TTL level input pin with internal pull up resistor                  |

| INts               | TTL level Schmitt-trigger input pin                                 |

| IN <sub>tsp3</sub> | 3.3V TTL level Schmitt-trigger input pin                            |

| IN <sub>C</sub>    | CMOS level input pin                                                |

| IN <sub>cu</sub>   | CMOS level input pin with internal pull up resistor                 |

| IN <sub>cd</sub>   | CMOS level input pin with internal pull down resistor               |

| IN <sub>CS</sub>   | CMOS level Schmitt-trigger input pin                                |

| IN <sub>csu</sub>  | CMOS level Schmitt-trigger input pin with internal pull up resistor |

## 1.1 LPC Interface

| SYMBOL   | PIN   | I/O                  | FUNCTION                                                                                                                        |

|----------|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|

| CLKIN    | 17    | IN <sub>tp3</sub>    | System clock input. According to the input frequency 24MHz or 48MHz, it is selectable through register. Default is 24MHz input. |

| PME#     | 98    | OD <sub>12p3</sub>   | Generated PME event.                                                                                                            |

| PCICLK   | 19    | IN <sub>tsp3</sub>   | PCI clock input.                                                                                                                |

| LDRQ#    | 20    | O <sub>12p3</sub>    | Encoded DMA Request signal.                                                                                                     |

| SERIRQ   | 21    | I/O12tp3             | Serial IRQ input/Output.                                                                                                        |

| LAD[3:0] | 23-26 | I/O <sub>12tp3</sub> | These signal lines communicate address, control, and data information over the LPC bus between a host and a peripheral.         |

| LFRAME#  | 27    | IN <sub>tsp3</sub>   | Indicates start of a new cycle or termination of a broken cycle.                                                                |

| LRESET#  | 28    | IN <sub>tsp3</sub>   | Reset signal. It can connect to PCIRST# signal on the host.                                                                     |

## 1.2 FDC Interface

| SYMBOL  | PIN | 1/0               | FUNCTION                                                                                                                                                                                                                                                                          |

|---------|-----|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRVDEN0 | 1   | OD <sub>24</sub>  | Drive Density Select bit 0.                                                                                                                                                                                                                                                       |

| INDEX#  | 2   | IN <sub>csu</sub> | This Schmitt-triggered input from the disk drive is active low when the head is positioned over the beginning of a track marked by an index hole. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

| MOA#    | 3   | OD <sub>24</sub>  | Motor A On. When set to 0, this pin enables disk drive 0. This is an open drain output.                                                                                                                                                                                           |

| DSB#    | 4   | OD <sub>24</sub>  | Drive Select B. When set to 0, this pin enables disk drive B. This is an open drain output.                                                                                                                                                                                       |

| DSA#    | 6   | OD <sub>24</sub>  | Drive Select A. When set to 0, this pin enables disk drive A. This is an open drain output.                                                                                                                                                                                       |

| MOB2#   | 7   | OD <sub>24</sub>  | Motor B On. When set to 0, this pin enables disk drive 1. This is an open drain output.                                                                                                                                                                                           |

| DIR#    | 8   | OD <sub>24</sub>  | Direction of the head step motor. An open drain output.                                                                                                                                                                                                                           |

|         |     |                   | Logic 1 = outward motion                                                                                                                                                                                                                                                          |

|         |     |                   | Logic 0 = inward motion                                                                                                                                                                                                                                                           |

| STEP#   | 9   | OD <sub>24</sub>  | Step output pulses. This active low open drain output produces a pulse to move the head to another track.                                                                                                                                                                         |

| WD#     | 10 | OD <sub>24</sub>  | Write data. This logic low open drain writes pre-compensation serial data to the selected FDD. An open drain output.                                                                                                                                          |

|---------|----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WE#     | 11 | OD <sub>24</sub>  | Write enable. An open drain output.                                                                                                                                                                                                                           |

| TRAK0#  | 12 | IN <sub>csu</sub> | Track 0. This Schmitt-triggered input from the disk drive is active low when the head is positioned over the outermost track. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN). |

| WP#     | 13 | IN <sub>csu</sub> | Write protected. This active low Schmitt input from the disk drive indicates that the diskette is write-protected. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).            |

| RDATA#  | 14 | IN <sub>csu</sub> | The read data input signal from the FDD. This input pin is pulled up internally by a 1 K $\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                                                                      |

| HEAD#   | 15 | OD <sub>24</sub>  | Head select. This open drain output determines which disk drive head is active.  Logic 1 = side 0  Logic 0 = side 1                                                                                                                                           |

| DSKCHG# | 16 | IN <sub>csu</sub> | Diskette change. This signal is active low at power on and whenever the diskette is removed. This input pin is pulled up internally by a 1 $K\Omega$ resistor. The resistor can be disabled by bit 7 of L0-CRF0 (FIPURDWN).                                   |

## 1.3 Multi-Mode Parallel Port

The following pins have alternate functions, which are controlled by CR28 and L3-CRF0.

| SYMBOL | PIN | I/O              | FUNCTION                                                                                                                                                                                                                             |

|--------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLCT   | 29  | IN <sub>ts</sub> | PRINTER MODE:                                                                                                                                                                                                                        |

|        |     |                  | An active high input on this pin indicates that the printer is selected. This pin is pulled high internally. Refer to the description of the parallel port for definition of this pin in ECP and EPP mode.                           |

| WE2#   |     | OD <sub>12</sub> | EXTENSION FDD MODE: WE2#                                                                                                                                                                                                             |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the WE# pin of FDC.                                                                                                                                                     |

|        |     |                  | EXTENSION 2FDD MODE: WE2#                                                                                                                                                                                                            |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the WE# pin of FDC.                                                                                                                                               |

| PE     | 30  | IN <sub>ts</sub> | PRINTER MODE:                                                                                                                                                                                                                        |

|        |     |                  | An active high input on this pin indicates that the printer has detected the end of the paper. This pin is pulled high internally. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. |

| WD2#   |     | OD <sub>12</sub> | EXTENSION FDD MODE: WD2#                                                                                                                                                                                                             |

|        |     |                  | This pin is for Extension FDD B; its function is the same as the WD# pin of FDC.                                                                                                                                                     |

|        |     |                  | EXTENSION 2FDD MODE: WD2#                                                                                                                                                                                                            |

|        |     |                  | This pin is for Extension FDD A and B; its function is the same as the WD# pin of FDC.                                                                                                                                               |

| SYMBOL     | PIN | I/O              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUSY MOB2# | 31  | IN <sub>ts</sub> | PRINTER MODE: An active high input indicates that the printer is not ready to receive data. This pin is pulled high internally. Refer to the description of the parallel port for definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: MOB2#                                                                                                                                             |

| MOB2#      |     | OD <sub>12</sub> | This pin is for Extension FDD B; its function is the same as the MOB# pin of FDC.  EXTENSION 2FDD MODE: MOB2#  This pin is for Extension FDD A and B; its function is the same as the MOB# pin of FDC.                                                                                                                                                                                               |

| ACK#       | 32  | IN <sub>ts</sub> | PRINTER MODE: ACK#  An active low input on this pin indicates that the printer has received data and is ready to accept more data. This pin is pulled high internally. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: DSB2#                                                                                                  |

|            |     | 12               | This pin is for the Extension FDD B; its functions is the same as the DSB# pin of FDC.  EXTENSION 2FDD MODE: DSB2#  This pin is for Extension FDD A and B; its function is the same as the DSB# pin of FDC.                                                                                                                                                                                          |

| ERR#       | 33  | IN <sub>ts</sub> | PRINTER MODE: ERR#  An active low input on this pin indicates that the printer has encountered an error condition. This pin is pulled high internally. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: HEAD2#  This pin is for Extension FDD B; its function is the same as the HEAD#pin of FDC.  EXTENSION 2FDD MODE: HEAD2# |

|            |     |                  | This pin is for Extension FDD A and B; its function is the same as the HEAD# pin of FDC.                                                                                                                                                                                                                                                                                                             |

| SYMBOL  | PIN | I/O              | FUNCTION                                                                                                                                                                                                                                 |

|---------|-----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SLIN#   | 34  | OD <sub>12</sub> | PRINTER MODE: SLIN#                                                                                                                                                                                                                      |

| OTEDO#  |     | 0.0              | Output line for detection of printer selection. This pin is pulled high internally. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: STEP2#                        |

| STEP2#  |     | OD <sub>12</sub> | This pin is for Extension FDD B; its function is the same as the STEP# pin of FDC.                                                                                                                                                       |

|         |     |                  | EXTENSION 2FDD MODE: STEP2#                                                                                                                                                                                                              |

|         |     |                  | This pin is for Extension FDD A and B; its function is the same as the STEP# pin of FDC.                                                                                                                                                 |

| INIT#   | 43  | OD <sub>12</sub> | PRINTER MODE: INIT#                                                                                                                                                                                                                      |

|         |     |                  | Output line for the printer initialization. This pin is pulled high internally. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                                                        |

| DIR2#   |     | OD <sub>12</sub> | EXTENSION FDD MODE: DIR2#                                                                                                                                                                                                                |

|         |     |                  | This pin is for Extension FDD B; its function is the same as the DIR# pin of FDC.                                                                                                                                                        |

|         |     |                  | EXTENSION 2FDD MODE: DIR2#                                                                                                                                                                                                               |

|         |     |                  | This pin is for Extension FDD A and B; its function is the same as the DIR# pin of FDC.                                                                                                                                                  |

| AFD#    | 44  | OD <sub>12</sub> | PRINTER MODE: AFD#                                                                                                                                                                                                                       |

| DRVDEN0 |     |                  | An active low output from this pin causes the printer to auto feed a line after a line is printed. This pin is pulled high internally. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode. |

| DIVUENO |     | OD <sub>12</sub> | EXTENSION FDD MODE: DRVDEN0                                                                                                                                                                                                              |

|         |     |                  | This pin is for Extension FDD B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                                                     |

|         |     |                  | EXTENSION 2FDD MODE: DRVDEN0                                                                                                                                                                                                             |

|         |     |                  | This pin is for Extension FDD A and B; its function is the same as the DRVDEN0 pin of FDC.                                                                                                                                               |

| SYMBOL   | PIN | I/O                 | FUNCTION                                                                                                                |

|----------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------|

| STB#     | 46  | OD <sub>12</sub>    | PRINTER MODE: STB#                                                                                                      |

|          |     |                     | An active low output is used to latch the parallel data into the                                                        |

|          |     |                     | printer. This pin is pulled high internally. Refer to the description of                                                |

|          |     |                     | the parallel port for the definition of this pin in ECP and EPP mode.                                                   |

|          |     | -                   | EXTENSION FDD MODE: This pin is a tri-state output.                                                                     |

|          |     | -                   | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                    |

| PD0      | 42  | I/O <sub>12ts</sub> | PRINTER MODE: PD0                                                                                                       |

|          |     |                     | Parallel port data bus bit 0. Refer to the description of the parallel                                                  |

| INIDEVO# |     | INI                 | port for the definition of this pin in ECP and EPP mode.                                                                |

| INDEX2#  |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: INDEX2#  This pin is for Extension FDD B; its function is the same as the                           |

|          |     |                     | INDEX# pin of FDC. It is pulled high internally.                                                                        |

|          |     |                     | EXTENSION 2FDD MODE: INDEX2#                                                                                            |

|          |     |                     | This pin is for Extension FDD A and B; its function is the same as                                                      |

|          |     |                     | the INDEX# pin of FDC. It is pulled high internally.                                                                    |

| PD1      | 41  | I/O <sub>12ts</sub> | PRINTER MODE: PD1                                                                                                       |

|          |     |                     | Parallel port data bus bit 1. Refer to the description of the parallel                                                  |

|          |     |                     | port for the definition of this pin in ECP and EPP mode.                                                                |

| TRAK02#  |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: TRAK02#                                                                                             |

|          |     |                     | This pin is for Extension FDD B; its function is the same as the                                                        |

|          |     |                     | TRAK0# pin of FDC. It is pulled high internally.                                                                        |

|          |     |                     | EXTENSION. 2FDD MODE: TRAK02#                                                                                           |

|          |     |                     | This pin is for Extension FDD A and B; its function is the same as the TRAK0# pin of FDC. It is pulled high internally. |

| PD2      | 40  | I/O <sub>12ts</sub> | PRINTER MODE: PD2                                                                                                       |

| . 52     |     | " 012ts             | Parallel port data bus bit 2. Refer to the description of the parallel                                                  |

|          |     |                     | port for the definition of this pin in ECP and EPP mode.                                                                |

| WP2#     |     | IN <sub>ts</sub>    | EXTENSION FDD MODE: WP2#                                                                                                |

|          |     | ເວ                  | This pin is for Extension FDD B; its function is the same as the                                                        |

|          |     |                     | WP# pin of FDC. It is pulled high internally.                                                                           |

|          |     |                     | EXTENSION. 2FDD MODE: WP2#                                                                                              |

|          |     |                     | This pin is for Extension FDD A and B; its function is the same as                                                      |

|          |     |                     | the WP# pin of FDC. It is pulled high internally.                                                                       |

| SYMBOL    | PIN | I/O                  | FUNCTION                                                                                                                                                      |  |  |  |  |  |  |

|-----------|-----|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PD3       | 39  | I/O <sub>12ts</sub>  | PRINTER MODE: PD3                                                                                                                                             |  |  |  |  |  |  |

|           |     |                      | Parallel port data bus bit 3. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                               |  |  |  |  |  |  |

| RDATA2#   |     | IN <sub>ts</sub>     | EXTENSION FDD MODE: RDATA2#                                                                                                                                   |  |  |  |  |  |  |

|           |     |                      | This pin is for Extension FDD B; its function is the same as the RDATA# pin of FDC. It is pulled high internally.                                             |  |  |  |  |  |  |

|           |     |                      | EXTENSION 2FDD MODE: RDATA2#                                                                                                                                  |  |  |  |  |  |  |

|           |     |                      | This pin is for Extension FDD A and B; its function is the same as the RDATA# pin of FDC. It is pulled high internally.                                       |  |  |  |  |  |  |

| PD4       | 38  | I/O <sub>12ts</sub>  | PRINTER MODE: PD4                                                                                                                                             |  |  |  |  |  |  |

| DOKOLIOO# |     |                      | Parallel port data bus bit 4. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.  EXTENSION FDD MODE: DSKCHG2# |  |  |  |  |  |  |

| DSKCHG2#  |     | IN <sub>ts</sub>     |                                                                                                                                                               |  |  |  |  |  |  |

|           |     |                      | This pin is for Extension FDD B; the function of this pin is the same as the DSKCHG# pin of FDC. It is pulled high internally.                                |  |  |  |  |  |  |

|           |     |                      | EXTENSION 2FDD MODE: DSKCHG2#                                                                                                                                 |  |  |  |  |  |  |

|           |     |                      | This pin is for Extension FDD A and B; this function of this pin is the same as the DSKCHG# pin of FDC. It is pulled high internally.                         |  |  |  |  |  |  |

| PD5       | 37  | I/O <sub>12ts</sub>  | PRINTER MODE: PD5                                                                                                                                             |  |  |  |  |  |  |

|           |     |                      | Parallel port data bus bit 5. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                               |  |  |  |  |  |  |

|           |     | -                    | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                           |  |  |  |  |  |  |

|           |     | -                    | EXTENSION 2FDD MODE: This pin is a tri-state output.                                                                                                          |  |  |  |  |  |  |

| PD6       | 36  | I/OD <sub>12ts</sub> | PRINTER MODE: PD6                                                                                                                                             |  |  |  |  |  |  |

|           |     | _                    | Parallel port data bus bit 6. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                               |  |  |  |  |  |  |

|           |     |                      | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                           |  |  |  |  |  |  |

| MOA2#     |     | OD <sub>12</sub>     | EXTENSION. 2FDD MODE: MOA2#                                                                                                                                   |  |  |  |  |  |  |

|           |     | .1                   | This pin is for Extension FDD A; its function is the same as the MOA# pin of FDC.                                                                             |  |  |  |  |  |  |

| PD7       | 35  | I/OD <sub>12ts</sub> | PRINTER MODE: PD7                                                                                                                                             |  |  |  |  |  |  |

|           |     |                      | Parallel port data bus bit 7. Refer to the description of the parallel port for the definition of this pin in ECP and EPP mode.                               |  |  |  |  |  |  |

|           |     | -                    | EXTENSION FDD MODE: This pin is a tri-state output.                                                                                                           |  |  |  |  |  |  |

| DSA2#     |     | OD <sub>12</sub>     | EXTENSION 2FDD MODE: DSA2#                                                                                                                                    |  |  |  |  |  |  |

|           |     |                      | This pin is for Extension FDD A; its function is the same as the DSA# pin of FDC.                                                                             |  |  |  |  |  |  |

## 1.4 Serial Port Interface

| SYMBOL         | PIN      | I/O             | FUNCTION                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|----------------|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| CTSA#          | 47       | IN <sub>t</sub> | Clear To Send. It is the modem control input.                                                                                                                                                                                                       |  |  |  |  |  |  |

| CTSB#          | 55       |                 | The function of these pins can be tested by reading bit 4 of the handshake status register.                                                                                                                                                         |  |  |  |  |  |  |

| DSRA#<br>DSRB# | 48<br>56 | IN <sub>t</sub> | Data Set Ready. An active low signal indicates the modem or dat set is ready to establish a communication link and transfer data to the UART.                                                                                                       |  |  |  |  |  |  |

| RTSA#          | 49       | Ο <sub>8</sub>  | UART A Request To Send. An active low signal informs the modem or data set that the controller is ready to send data.                                                                                                                               |  |  |  |  |  |  |

| HEFRAS         |          | lNcd            | During power-on reset, this pin is pulled down internally and is defined as HEFRAS, which provides the power-on value for CR26 b 6 (HEFRAS). A 4.7 k $\Omega$ is recommended if intends to pull up (select 4EH as configuration I/O port's address) |  |  |  |  |  |  |

| RTSB#          | 57       | O <sub>8</sub>  | UART B Request To Send. An active low signal informs the moder or data set that the controller is ready to send data.                                                                                                                               |  |  |  |  |  |  |

| DTRA#          | 50       | Ο <sub>8</sub>  | UART A Data Terminal Ready. An active low signal informs the modem or data set that the controller is ready to communicate.                                                                                                                         |  |  |  |  |  |  |

| PNPCSV#        |          | lNcd            | During power-on reset, this pin is pulled down internally and is defined as PNPCSV#, which provides the power-on value for CR24 bit 0 (PNPCSV#). A 4.7 k $\Omega$ is recommended if intends to pull up.                                             |  |  |  |  |  |  |

|                |          |                 | (clear the default value of FDC, UARTs, and PRT)                                                                                                                                                                                                    |  |  |  |  |  |  |

| DTRB#          | 58       | O <sub>8</sub>  | UART B Data Terminal Ready. An active low signal informs the modem or data set that controller is ready to communicate.                                                                                                                             |  |  |  |  |  |  |

| SINA<br>SINB   | 51<br>59 | IN <sub>t</sub> | Serial Input. It is used to receive serial data through the communication link.                                                                                                                                                                     |  |  |  |  |  |  |

| SOUTA          | 52       | O <sub>8</sub>  | UART A Serial Output. It is used to transmit serial data out to the communication link.                                                                                                                                                             |  |  |  |  |  |  |

| PENROM#        |          | INcd            | During power on reset , this pin is pulled down internally and is defined as PENROM#, which provides the power on value for CR24 bit 1. A $4.7 k\Omega$ is recommended if intends to pull up .                                                      |  |  |  |  |  |  |

| SOUTB          | 61       | O <sub>8</sub>  | UART B Serial Output. During power-on reset, this pin is pulled                                                                                                                                                                                     |  |  |  |  |  |  |

| PEN48          |          | INcd            | down internally and is defined as PEN48, which provides the power-on value for CR24 bit 6 (EN48). A 4.7 k $\Omega$ resistor is recommended if intends to pull up.                                                                                   |  |  |  |  |  |  |

| DCDA#<br>DCDB# | 53<br>62 | IN <sub>t</sub> | Data Carrier Detect. An active low signal indicates the modem or data set has detected a data carrier.                                                                                                                                              |  |  |  |  |  |  |

| RIA#           | 54       | IN <sub>t</sub> | Ring Indicator. An active low signal indicates that a ring signal is                                                                                                                                                                                |  |  |  |  |  |  |

| RIB#           | 63       | 1               | being received from the modem or data set.                                                                                                                                                                                                          |  |  |  |  |  |  |

## 1.5 Infrared Port

| SYMBOL | PIN | I/O              | FUNCTION                                                |

|--------|-----|------------------|---------------------------------------------------------|

| IRRX   | 64  | IN <sub>ts</sub> | Alternate Function Input: Infrared Receiver input.      |

|        |     |                  | General purpose I/O port 3 bit 6.                       |

| IRTX   | 65  | O12              | Alternate Function Output: Infrared Transmitter Output. |

|        |     |                  | General purpose I/O port 3 bit 7.                       |

## 1.6 Flash ROM Interface

| SYMBOL    | PIN   | I/O                 | FUNCTION                                |  |  |  |  |

|-----------|-------|---------------------|-----------------------------------------|--|--|--|--|

| XA18-XA16 | 66-68 | O12                 | Flash ROM interface Address[18:16]      |  |  |  |  |

| GP57-GP55 |       | I/OD <sub>12t</sub> | General purpose I/O port 5 bit7-5       |  |  |  |  |

| XA15-XA10 | 69-74 | O12                 | Flash ROM interface Address[15:10]      |  |  |  |  |

| GP47-GP42 |       | I/OD <sub>12t</sub> | General purpose I/O port 4 bit7-2       |  |  |  |  |

| XA9-XA8   | 76-77 | O12                 | Flash ROM interface Address[9:8]        |  |  |  |  |

| GP41-GP40 |       | I/OD <sub>12t</sub> | General purpose I/O port 4 bit1-0       |  |  |  |  |

| XA7-XA0   | 78-85 | O12                 | Flash ROM interface Address[7:0]        |  |  |  |  |

| GP37-GP30 |       | I/OD <sub>12t</sub> | General purpose I/O port 3 bit7-0       |  |  |  |  |

| XD7-XD4   | 86-89 | I/O12t              | Flash ROM interface Data Bus[7:4]       |  |  |  |  |

| GP27-GP24 |       | I/OD <sub>12t</sub> | General purpose I/O port 2 bit7-4       |  |  |  |  |

| XD3-XD0   | 91-94 | I/O12t              | Flash ROM interface Data Bus [3:0]      |  |  |  |  |

| GP23-GP20 |       | I/OD <sub>12t</sub> | General purpose I/O port 2 bit3-0       |  |  |  |  |

| ROMCS#    | 95    | O12                 | Flash ROM interface Chip Select         |  |  |  |  |

| GP54      |       | I/OD <sub>12t</sub> | General purpose I/O port 5 bit4         |  |  |  |  |

| MEMR#     | 96    | O12                 | Flash ROM interface Memory Read Enable  |  |  |  |  |

| GP53      |       | I/OD <sub>12t</sub> | General purpose I/O port 5 bit3         |  |  |  |  |

| MEMW#     | 97    | O12                 | Flash ROM interface Memory Write Enable |  |  |  |  |

| GP52      |       | I/OD <sub>12t</sub> | General purpose I/O port 5 bit2         |  |  |  |  |

## 1.7 General Purpose I/O Port

| SYMBOL | PIN | I/O                 | FUNCTION                         |

|--------|-----|---------------------|----------------------------------|

| GP73   | 111 | I/OD <sub>12t</sub> | General purpose I/O port 7 bit3  |

|        |     |                     |                                  |

| GP80   | 118 | I/OD <sub>12t</sub> | General purpose I/O port 8 bit0  |

| WDTO   |     | O <sub>12</sub>     | Watch dog timer output.          |

| GP67   | 99  | I/OD <sub>12t</sub> | General purpose I/O port 6 bit7. |

| GP66   | 100 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit6. |

| GP65   | 101 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit5. |

| GP64   | 102 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit4. |

| GP63   | 103 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit3. |

| GP62   | 104 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit2. |

| GP61   | 105 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit1. |

| GP60   | 106 | I/OD <sub>12t</sub> | General purpose I/O port 6 bit0. |

#### 1.8 Smart Card Interface

| SYMBOL | PIN | I/O                 | FUNCTION                                            |

|--------|-----|---------------------|-----------------------------------------------------|

| SCPSNT | 107 | IN <sub>ts</sub>    | Smart card present detection Schmitt-trigger input. |

| GP77   |     | I/OD <sub>24t</sub> | General purpose I/O port 7 bit7.                    |

| SCIO   | 108 | I/O <sub>24t</sub>  | Smart card data I/O channel.                        |

| GP76   |     | I/OD <sub>24t</sub> | General purpose I/O port 7 bit6.                    |

| SCCLK  | 109 | O4                  | Smart card clock output.                            |

| GP75   |     | I/OD <sub>4t</sub>  | General purpose I/O port 7 bit5.                    |

| SCRST  | 110 | O24                 | Smart card reset output.                            |

| GP74   |     | I/OD <sub>24t</sub> | General purpose I/O port 7 bit4.                    |

| SCC8   | 112 | I/O <sub>24t</sub>  | Smart card General Purpose I/O channel.             |

| GP72   |     | I/OD <sub>24t</sub> | General purpose I/O port 7 bit2.                    |

| SCPWR  | 113 | O12                 | Smart card power control.                           |

| GP71   |     | I/OD <sub>12t</sub> | General purpose I/O port 7 bit1.                    |

| SCC4   | 114 | I/O <sub>24t</sub>  | Smart card General Purpose I/O channel.             |

| GP70   |     | I/OD <sub>24t</sub> | General purpose I/O port 7 bit0.                    |

## 1.9 PWM & General Purpose I/O Port 8

| SYMBOL  | PIN  | I/O                 | FUNCTION                                                 |

|---------|------|---------------------|----------------------------------------------------------|

| PWM2    | 115  | O12                 | Fan speed control . Use the Pulse Width Modulation (PWM) |

| PLED    |      | O <sub>12</sub>     | Power LED output, this signal is low after system reset. |

| GP83    |      | I/OD <sub>12t</sub> | General purpose I/O port 8 bit2-1                        |

| PWM1-0  | 116- | O12                 | Fan speed control . Use the Pulse Width Modulation (PWM) |

|         | 117  |                     | Techno knowledge to control the Fan's RPM.               |

| GP82-81 |      | I/OD <sub>12t</sub> | General purpose I/O port 8 bit2-1                        |

## 1.10 Game Port & MIDI Port

| SYMBOL | PIN | I/O                  | FUNCTION                                                          |

|--------|-----|----------------------|-------------------------------------------------------------------|

| MSI    | 119 | INcu                 | MIDI serial data input .                                          |

| GP51   |     | I/OD <sub>24c</sub>  | General purpose I/O port 5 bit 1.                                 |

| MSO    | 120 | O12                  | MIDI serial data output.                                          |

| GP50   |     | I/OD <sub>12t</sub>  | General purpose I/O port 5 bit 0.                                 |

| GPAS2  | 121 | INcs                 | Active-low, Joystick I switch input 2. This pin has an internal   |

|        |     |                      | pull-up resistor. (Default)                                       |

| GP17   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 7.                                 |

| GPBS2  | 122 | INcs                 | Active-low, Joystick II switch input 2. This pin has an internal  |

|        |     |                      | pull-up resistor. (Default)                                       |

| GP16   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 6.                                 |

| GPAY   | 123 | I/OD <sub>24a</sub>  | Joystick I timer pin. this pin connect to Y positioning variable  |

|        |     |                      | resistors for the Joystick. (Default)                             |

| GP15   |     | I/OD24cs             | General purpose I/O port 1 bit 5.                                 |

| GPBY   | 124 | I/OD <sub>24a</sub>  | Joystick II timer pin. this pin connect to Y positioning variable |

|        |     |                      | resistors for the Joystick. (Default)                             |

| GP14   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 4.                                 |

#### 1.10 Game Port & MIDI Port, continued

| SYMBOL | PIN | I/O                  | FUNCTION                                                          |

|--------|-----|----------------------|-------------------------------------------------------------------|

| GPBX   | 125 | I/OD <sub>24a</sub>  | Joystick II timer pin. this pin connect to X positioning variable |

|        |     |                      | resistors for the Joystick. (Default)                             |

| GP13   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 3.                                 |

| GPAX   | 126 | I/OD24a              | Joystick I timer pin. This pin connect to X positioning variable  |

|        |     |                      | resistors for the Joystick. (Default)                             |

| GP12   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 2.                                 |

| GPBS1  | 127 | Incs                 | Active-low, Joystick II switch input 1. This pin has an internal  |

|        |     |                      | pull-up resistor. (Default)                                       |

| GP11   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 1.                                 |

| GPAS1  | 128 | Incs                 | Active-low, Joystick I switch input 1. This pin has an internal   |

|        |     |                      | pull-up resistor. (Default)                                       |

| GP10   |     | I/OD <sub>24cs</sub> | General purpose I/O port 1 bit 0.                                 |

### 1.11 POWER PINS

| SYMBOL | PIN         | FUNCTION                                             |

|--------|-------------|------------------------------------------------------|

| VCC    | 5, 45, 75,  | +5V power supply for the digital circuitry.          |

| VCC3V  | 22          | +3.3V power supply for driving 3V on host interface. |

| GND    | 18, 60, 90, | Ground.                                              |

#### 2. SMART CARD READER INTERFACE (SCR)

#### 2.1 Features

Winbond's implementation of Smart Card Reader interface is based on ISO/IEC 7816-3 standard and fully compliant with PC/SC Specifications 1.0. Except for pins specified in ISO/IEC 7816-3, W83697SF's SCI also includes SCPSNT (Smart Card Present) monitoring status of card insertion/extraction, SCLED (Smart Card traffic LED display) which is active high when host is accessing information to/from card, and two general-purpose I/O pins SCC4 and SCC8 (only available in W83697SF) for users to design application-specific functions.

Register file (control and status registers) of Winbond's Smart Card interface is designed in an UART-like structure so that users with previous UART experience should have no trouble to implement Winbond's SCI applications.

Power consumption is minimized by sophisticated device's operation scheme.

## 2.2 Register file

Complete register file table

|                          |                                                     |       |                 | Bit             | Number         |                 |                  |                  |                   |                      |

|--------------------------|-----------------------------------------------------|-------|-----------------|-----------------|----------------|-----------------|------------------|------------------|-------------------|----------------------|

| Register file            |                                                     | Abbr. | 7               | 6               | 5              | 4               | 3                | 2                | 1                 | 0                    |

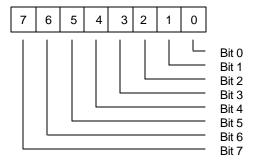

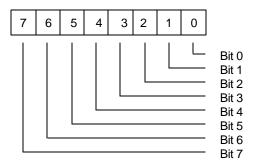

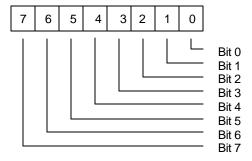

| Base + 0<br>BDLAB =<br>0 | Receiver Buffer<br>Register (Read<br>only)          | RBR   | Bit 7           | Bit 6           | Bit 5          | Bit 4           | Bit 3            | Bit 2            | Bit 1             | Bit 0                |

| Base + 0<br>BDLAB =<br>0 | Transmitter Buffer<br>Register (Write<br>only)      | TBR   | Bit 7           | Bit 6           | Bit 5          | Bit 4           | Bit 3            | Bit 2            | Bit 1             | Bit 0                |

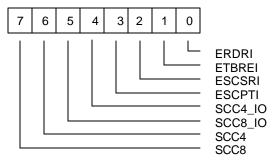

| Base + 1<br>BDLAB =<br>0 | Interrupt Enable<br>Register                        | IER   | SCC8            | SCC4            | SCC8_IO (note) | SCC4_IO (note)  | ESCPTI<br>(note) | ESCSRI<br>(note) | ETBREI<br>(note)  | ERDRI<br>(note)      |

| 0                        | default                                             |       | Х               | Х               | 0              | 0               | 0                | 0                | 0                 | 0                    |

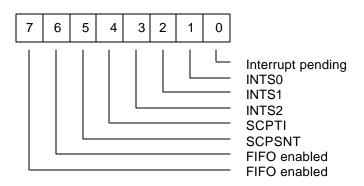

| Base + 2<br>BDLAB =<br>0 | Interrupt Status<br>Register (Read<br>only)         | ISR   | FIFO<br>enabled | FIFO<br>enabled | SCPSNT         | SCPTI<br>(note) | INTS2<br>(note)  | INTS1<br>(note)  | (note)            | Interrupt<br>pending |

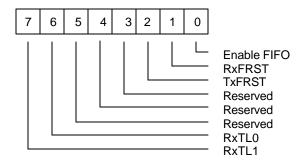

| Base + 2<br>BDLAB =<br>0 | Smart Card FIFO<br>control Register<br>(Write only) | SCFR  | RxTL1<br>(note) | RxTL0<br>(note) | Reserved       | Reserved        | Reserved         | TxFRST (note)    | RxFRST (note)     | Enable<br>FIFO       |

|                          | default                                             |       | 0               | 0               | x              | х               | х                | 0                | 0                 | 0                    |

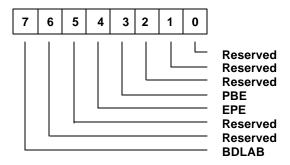

| Base + 3                 | Smart Card Control<br>Register                      | SCCR  | BDLAB (note)    | Reserved        | Reserved       | EPE<br>(note)   | PBE<br>(note)    | Reserved         | Reserved          | SC_SEL               |

|                          | default                                             |       | 0               | х               | х              | 0               | 0                | х                | х                 | 0                    |

| Base + 4                 | Clock Base<br>Register                              | CBR   | Bit 7           | Bit 6           | Bit 5          | Bit 4           | Bit 3            | Bit 2            | Bit 1             | Bit 0                |

|                          | default                                             |       | 0               | 0               | 0              | 0               | 1                | 1                | 0                 | 0                    |

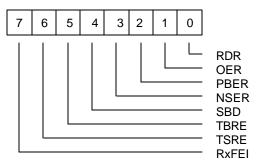

| Base + 5                 | Smart Card Status<br>Register (Read<br>only)        | SCSR  | RxFEI<br>(note) | TSRE<br>(note)  | TBRE<br>(note) | SBD<br>(note)   | NSER<br>(note)   | PBER<br>(note)   | OER<br>(note)     | RDR<br>(note)        |

| Base + 6                 | Guard Time<br>Register                              | GTR   | Bit 7           | Bit 6           | Bit 5          | Bit 4           | Bit 3            | Bit 2            | Bit 1             | Bit 0                |

|                          | default                                             |       | 0               | 0               | 0              | 0               | 0                | 0                | 0                 | 1                    |

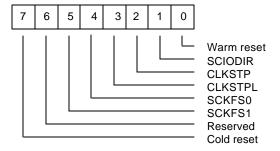

| Base + 7                 | Extended Control<br>Register                        | ECR   | Cold reset      | Reserved        | SCKFS1 (note)  | SCKFS0 (note)   | CLKSTPL (note)   | CLKSTP (note)    | SCIODIR<br>(note) | Warm<br>reset        |

|                          | default                                             |       | 0               | х               | 0              | 1               | 0                | 0                | 1                 | 0                    |

| Base + 0<br>BDLAB =      | Baud rate divisor<br>Latch Lower byte               | BLL   | Bit 7           | Bit 6           | Bit 5          | Bit 4           | Bit 3            | Bit 2            | Bit 1             | Bit 0                |

| 1                        | default                                             |       | 0               | 0               | 0              | 1               | 1                | 1                | 1                 | 1                    |

| Base + 1<br>BDLAB =      | Baud rate divisor<br>Latch Higher byte              | BLH   | Bit 15          | Bit 14          | Bit 13         | Bit 12          | Bit 11           | Bit 10           | Bit 9             | Bit 8                |

| 1                        | default                                             |       | 0               | 0               | 0              | 0               | 0                | 0                | 0                 | 0                    |

| Base + 2 | Smart Card ID      | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

|----------|--------------------|---|---|---|---|---|---|---|---|

| BDLAB =  | number (Read only) |   |   |   |   |   |   |   | 0 |

| 1        |                    |   |   |   |   |   |   |   |   |

Note:

Abbreviation explanation (in alphabetical order) -

BDLAB - Baud rate divisor latch access bit.

CLKSTP - Stop Smart Card interface's clock SCCLK.

CLKSTPL - Set SCCLK level when CLKSTP is "1".

EPE – Even parity enable.

ERDRI - Enable RBR (Receiver Buffer Register) data ready interrupt.

ESCPTI - Enable SCPSNT interrupt.

ESCSRI - Enable interrupts of SCSR (read only Smart Card Status Register at base address + 5) events.

ETBREI – Enable TBR (write only Transmitter Buffer Register at base address + 0) empty interrupt.

INTS2 ~ INTS0 – Interrupt status bits. Refer to description of ISR (read only Interrupt Status Register at base address + 2) for details.

NSER – No stop bit error.

OER – Overrun error.

PBE - Parity bit enable.

PBER – Parity bit error.

RDR - Receiver data ready status.

RxFEI - Receiver FIFO error indication.

RxFRST - Receiver FIFO reset.

RxTL1 ~ RxTL0 - Receiver threshold level setting bits. Refer to description of SCFR (write only Smart Card FIFO control register at base address + 2) for details.

SBD – Silent byte detected.

SCIODIR – SCIO direction bit (0/1 mean output/input respectively).

SCKFS1 ~ SCKFS0 – Smart Card interface clock frequency selection bits. Refer to description of ECR (Extended Control Register at base address + 7) for details.

SCPTI – SCPSNT toggle interrupt status.

SC\_SEL - Smart Card socket selection.

TBRE – TBR (write only Transmitter Buffer Register at base address + 0) empty status.

TSRE - TSR (Transmitter shift register) empty status.

TxFRST - Transmitter FIFO reset.

#### Receiver Buffer Register (RBR at base address + 0 when BDLAB = 0, read only)

This register is the access port for receiver FIFO. It is active when Smart Card interface is in input mode with SCIODIR (bit 1 of ECR at base address + 7) set to "1". The depth of receiver FIFO is 16 bytes.

Bit 7 ~ bit 0: Access port for receiver FIFO.

#### Receiver Buffer Register (RBR at base address + 0 when BDLAB = 0, read only)

This register is the access port for transmitter FIFO. It is active when Smart Card interface is in output mode with SCIODIR (bit 1 of ECR at base address + 7) set to "0". The depth of transmitter FIFO is 16 bytes.

Bit 7 ~ bit 0: Access port for receiver FIFO.

#### Interrupt Enable Register (IER at base address + 1 when BDLAB = 0)