# **PCI6050** Serial PCI-to-PCI Bridge

# Data Manual

June 2000

**MSDS Bus Solutions**

SLLS434A

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

# Contents

| Se | ection |           | Title                               | Page |

|----|--------|-----------|-------------------------------------|------|

| 1  | Introc | luction . |                                     | 1–1  |

|    | 1.1    | Feature   | S                                   | 1–1  |

|    | 1.2    | Related   | Documents                           | 1–1  |

|    | 1.3    | Tradem    | arks                                | 1–2  |

|    | 1.4    | Ordering  | g Information                       | 1–2  |

| 2  | Termi  | nal Desc  | riptions                            | 2–1  |

| 3  | Featu  | re/Proto  | col Descriptions                    | 3–1  |

|    | 3.1    | Introduc  | ction to the PCI6050                | 3–1  |

|    | 3.1    | PCI605    | 0 System Diagram                    | 3–2  |

|    | 3.2    | Protoco   | I Fundamentals                      | 3–2  |

|    |        | 3.2.1     | Packet Format                       | 3–2  |

|    |        | 3.2.2     | Start Up Procedure                  | 3–3  |

|    |        | 3.2.3     | Packet Summary                      | 3–3  |

|    | 3.3    | PCI Cor   | mmands                              | 3–4  |

|    | 3.4    | Configu   | ration Cycles                       | 3–4  |

|    | 3.5    | Second    | ary PCI Clocking                    | 3–6  |

|    | 3.6    | Special   | Cycle Generation                    | 3–7  |

|    | 3.7    | Bus Arb   | pitration                           | 3–7  |

|    |        | 3.7.1     | Primary Bus Arbitration             | 3–7  |

|    |        | 3.7.2     | Secondary Bus Arbitration           | 3–7  |

|    | 3.8    | Decode    | Options                             | 3–7  |

|    | 3.9    | System    | Error Handling                      | 3–7  |

|    |        | 3.9.1     | Posted Write Parity Error           | 3–8  |

|    |        | 3.9.2     | Posted Write Timeout                | 3–8  |

|    |        | 3.9.3     | Target Abort on Posted Writes       | 3–8  |

|    |        | 3.9.4     | Master Abort on Posted Writes       | 3–8  |

|    |        | 3.9.5     | Master Delayed Write Timeout        | 3–8  |

|    |        | 3.9.6     | Master Delayed Read Timeout         |      |

|    |        | 3.9.7     | Secondary SERR                      | 3–8  |

|    | 3.10   | Parity H  | landling and Parity Error Reporting | 3–8  |

|    | 3.11   | Master a  | and Target Abort Handling           | 3–9  |

|    | 3.12   | Discard   | Timer                               | 3–9  |

|    | 3.13   | Delayed   | d Transactions                      | 3–9  |

|    | 3.14   | Compac    | ctPCI Hot-Swap Support              | 3–10 |

|    | 3.15   | JTAG S    | upport                              | 3–10 |

|    | 3.16   | GPIO In   | nterface                            | 3–14 |

|    | 3.17   | PCI Pov   | wer Management                      | 3–15 |

|    |        |           |                                     |      |

|   |        | 3.17.1 Behavior in Low Power States       | 3–15 |

|---|--------|-------------------------------------------|------|

|   | 3.18   | Serial ROM Implementation                 | 3–15 |

| 4 | Bridge | e Configuration Header                    | 4–1  |

|   | 4.1    | Vendor Register                           | 4–2  |

|   | 4.2    | Device ID Register                        | 4–2  |

|   | 4.3    | PCI Command Register                      | 4–3  |

|   | 4.4    | PCI Status Register                       | 4–4  |

|   | 4.5    | Revision ID Register                      | 4–5  |

|   | 4.6    | Class Code Register                       | 4–5  |

|   | 4.7    | Cache Line Size Register                  | 4–5  |

|   | 4.8    | Primary Latency Timer Register            | 4–6  |

|   | 4.9    | Header Type Register                      | 4–6  |

|   | 4.10   | BIST Register                             | 4–6  |

|   | 4.11   | Primary Bus Number Register               | 4–7  |

|   | 4.12   | Secondary Bus Number Register             | 4–7  |

|   | 4.13   | Subordinate Bus Number Register           | 4–7  |

|   | 4.14   | Secondary Bus Latency Timer Register      | 4–8  |

|   | 4.15   | I/O Base Register                         | 4–8  |

|   | 4.16   | I/O Limit Register                        | 4–8  |

|   | 4.17   | Secondary Status Register                 | 4–9  |

|   | 4.18   | Memory Base Register                      | 4–10 |

|   | 4.19   | Memory Limit Register                     | 4–10 |

|   | 4.20   | Prefetchable Memory Base Register         | 4–10 |

|   | 4.21   | Prefetchable Memory Limit Register        | 4–11 |

|   | 4.22   | Prefetchable Base Upper 32 Bits Register  | 4–11 |

|   | 4.23   | Prefetchable Limit Upper 32 Bits Register | 4–12 |

|   | 4.24   | I/O Base Upper 16 Bits Register           | 4–12 |

|   | 4.25   | I/O Limit Upper 16 Bits Register          | 4–12 |

|   | 4.26   | Capability Pointer Register               | 4–13 |

|   | 4.27   | Interrupt Line Register                   | 4–13 |

|   | 4.28   | Interrupt Pin Register                    | 4–13 |

|   | 4.29   | Bridge Control Register                   | 4–14 |

| 5 | Exten  | sion Registers                            | 5–1  |

|   | 5.1    | Chip Control Register                     | 5–1  |

|   | 5.2    | Diagnostic Control Register               | 5–2  |

|   | 5.3    | Arbiter Control Register                  |      |

|   | 5.4    | Primary SERR Event Disable Register       |      |

|   | 5.5    | Primary GPIO Output Data Register         | 5–5  |

|   | 5.6    | Primary GPIO Output Enable Register       |      |

|   | 5.7    | Primary GPIO Input Data Register          |      |

|   | 5.8    | Primary CLKOUT Control Register           |      |

|   | 5.9    | Primary SERR Status Register              |      |

|   | 5.10   | Secondary CLKOUT Control Register         |      |

|   | 5.11   | Secondary SERR Status Register            |      |

| 5.12 | General Purpose Event Register                    | 5–11 |

|------|---------------------------------------------------|------|

| 5.13 | Extended Diagnostic Status Register               | 5–12 |

| 5.14 | Secondary GPIO Output Data Register               | 5–13 |

| 5.15 | Secondary GPIO Output Enable Register             | 5–13 |

| 5.16 | Secondary GPIO Input Data Register                | 5–14 |

| 5.17 | Sequence Error Count Register                     | 5–14 |

| 5.18 | CRC Error Count Register                          | 5–14 |

| 5.19 | Receive Error Count Register                      | 5–15 |

| 5.20 | Transceiver Test Control and Status Register      | 5–15 |

| 5.21 | PM Capability ID Register                         | 5–16 |

| 5.22 | PM Next Item Pointer Register                     | 5–16 |

| 5.23 | Power Management Capabilities Register            | 5–17 |

| 5.24 | Power Management Control/Status Register          | 5–18 |

| 5.25 | PMCSR Bridge Support Register                     | 5–18 |

| 5.26 | PM Data Register                                  | 5–19 |

| 5.27 | HS Capability ID Register                         | 5–19 |

| 5.28 | HS Next Item Pointer Register                     | 5–19 |

| 5.29 | Primary CPCI Hot Swap Control and Status Register | 5–20 |

| 5.30 | Subsystem Vendor ID Register                      | 5–20 |

| 5.31 | Subsystem ID Register                             | 5–21 |

| 5.32 | FIFO BIST Register                                | 5–21 |

|      |                                                   |      |

# List of Illustrations

| Figu | re Title                                                      | Page |

|------|---------------------------------------------------------------|------|

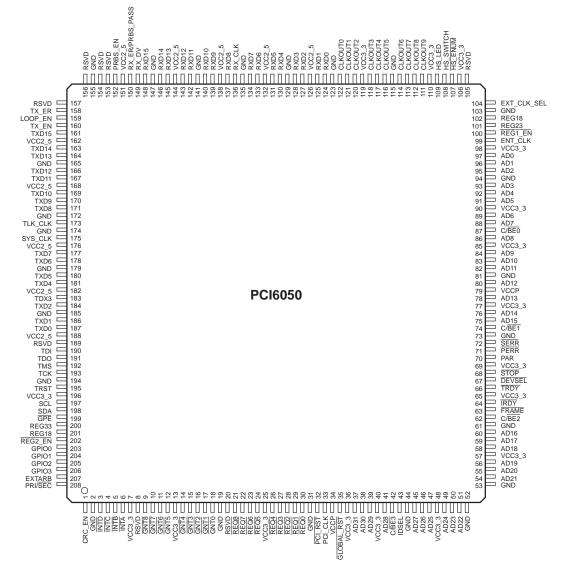

| 2–1  | PCI6050 Terminal Diagram                                      | 2–1  |

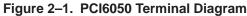

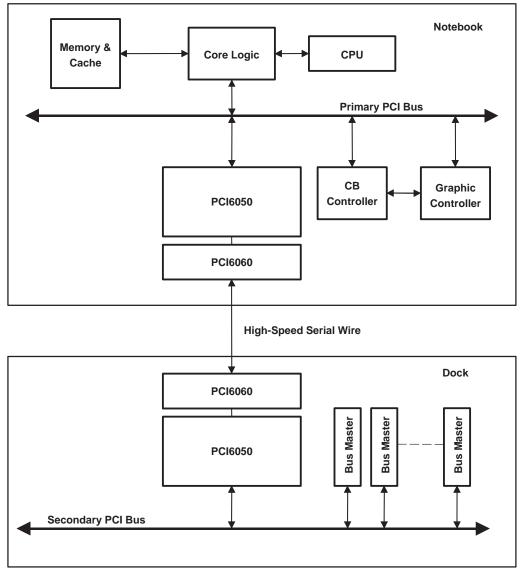

| 3–1  | The PCI-to-PCI Bridge Implementation With PCI6050 Device      | 3–1  |

| 3–2  | PCI6050 System Diagram                                        | 3–2  |

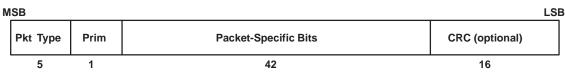

| 3–3  | Packet Format and Bit Ordering                                | 3–3  |

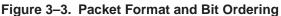

| 3–4  | AD[31–0] During Address Phase of a Type 0 Configuration Cycle | 3–4  |

| 3–5  | AD[31–0] During Address Phase of a Type 1 Configuration Cycle | 3–5  |

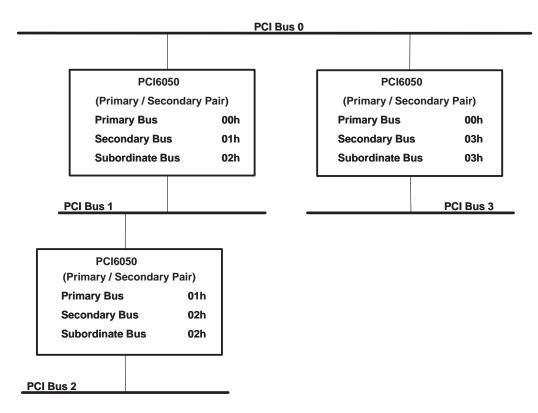

| 3–6  | Bus Hierarchy and Numbering                                   | 3–6  |

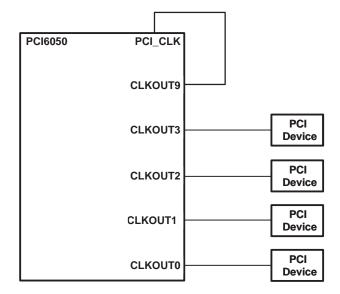

| 3–7  | Secondary PCI Clock Block Diagram                             | 3–6  |

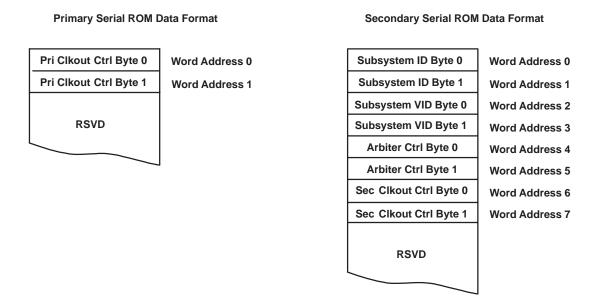

| 3–8  | Serial ROM Data Format                                        | 3–16 |

## **List of Tables**

| Table Title                                                        | Page   |

|--------------------------------------------------------------------|--------|

| 2–1 Terminal Signal Names Sorted by Terminal Number                | . 2–2  |

| 2–2 Terminal Signal Names Sorted Alphabetically to Terminal Number | . 2–3  |

| 2-3 PCI System                                                     | . 2–4  |

| 2–4 PCI Address and Data                                           | . 2–4  |

| 2–5 PCI Interface Control                                          | . 2–5  |

| 2–6 PCI Clock Distribution                                         | . 2–6  |

| 2–7 Secondary PCI Arbitration and Control                          | . 2–6  |

| 2-8 PCI6060 Clock and Control Interface                            | . 2–7  |

| 2–9 PCI6060 Transmit Data Path                                     | . 2–7  |

| 2–10 PCI6060 Receive Data Path                                     | . 2–8  |

| 2–11 Miscellaneous Terminals                                       | . 2–8  |

| 2–12 JTAG Interface Terminals                                      | . 2–9  |

| 2–13 Power Supply                                                  | . 2–9  |

| 3–1 PCI Command Definition                                         | . 3–4  |

| 3–2 AD[31–16] During Address Phase of a Type 0 Configuration Cycle | . 3–5  |

| 3–3 JTAG Instructions and Op Codes                                 | . 3–10 |

| 3–4 Boundary Scan Pin Order                                        | . 3–11 |

| 4–1 PCI Command Register Description                               | . 4–3  |

| 4–2 PCI Status Register Description                                | . 4–4  |

| 4–3 Secondary Status Register Description                          | . 4–9  |

| 4–4 Bridge Control Register Description                            | . 4–14 |

| 5–1 Chip Control Register Description                              | . 5–1  |

| 5–2 Diagnostic Control Register Description                        | . 5–2  |

| 5–3 Arbiter Control Register Description                           | . 5–3  |

| 5–4 Primary SERR Event Disable Register Description                | . 5–4  |

| 5–5 Primary GPIO Output Data Register Description                  | . 5–5  |

| 5–6 Primary GPIO Output Enable Register Description                | . 5–5  |

| 5–7 Primary GPIO Input Data Register Description                   | . 5–6  |

| 5–8 Primary CLKOUT Control Register Description                    | . 5–7  |

| 5–9 Primary SERR Status Register Description                       | . 5–8  |

| 5–10 Secondary CLKOUT Control Register Description                 | . 5–9  |

| 5–11 Secondary SERR Status Register Description                    | . 5–10 |

| 5–12 General Purpose Event Register Description                    | . 5–11 |

| 5–13 Extended Diagnostic Status Register Description               | . 5–12 |

| 5–14 Secondary GPIO Output Data Register Description               | . 5–13 |

| 5–15 Secondary GPIO Output Enable Register Description             | . 5–13 |

| 5–16 Secondary GPIO Input Data Register Description                | . 5–14 |

| 5–17 | Transceiver Test Control and Status Register Description      | 5–15 |

|------|---------------------------------------------------------------|------|

| 5–18 | Power Management Capabilities Register Description            | 5–17 |

| 5–19 | Power Management Control/Status Register Description          | 5–18 |

| 5–20 | PMCSR Bridge Support Register Description                     | 5–18 |

| 5–21 | Primary CPCI Hot Swap Control and Status Register Description | 5–20 |

| 5–22 | FIFO BIST Register Description                                | 5–21 |

## 1 Introduction

The Texas Instruments PCI6050 symmetric serialized PCI-to-PCI bridge provides a high-performance connection path between two peripheral component interconnect (PCI) buses. Transactions occur between masters on one PCI bus and targets on another PCI bus, and the PCI6050 device allows bridged transactions to occur concurrently on both buses. The PCI6050 pipeline architecture supports burst-mode transfers to maximize data throughput, and the two bus traffic paths through the bridge act independently.

A PCI6050-based PCI-to-PCI bridge is compliant with the *PCI Local Bus Specification* and can be used to overcome trace length limitations by allowing PCI-to-PCI implementations to span across separate system boards, and extend the electrical loading limits of 10 devices per PCI bus and 1 PCI device per expansion slot by creating hierarchical buses. The PCI6050 device provides two-tier internal arbitration for up to nine secondary bus masters and may be implemented with an external secondary PCI bus arbiter.

The compact-PCI hot-swap extended PCI capability is provided, which makes the PCI6050 device an ideal solution for multifunction compact PCI cards, remote chassis-to-chassis interconnects, and the adaptation of single function cards for hot-swap compliance.

## 1.1 Features

The PCI6050 device supports the following features:

- Configurable for PCI Bus Power Management Interface Specification

- Provides CompactPCI hot-swap functionality

- 3.3-V PCI core logic with universal PCI interface compatible with 3.3-V and 5-V PCI signaling environments

- 2.5-V serial link core logic compatible with the PCI6060 transceiver

- Supports 32-bit, 33-MHz PCI buses

- Provides internal two-tier arbitration for up to nine secondary bus masters and supports an external secondary bus arbiter

- Performs burst data transfers with pipeline architecture to maximize data throughput in both directions

- Independent read and write buffers for each direction

- Allows up to three delayed transactions in both directions

- Provides 10 secondary PCI clock outputs

- Predictable latency per PCI Local Bus Specification

- Propagates bus locking

- Secondary bus is driven low during reset

- Provides VGA/palette memory and I/O, and subtractive decoding options

- Advanced submicron, low-power CMOS technology

#### 1.2 Related Documents

- Advanced Configuration and Power Interface (ACPI) Specification (Revision 1.0)

- PCI Local Bus Specification (Revision 2.2)

- PCI-to-PCI Bridge Architecture Specification (Revision 1.1)

- PCI Bus Power Management Interface Specification (Revision 1.1)

- PICMG Compact-PCI Hot Swap Specification (Revision 1.0) Texas Instruments PCI6060 Product Data Manual •

- •

## 1.3 Trademarks

## 1.4 Ordering Information

| DEVICE  | NAME                     | VOLTAGE | PACKAGE          |

|---------|--------------------------|---------|------------------|

| PCI6050 | Serial PCI-to-PCI Bridge |         | 208-Terminal QFP |

## **2** Terminal Descriptions

Figure 2-1 illustrates the terminals in the PCI6050 device.

Table 2–1 lists the PCI6050 device terminals in numeric order; Table 2–2 presents them in alphabetic order with their corresponding terminal number.

| NO  |              |     | Terminal Signal Nan |     | ę               |     |         |

|-----|--------------|-----|---------------------|-----|-----------------|-----|---------|

| NO. |              | NO. |                     | NO. |                 | NO. |         |

| 1   | CRC_EN       | 53  | GND                 | 105 | RSVD            | 157 | RSVD    |

| 2   | GND          | 54  | AD21                | 106 | VCC3_3          | 158 | TX_ER   |

| 3   | INTD         | 55  | AD20                | 107 | HS_ENUM         | 159 | LOOP_EN |

| 4   | INTC         | 56  | AD19                | 108 | HS_SWITCH       | 160 | TX_EN   |

| 5   | INTB         | 57  | VCC3_3              | 109 | HS_LED          | 161 | TXD15   |

| 6   | INTA         | 58  | AD18                | 110 | VCC3_3          | 162 | VCC2_5  |

| 7   | VCC3_3       | 59  | AD17                | 111 | CLKOUT9         | 163 | TXD14   |

| 8   | RSVD         | 60  | AD16                | 112 | CLKOUT8         | 164 | TXD13   |

| 9   | GNT8         | 61  | GND                 | 113 | CLKOUT7         | 165 | GND     |

| 10  | GNT7         | 62  | C/BE2               | 114 | CLKOUT6         | 166 | TXD12   |

| 11  | GNT6         | 63  | FRAME               | 115 | GND             | 167 | TXD11   |

| 12  | GNT5         | 64  | IRDY                | 116 | CLKOUT5         | 168 | VCC2_5  |

| 13  | VCC3_3       | 65  | VCC3_3              | 117 | CLKOUT4         | 169 | TXD10   |

| 14  | GNT4         | 66  | TRDY                | 118 | CLKOUT3         | 170 | TXD9    |

| 15  | GNT3         | 67  | DEVSEL              | 119 | VCC3_3          | 171 | TXD8    |

| 16  | GNT2         | 68  | STOP                | 120 | CLKOUT2         | 172 | GND     |

| 17  | GNT1         | 69  | VCC3_3              | 121 | CLKOUT1         | 173 | TLK_CLK |

| 18  | <b>GNT</b> 0 | 70  | PAR                 | 122 | CLKOUT0         | 174 | GND     |

| 19  | GND          | 71  | PERR                | 123 | GND             | 175 | SYS_CLK |

| 20  | RSVD         | 72  | SERR                | 124 | RXD0            | 176 | VCC2_5  |

| 21  | REQ8         | 73  | GND                 | 125 | RXD1            | 177 | TXD7    |

| 22  | REQ7         | 74  | C/BE1               | 126 | VCC2_5          | 178 | TXD6    |

| 23  | REQ6         | 75  | AD15                | 127 | RXD2            | 179 | GND     |

| 24  | REQ5         | 76  | AD14                | 128 | RXD3            | 180 | TXD5    |

| 25  | VCC3_3       | 77  | VCC3_3              | 129 | GND             | 181 | TXD4    |

| 26  | REQ4         | 78  | AD13                | 130 | RXD4            | 182 | VCC2_5  |

| 27  | REQ3         | 79  | VCCP                | 131 | RXD5            | 183 | TXD3    |

| 28  | REQ2         | 80  | AD12                | 132 | VCC2_5          | 184 | TXD2    |

| 29  | REQ1         | 81  | GND                 | 133 | RXD6            | 185 | GND     |

| 30  | REQ0         | 82  | AD11                | 134 | RXD7            | 186 | TXD1    |

| 31  | GND          | 83  | AD10                | 135 | GND             | 187 | TXD0    |

| 32  | PCI_RST      | 84  | AD9                 | 136 | RX_CLK          | 188 | VCC2_5  |

| 33  | PCI_CLK      | 85  | VCC3_3              | 137 | RXD8            | 189 | RSVD    |

| 34  | VCCP         | 86  | AD8                 | 138 | VCC2_5          | 190 | TDI     |

| 35  | GLOBAL_RST   | 87  | C/BE0               | 139 | RXD9            | 191 | TDO     |

| 36  | VCC3_3       | 88  | AD7                 | 140 | RXD10           | 192 | TMS     |

| 37  | AD31         | 89  | AD6                 | 141 | GND             | 193 | TCK     |

| 38  | AD30         | 90  | VCC3_3              | 142 | RXD11           | 194 | GND     |

| 39  | AD29         | 91  | AD5                 | 143 | RXD12           | 195 | TRST    |

| 40  | VCC3_3       | 92  | AD4                 | 144 | VCC2_5          | 196 | VCC3_3  |

| 41  | AD28         | 93  | AD3                 | 145 | RXD13           | 197 | SCL     |

| 42  | C/BE3        | 94  | GND                 | 146 | RXD14           | 198 | SDA     |

| 43  | IDSEL        | 95  | AD2                 | 147 | GND             | 199 | GPE     |

| 44  | GND          | 96  | AD1                 | 148 | RXD15           | 200 | REG33   |

| 45  | AD27         | 97  | AD0                 | 149 | RX_DV           | 201 | REG18   |

| 46  | AD26         | 98  | VCC3_3              | 150 | RX_ER/PRBS_PASS | 202 | REG2_EN |

| 47  | AD25         | 99  | EXT_CLK             | 151 | VCC2_5          | 203 | GPIO0   |

| 48  | VCC3_3       | 100 | REG1_EN             | 152 | PRBSEN          | 204 | GPIO1   |

| 49  | AD24         | 101 | REG33               | 153 | RSVD            | 205 | GPIO2   |

| 50  | AD23         | 102 | REG18               | 154 | RSVD            | 206 | GPIO3   |

| 51  | AD22         | 103 | GND                 | 155 | GND             | 207 | EXTARB  |

| 52  | GND          | 104 | EXT_CLK_SEL         | 156 | RSVD            | 208 | PRI/SEC |

|     |              |     |                     |     |                 |     |         |

Table 2–1. Terminal Signal Names Sorted by Terminal Number

| TERMINAL NAME | NO.      | TERMINAL NAME | NO. | TERMINAL NAME   | NO.       | TERMINAL NAME  | NO. |

|---------------|----------|---------------|-----|-----------------|-----------|----------------|-----|

| ADO           | 97       | GLOBAL_RST    | 35  | PERR            | 71        | TDO            | 191 |

| AD1           | 96       | GND           | 2   | PRBSEN          | 152       | TLK CLK        | 173 |

| AD2           | 95       | GND           | 19  | PRI/SEC         | 208       | TMS            | 192 |

| AD3           | 93       | GND           | 31  | REG1_EN         | 100       | TRDY           | 66  |

| AD4           | 92       | GND           | 44  | REG18           | 102       | TRST           | 195 |

| AD5           | 91       | GND           | 52  | REG18           | 201       | TXD0           | 187 |

| AD6           | 89       | GND           | 53  | REG2_EN         | 202       | TXD1           | 186 |

| AD7           | 88       | GND           | 61  | REG33           | 101       | TXD2           | 184 |

| AD7           | 86       | GND           | 73  | REG33           | 200       | TXD2<br>TXD3   | 183 |

| AD9           | 84       | GND           | 81  | REQO            | 30        | TXD4           | 181 |

| AD10          | 83       | GND           | 94  | REQ1            | 29        | TXD4           | 180 |

| AD10          | 82       | GND           | 103 | REQ2            | 28        | TXD6           | 178 |

| AD12          | 80       | GND           | 115 | REQ3            | 20        | TXD0           | 177 |

| AD12<br>AD13  | 78       | GND           | 123 | REQ3            | 26        | TXD7           | 171 |

| AD13<br>AD14  | 76       | GND           | 123 | REQ5            | 20        | TXD9           | 170 |

| AD14<br>AD15  | 76       | GND           | 135 | REQ5            | 24        | TXD10          | 169 |

| AD15          | 60       | GND           | 141 | REQ0            | 23        | TXD10          | 167 |

| AD10          | 59       | GND           | 141 | REQ7            |           | TXD12          | 166 |

|               | 59       | GND           | 147 | RSVD            | 21<br>8   | TXD12<br>TXD13 | -   |

| AD18          |          | GND           | 165 | RSVD            |           | TXD13          | 164 |

| AD19          | 56<br>55 | GND           | 172 | RSVD            | 20<br>105 | TXD14<br>TXD15 | 163 |

| AD20          |          |               |     |                 |           |                | 161 |

| AD21          | 54       | GND           | 174 | RSVD            | 153       | TX_EN          | 160 |

| AD22          | 51       | GND           | 179 | RSVD            | 154       | TX_ER          | 158 |

| AD23          | 50       | GND           | 185 | RSVD            | 156       | VCCP           | 34  |

| AD24          | 49       | GND           | 194 | RSVD            | 157       | VCCP           | 79  |

| AD25          | 47       | GNT0          | 18  | RSVD            | 189       | VCC2_5         | 126 |

| AD26          | 46       | GNT1          | 17  | RX_CLK          | 136       | VCC2_5         | 132 |

| AD27          | 45       | GNT2          | 16  | RXD0            | 124       | VCC2_5         | 138 |

| AD28          | 41       | GNT3          | 15  | RXD1            | 125       | VCC2_5         | 144 |

| AD29          | 39       | GNT4          | 14  | RXD2            | 127       | VCC2_5         | 151 |

| AD30          | 38       | GNT5          | 12  | RXD3            | 128       | VCC2_5         | 162 |

| AD31          | 37       | GNT6          | 11  | RXD4            | 130       | VCC2_5         | 168 |

| C/BE0         | 87       | GNT7          | 10  | RXD5            | 131       | VCC2_5         | 176 |

| C/BE1         | 74       | GNT8          | 9   | RXD6            | 133       | VCC2_5         | 182 |

| C/BE2         | 62       | GPE           | 199 | RXD7            | 134       | VCC2_5         | 188 |

| C/BE3         | 42       | GPIO0         | 203 | RXD8            | 137       | VCC3_3         | 7   |

| CLKOUT0       | 122      | GPIO1         | 204 | RXD9            | 139       | VCC3_3         | 13  |

| CLKOUT1       | 121      | GPIO2         | 205 | RXD10           | 140       | VCC3_3         | 25  |

| CLKOUT2       | 120      | GPIO3         | 206 | RXD11           | 142       | VCC3_3         | 36  |

| CLKOUT3       | 118      | HS_ENUM       | 107 | RXD12           | 143       | VCC3_3         | 40  |

| CLKOUT4       | 117      | HS_LED        | 109 | RXD13           | 145       | VCC3_3         | 48  |

| CLKOUT5       | 116      | HS_SWITCH     | 108 | RXD14           | 146       | VCC3_3         | 57  |

| CLKOUT6       | 114      | IDSEL         | 43  | RXD15           | 148       | VCC3_3         | 65  |

| CLKOUT7       | 113      | INTA          | 6   | RX_DV           | 149       | VCC3_3         | 69  |

| CLKOUT8       | 112      | INTB          | 5   | RX_ER/PRBS_PASS | 150       | VCC3_3         | 77  |

| CLKOUT9       | 111      | INTC          | 4   | SCL             | 197       | VCC3_3         | 85  |

| CRC_EN        | 1        | INTD          | 3   | SDA             | 198       | VCC3_3         | 90  |

| DEVSEL        | 67       | IRDY          | 64  | SERR            | 72        | VCC3_3         | 98  |

| EXTARB        | 207      | LOOP_EN       | 159 | STOP            | 68        | VCC3_3         | 106 |

| EXT_CLK       | 99       | PAR           | 70  | SYS_CLK         | 175       | VCC3_3         | 110 |

| EXT_CLK_SEL   | 104      | PCI_CLK       | 33  | ТСК             | 193       | VCC3_3         | 119 |

| FRAME         | 63       | PCI_RST       | 32  | TDI             | 190       | VCC3_3         | 196 |

Table 2–2. Terminal Signal Names Sorted Alphabetically to Terminal Number

Table 2–3 lists the PCI system terminals and describes their function.

| TERMINAI   | L   |      | <b>EUNOTION</b>                                                                                                                                                                                                                                                                                                           |

|------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME       | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                  |

| GLOBAL_RST | 35  | I    | Global reset. GLOBAL_RST is used to initialize the PCI6050 device to its default state after power is applied.<br>This reset must be supplied to both the primary and secondary nodes in order for the serial link to be<br>established. Note that GLOBAL_RST serves as the only reset input to a secondary PCI6050 node. |

| PCI_CLK    | 33  | I    | PCI clock. PCI_CLK provides timing for all PCI transactions with a maximum frequency of 33 MHz. All PCI bus signals are sampled at rising edge of PCI_CLK.                                                                                                                                                                |

| PCI_RST    | 32  | I/O  | PCI reset. For a primary PCI6050 node, PCI_RST is an input that causes the bridge to put all output buffers in a high-impedance state and reset all internal registers. For a secondary PCI6050 node, PCI_RST is the output to the secondary PCI bus that initiates a bus reset.                                          |

### Table 2–3. PCI System

Table 2–4 lists the PCI address and data terminals and describes their function.

| TERMIN | TERMINAL |      |                                                                                                                |

|--------|----------|------|----------------------------------------------------------------------------------------------------------------|

| NAME   | NO.      | TYPE | FUNCTION                                                                                                       |

| AD31   | 37       | I/O  | PCI address and data bus. The AD[31–0] signals make up the multiplexed PCI address and data bus on the         |

| AD30   | 38       |      | PCI interface. During the address phase of a PCI bus cycle, AD[31-0] contain a 32-bit address or other         |

| AD29   | 39       |      | destination information. During each data phase of the transaction, AD[31–0] contain data.                     |

| AD28   | 41       |      |                                                                                                                |

| AD27   | 45       |      |                                                                                                                |

| AD26   | 46       |      |                                                                                                                |

| AD25   | 47       |      |                                                                                                                |

| AD24   | 49       |      |                                                                                                                |

| AD23   | 50       |      |                                                                                                                |

| AD22   | 51       |      |                                                                                                                |

| AD21   | 54       |      |                                                                                                                |

| AD20   | 55       |      |                                                                                                                |

| AD19   | 56       |      |                                                                                                                |

| AD18   | 58       |      |                                                                                                                |

| AD17   | 59       |      |                                                                                                                |

| AD16   | 60       |      |                                                                                                                |

| AD15   | 75       |      |                                                                                                                |

| AD14   | 76       |      |                                                                                                                |

| AD13   | 78       |      |                                                                                                                |

| AD12   | 80       |      |                                                                                                                |

| AD11   | 82       |      |                                                                                                                |

| AD10   | 83       |      |                                                                                                                |

| AD9    | 84       |      |                                                                                                                |

| AD8    | 86       |      |                                                                                                                |

| AD7    | 88       |      |                                                                                                                |

| AD6    | 89       |      |                                                                                                                |

| AD5    | 91       |      |                                                                                                                |

| AD4    | 92       |      |                                                                                                                |

| AD3    | 93       |      |                                                                                                                |

| AD2    | 95       |      |                                                                                                                |

| AD1    | 96       |      |                                                                                                                |

| AD0    | 97       |      |                                                                                                                |

| C/BE3  | 42       | I/O  | PCI command and byte enables. During the address phase of a PCI bus cycle, C/BE3-C/BE0 defines the             |

| C/BE2  | 62       |      | bus command for the transaction. During the data phase, this 4-bit bus determines which byte lanes of the full |

| C/BE1  | 74       |      | 32-bit data bus carries meaningful data. C/BE0 applies to byte 0 (AD[7-0]), C/BE1 applies to byte 1            |

| C/BE0  | 87       |      | (AD[15–8]), C/BE2 applies to byte 2 (AD[23–16]), and C/BE3 applies to byte 3 (AD[31–24]).                      |

|        |          |      |                                                                                                                |

|        |          | -    | ·                                                                                                              |

## Table 2–4. PCI Address and Data

Table 2–5 describes the PCI interface control signals.

| TERMINAL                     |                  |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|------------------------------|------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                         | NO.              | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| DEVSEL                       | 67               | I/O  | PCI device select. DEVSEL is driven by the target of a PCI transaction to claim the cycle. As a PCI master, the PCI6050 device monitors DEVSEL until a target responds. If no target responds before the time-out condition occurs, then the bridge terminates the cycle with a master abort.                                                                                                                                                                       |  |  |  |

| FRAME                        | 63               | I/O  | PCI cycle frame. FRAME is driven by the master of a PCI bus cycle. FRAME is asserted to indicate that a bus transaction is beginning, and data transfers continue while this signal is asserted. When FRAME is deasserted, the primary bus transaction is in the final data phase.                                                                                                                                                                                  |  |  |  |

| GNTO                         | 18               | I/O  | PCI bus grant. For a primary PCI6050 node, GNT0 is the PCI bus grant input and is driven by the primary PCI bus arbiter to grant the bridge access to the primary PCI bus after the current data transaction has completed. For a secondary PCI6050 node, GNT0 is an output from the internal bus arbiter to another secondary bus master. If the internal arbiter is disabled (external arbiter), then this terminal is the secondary PCI6050 PCI bus grant input. |  |  |  |

| IDSEL                        | 43               | I    | PCI initialization and device select. IDSEL selects a primary PCI6050 node during configuration space accesses. IDSEL can be connected to one of the upper 24 PCI address lines on the primary PCI bus. This terminal is not used in secondary PCI6050 node applications and should be tied to a valid logic level.                                                                                                                                                 |  |  |  |

|                              |                  |      | Note: The configuration space of the PCI6050 device can only be accessed from the primary bus.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| INTD<br>INTC<br>INTB<br>INTA | 3<br>4<br>5<br>6 | I/O  | PCI interrupts. The PCI6050 device provides PCI interrupt routing from the secondary PCI bus to the primary PCI bus. The INTx terminals are inputs to a secondary PCI6050 node, which are transmitted to the primary PCI6050 node by way of the serial link. The primary PCI6050 node provides the interrupt information to the host system by way of the INTx terminal outputs.                                                                                    |  |  |  |

| IRDY                         | 64               | I/O  | PCI initiator ready. IRDY indicates ability of the PCI bus master to complete the current data phase of the transaction. A data phase is completed on a rising edge of PCI_CLK where both IRDY and TRDY are asserted. Until IRDY and TRDY are both sampled asserted, wait states are inserted.                                                                                                                                                                      |  |  |  |

| PAR                          | 70               | I/O  | PCI parity. In all primary bus read and write cycles, the bridge calculates even parity across the AD and C/BE buses. As a master during PCI write cycles, the bridge outputs this parity indicator with one PCI_CLK delay. As a target during PCI read cycles, the calculated parity is compared to the parity indicator driven by the master; a miscompare can result in a parity error assertion (PERR).                                                         |  |  |  |

| PERR                         | 71               | I/O  | PCI parity error. PERR is driven by a primary PCI6050 node when enabled through the command register to indicate that the calculated parity does not match the sampled PAR or that PERR was detected by the secondary PCI6050 node. For a secondary PCI6050 node, PERR is an input asserted by a secondary bus PCI device to indicate that calculated parity does not match the sampled PAR.                                                                        |  |  |  |

| REQO                         | 30               | I/O  | PCI bus request. For a primary PCI6050 node, REQ0 is the PCI bus request output and is driven by the PCI6050 device to request access to the primary PCI bus after the current data transaction has completed. For a secondary PCI6050 node, REQ0 is an input to the internal bus arbiter from another secondary bus master. If the internal arbiter is disabled (external arbiter), then this terminal is the secondary PCI6050 PCI bus request output.            |  |  |  |

| SERR                         | 72               | I/O  | PCI system error. SERR is driven by a primary PCI6050 node to indicate that a critical system error has occurred or that SERR was detected on one of the subordinate buses downstream from the secondary PCI6050 node. The assertion need not be from the target of the primary PCI cycle. For a secondary PCI6050 node, SERR is an input asserted by a secondary bus PCI device to indicate that a critical system error has occurred.                             |  |  |  |

| STOP                         | 68               | I/O  | PCI cycle stop. STOP is driven by a PCI target to request that the initiator stop the current PCI bus transaction. This signal is used for target disconnects and is commonly asserted by target devices which do not support multiple data transfers.                                                                                                                                                                                                              |  |  |  |

| TRDY                         | 66               | I/O  | PCI target ready. TRDY indicates the ability of the PCI bus target to complete the current data phase of the transaction. A data phase is completed upon a rising edge of PCI_CLK where both IRDY and TRDY are asserted. Until both IRDY and TRDY are both sampled asserted, wait states are inserted.                                                                                                                                                              |  |  |  |

## Table 2–5. PCI Interface Control

Table 2–6 describes the PCI clock signals; Table 2–7 describes the secondary PCI arbitration and control signals.

| TERMINAL           |            | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                           |

|--------------------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME               | NO.        | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                           |

| CLKOUT9<br>CLKOUT8 | 111<br>112 | 0    | PCI clocks outputs. CLKOUT[9–0] provide timing for all transactions on the secondary PCI bus. Each<br>secondary bus device samples all secondary PCI signals at the rising edge of its corresponding CLKOUT                                                                                                                        |

| CLKOUT7            | 113        |      | input. If CLKOUT[9–0] are utilized as PCI clock sources, then CLKOUT9 is fed back to the PCI_CLK input.                                                                                                                                                                                                                            |

| CLKOUT6<br>CLKOUT5 | 114<br>116 |      | Note: The CLKOUT9 feedback trace should exceed the length of other CLKOUT traces by 2.5 inches.                                                                                                                                                                                                                                    |

| CLKOUT4            | 117        |      |                                                                                                                                                                                                                                                                                                                                    |

| CLKOUT3            | 118        |      |                                                                                                                                                                                                                                                                                                                                    |

| CLKOUT2            | 120        |      |                                                                                                                                                                                                                                                                                                                                    |

| CLKOUT1            | 121        |      |                                                                                                                                                                                                                                                                                                                                    |

| CLKOUT0            | 122        |      |                                                                                                                                                                                                                                                                                                                                    |

| EXT_CLK            | 99         | I    | External clock. EXT_CLK is an optional 33-MHz PCI clock input from an external oscillator or clock source. This input is multiplexed with the internal 31.25-MHz (125 MHz divided by 4) clock and may be used for driving the CLKOUT terminals. When unused, this terminal should be tied to a valid logic level.                  |

| EXT_CLK_SEL        | 104        | I    | External clock select. EXT_CLK_SEL is used to select between an external 33-MHz clock source (EXT_CLK) and the internal 31.25-MHz (125 MHz divided by 4) clock as the CLKOUT terminal source. When EXT_CLK_SEL is high, the external clock is used. When EXT_CLK_SEL is low, the internal clock is used to drive CLKOUT terminals. |

#### Table 2–6. PCI Clock Distribution

| TERMINA | AL. |      | FUNCTION                                                                                                                                                                                                                                                                                                                             |

|---------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                             |

| GNT8    | 9   | 0    | Secondary PCI grants. When the internal arbiter is used, GNT8-GNT1 are outputs from the secondary                                                                                                                                                                                                                                    |

| GNT7    | 10  |      | PCI6050 node to other secondary bus masters to indicate when they are permitted to take ownership of the                                                                                                                                                                                                                             |

| GNT6    | 11  |      | bus. These terminals are not used in a primary PCI6050 node.                                                                                                                                                                                                                                                                         |

| GNT5    | 12  |      |                                                                                                                                                                                                                                                                                                                                      |

| GNT4    | 14  |      |                                                                                                                                                                                                                                                                                                                                      |

| GNT3    | 15  |      |                                                                                                                                                                                                                                                                                                                                      |

| GNT2    | 16  |      |                                                                                                                                                                                                                                                                                                                                      |

| GNT1    | 17  |      |                                                                                                                                                                                                                                                                                                                                      |

| REQ8    | 21  | I    | Secondary PCI requests. When the internal arbiter is used, REQ8-REQ1 are inputs from other secondary                                                                                                                                                                                                                                 |

| REQ7    | 22  |      | bus masters to indicate when they wish to take ownership of the bus. These terminals are not used in a prima-                                                                                                                                                                                                                        |

| REQ6    | 23  |      | ry PCI6050 node.                                                                                                                                                                                                                                                                                                                     |

| REQ5    | 24  |      |                                                                                                                                                                                                                                                                                                                                      |

| REQ4    | 26  |      |                                                                                                                                                                                                                                                                                                                                      |

| REQ3    | 27  |      |                                                                                                                                                                                                                                                                                                                                      |

| REQ2    | 28  |      |                                                                                                                                                                                                                                                                                                                                      |

| REQ1    | 29  |      |                                                                                                                                                                                                                                                                                                                                      |

| EXTARB  | 207 | I    | Secondary external arbiter. EXTARB indicates whether or not an external arbiter is used in a secondary PCI6050 application and has no usage in primary PCI6050 applications. When EXTARB is sampled high, the internal secondary bus arbiter is disabled. When EXTARB is low, the PCI6050 internal secondary bus arbiter is enabled. |

#### Secondary PCI Arbitration and Control Table 2-7

Table 2–8 describes the PCI6060 device clock and control interface signals; Table 2–9 describes the transmit data signals for the PCI6060 device.

| TERMIN  | AL  | -    |                                                                                                                                                                                                                                                                                                |

|---------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                                                       |

| SYS_CLK | 175 | I    | 125-MHz system clock. SYS_CLK is a 125-MHz clock input used to control the 16-bit transmit data path (TXD[15–0], TX_EN, and TX_ER) to the PCI6060 device. The PCI6050 device internally divides this clock by 4 to generate the 31.25-MHz clock which may be used for the CLKOUT[9–0] outputs. |

| TLK_CLK | 173 | 0    | 125-MHz reference clock. This output clock is synchronous to the 16-bit transmit data path (TXD[15–0], TX_EN, and TX_ER) and should be used as the transmit clock source for the PCI6060 device.                                                                                               |

| LOOP_EN | 159 | 0    | Loop enable. This output from the PCI6050 device can be connected to the PCI6060 LOOPEN terminal in order to allow the PCI6050 device to enable or disable its internal loop-back path.                                                                                                        |

| PRBSEN  | 152 | 0    | Pseudo-random bit stream enable. This output from the PCI6050 device can be connected to the PCI6060 PRBSEN terminal in order to allow the PCI6050 device to enable or disable its internal pseudo-random bit stream generator for loopback testing.                                           |

| RX_CLK  | 136 | I    | Receive clock. This 125-MHz clock is synchronous to the receive data path (RXD[15–0], RX_DV, and RX_ER) and is provided by the PCI6060 device.                                                                                                                                                 |

| Table 2-8. PCI6060 Clock a | and Control Interface |

|----------------------------|-----------------------|

|----------------------------|-----------------------|

| TERMIN | AL  | -    |                                                                                                                                                                                                                                                            |

|--------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | TYPE | FUNCTION                                                                                                                                                                                                                                                   |

| TXD15  | 161 | 0    | Transmit data. TXD[15–0] carries the 16-bit data stream from the PCI6050 device to the PCI6060 device.                                                                                                                                                     |

| TXD14  | 163 |      |                                                                                                                                                                                                                                                            |

| TXD13  | 164 |      |                                                                                                                                                                                                                                                            |

| TXD12  | 166 |      |                                                                                                                                                                                                                                                            |

| TXD11  | 167 |      |                                                                                                                                                                                                                                                            |

| TXD10  | 169 |      |                                                                                                                                                                                                                                                            |

| TXD9   | 170 |      |                                                                                                                                                                                                                                                            |

| TXD8   | 171 |      |                                                                                                                                                                                                                                                            |

| TXD7   | 177 |      |                                                                                                                                                                                                                                                            |

| TXD6   | 178 |      |                                                                                                                                                                                                                                                            |

| TXD5   | 180 |      |                                                                                                                                                                                                                                                            |

| TXD4   | 181 |      |                                                                                                                                                                                                                                                            |

| TXD3   | 183 |      |                                                                                                                                                                                                                                                            |

| TXD2   | 184 |      |                                                                                                                                                                                                                                                            |

| TXD1   | 186 |      |                                                                                                                                                                                                                                                            |

| TXD0   | 187 |      |                                                                                                                                                                                                                                                            |

| TX_EN  | 160 | 0    | Transmit data enable. TX_EN is driven by the PCI6050 device to indicate to the PCI6060 device when there is valid data on TXD[15–0]. This signal may also be used in conjunction with TX_ER to produce special control codes on the transceiver interface. |

| TX_ER  | 158 | 0    | Transmit error. This signal is used in conjunction with TX_EN to produce special control codes on the transceiver interface.                                                                                                                               |

#### Table 2–9. PCI6060 Transmit Data Path

Table 2–10 describes the PCI6060 device receive data signals. Table 2–11 describes miscellaneous terminals on the PCI6050 device.

|                     |          | r    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|---------------------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TERMINA             | IERMINAL |      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| NAME                | NO.      | TYPE | TONCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| RXD15               | 148      | I    | Receive data. RXD[15–0] carries the 16-bit data stream from the PCI6060 device to the PCI6050 device.                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| RXD14               | 146      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD13               | 145      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD12               | 143      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD11               | 142      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD10               | 140      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD9                | 139      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD8                | 137      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD7                | 134      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD6                | 133      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD5                | 131      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD4                | 130      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD3                | 128      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD2                | 127      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD1                | 125      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RXD0                | 124      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RX_DV               | 149      | I    | Receive data valid. RX_DV is driven by the PCI6060 device to indicate to the PCI6050 device when there is valid data on RXD[15–0]. This signal may also be used in conjunction with RX_ER to determine when there are special control codes on the receiver interface or when a receiver error has occurred.                                                                                                                                                                              |  |  |

| RX_ER/<br>PRBS_PASS | 150      | I    | Receive error/status of PRBS test. The RX_ER may be used along with RX_DV by the PCI6050 device to determine when a special control code or transmit error was received by the PCI6060 device. The PRBS_PASS input from the PCI6060 device indicates whether the internal loop-back of pseudo-random data passed or failed. A primary PCI6050 device provides a mechanism to enable and read the status of the PRBS loop-back test via the transceiver test control and status registers. |  |  |

#### Table 2–10. PCI6060 Receive Data Path

#### Table 2–11. Miscellaneous Terminals