# THS56X1EVM for the THS5641/51/61/71 8-Bit, 10-Bit, 12-Bit, and 14-Bit CommsDAC™ Digital-to-Analog Converters

# User's Guide

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

#### **Preface**

## **Read This First**

#### About This Manual

This user's guide describes the characteristics, operation, and use of the THS56X1 evaluation module (EVM).

#### How to Use This Manual

This document contains the following chapters:

Chapter 1 – EVM Overview

Chapter 2 – Getting Started

Chapter 3 – User Configurations

Chapter 4 – Control Modes

Chapter 5 – Software

#### Related Documentation From Texas Instruments

To obtain a copy of any of the following TI documents, call the Texas Instruments Literature Response Center at (800) 477–8924 or the Product Information Center (PIC) at (972) 644–5580. When ordering, please identify the book by its title and literature number if possible.

#### **Data Sheets:**

| LT1004           | Literature No. SLVS022H |

|------------------|-------------------------|

| THS3001          | Literature No. SLOS217A |

| SN74LVT245B      | Literature No. SCES004C |

| SN74AHCT1G08DBVR | Literature No. SCLS316G |

| SN74ALVC08D      | Literature No. SCES101D |

| SN74AHCTIG32     | Literature No. SCLS320G |

| THS5671          | Literature No. SLAS201  |

| THS5661          | Literature No. SLAS200A |

| THS5651          | Literature No. SLAS197A |

| THS5641          | Literature No. SLAS199A |

#### **CE/FCC Warning**

This equipment is intended for use in a laboratory test environment only. It generates, uses, and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to subpart J of part 15 of FCC rules. This device has been tested and found to comply with the limits for a CISPRII Group 1 and the following directives: EMC Directive 89/336/EEC amending directive 92/31/EEC and 93/68/EEC as per ENV50204: 1995, EN55011: 1995 Class A, EN61000–4-4: 1995, and EN6100–4-3: 1993. Operation of this equipment in other environments may cause interference with radio communications, in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.

#### Trademarks

TI is a trademark of Texas Instruments Incorporated.

SPI and WSPI are trademarks of Motorola, Inc.

# **Contents**

| 1 | EVM   | Overvie  | ew                                                  | 1-1 |

|---|-------|----------|-----------------------------------------------------|-----|

|   | 1.1   | Syster   | m Block Diagram                                     | 1-2 |

|   | 1.2   |          | nsDAC System Description                            |     |

|   |       | 1.2.1    | THS5671/THS5661/THS5651/THS5641 CommsDAC            | 1-3 |

|   |       | 1.2.2    | Control/Interface                                   | 1-4 |

|   |       | 1.2.3    | Output Stage                                        | 1-4 |

|   | 1.3   | EVM C    | Operating Modes                                     | 1-4 |

|   |       | 1.3.1    | C542/C54xx DSK/Microprocessor Mode                  | 1-4 |

|   |       | 1.3.2    | Pattern Generator Mode                              | 1-4 |

|   |       | 1.3.3    | Analog Output                                       | 1-5 |

|   | 1.4   | Power    | and Cabling Requirements                            | 1-5 |

|   | 1.5   | Printed  | d Circuit Assembly as Part of a System              | 1-5 |

|   |       | 1.5.1    | C542/C54xx DSK/Microprocessor Mode                  | 1-5 |

|   |       | 1.5.2    | Pattern Generator Mode                              | 1-5 |

|   |       | 1.5.3    | CommsDAC Output Configurations                      | 1-9 |

|   | 1.6   | Printed  | d Circuit Assembly Options Available                | 1-9 |

| 2 | Getti | ng Stari | ted                                                 | 2-1 |

|   | 2.1   | _        | cal Description                                     |     |

|   | 2.2   | Parts I  | List                                                | 2-5 |

| 3 | User  | Config   | urations                                            | 3-1 |

| • | 3.1   | _        | natic Diagram                                       |     |

|   | 3.2   |          | Options                                             |     |

|   | 3.3   |          | g/Digital Supply Voltages                           |     |

|   | 3.4   | -        | Input Configurations                                |     |

|   |       | 3.4.1    | Apply DSP Signals to THS56X1 CommsDAC               |     |

|   |       | 3.4.2    | Apply Pattern Generator Signals to THS56X1 CommsDAC |     |

|   | 3.5   | _        | ating a Voltage Reference                           |     |

|   |       | 3.5.1    | Internal Reference                                  |     |

|   |       | 3.5.2    | Onboard External Reference                          |     |

|   | 3.6   | Extern   | al Clock                                            |     |

|   |       | 3.6.1    | External Clock Generation                           |     |

|   |       | 3.6.2    | C542/C54xxDSK/Microprocessor Mode                   |     |

|   |       | 3.6.3    | Analog Output Circuits                              |     |

|   | 27    |          | ector Din and Function Assignments                  |     |

#### Contents

| 4 | Contr | ol Modes        | 4-1 |

|---|-------|-----------------|-----|

|   | 4.1   | SLEEP Input Pin | 4-2 |

|   | 4.2   | MODE Input Pin  | 4-2 |

|   | 4.3   | BIASJ Input Pin | 4-2 |

|   | 4.4   | EXTLO Input Pin | 4-2 |

|   | 4.5   | EXTIO Input Pin | 4-2 |

| 5 | Softw | /are            | 5-1 |

# **Figures**

| 1–1 | THS56X1 Block Diagram                                                              | 1-2 |

|-----|------------------------------------------------------------------------------------|-----|

| 1–2 | Mating of Connectors on the THS56X1 EVM to the Tektronix HFS9009 Pattern Generator |     |

| 1–3 | Mating of Connectors on the THS56X1 EVM to the SMA-Ribbon Cable Adapter            |     |

| 1–4 | Mating of Connectors on the C542DSK to the C542 DSKplus                            | 1-8 |

| 1–5 | Connecting the THS56X1 Outputs to J8 and J9                                        | 1-9 |

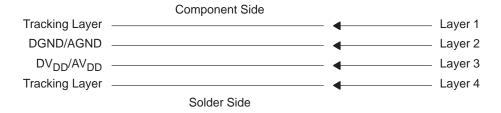

| 2–1 | PWB Layers                                                                         |     |

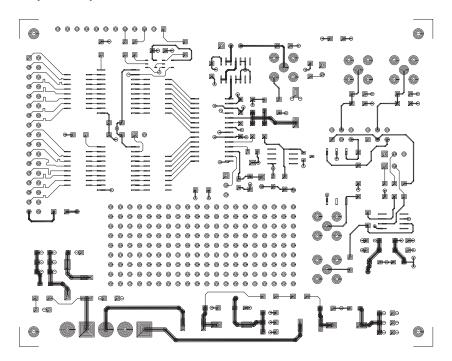

| 2–2 | Board Layout, Layer 1                                                              |     |

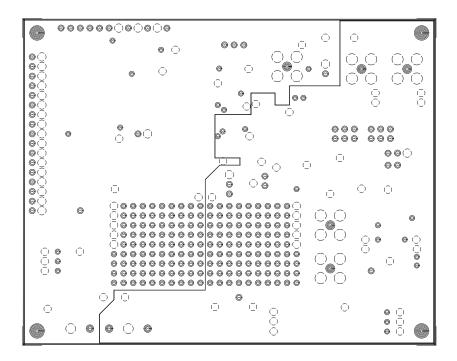

| 2–3 | Board Layout, Layer 2                                                              |     |

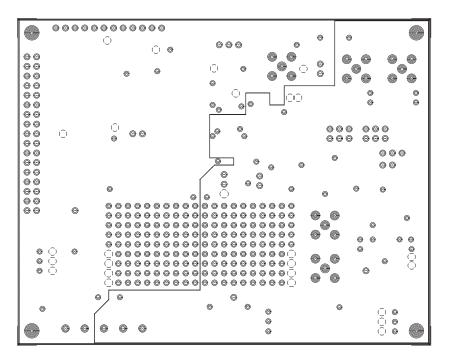

| 2–4 | Board Layout, Layer 3                                                              |     |

| 2–5 | Board Layout, Layer 4                                                              | 2-4 |

| 2–6 | Silk Screen                                                                        |     |

| 3–1 | EVM Schematic Diagram                                                              |     |

| 3–2 | Reconfiguration Hardware Location                                                  |     |

| 3–3 | Direct Connect Jumper Configuration for THS56X1                                    |     |

| 3–4 | Jumper Configuration for Internal Reference Voltage                                |     |

| 3–5 | Jumper Configuration for External Reference                                        |     |

| 3–6 | External Clock Signal                                                              |     |

# **Tables**

| 3–1  | Jumper Functions                                   | 3-4 |

|------|----------------------------------------------------|-----|

| 3–2  | Analog Voltage Supply Configuration Options        |     |

| 3–3  | Digital Input Options                              |     |

| 3–4  | Shipping Condition of Jumpers W1 Through W9        |     |

| 3–5  | Jumper Configuration for Internal Reference        |     |

| 3–6  | Jumper Configuration for External VREF             | 3-8 |

| 3–7  | Connector Pin and Function Assignments             |     |

| 3–8  | J4 and J2 Power Connectors                         |     |

| 3–9  | J6, J7, J8, and J9 Analog Output Signal Connectors |     |

| 3–10 | J3 C542/C54xxDSK/Microprocessor Control Connector  |     |

| 3–11 | J1 Parallel Data Connector                         |     |

| 3–12 | Function of Connector J5                           |     |

### **Chapter 1**

## **EVM Overview**

This user's guide describes the characteristics, operation, and use of the THS56X1 evaluation module (EVM). The THS56X1 EVM, connected to the TMS320C542/TMS320C54xx DSP and controlled by very user friendly software – Tl's Code Composer Development Environment – or to a pattern generator. This gives the user possibilities to measure the performance of the CommsDAC, to evaluate different types of DAC output interface circuits, and to evaluate external voltage reference (Vref) suitable for use with the THS56X1 family of digital-to-analog converter (CommsDAC). The CommsDAC family consists of the pin compatible 8-bit resolution THS5641, 10-bit resolution THS5651, 12-bit resolution THS5661 and 14-bit resolution THS5671 digital-to-analog converter (DAC).

| Topi | c Page                                           |

|------|--------------------------------------------------|

| 1.1  | System Block Diagram 1-2                         |

| 1.2  | CommsDAC System Description                      |

| 1.3  | EVM Operating Modes 1-4                          |

| 1.4  | Power and Cabling Requirements 1-5               |

| 1.5  | Printed Circuit Assembly as Part of a System 1-5 |

| 1.6  | Printed Circuit Assembly Options Available 1-9   |

#### 1.1 System Block Diagram

The THS56X1 EVM provides a practical platform for evaluating the following devices:

- ☐ THS5671 14-bit resolution, 100 MSPS CommsDAC

- ☐ THS5661 12-bit resolution, 100 MSPS CommsDAC

- ☐ TLV5651 10-bit resolution, 100 MSPS CommsDAC

- ☐ THS5641 8-bit resolution, 100 MSPS CommsDAC

The EVM supports the SOIC (DW) package style, but all devices are available in other packages (see Table 1–1).

Table 1-1. Package Styles Available

| Device  | DA Package <sup>†</sup><br>Supported? | DW Package <sup>‡</sup><br>Supported? | PW Package <sup>§</sup><br>Supported? |

|---------|---------------------------------------|---------------------------------------|---------------------------------------|

| THS5671 | No                                    | Yes, 28 pins                          | Yes, 28 pins                          |

| THS5661 | No                                    | Yes, 28 pins                          | Yes, 28 pins                          |

| THS5651 | No                                    | Yes, 28 pins                          | Yes, 28 pins                          |

| THS5641 | No                                    | Yes, 28 pins                          | Yes, 28 pins                          |

The DA package is a TSSOP device, with pins on a 0.65-mm pitch.

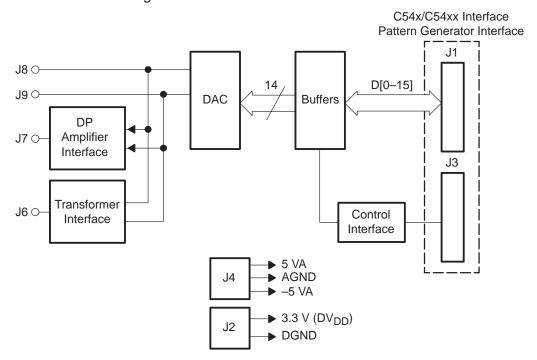

A block diagram for the THS56X1 EVM is drawn in Figure 1–1. The important features of each component of the block diagram are discussed at length in Section 1.2.

Figure 1-1. THS56X1 Block Diagram

<sup>&</sup>lt;sup>‡</sup> The DW package is a small outline (SOIC) device, with pins on a 1.27–mm pitch.

<sup>§</sup> The PW package is a TSSOP device, with pins on a 0.65–mm pitch.

Figure 1–1 comprises two input buffers, CommsDAC control logic, a CommsDAC, an external Vref, a transformer, and an operational amplifier(op amp). This illustration provides a general overview of the EVM. It is not meant to replace the circuit diagram, but to give a brief indication of the features and functions available. It should be read in combination with the circuit diagram supplied and the device data sheet SLAS200A.

#### 1.2 CommsDAC System Description

| This printed wiring board (PWB) EVM supports four digital-to-analog converters (DACs). |

|----------------------------------------------------------------------------------------|

| ☐ THS5641                                                                              |

| ☐ THS5651                                                                              |

| ☐ THS5661                                                                              |

| ☐ THS5671                                                                              |

| The resolution is the main difference between these parts.                             |

Table 1–2. General ADC Features

| Device  | Resolution | Output<br>Channels | Supports<br>Vref_int/<br>Vref_Ext | Throughput<br>VDD =3.3V | Throughput<br>VDD= 5 V | Available<br>Package | EVM Order<br>Number |

|---------|------------|--------------------|-----------------------------------|-------------------------|------------------------|----------------------|---------------------|

| THS5571 | 14-bit     | 2                  | Yes                               | 67 MSPS                 | 100 MSPS               | DW/PW                | THS5671             |

| THS5661 | 12-bit     | 2                  | Yes                               | 67 MSPS                 | 100 MSPS               | DW/PW                | THS5661             |

| THS5651 | 10-bit     | 2                  | Yes                               | 67 MSPS                 | 100 MSPS               | DW/PW                | THS5651             |

| THS5641 | 8-bit      | 2                  | Yes                               | 67 MSPS                 | 100 MSPS               | DW/PW                | THS5641             |

General features of these DACs are given in Table 1–2.

#### 1.2.1 THS5671/THS5661/THS5651/THS5641 CommsDAC

The low-power CMOS CommsDAC device integrates a 1.2-V bandgap reference, a current-source-array, a control amplifier, output current switches, and input latches/logic for controlling the differential output current switches. The device has good linearity and excellent SFDR specs, symmetrical output ON/OFF switching, differential output and can directly drive a 50 Ohms load. The CommsDAC family consists of pin compatible 14-, 12-, 10-, and 8-bit DACs all devices offer identical user interface and operate from an analog supply of 5 V and a digital supply of 3.3 V or 5 V. The THS56X1 full-scale current is adjustable from 2 mA to 20 mA. Power dissipation at 5 V is less than 175 mW and in sleep mode the standby power is about 25 mW. The THS56X1 is driven by the on-chip voltage reference or by an external voltage reference.

Any of the digital-to-analog converter (DAC) present on the EVM can be used to process the output of a parallel output ADC or as an independent device driven by either a pattern generator or a DSP starter kit (DSK) board.

#### 1.2.2 Control/Interface

The control signals can be derived from either a DSK/microprocessor or a dedicated GND and 3-V to 5-V supply connected to J3. The signals from either source are similar. The decision regarding which host system to use is left to of the user.

#### 1.2.3 Output Stage

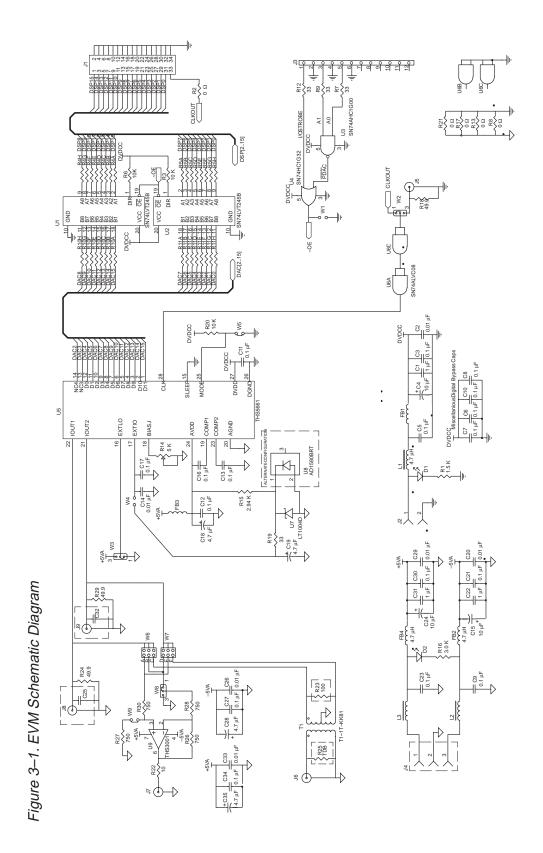

Several circuits for achieving a single-ended output from the DAC's differential outputs are designed into the THS56X1 EVM. Figure 3–1 shows the arrangement of the output circuits.

#### 1.3 EVM Operating Modes

| The                                     | There are two modes of operation for the EVM: |  |  |  |  |

|-----------------------------------------|-----------------------------------------------|--|--|--|--|

|                                         | DSK/Microprocessor mode                       |  |  |  |  |

|                                         | Pattern Generator mode                        |  |  |  |  |

| Each of these modes is discussed below. |                                               |  |  |  |  |

#### 1.3.1 C542/C54xx DSK/Microprocessor Mode

The C542/C54XX starter kit (DSK)/Microprocessor is used to supply the sample clock (CLKOUT), the EVM device-select control signals, and data via the 16-bit parallel data bus. The digital data sent to the DAC for conversion is usually stored in a lookup table—see the example program shown in Section 5. If the input digital data source can conveniently provide data and sample-clock, then the user must connect jumper W1 or make the following connections: J3 pin1 to J3 pin2, J2 pin 3 and pin 5 tied to either 3.3 V or 5 V in order to enable the SN74LVT245B buffers.

W5 is used to set the THS56X1 CommsDAC operating modes. Mode 0 (W5, closed) configures the device for binary input data word format. Mode 1 (W5, opened) sets a twos (2s) complement input data word format.

#### 1.3.2 Pattern Generator Mode

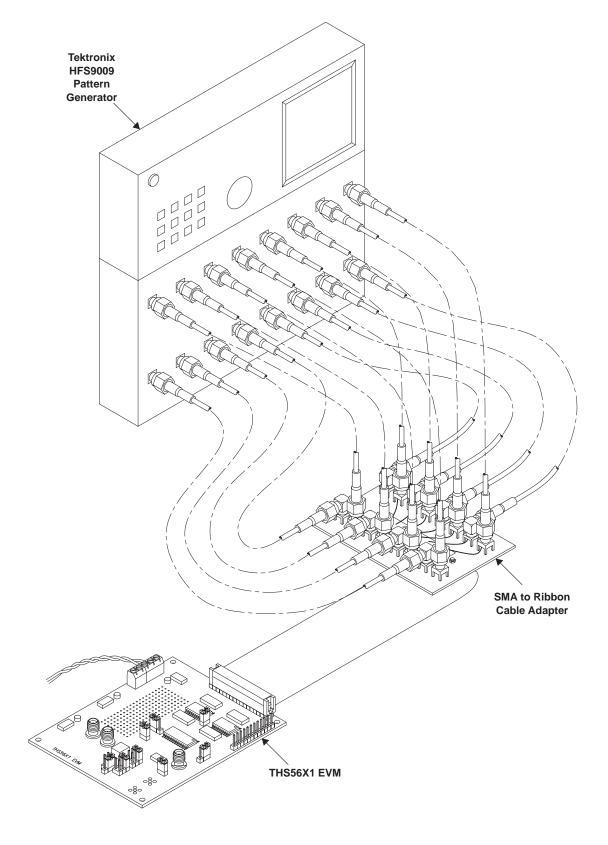

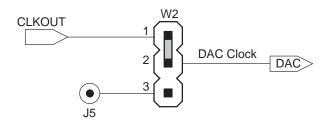

A pattern generator, similar to the Tektronix HFS9009, can be used to supply the input digital data stream and sample clock. The EVM device select signal is provided via J3 or W1. The pattern generator is programmed, typically, to output a sine wave and the appropriate sample clock (either 100 MHz or 67 MHz). The clock feeds directly into SMA connector J5 and the digital data to J1 goes via a SMA-to-ribbon cable adapter (see Figure 1–2).

W5 is used to set the THS56X1 CommsDAC operating modes. Mode 0 ( W5, closed ) configures the device for binary input data word format. Mode 1 ( W5, opened) sets a twos (2s) complement input data word format.

#### 1.3.3 Analog Output

The techniques used in a design of this type are different from those used in lower speed DACs. Single-ended analog output is derived from the THS56X1 CommsDAC differential outputs IOUT1 and IOUT2 via a 1:1 RF transformer. A THS3001 operational amplifier (op amp) is a convenient way to derive a buffered noninverting single-ended output, a buffered inverting single-ended output, or a buffered differential to single-ended output.

#### 1.4 Power and Cabling Requirements

The EVM dc supply voltages are analog ±5 V and digital 3 V or 5 V. These voltages should be supplied to the EVM through shielded twisted-pair wire for best performance. This type of power cabling minimizes any stray or transient pickup from the higher-frequency digital circuitry. If ribbon cables are used for interfacing to both J1 and J3, the crosstalk between adjacent conductors is minimized if shielded ribbon cables are used.

#### 1.5 Printed Circuit Assembly as Part of a System

#### 1.5.1 C542/C54xx DSK/Microprocessor Mode

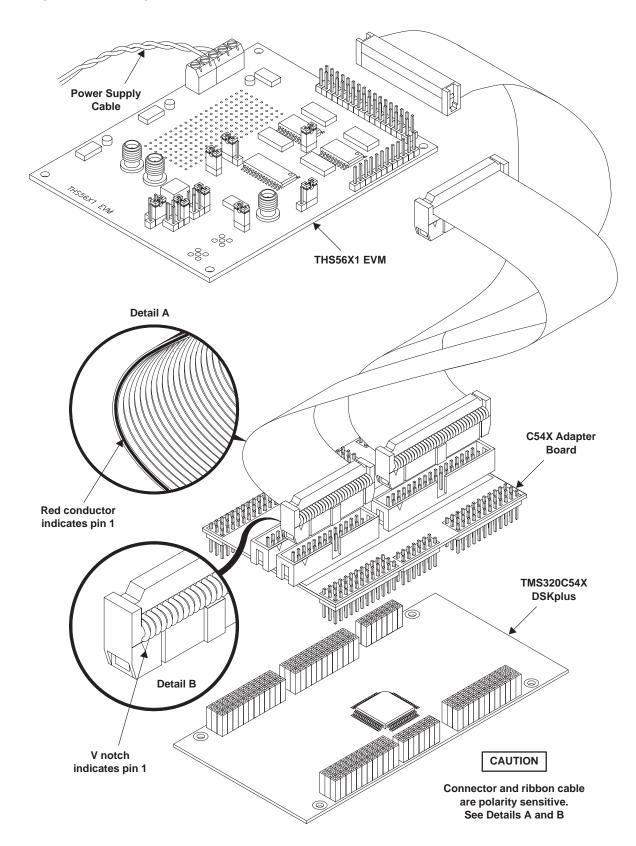

In this mode the DSP or microprocessor supplies data, sample clock, and control signals via J1 and J3, respectively. W2 is set to positions 1-2, and W1, W3, W5, W6 – W9 are set appropriately (see the User Configuration section of this document and Figure 1–4).

#### 1.5.2 Pattern Generator Mode

In this mode the pattern generator (Tektronix HFS9009) supplies data and sample clock signals to J1 and J5, respectively. Shown in Figure 1-2 the mating of the pattern generator adapter and the THS56X1 EVM connector J1, and control is provided via J3.

Figure 1–2. Mating of Connectors on the THS56X1 EVM to the Tektronix HFS9009 Pattern Generator

SMA to Ribbon

Cable Adapter

THS56X1 EVM

Figure 1–3. Mating of Connectors on the THS56X1 EVM to the SMA–Ribbon Cable Adapter

Figure 1-4. Mating of Connectors on the C542DSK to the C542 DSKplus

#### 1.5.3 CommsDAC Output Configurations

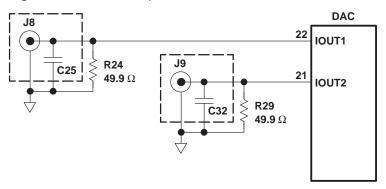

The THS56X1 CommsDAC output can be configured as single-ended outputs or as a differential output (see also THS5661, 12-bit, 100MSPS, CommsDAC data sheet SLAS200). Differential output configuration requires IOUT1 and IOUT2 to feed directly into SMA connectors, J8 and J9 (see Figure 1-5).

Figure 1–5. Connecting the THS56X1 Outputs to J8 and J9

#### 1.6 Printed Circuit Assembly Options Available

To ensure the flexibility of the printed-circuit board (PCB), four possible CommsDACs featured in this series are described in Table 1-3.

Table 1-3. Possible DACs

| DAC Part No. | No. of Bits | Speed    | EVM Order No. |

|--------------|-------------|----------|---------------|

| THS5671      | 14          | 100 MSPS | THS5671       |

| THS5661      | 12          | 100 MSPS | THS5661       |

| THS5651      | 10          | 100 MSPS | THS5651       |

| THS5641      | 8           | 100 MSPS | THS5641       |

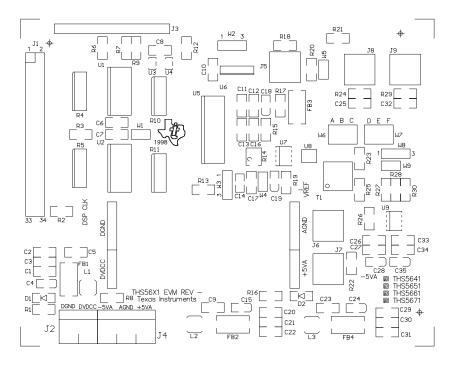

Ensure that the printed-circuit assembly (PCA) has the correct check mark on the silkscreen.

Each PCA may have additional hardware to install, if appropriate.

# Chapter 2

# **Getting Started**

This chapter describes the physical characteristics and PCB layout of the EVM, and lists the components used on the module.

| Topic |     | c Pag                | age |  |

|-------|-----|----------------------|-----|--|

|       | 2.1 | Physical Description | 2   |  |

|       |     | Parts List 2-5       |     |  |

#### 2.1 Physical Description

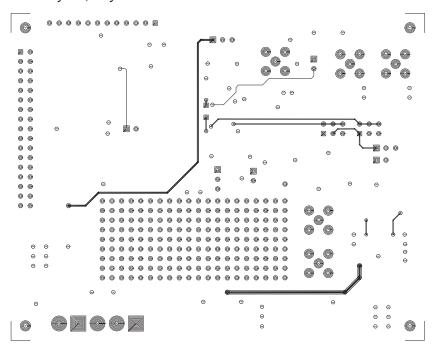

The PWB is constructed in four layers as shown in the following illustrations. The dimensions of the PWB are 4.25 in  $\times$  3.375 in (107.95 mm  $\times$  85.73 mm). See Figure 2–1.

Figure 2–1. PWB Layers

Figures 2–2 through 2–5 show the tracking for each layer.

Figure 2-2. Board Layout, Layer 1

Figure 2-3. Board Layout, Layer 2

Figure 2–4. Board Layout, Layer 3

Figure 2-5. Board Layout, Layer 4

Figure 2-6. Silk Screen

#### 2.2 Parts List

This table lists the parts required for the THS56X1 devices.

| QTY | REFERENCE DESIGNATION                                                               | PART NUMBER                  | DESCRIPTION                                   | MANUFACTURER       |

|-----|-------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------|--------------------|

| 3   | C1, C22, C31                                                                        | 1206ZC105KAT2A               | Ceramic 1 μF, 10 V,<br>X7R, 10%               | AVX                |

| 4   | C18, C19, C28, C35                                                                  | ECSTOJY475                   | 6.3 V, 4.7 μF, tantalum                       | Panasonic          |

| 3   | C15, C24, C4                                                                        | ECSTOJY106                   | 6.3 V, 10 μF, tantalum                        | Panasonic          |

| 0   | C25, C32                                                                            |                              | Ceramic, not installed,<br>50 V, X7R, 10%     |                    |

| 6   | C14, C2, C20, C26, C29, C33                                                         | 12065C103KAT2A               | Ceramic, 0.01 μF, 50<br>V, X7R, 10%           | AVX                |

| 17  | C10, C11, C12, C13, C16,<br>C17, C21, C23, C27, C3, C30,<br>C34, C5, C6, C7, C8, C9 | 12065C104KAT2A               | Ceramic, 0.1 μF, 50 V,<br>X7R, 10%            | AVX                |

| 2   | D1, D2                                                                              | AND/AND5GA or equivalent     | GREEN LED, 1206<br>size SM chip LED           |                    |

| 4   | FB1, FB2, FB3, FB4                                                                  | 27-43-037447                 | Fair-Rite SM beads<br>#27-037447              | FairRite           |

| 1   | J1                                                                                  | TSW-117-07-L-D or equivalent | 34-Pin header for IDC                         | Samtec             |

| 1   | J2                                                                                  | KRMZ2 or equivalent          | 2 Terminal screw con-<br>nector, 2TERM_CON    | Lumberg            |

| 1   | J3                                                                                  | TSW-112-07-L-S or equivalent | Single row 12-pin header                      | Samtec             |

| 1   | J4                                                                                  | KRMZ3 or equivalent          | 3 Terminal screw con-<br>nector               | Lumberg            |

| 3   | J5, J6, J7                                                                          | 142-0701-206 or equivalent   | PCB Mount SMA jack,<br>SMA_PCB_MT             | Johnson Components |

| 0   | J8, J9                                                                              | 142-0701-206 or equivalent   | PCB Mount SMA jack, not installed             | Johnson Components |

| 3   | L1, L2, L3                                                                          | DO1608C-472                  | DO1608C-series,<br>DS1608C-472                | Coil Craft         |

| 1   | R1                                                                                  | 1206                         | 1206 Chip resistor,<br>1.5K, 1/4 W, 1%        |                    |

| 4   | R10, R11, R4, R5                                                                    | CTS/CTS766-163-(R)330-G-TR   | 8-Element isolated resistor pack, 33 $\Omega$ |                    |

| 4   | R12, R19, R7, R9                                                                    | 1206                         | 1206 Chip resistor, 33<br>Ω, 1/4 W, 1%        |                    |

| 5   | R13, R17. R2, R21, R8                                                               | 1206                         | 1206 Chip resistor, 0<br>Ω, 1/4 W, 1%         |                    |

| 1   | R14                                                                                 | 3214W-1-502 E or equivalent  | 4 mm SM Pot, 5K                               | Bourns             |

| 1   | R15                                                                                 | 1206                         | 1206 Chip resistor,<br>2.94K, 1/4 W, 1%       |                    |

| 1   | R16                                                                                 | 1206                         | 1206 Chip resistor, 3K, 1/4 W, 1%             |                    |

| 3   | R18, R24, R29                                                                       | 1206                         | 1206 Chip resistor,<br>49.94K, 1/4 W, 1%      |                    |

| 3   | R20, R3, R6                                                                         | 1206                         | 1206 Chip resistor,<br>10K, 1/4 W, 1%         |                    |

Note: Manufacturer and part number data is supplied for reference only. Substitutions are permissible on all but TI parts.

| QTY            | REFERENCE DESIGNATION | PART NUMBER                           | DESCRIPTION                                        | MANUFACTURER |  |

|----------------|-----------------------|---------------------------------------|----------------------------------------------------|--------------|--|

| 1              | R22                   | 1206                                  | 1206 Chip resistor,<br>10K, 1/4 W, 1%              |              |  |

| 1              | R23                   | 1206                                  | 1206 Chip resistor,<br>100K, 1/4 W, 1%             |              |  |

| 1              | R25                   | 1206                                  | 1206 Chip resistor,<br>TBD, 1/4 W, 1%              |              |  |

| 4              | R26, R27, R28, R30    | 1206                                  | 1206 Chip resistor,<br>750K, 1/4 W, 1%             |              |  |

| 1              | T1                    | T1-1T-KK81                            | RF Transformer,<br>T1-1T-KK81                      | MiniCircuits |  |

| 2              | U1, U2                | SN74LVT245BDW                         | Octal bus transceiver,<br>3-state, SN74LVT245B     | TI           |  |

| 1              | U3                    | SN74AHCT1G00DBVR/<br>SN74AHC1G00DBVR  | Single gate NAND,<br>SN74AHC1G00                   | TI           |  |

| 1              | U4                    | SN74AHCT1G32DBVR/<br>SN74AHCC1G32DBVR | Single 2 input positive or gate, SN74AHC1G32       | ТІ           |  |

| 1†             | THS5641               | THS5641IDW                            | DAC, 2.7–5.5 V, 8 Bit,<br>125 MHz                  | TI           |  |

| 1 <sup>†</sup> | THS5651               | THS5651IDW                            | DAC, 2.7–5.5 V, 10<br>Bit, 125 MHz                 | TI           |  |

| 1†             | THS5661               | THS5661IDW                            | DAC, 2.7–5.5 V, 12<br>Bit, 125 MHz                 | ТІ           |  |

| 1†             | THS5671               | THS5647IDW                            | DAC, 2.7–5.5 V, 14<br>Bit, 125 MHz                 | TI           |  |

| 1              | SN74ALVC08            | SN74ALVC08D                           | Quad AND gate                                      | TI           |  |

| 1              | LT1004D               | LT1004CD-1-2/LT1004ID-1-2             | Precision 1.2 V reference                          | TI           |  |

| 0              | NOT INSTALLED         | AD1580BRT                             | Precision voltage reference, not installed         |              |  |

| 1              | THS3001               | THS3001CD/THS2001ID                   | THS3001 high-speed op amp                          | TI           |  |

| 4              | W1, W2, W5, W9        | TSW-102-07-L-S or equivalent          | 2 position jumper1" spacing, W2                    | Samtec       |  |

| 3              | W2, W3, W8            | TSW-102-07-L-S or equivalent          | 3 position jumper1" Samtec spacing, W3             |              |  |

| 2              | 2X3_JUMPER, W6, W7    | TSW-102-07-L-S or equivalent          | 6-Pin header dual row,<br>0.025×0.1,<br>2X3_JUMPER | Samtec       |  |

<sup>†</sup> See work order for proper part installation.

Note: Manufacturer and part number data is supplied for reference only. Substitutions are permissible on all but TI parts.

# Chapter 3

# **User Configurations**

This chapter describes the user-definable options.

| Горіс | C                                      | Page   |

|-------|----------------------------------------|--------|

| 3.1   | Schematic Diagram                      | 3-2    |

| 3.2   | User Options                           | 3-4    |

| 3.3   | Analog/Digital Supply Voltages         | 3-5    |

| 3.4   | Analog Input Configurations            | 3-6    |

| 3.5   | Generating a Voltage Reference         | 3-7    |

| 3.6   | External Clock                         | 3-9    |

| 3.7   | Connector Pin and Function Assignments | . 3-11 |

|       |                                        |        |

#### 3.1 Schematic Diagram

Figure 3–1 illustrates the EVM schematic.

User Configurations 3-3

#### 3.2 User Options

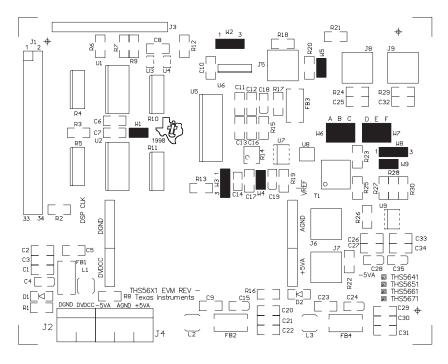

The PCA ships in a state that enables immediate evaluation of the digital-to-analog converter (DAC). However, you can reconfigure various options through hardware. This chapter discusses these options to ensure that any reconfiguration is conducted properly.

The hardware on the PCA falls into various groups:

☐ 18 jumpers

☐ 4 wire links

Table 3–1 lists jumper options, a brief description of each function, and information on where the option can be found.

Table 3–1. Jumper Functions

| Jumper<br>Reference | Function Description                                                                | Section         | Comment   |

|---------------------|-------------------------------------------------------------------------------------|-----------------|-----------|

| W1                  | ~OE input for the SN74LVT245B buffers                                               | 3.4/3.4.2       | Wire link |

| W2                  | Selects CLKOUT signal from the DSP or clock input from signal gen.                  | 3.8/3.8.1       |           |

| W3                  | Selects external or internal Vref.                                                  | 3.5.1/5.3.2     |           |

| W4                  | Supplies external Vref to the DAC                                                   | 3.5.1/<br>3.5.2 | Wire link |

| W5                  | Selects binary input mode or 2s complement input mode to the DAC                    | 4.2             | Wire link |

| W6                  | Selects IOUT1 or IOUT2 output from DAC to amplifier or transformer                  | 4.3             |           |

| W7                  | Selects IOUT1 or IOUT2 output from DAC to amplifier or transformer                  | 4.3             |           |

| W8                  | Configures the op amp for either differential input, noninverting or inverting mode | 3.8.3           |           |

| W9                  | Configures the op amp for inverting, noninverting or differential mode              | 3.8.3           | Wire link |

Figure 3–2 indicates the physical locations of this hardware.

Figure 3–2. Reconfiguration Hardware Location

#### 3.3 Analog/Digital Supply Voltages

Two options supply power to the digital section of the EVM:

- ☐ 3.3 V or 5V digital DVDD (for 5-V operation replace U1 and U2 with SN74HC245)

- ☐ 5-V only analog AVDD

Configure the power supply voltages in accordance with the following tables.

Table 3-2. Analog Voltage Supply Configuration Options

| J4        | J2          |

|-----------|-------------|

| J4-1 +5-V | J2-1 +3.3-V |

| J4–2 AGND | J2–2 DGND   |

| J4-2 -5-V |             |

#### 3.4 Digital Input Configurations

A variety of options are available to configure the analog inputs. This section describes these options, along with the jumper settings required.

The two alternatives for the analog inputs are given in the following table.

Table 3–3. Digital Input Options

| Analog Input Option                                                                | Connector Reference and Type |  |

|------------------------------------------------------------------------------------|------------------------------|--|

|                                                                                    | IDC                          |  |

| Option 1                                                                           |                              |  |

| Apply input data/clock from DSP to J1                                              | J1 – 2 x 17 plug             |  |

| Control signals from DSP to J3                                                     | J3 – 1 x 12 plug             |  |

| Option 2                                                                           |                              |  |

| Apply input data/clock from pattern generator via an adapter board to J1           | J1 – 2 x 17 plug             |  |

| For control signals connect J1–1 to J1–2 Connect +3.3 V to J3–3 and J2–5 (W1 open) | J3 – 1 x 12 plug             |  |

The user selects one of the above configurations based on the test equipment available. These are discussed below.

#### 3.4.1 Apply DSP Signals to THS56X1 CommsDAC

If you intend to implement a sine wave signal, as shown in the program in List 1, you will need to store values in a lookup table in the DSP onboard memory. The DSP sequentially outputs the data from the memory via the data bus to the commsDAC, where it is converted into an analog waveform.

DSP 16-bit wide data bus lines are provided via connector J1. Section 3.9 *Connects Pin and Function Assignments*, gives the pin assignments for J1. The THS56X1 EVM to C542 DSKplus interface is shown in Figure 1–4.

#### 3.4.2 Apply Pattern Generator Signals to THS56X1 CommsDAC

Digital inputs can also be taken directly from a pattern generator, via an adapter board, to connectors J1.

In this configuration the user should jumper J3 pin 1 to pin 2 and connect +5 V to J3 pin 3 and pin 5 or simply install W1.

5 VA W3 DAC **EXTLO** J1 D[2-15] D[0-15] D[0-13] W4 **IOUT 1 EXTIO**  $50 \Omega$ **BIASJ**  $DV_{DD}$ J1 Pin 33 MODE CLKOUT IOUT 2 W5 ≥ 50 Ω CLK DAC Clock

Figure 3–3. Direct Connect Jumper Configuration for THS56X1

Table 3-4. Shipping Condition of Jumpers W1 Through W9

| Jumper | Pins 1 and 2                   | Pins 2 and 3         |

|--------|--------------------------------|----------------------|

| W1     | Jumper not installed           | N/A                  |

| W2     | Jumper installed               | Jumper not installed |

| W3     | Jumper installed               | Jumper not installed |

| W4     | Jumper not installed           | N/A                  |

| W5     | Jumper installed               | N/A                  |

| W6     | W7 jumper positioin F to IOUT2 | N/A                  |

| W7     | W7 jumper position C to IOUT1  | N/A                  |

| W8     | Jumper not installed           | Jumper installed     |

| W9     | Jumper not installed           | N/A                  |

#### 3.5 Generating a Voltage Reference

Two options provide the voltage reference:

- ☐ Internal reference

- Onboard external reference

#### 3.5.1 Internal Reference

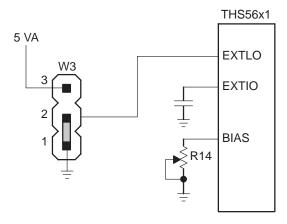

To set the THS56X1 to use the use the internal 1.2V on—chip Vref the jumper configuration is shown in Table 3–5. A drawing depicting the jumper placement is shown in Figure 3–4.

Table 3–5. Jumper Configuration for Internal Reference

| Jumper       | Pins 1 and 2                            | Pins 2 and 3 |  |

|--------------|-----------------------------------------|--------------|--|

| VREF setting |                                         |              |  |

| W3           | 3 Jumper installed Jumper not installed |              |  |

| W4           | Jumper not installed                    | N/A          |  |

Figure 3-4. Jumper Configuration for Internal Reference Voltage

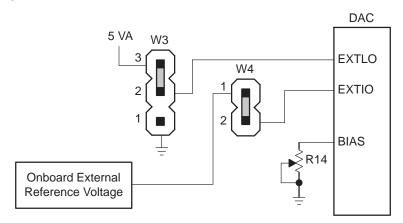

#### 3.5.2 Onboard External Reference

To select the onboard external reference voltage, the user should follow the jumper configuration shown in Table 3–6.

Table 3–6. Jumper Configuration for External VREF

| Jumper       | Pins 1 and 2         | Pins 2 and 3     |

|--------------|----------------------|------------------|

| VREF setting |                      |                  |

| W3           | Jumper not installed | Jumper installed |

| W4           | Jumper installed     | N/A              |

It is important to understand that the reference voltage plays a fundamental part in the conversion process. Changes in the value of the reference voltage are reflected in the full-scale range of the device. The variation in voltage for the reference should, ideally, contribute less than 1/2 an LSB of error to the total conversion process.

External reference voltages can be supplied via W4; see Table 3–5 for details.

Figure 3-5. Jumper Configuration for External Reference

Under no circumstance should the external reference voltage exceed 1.25 V.

#### 3.6 External Clock

The CommsDAC requires an external clock. There are two possible external sources for the clock required by the CommsDAC. To obtain optimum device performance the user should adhere to the minimum data to clock transition setup and hold times specified in the data sheet SLAS200A. Violating these timing parameters may result in increased converter output noise level. The choices are simple and are discussed in the following sections.

#### 3.6.1 External Clock Generation

The maximum operating speed of the CommsDAC is 100 MHz, when connected to an AVDD supply of 5 V, and DVDD supply of 5 V. When the DVDD supply is 3.3 V the maximum clock speed is 67 MHz. The clock signal comes from either the DSP CLKOUT signal or from the CLK output from a pattern generator via J5.

Figure 3–6. External Clock Signal

#### 3.6.2 C542/C54xxDSK/Microprocessor Mode

A DSP subsystem such as the C54X DSPplus/C5410 DSK provides some advantage when evaluating the DAC performance with signals, such as W-CDMA data points and arbitrary generated waveform data points. The clock frequency, via the 'C54x DSK adapter board, is set at 40 MHz.

#### 3.6.3 Analog Output Circuits

The 1:1 RF transformer is used for impedance matching, dc isolation and interfacing between the balanced differential CommsDAC outputs and an unbalanced single-ended output. The resistors R23, R24, and R29 are used to form a network that reflects  $50~\Omega$  across the primary circuit (J6).

Potentiometer R14 is used to set the CommsDAC full-scale output current. With R14 value set equal to 1.9 k $\Omega$  the full-scale current from the DAC is 20 mA.

A spectrum analyzer with  $50-\Omega$  input impedance is normally used to measure the performance of the DAC. A  $50-\Omega$  coaxial cable is used to connect J6 output to the  $50-\Omega$  input of the spectrum analyzer. The spectrum analyzer impedance is in parallel to the transformer  $50-\Omega$  reflected impedance across J6. Therefore, the voltage at the input of the spectrum analyzer is 1/2 J6. If a larger voltage is required, use a 1:2 step up voltage ratio transformer to produce twice the voltage at J6. In addition set R23 to  $200~\Omega$  and remove R24 and R29. R14 may require some adjustments.

A 1-V output will appear at J8 and J9 when IOUT1 and IOUT2 are terminated into  $50-\Omega$  external resistor loads (output taken from J8 and J9 and W6 and W7 open). If  $75-\Omega$  external resistors are used the maximum IOUT1/IOUT2 output current is 16 mA.

The THS3001 operates as a differential amplifier when: W9 is left opened, W8 pins 1 and 2 are connected together, W6 position A is connected to IOUT1, and W7 position D is connected to IOUT2.

The THS3001 operates as an inverting amplifier when: W9 is connected, R27 is set to 0  $\Omega$ , W8 pins 1 and 2 are connected together, and the input is from either W6 position B or W7 position D. If the input is via W6 position B, the output at J7 is -1.2 V. If the input is via W7 position D, the output will be -1.2 V.

The THS3001 operates as a noninverting amplifier when: W9 is opened, W8 pins 2 and 3 are joined together, and the input is from either W6 position A or W7 position E. If the input is via W6 position A, the output voltage is 2 V. If the input is taken via W7 position E, the output voltage at J7 is 2 V.

#### 3.7 Connector Pin and Function Assignments

This section details the pinouts and functions for all user connectors.

Table 3–7. Connector Pin and Function Assignments

| Reference Designator | Function                                             |

|----------------------|------------------------------------------------------|

| J1                   | Data bits 0 through 13 and CLKOUT input              |

| J2, J4               | Supplies power to the EVM                            |

| J3                   | Input control signals used to create EVM chip select |

| J5                   | Input for a clock signal source                      |

| J6,J7,J8,J9          | DAC output signal                                    |

Table 3-8. J4 and J2 Power Connectors

| Pin Number             | Function                     |  |

|------------------------|------------------------------|--|

| J2-1                   | J2–1 Digital Power 3 V – 5 V |  |

| J2-2                   | DGND                         |  |

| J4-1                   | J4–1 Analog Power +5 V       |  |

| J4-2                   | J4–2 AGND                    |  |

| J4–3 Analog Power –5 V |                              |  |

Table 3–9. J6, J7, J8, and J9 Analog Output Signal Connectors

| SMA  | Function                                                | SMA  | Function |

|------|---------------------------------------------------------|------|----------|

| J6-1 | Differential to single-ended DAC output via transformer | J6-2 | AGND     |

| J7-1 | Differential or single-ended DAC output via op amp      | J7-2 | AGND     |

| J8-1 | DAC output IOUT1                                        | J8-2 | AGND     |

| J9-1 | DAC output IOUT2                                        | J9-2 | AGND     |

Table 3–10. J3 C542/C54xxDSK/Microprocessor Control Connector

| Pin Number | Function    | Pin Number | Function         |

|------------|-------------|------------|------------------|

| 1          | ~ I/OSTROBE | 2          | Ground (digital) |

| 3          | A1          | 4          | Ground (digital) |

| 5          | A0          | 6          | Ground (digital) |

| 7          | NC          | 8          | NC               |

| 9          | NC          | 10         | NC               |

| 11         | NC          | 12         | NC               |

The control signals are used to generate the device select signal for the THS56X1 EVM. In general more than one device is hooked to the DSP address and data buses.

Table 3–11. J1 Parallel Data Connector

| Pin Number | Function     | Pin Number | Function         |

|------------|--------------|------------|------------------|

| 1          | DSP_15 (MSB) | 2          | Ground (digital) |

| 3          | DSP_14       | 4          | Ground (digital) |

| 5          | DSP_13       | 6          | Ground (digital) |

| 7          | DSP_12       | 8          | Ground (digital) |

| 9          | DSP_11       | 10         | Ground (digital) |

| 11         | DSP_10       | 12         | Ground (digital) |

| 13         | DSP_09       | 14         | Ground (digital) |

| 15         | DSP_08       | 16         | Ground (digital) |

| 17         | DSP_07       | 18         | Ground (digital) |

| 19         | DSP_06       | 20         | Ground (digital) |

| 21         | DSP_05       | 22         | Ground (digital) |

| 23         | DSP_04       | 24         | Ground (digital) |

| 25         | DSP_03       | 26         | Ground (digital) |

| 27         | DSP_02       | 28         | Ground (digital) |

| 29         | DSP_01       | 30         | Ground (digital) |

| 31         | DSP_00 (LSB) | 32         | Ground (digital) |

| 33         | CLKOUT       | 34         | Ground (digital) |

Table 3–12. Function of Connector J5

| Reference Designator | Function                                 |

|----------------------|------------------------------------------|

| J5                   | DAC clock input signal via SMA connector |

# Chapter 4

# **Control Modes**

The SLEEP, MODE, EXTLO, EXTIO and BIASJ pins of the THS5671/THS5661/THS5651/THS5641 control various DAC features and functions. This section describes the function of these pins.

| Горі | C               | Page |

|------|-----------------|------|

| 4.1  | SLEEP Input Pin |      |

| 4.2  | MODE Input Pin  | 4-2  |

| 4.3  | BIASJ Input Pin | 4-2  |

| 4.4  | EXTLO Input Pin | 4-2  |

| 4.5  | EXTIO Input Pin | 4-2  |

|      |                 |      |

#### 4.1 SLEEP Input Pin

The SLEEP pin is used to power down the device. It is an active high asynchronous power-down input. The device has an internal pulldown resistor. So for normal operations of the device, it is not necessary to tie the pin to DGND. The device requires 5  $\mu$ S to power down and 3 mS to power up. W5 is used to control the SLEEP input.

#### 4.2 MODE Input Pin

#### MODE bit = 1

When the MODE pin is connected to DVDD the device is configured to read 2s complement input data.

#### MODE bit = 0

When the MODE pin is connected to DGND the device is configured to read binary input data.

#### 4.3 BIASJ Input Pin

For an output current of 20 mA the potentiometer R14 value is typically set to 1.8 k $\Omega$ . Owing to the fact that the maximum full-scale current is 20 mA when IOUT1 and IOUT2 are terminated into 50  $\Omega$  load resistors, the voltage at J8 and J9 is 1 V.

#### 4.4 EXTLO Input Pin

The internal 1.2 V Vref is selected when the EXTLO pin is grounded (W3 pins 2 and 3 shorted). When EXTLO pin is tied to 5V (W3 pins 2 and 3 shorted) and W4 jumper is in place, the external 1.2 V Vref is selected.

#### 4.5 EXTIO Input Pin

An external reference voltage is provided via the EXTIO input pin. U7 or U8 is used to generate the external reference voltage. Jumper W4 is for selecting the external reference voltage.

## **Chapter 5**

# **Software**

The code presented runs on the 40 MHz C542 DSKplus. It allows you to output a 220 kHz sinewave from the DAC, while the DAC is being clocked at 40 MHz. Running the code on a 100 MHz C542 DSP or the C5410 DSP will give output sinewave speeds up to 2 MHz. The program is also useful for checking that the THS56X1 EVM is functioning properly.

The complete C-callable assembly code is shown in List 1.

#### List 1. Complete Software Listing for a Sinewave Generator

```

/* Title: THS56X1 ADC C program main routine

/* File:

* /

CDAC.C

/* Description: In this c-program file the user calls the sine wave */

/* function which never returns to this c-program again

extern void sinewave();

main(void)

sinewave();

******************

* TITLE : THS5651 Interface routine

* FUNCTION : MAIN

* PROTOTYPE :

: void MAIN ()

* CALLS

: N/A

* PRECONDITION : N/A

* POSTCONDITION : N/A

* DESCRIPTION : main routine is used the generated a sine wave

input for THS56x1 EVM using the 'C542 DSKplus board.

* AUTHOR : AAP Application Group, L. Philipose, Dallas,TX

CREATED 1999(C) BY TEXAS INSTRUMENTS INCORPORATED.

: TMS320C54x User's Guide, TI 1997

* REFERENCE

Data Aquisation Circuits, TI 1999

******************

.title "THS56x1 sine wave"

.mmregs

.width 80

.length 55

.version 542

.sect ".vectors"

.copy "vectors.asm"

.sect ".data"

*global Variables

.global _sinewave

*Local Varibles

AD_DP

.usect ".variabl", 0 ;

* Address Decoder constants:

.set 00003h

; activate A2 when DAC1 is choosen

.sect ".SINE"

sinevals

.word 07FC0h

;sine wave table.

.word 0A800h

.word 0C780h

.word 0E300h

.word 0F380h

.word OFFCOh

.word 0FEC0h

.word 0EB00h

.word 0D200h

.word 0B900h

.word 09440h

.word 07380h

.word 05280h

.word 03080h

```

```

.word 01900h ;

.word 00900h ;

.word 00000h

.word 01500h

.word 02A00h

.word 04580h

.word 05E80h

.sect ".text"

_sinewave:

_MAIN:

START:

INITIALIZATION:

* copy interrupt routine, which are uncritical by the EVM to the IRQ table

location:

= #1;

DP

= #00200h;

AR7

repeat(#3h)

data(0084h) = *AR7+

; copy the NMI vector

AR7

= #00240h

repeat(#35)

data(00C0h) = *AR7+

; copy INTO, INT1,...

* initialize registers:

DP = #00000h

IFR = #1

; point to page zero

; reset any old interrupt on pin INTO

|= #01

; allow INTO

@IMR

SXM=#0

; no sign extension

* enable global interrupt (this is even required, if no IRQ routine is used

* by this program because the debugger needs to do its backgroud interrupts)

INTM

; enable global IRQ

```