# 3.3 V FCC/JATE DIRECT ACCESS ARRANGEMENT

#### **Features**

Complete DAA includes the following:

- 3.3 V to 5 V Digital/Analog Power Supplies

- JATE Filter Option

- 86 dB Dynamic Range TX/RX Paths

- Daisy-Chaining for Up to Eight Devices

- Integrated Ring Detector

- 3000 V Isolation

- Support for Caller ID

- Low Profile SOIC Packages

- Direct Interface to DSPs

- Integrated Modem Codec

- Compliant with FCC Part 68

- Low-Power Standby Mode

- Proprietary ISOcap<sup>™</sup> Technology

- Pin Compatible with Si3034, Si3032

- Optional IIR Digital Filter

## **Applications**

- V.90 Modems

- Voice Mail Systems

- Fax Machines

- Set Top Boxes

## **Description**

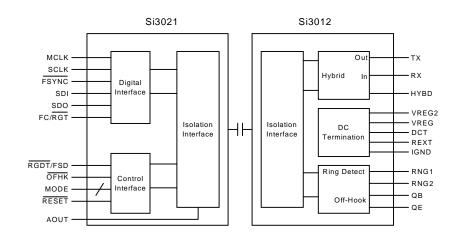

The Si3035 is an integrated direct access arrangement (DAA) chipset that provides a digital, low-cost, solid-state interface to a telephone line. Available in two 16-pin small outline packages, it eliminates the need for an analog front end (AFE), an isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid. The Si3035 dramatically reduces the number of discrete components and cost required to achieve compliance with FCC Part 68. The Si3035 interfaces directly to standard modem DSPs and supports all FCC and JATE out-of-band noise requirements. International support is provided by the pin compatible Si3034.

#### **Functional Block Diagram**

US Patent # 5,870,046 US Patent # 6,061,009 Other Patents Pending

2

# TABLE OF CONTENTS

| <u>Section</u>              | <u>Page</u> |

|-----------------------------|-------------|

| Electrical Specifications   |             |

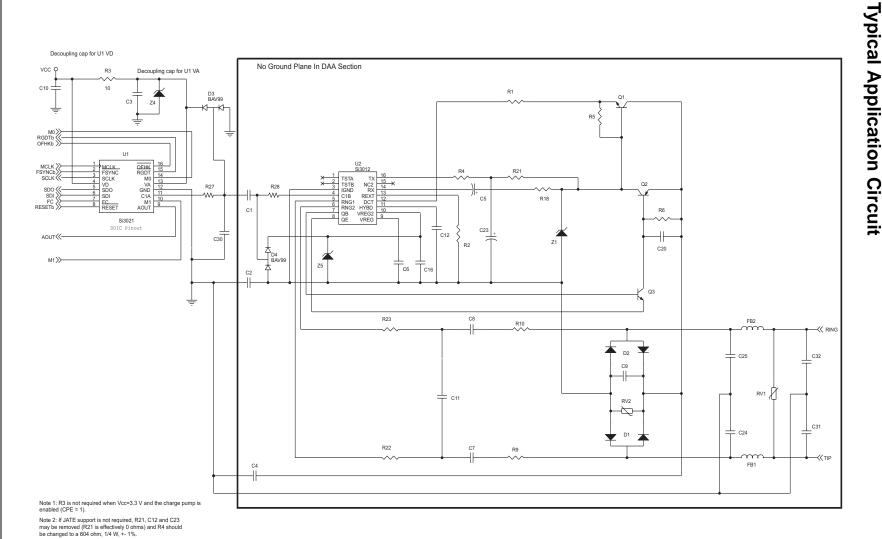

| Typical Application Circuit |             |

| Bill of Materials           | . 16        |

| Analog Output               |             |

| Functional Description      | . 18        |

| Initialization              | . 18        |

| Isolation Barrier           | . 18        |

| Off-Hook                    | . 18        |

| Ring Detect                 | . 19        |

| Improved JATE Support       | . 19        |

| Digital Interface           | . 19        |

| Clock Generation Subsystem  | . 20        |

| Power Management            | . 24        |

| Analog Output               | . 24        |

| On-Hook Line Monitor        | . 25        |

| Loop Current Monitor        | . 25        |

| Multiple Device Support     | . 25        |

| Gain Control                | . 26        |

| Filter Selection            | . 26        |

| Revision Identification     | . 32        |

| Calibration                 | . 32        |

| In-Circuit Testing          | . 32        |

| Exception Handling          | . 33        |

| Control Registers           | . 34        |

| Appendix—UL1950 3rd Edition | . 45        |

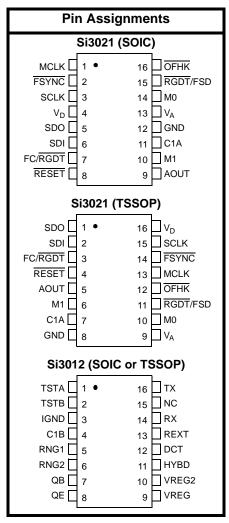

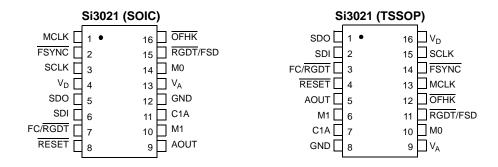

| Pin Descriptions: Si3021    | . 46        |

| Pin Descriptions: Si3012    | . 48        |

| Ordering Guide              | . 50        |

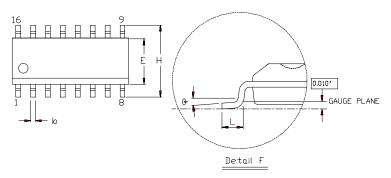

| SOIC Outline                | . 51        |

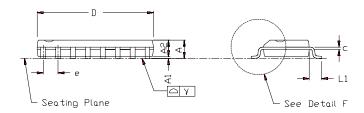

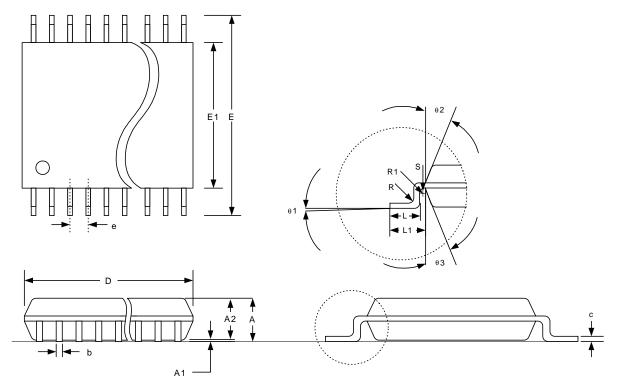

| TSSOP Outline               |             |

| Contact Information         | ΕA          |

## **Electrical Specifications**

**Table 1. Recommended Operating Conditions**

| Parameter <sup>1</sup>                      | Symbol         | Test Condition | Min <sup>2</sup> | Тур     | Max <sup>2</sup> | Unit |

|---------------------------------------------|----------------|----------------|------------------|---------|------------------|------|

| Ambient Temperature                         | T <sub>A</sub> | K-Grade        | 0                | 25      | 70               | °C   |

| Si3021 Supply Voltage, Analog               | V <sub>A</sub> |                | 4.75             | 5.0     | 5.25             | V    |

| Si3021 Supply Voltage, Digital <sup>3</sup> | V <sub>D</sub> |                | 3.0              | 3.3/5.0 | 5.25             | V    |

## Notes:

- 1. The Si3035 specifications are guaranteed when the typical application circuit (including component tolerances) and any Si3021 and any Si3012 are used. See Figure 16 on page 15 for typical application circuit.

- **2.** All minimum and maximum specifications are guaranteed and apply across the recommended operating conditions. Typical values apply at nominal supply voltages and an operating temperature of 25 °C unless otherwise stated.

- 3. The digital supply, V<sub>D</sub>, can operate from either 3.3 V or 5.0 V. The Si3021 supports interface to 3.3 V logic when operating from 3.3 V. The 3.3 V operation applies to both the serial port and the digital signals RGDT, OFHK, RESET, M0, and M1.

## Table 2. Loop Characteristics

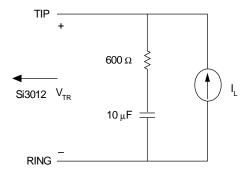

$(V_A = Charge Pump, V_D = +3.3 V \pm 0.3 V, T_A = 0 to 70^{\circ}C for K-Grade, Refer to Figure 1)$

| Parameter                                | Symbol           | Test Condition           | Min | Тур | Max  | Unit             |

|------------------------------------------|------------------|--------------------------|-----|-----|------|------------------|

| DC Termination Voltage                   | $V_{TR}$         | $I_L = 20 \text{ mA}$    | _   | _   | 7.7  | V                |

| DC Termination Voltage                   | $V_{TR}$         | I <sub>L</sub> = 105 mA  | 12  | _   | _    | V                |

| DC Ring Current (with caller ID)         | I <sub>RDC</sub> |                          | _   | _   | 1    | mA               |

| DC Ring Current (w/o caller ID)          | I <sub>RDC</sub> |                          | _   | _   | 20   | μA               |

| AC Termination Impedance                 | Z <sub>ACT</sub> |                          | _   | 600 | _    | Ω                |

| Operating Loop Current                   | I <sub>LP</sub>  |                          | 20  | _   | 120  | mA               |

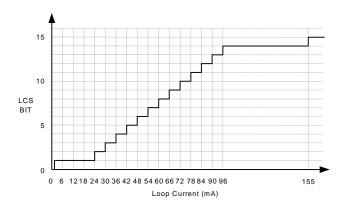

| Loop Current Sense Bits                  | LCS              | LCS = Fh                 | 180 | 155 | _    | mA               |

| Ring Voltage Detect                      | $V_{RD}$         |                          | 13  | 18  | 26   | V <sub>RMS</sub> |

| Ring Frequency                           | F <sub>R</sub>   |                          | 15  | _   | 68   | Hz               |

| On-Hook Leakage Current                  | I <sub>LK</sub>  | V <sub>BAT</sub> = -48 V | _   | _   | 1    | μΑ               |

| Ringer Equivalence Num. (with caller ID) | REN              |                          | _   | 1.0 | 1.67 | _                |

| Ringer Equivalence Num. (w/o caller ID)  | REN              |                          | _   | 0.2 | _    | _                |

Figure 1. Test Circuit for Loop Characteristics

Table 3. DC Characteristics,  $V_D = +5 \text{ V}$

$(V_A = +5 \text{ V } \pm 5\%, V_D = +5 \text{ V } \pm 5\%, T_A = 0 \text{ to } 70^{\circ}\text{C for K-Grade})$

| Parameter                                       | Symbol                          | Test Condition        | Min | Тур  | Max | Unit |

|-------------------------------------------------|---------------------------------|-----------------------|-----|------|-----|------|

| High Level Input Voltage                        | V <sub>IH</sub>                 |                       | 3.5 | _    | _   | V    |

| Low Level Input Voltage                         | V <sub>IL</sub>                 |                       | _   | _    | 0.8 | V    |

| High Level Output Voltage                       | V <sub>OH</sub>                 | $I_O = -2 \text{ mA}$ | 3.5 | _    | _   | V    |

| Low Level Output Voltage                        | V <sub>OL</sub>                 | I <sub>O</sub> = 2 mA | _   | _    | 0.4 | V    |

| Input Leakage Current                           | IL                              |                       | -10 | _    | 10  | μA   |

| Power Supply Current, Analog                    | I <sub>A</sub>                  | V <sub>A</sub> pin    | _   | 0.3  | 1   | mA   |

| Power Supply Current, Digital <sup>1</sup>      | I <sub>D</sub>                  | V <sub>D</sub> pin    | _   | 14   | 18  | mA   |

| Total Supply Current, Sleep Mode <sup>1</sup>   | I <sub>A</sub> + I <sub>D</sub> | PDN = 1, PDL = 0      | _   | 1.3  | 2.5 | mA   |

| Total Supply Current, Deep Sleep <sup>1,2</sup> | I <sub>A</sub> + I <sub>D</sub> | PDN = 1, PDL = 1      | _   | 0.04 | 0.5 | mA   |

#### Notes:

- All inputs at 0.4 or V<sub>D</sub> 0.4 (CMOS levels). All inputs held static except clock and all outputs unloaded (Static I<sub>OLIT</sub> = 0 mA).

- 2. RGDT is not functional in this state.

## Table 4. DC Characteristics, $V_D = +3.3 \text{ V}$

( $V_A$  = Charge Pump,  $V_D$  = +3.3 V ± 0.3 V,  $T_A$  = 0 to 70°C for K-Grade)

| Parameter                                       | Symbol                          | Test Condition         | Min | Тур  | Max  | Unit |

|-------------------------------------------------|---------------------------------|------------------------|-----|------|------|------|

| High Level Input Voltage                        | V <sub>IH</sub>                 |                        | 2.0 | _    | _    | V    |

| Low Level Input Voltage                         | V <sub>IL</sub>                 |                        | _   | _    | 0.8  | V    |

| High Level Output Voltage                       | V <sub>OH</sub>                 | I <sub>O</sub> = -2 mA | 2.4 |      | _    | V    |

| Low Level Output Voltage                        | V <sub>OL</sub>                 | I <sub>O</sub> = 2 mA  | _   | _    | 0.35 | V    |

| Input Leakage Current                           | IL                              |                        | -10 |      | 10   | μΑ   |

| Power Supply Current, Analog <sup>1,2</sup>     | I <sub>A</sub>                  | V <sub>A</sub> pin     | _   | 0.3  | 1    | mA   |

| Power Supply Current, Digital <sup>3</sup>      | I <sub>D</sub>                  | V <sub>D</sub> pin     | _   | 9    | 12   | mA   |

| Total Supply Current, Sleep Mode <sup>3</sup>   | $I_A + I_D$                     | PDN = 1, PDL = 0       | _   | 1.2  | 2.5  | mA   |

| Total Supply Current, Deep Sleep <sup>3,4</sup> | I <sub>A</sub> + I <sub>D</sub> | PDN = 1, PDL = 1       | _   | 0.04 | 0.5  |      |

| Power Supply Voltage, Analog <sup>1,5</sup>     | V <sub>A</sub>                  | Charge Pump On         | 4.3 | 4.6  | 5.00 | V    |

#### Notes:

- 1. Only a decoupling capacitor should be connected to  $V_{\mbox{\scriptsize A}}$  when the charge pump is on.

- 2. There is no I<sub>A</sub> current consumption when the internal charge pump is enabled and only a decoupling cap is connected to the V<sub>A</sub> pin.

- 3. All inputs at 0.4 or  $V_D 0.4$  (CMOS levels). All inputs held static except clock and all outputs unloaded (Static  $I_{OUT} = 0$  mA).

- **4.** RGDT is not functional in this state.

- 5. The charge pump is recommended to be used only when  $V_D < 4.5 \text{ V}$ . When the charge pump is not used,  $V_A$  should be applied to the device before  $V_D$  is applied on power up if driven from separate supplies.

## **Table 5. AC Characteristics**

( $V_A$  = Charge Pump,  $V_D$  = +3.3 V ± 0.3 V,  $T_A$  = 0 to 70°C for K-Grade)

| Parameter                                           | Symbol            | Test Condition                    | Min | Тур                 | Max    | Unit              |

|-----------------------------------------------------|-------------------|-----------------------------------|-----|---------------------|--------|-------------------|

| Sample Rate <sup>1</sup>                            | Fs                | Fs = F <sub>PLL2</sub> /5120      | 7.2 | _                   | 11.025 | kHz               |

| PLL1 Output Clock Frequency                         | F <sub>PLL1</sub> | FPLL1 = F <sub>MCLK</sub> • M1/N1 | 36  | _                   | 58     | MHz               |

| Transmit Frequency Response                         |                   | Low –3 dB corner                  | _   | 16                  | _      | Hz                |

| Receive Frequency Response                          |                   | Low –3 dB corner                  | _   | 16                  | _      | Hz                |

| Transmit Full Scale Level <sup>2</sup> (0 dB gain)  | $V_{TX}$          |                                   | _   | 0.98                | _      | $V_{PEAK}$        |

| Receive Full Scale Level <sup>2,3</sup> (0 dB gain) | $V_{RX}$          |                                   | _   | 0.98                | _      | $V_{PEAK}$        |

| Dynamic Range <sup>4</sup>                          | DR                | VIN = 1 kHz, -3 dBFS              | 80  | 86                  | _      | dB                |

| Dynamic Range <sup>5</sup>                          | DR                | VIN = 1 kHz, -3 dBFS              | _   | 84                  | _      | dB                |

| Total Harmonic Distortion <sup>6</sup>              | THD               | VIN = 1 kHz, -3 dBFS              | _   | -84                 | _      | dB                |

| Dynamic Range (call progress AOUT)                  | DR <sub>AO</sub>  | VIN = 1 kHz                       | 60  | _                   | _      | dB                |

| THD (call progress AOUT)                            | THD <sub>AO</sub> | VIN = 1 kHz                       | _   | 1.0                 | _      | %                 |

| AOUT Full Scale Level                               |                   |                                   | _   | 0.75 V <sub>D</sub> | _      | V <sub>PP</sub>   |

| AOUT Output Impedance                               |                   |                                   | _   | 10                  | _      | kΩ                |

| Mute Level (call progress AOUT)                     |                   |                                   | -90 | _                   | _      | dB                |

| Dynamic Range (caller ID mode)                      | DR <sub>CID</sub> | VIN = 1 kHz, -13 dBFS             | _   | 60                  | _      | dB                |

| Caller ID Full Scale Level (0 dB gain) <sup>2</sup> | $V_{CID}$         |                                   | _   | 0.8                 | _      | V <sub>PEAK</sub> |

## Notes:

- 1. See Figure 23 on page 22.

- 2. Parameter measured at TIP and RING of Figure 16 on page 15.

- 3. Receive Full Scale Level will produce 0.9 dBFS at SDO.

- **4.** DR = 3 dB + 20 log (RMS signal/RMS noise). Applies to both the transmit and receive paths. Measurement bandwidth is 300 to 3400 Hz. Sample Rate = 9.6 kHz, Loop Current = 40 mA.

- **5.** DR = 3 dB + 20 log (RMS signal/RMS noise). Applies to both the transmit and receive paths. Measurement bandwidth is 15 to 3400 Hz. Sample Rate = 9.6 kHz, Loop Current = 40 mA.

- **6.** THD = 20 log (RMS distortion/RMS signal). Applies to both the transmit and receive paths. Sample Rate = 9.6 kHz, Loop Current = 40 mA.

**Table 6. Absolute Maximum Ratings**

| Parameter                                | Symbol           | Value                          | Unit |

|------------------------------------------|------------------|--------------------------------|------|

| DC Supply Voltage                        | $V_D, V_A$       | -0.5 to 6.0                    | V    |

| Input Current, Si3021 Digital Input Pins | I <sub>IN</sub>  | ±10                            | mA   |

| Digital Input Voltage                    | V <sub>IND</sub> | -0.3 to (V <sub>D</sub> + 0.3) | V    |

| Operating Temperature Range              | T <sub>A</sub>   | -40 to 100                     | °C   |

| Storage Temperature Range                | T <sub>STG</sub> | -65 to 150                     | °C   |

Note: Permanent device damage may occur if the above Absolute Maximum Ratings are exceeded. Functional operation should be restricted to the conditions as specified in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

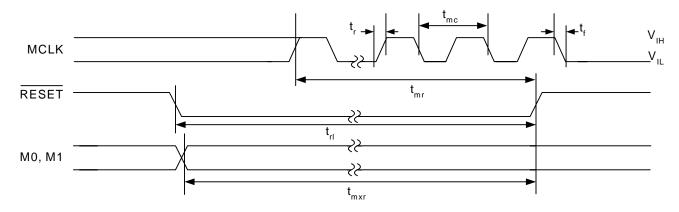

## Table 7. Switching Characteristics—General Inputs

(V<sub>A</sub> = Charge Pump,  $V_D$  = 3.0 to 5.25 V,  $T_A$  = 0 to 70°C for K-Grade,  $C_L$  = 20 pF)

| Parameter <sup>1</sup>         | Symbol           | Min   | Тур | Max  | Unit   |

|--------------------------------|------------------|-------|-----|------|--------|

| Cycle Time, MCLK               | t <sub>mc</sub>  | 16.67 | _   | 1000 | ns     |

| MCLK Duty Cycle                | t <sub>dty</sub> | 40    | 50  | 60   | %      |

| Rise Time, MCLK                | t <sub>r</sub>   | _     | _   | 5    | ns     |

| Fall Time, MCLK                | t <sub>f</sub>   | _     | _   | 5    | ns     |

| MCLK Before RESET ↑            | t <sub>mr</sub>  | 10    | _   | _    | cycles |

| RESET Pulse Width <sup>2</sup> | t <sub>rl</sub>  | 250   | _   | _    | ns     |

| M0, M1 Before RESET↑3          | t <sub>mxr</sub> | 150   | _   | _    | ns     |

#### Notes:

- 1. All timing (except Rise and Fall time) is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D - 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ . Rise and Fall times are referenced to the 20% and 80% levels of the waveform.

2. The minimum RESET pulse width is the greater of 250 ns or 10 MCLK cycle times.

3. M0 and M1 are typically connected to  $V_D$  or GND and should not be changed during normal operation.

Figure 2. General Inputs Timing Diagram

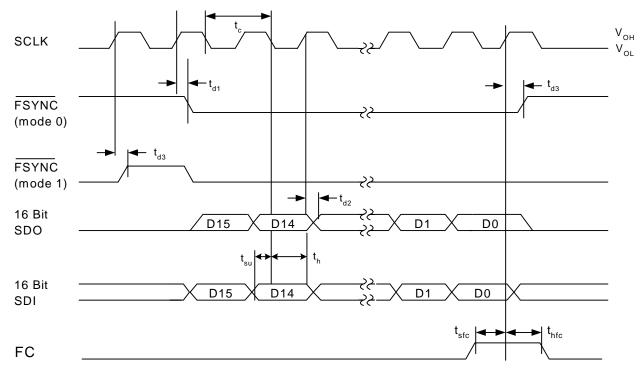

**Table 8. Switching Characteristics—Serial Interface (DCE = 0)**

$(V_A = Charge Pump, V_D = 3.0 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70^{\circ}\text{C} \text{ for K-Grade, } C_L = 20 \text{ pF})$

| Parameter                                                                                                                                               | Symbol           | Min | Тур      | Max | Unit |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|----------|-----|------|--|--|--|

| Cycle time, SCLK                                                                                                                                        | t <sub>c</sub>   | 354 | 1/256 Fs | _   | ns   |  |  |  |

| SCLK duty cycle                                                                                                                                         | t <sub>dty</sub> | _   | 50       | _   | %    |  |  |  |

| Delay time, SCLK $\uparrow$ to $\overline{FSYNC}\ \downarrow$                                                                                           | t <sub>d1</sub>  | _   | _        | 10  | ns   |  |  |  |

| Delay time, SCLK ↑ to SDO valid                                                                                                                         | t <sub>d2</sub>  | _   | _        | 20  | ns   |  |  |  |

| Delay time, SCLK ↑ to FSYNC ↑                                                                                                                           | t <sub>d3</sub>  | _   | _        | 10  | ns   |  |  |  |

| Setup time, SDI before SCLK $\downarrow$                                                                                                                | t <sub>su</sub>  | 25  | _        | _   | ns   |  |  |  |

| Hold time, SDI after SCLK $\downarrow$                                                                                                                  | t <sub>h</sub>   | 20  | _        | _   | ns   |  |  |  |

| Setup time, FC ↑ before SCLK ↑                                                                                                                          | t <sub>sfc</sub> | 40  | _        | _   | ns   |  |  |  |

| Hold time, FC ↑ after SCLK ↑                                                                                                                            | t <sub>hfc</sub> | 40  | _        | _   | ns   |  |  |  |

| <b>Note:</b> All timing is referenced to the 50% level of the waveform. Input test levels are $V_{IH} = V_D - 0.4 \text{ V}$ , $V_{IL} = 0.4 \text{ V}$ |                  |     |          |     |      |  |  |  |

Figure 3. Serial Interface Timing Diagram

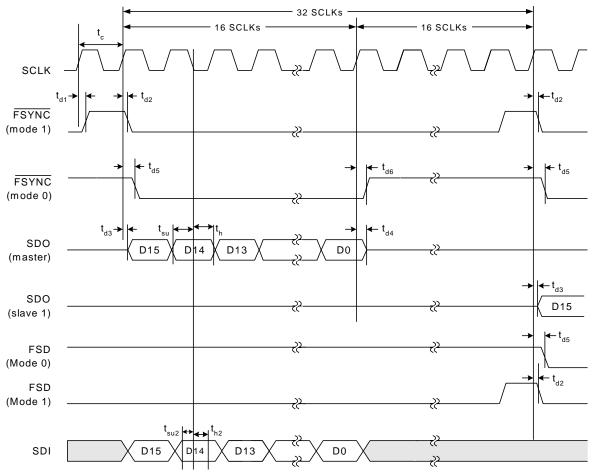

Table 9. Switching Characteristics—Serial Interface (DCE = 1, FSD = 0)

$(V_A = Charge Pump, V_D = 3.0 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70^{\circ}\text{C for K-Grade}, C_L = 20 \text{ pF})$

| Parameter <sup>1,2</sup>                 | Symbol           | Min              | Тур      | Max                     | Unit |

|------------------------------------------|------------------|------------------|----------|-------------------------|------|

| Cycle Time, SCLK                         | t <sub>c</sub>   | 354              | 1/256 Fs |                         | ns   |

| SCLK Duty Cycle                          | t <sub>dty</sub> |                  | 50       |                         | %    |

| Delay Time, SCLK ↑ to FSYNC ↑            | t <sub>d1</sub>  | _                | _        | 10                      | ns   |

| Delay Time, SCLK ↑ to FSYNC ↓            | t <sub>d2</sub>  | _                | _        | 10                      | ns   |

| Delay Time, SCLK ↑ to SDO valid          | t <sub>d3</sub>  | $0.25t_{c} - 20$ | _        | 0.25t <sub>c</sub> + 20 | ns   |

| Delay Time, SCLK ↑ to SDO Hi-Z           | t <sub>d4</sub>  | _                | _        | 20                      | ns   |

| Delay Time, SCLK ↑ to RGDT ↓             | t <sub>d5</sub>  | _                | _        | 20                      | ns   |

| Delay Time, SCLK ↑ to RGDT ↑             | t <sub>d6</sub>  | _                | _        | 20                      | ns   |

| Setup Time, SDO Before SCLK $\downarrow$ | t <sub>su</sub>  | 25               | _        | _                       | ns   |

| Hold Time, SDO After SCLK $\downarrow$   | t <sub>h</sub>   | 20               | _        | _                       | ns   |

| Setup Time, SDI Before SCLK              | t <sub>su2</sub> | 25               | _        | _                       | ns   |

| Hold Time, SDI After SCLK                | t <sub>h2</sub>  | 20               | _        | _                       | ns   |

| M. A.                                    |                  |                  |          |                         |      |

#### Notes:

- 1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ .

- 2. Refer to the section "Multiple Device Support" on page 25 for functional details.

Figure 4. Serial Interface Timing Diagram (DCE = 1, FSD = 0)

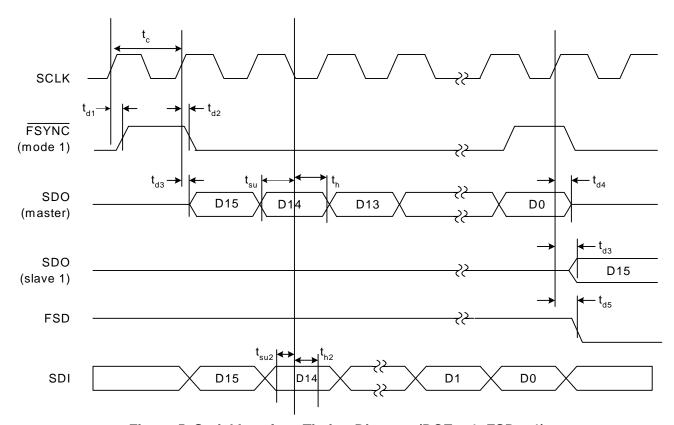

Table 10. Switching Characteristics—Serial Interface (DCE = 1, FSD = 1)

$(V_A = Charge Pump, V_D = 3.0 \text{ to } 5.25 \text{ V}, T_A = 0 \text{ to } 70^{\circ}C \text{ for K-Grade, } C_L = 20 \text{ pF})$

| Parameter <sup>1,2</sup>                 | Symbol           | Min                     | Тур      | Max                     | Unit |

|------------------------------------------|------------------|-------------------------|----------|-------------------------|------|

| Cycle Time, SCLK                         | t <sub>c</sub>   | 354                     | 1/256 Fs | _                       | ns   |

| SCLK Duty Cycle                          | t <sub>dty</sub> | _                       | 50       | _                       | %    |

| Delay Time, SCLK ↑ to FSYNC ↑            | t <sub>d1</sub>  | _                       | _        | 10                      | ns   |

| Delay Time, SCLK ↑ to FSYNC ↓            | t <sub>d2</sub>  | _                       | _        | 10                      | ns   |

| Delay Time, SCLK ↑ to SDO valid          | t <sub>d3</sub>  | 0.25t <sub>c</sub> – 20 | _        | 0.25t <sub>c</sub> + 20 | ns   |

| Delay Time, SCLK ↑ to SDO Hi-Z           | t <sub>d4</sub>  | _                       | _        | 20                      | ns   |

| Delay Time, SCLK ↑ to RGDT ↓             | t <sub>d5</sub>  | _                       | _        | 20                      | ns   |

| Setup Time, SDO Before SCLK $\downarrow$ | t <sub>su</sub>  | 25                      | _        | _                       | ns   |

| Hold Time, SDO After SCLK $\downarrow$   | t <sub>h</sub>   | 20                      | _        | _                       | ns   |

| Setup Time, SDI Before SCLK              | t <sub>su2</sub> | 25                      | _        | _                       | ns   |

| Hold Time, SDI After SCLK                | t <sub>h2</sub>  | 20                      | _        | _                       | ns   |

## Notes:

- 1. All timing is referenced to the 50% level of the waveform. Input test levels are  $V_{IH} = V_D 0.4 \text{ V}$ ,  $V_{IL} = 0.4 \text{ V}$ .

- 2. Refer to the section "Multiple Device Support" on page 25 for functional details.

Figure 5. Serial Interface Timing Diagram (DCE = 1, FSD = 1)

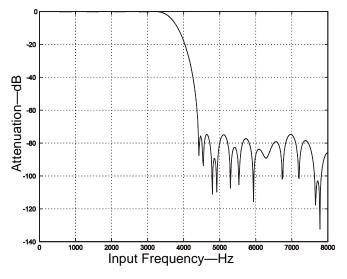

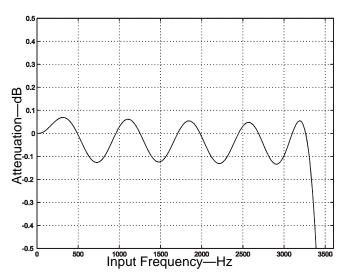

Table 11. Digital FIR Filter Characteristics—Transmit and Receive

$(V_A = Charge Pump, V_D = +5 V \pm 5\%, Sample Rate = 8 kHz, T_A = 0 to 70°C for K-Grade)$

| Parameter                                      | Symbol                | Min                                                                                                   | Тур   | Max | Unit |  |  |  |  |

|------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------|-------|-----|------|--|--|--|--|

| Passband (0.1 dB)                              | F <sub>(0.1 dB)</sub> | 0                                                                                                     | _     | 3.3 | kHz  |  |  |  |  |

| Passband (3 dB)                                | F <sub>(3 dB)</sub>   | 0                                                                                                     | _     | 3.6 | kHz  |  |  |  |  |

| Passband Ripple Peak-to-Peak                   |                       | -0.1                                                                                                  | _     | 0.1 | dB   |  |  |  |  |

| Stopband                                       |                       | _                                                                                                     | 4.4   | _   | kHz  |  |  |  |  |

| Stopband Attenuation                           |                       | -74                                                                                                   | _     | _   | dB   |  |  |  |  |

| Group Delay                                    | t <sub>gd</sub>       | _                                                                                                     | 12/Fs | _   | sec  |  |  |  |  |

| Note: Typical FIR filter characteristics for F | s = 8000 Hz are sh    | <b>Note:</b> Typical FIR filter characteristics for Fs = 8000 Hz are shown in Figures 6, 7, 8, and 9. |       |     |      |  |  |  |  |

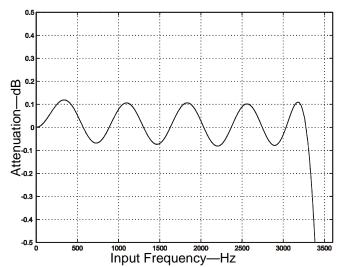

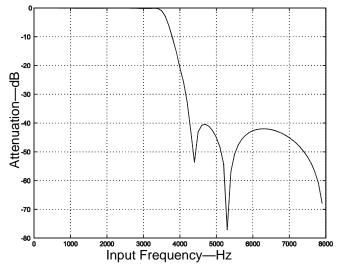

## Table 12. Digital IIR Filter Characteristics—Transmit and Receive

$(V_A = Charge Pump, V_D = +5 V \pm 5\%, Sample Rate = 8 kHz, T_A = 0 to 70°C for K-Grade)$

| Parameter                    | Symbol              | Min  | Тур    | Max | Unit |

|------------------------------|---------------------|------|--------|-----|------|

| Passband (3 dB)              | F <sub>(3 dB)</sub> | 0    | _      | 3.6 | kHz  |

| Passband Ripple Peak-to-Peak |                     | -0.2 | _      | 0.2 | dB   |

| Stopband                     |                     | _    | 4.4    | _   | kHz  |

| Stopband Attenuation         |                     | -40  | _      | _   | dB   |

| Group Delay                  | t <sub>gd</sub>     | _    | 1.6/Fs | _   | sec  |

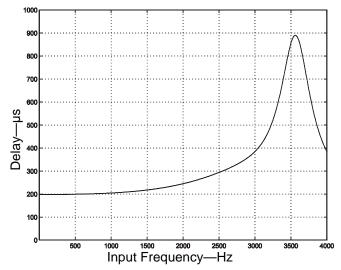

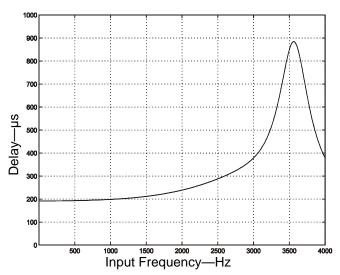

**Note:** Typical IIR filter characteristics for Fs = 8000 Hz are shown in Figures 10, 11, 12, and 13. Figures 14 and 15 show group delay versus input frequency.

20 20 40 40 400 5000 7000 800 Input Frequency—Hz

Figure 6. FIR Receive Filter Response

Figure 8. FIR Transmit Filter Response

Figure 7. FIR Receive Filter Passband Ripple

Figure 9. FIR Transmit Filter Passband Ripple

For Figures 6–9, all filter plots apply to a sample rate of Fs = 8 kHz. The filters scale with the sample rate as follows:

$$F_{(0.1 \text{ dB})} = 0.4125 \text{ Fs}$$

$$F_{(-3 dB)} = 0.45 Fs$$

where Fs is the sample frequency.

Figure 10. IIR Receive Filter Response

Figure 12. IIR Transmit Filter Response

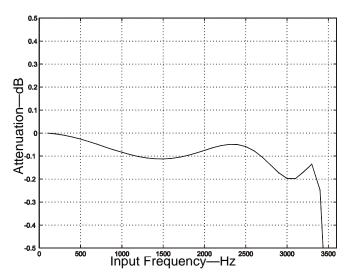

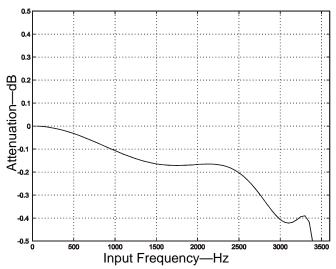

Figure 11. IIR Receive Filter Passband Ripple

Figure 13. IIR Transmit Filter Passband Ripple

For Figures 10–13, all filter plots apply to a sample rate of Fs = 8 kHz. The filters scale with the sample rate as follows:

$$F_{(-3 \text{ dB})} = 0.45 \text{ Fs}$$

where Fs is the sample frequency.

Figure 14. IIR Receive Group Delay

Figure 15. IIR Transmit Group Delay

Figure 16. Typical Application Schematic

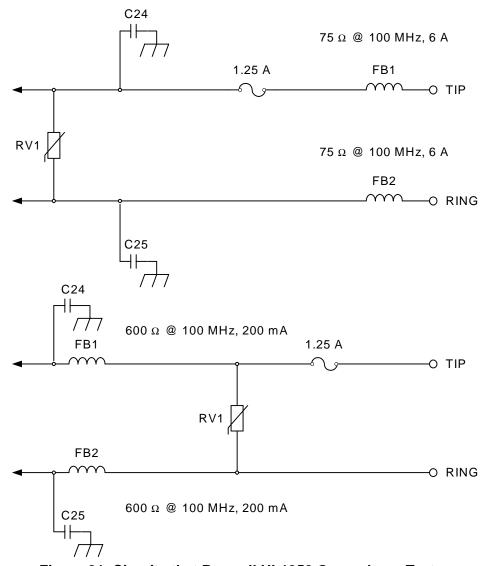

Note 3: See Appendix for applications requiring UL 1950 3rd Edition compliance.

## **Bill of Materials**

**Table 13. Component Values—Typical Application**

| Component <sup>1</sup>                | Value                             | Supplier(s)                                           |  |  |  |

|---------------------------------------|-----------------------------------|-------------------------------------------------------|--|--|--|

| C1,C4                                 | 150 pF, 3 kV, X7R, ±20%           | Novacap, Venkel, Johanson, Murata,<br>Panasonic, SMEC |  |  |  |

| C2                                    | Not Installed                     |                                                       |  |  |  |

| C3                                    | 0.22 μF, 16 V, X7R, ±20%          |                                                       |  |  |  |

| C5                                    | 1 μF, 16 V, Tant/Elec, ±20%       |                                                       |  |  |  |

| C6,C10,C16                            | 0.1 μF, 16 V, X7R, ±20%           |                                                       |  |  |  |

| C7,C8,C9                              | 15 nF, 250 V, X7R, ±20%           | Novacap, Johanson, Murata, Panasonic, SMEC            |  |  |  |

| C11                                   | 39 nF, 16 V, X7R, ±20%            |                                                       |  |  |  |

| C12 <sup>2</sup>                      | 2.7 nF, 16 V, X7R, ±20%           |                                                       |  |  |  |

| C23 <sup>2</sup>                      | 0.1 μF, 16 V, Tant/Elec/X7R, ±20% |                                                       |  |  |  |

| C24, C25, C31,C32 <sup>3</sup>        | 1000 pF, 3 kV, X7R, ±10%          | Novacap, Venkel, Johanson, Murata, Panasonic, SMEC    |  |  |  |

| C30 <sup>4</sup>                      | Not Installed                     |                                                       |  |  |  |

| D1,D2 <sup>5</sup>                    | Dual Diode, 300 V, 225 mA         | Central Semiconductor                                 |  |  |  |

| D3,D4                                 | BAV99 Dual Diode, 70 V, 350 mW    | Diodes, Inc., OnSemiconductor, Fairchild              |  |  |  |

| FB1,FB2                               | Ferrite Bead                      | Murata                                                |  |  |  |

| Q1,Q3                                 | A42, NPN, 300 V                   | OnSemiconductor, Fairchild                            |  |  |  |

| Q2                                    | A92, NPN, 300 V                   | OnSemiconductor, Fairchild                            |  |  |  |

| RV1                                   | Sidactor, 275 V, 100 A            | Teccor, ST Microelectronics, Microsemi, TI            |  |  |  |

| RV2                                   | MOV, 240 V                        | Panasonic                                             |  |  |  |

| R1                                    | 51 Ω, 1/2 W ±5%                   |                                                       |  |  |  |

| R2                                    | 15 Ω, 1/4 W ±5%                   |                                                       |  |  |  |

| R3 <sup>6</sup>                       | Not Installed                     |                                                       |  |  |  |

| R4 <sup>2</sup> ,R18,R21 <sup>2</sup> | 301 Ω, 1/10 W, ±1%                |                                                       |  |  |  |

| R5,R6                                 | 36 kΩ, 1/10 W ±5%                 |                                                       |  |  |  |

| R9,R10                                | 2 kΩ, 1/10 W ±5%                  |                                                       |  |  |  |

| R22,R23                               | 20 kΩ, 1/10 W ±5%                 |                                                       |  |  |  |

| R27,R28                               | 10 Ω, 1/10 W ±5%                  |                                                       |  |  |  |

| U1                                    | Si3021                            | Silicon Labs                                          |  |  |  |

| U2                                    | Si3012                            | Silicon Labs                                          |  |  |  |

| Z1                                    | Zener diode, 18 V                 | Vishay, Rohm, OnSemiconductor                         |  |  |  |

| Z4,Z5                                 | Zener diode, 5.6 V, 1/2 W         | Diodes, Inc., OnSemiconductor, Fairchild              |  |  |  |

#### Notes:

- **1.** The following reference designators were intentionally omitted: C13–C15, C17–C22, C26–C29, R7, R8, R11–R17, R19, and R20.

- 2. If JATE support is not required, C12, and C23 may be removed.

- 3. Alternate population option is C24, C25 (2200 pF, 3 kV, X7R, ±10% and C31, C32 not installed).

- 4. Install only if needed for improved radiated emissions performance (10 pF, 16 V, NPO, ±10%).

- 5. Several diode bridge configurations are acceptable (suppliers include General Semi, Diodes Inc.)

- **6.** If the charge pump is not enabled (with the CPE bit in Register 6),  $V_A$  must be 4.75 to 5.25 V. R3 can be installed with a 10  $\Omega$ , 1/10 W, ±5% if  $V_D$  is also 4.75 to 5.25 V.

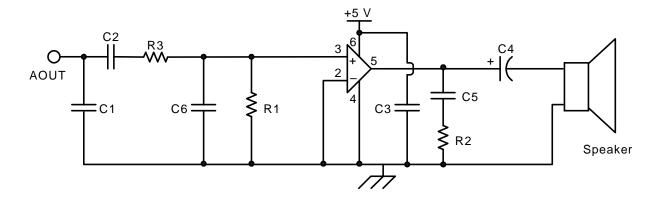

# **Analog Output**

Figure 17 illustrates an optional application circuit to support the analog output capability of the Si3035 for call progress monitoring purposes. The ARM bits in Register 6 allow the receive path to be attenuated by 0 dB, –6 dB, or –12 dB. The ATM bits, which are also in Register 6, allow the transmit path to be attenuated by –20 dB, –26 dB, or –32 dB. Both the transmit and receive paths can also be independently muted.

Figure 17. Optional Connection to AOUT for a Call Progress Speaker

Table 14. Component Values—Optional Connection to AOUT

| Symbol     | Value                    |

|------------|--------------------------|

| C1         | 2200 pF, 16 V, ±20%      |

| C2, C3, C5 | 0.1 μF, 16 V, ±20%       |

| C4         | 100 μF, 16 V, Elec. ±20% |

| C6         | 820 pF, 16 V, ±20%       |

| R1         | 3 kΩ, 1/10 W, ±5%        |

| R2         | 10 Ω, 1/10 W, ±5%        |

| R3         | 47 kΩ, 1/10 W, ±5%       |

| U1         | LM386                    |

## **Functional Description**

The Si3035 is an integrated chipset that provides a low-cost, isolated, silicon-based interface to the telephone line. The Si3035 saves cost and board area by eliminating the need for a modem AFE or serial codec. It also eliminates the need for an isolation transformer, relays, opto-isolators, and a 2- to 4-wire hybrid. The Si3035 solution requires only a few low-cost, discrete components to achieve full compliance with FCC Part 68 and JATE out-of-band noise requirements. See Figure 16 on page 15 for a typical application circuit. See the pin-compatible Si3034 or Si3044 data sheets for designs requiring global support.

The Si3035 North America/Japan DAA offers a number of new features not supported by the Si3032 device. These include operation from a single 3.3 V power supply, JATE (Japan) filter option, finer resolution for both transmit and receive levels on AOUT (call progress output), daisy-chaining for up to eight devices, and an optional IIR filter. Table 15 summarizes the new Si3035 features.

Table 15. New Si3035 Features

| Category             | Si3032       | Si3035                  |

|----------------------|--------------|-------------------------|

| Daisy-Chaining       | _            | Up to 8 Devices         |

| Optional IIR Filter  | _            | Yes                     |

| Receive Gain         | 0, 6 dB      | 0, 3, 6, 9, 12 dB       |

| Transmit Attenuation | 0, -3 dB     | 0, -3, -6 -9,<br>-12 dB |

| V <sub>A</sub>       | 5 V          | 3.3 V* or 5 V           |

| V <sub>D</sub>       | 3.3 V or 5 V | 3.3 V or 5 V            |

| JATE Support         | _            | Yes                     |

| AOUT Levels (dB)     | 0, mute      | 0, -6, -12, mute        |

\*Note: The  $V_A$  supply is internally generated by an on-chip charge pump.

## Initialization

When the Si3035 is initially powered up, the RESET pin should be asserted. When the RESET pin is deasserted, the registers will have default values. This reset condition guarantees the line-side chip (Si3012) is powered down with no possibility of loading the line (i.e., off-hook). The following is an example initialization

#### procedure:

- Program the PLLs with registers 7 to 9 (N1[7:0], M1[7:0], N2[3:0] and M2[3:0]) to the appropriate divider ratios for the supplied MCLK frequency and desired sample rate, as defined in "Clock Generation Subsystem" on page 20.

- 2. Wait until the PLLs are locked. This time is between 100  $\mu$ S and 1 ms.

- 3. Write an 0x80 into Register 6. This enables the charge pump for the  $V_A$  pin, powers up the line-side chip (Si3012), and enables the AOUT for call progress monitoring.

After this procedure is complete, the Si3035 is ready for ring detection and off-hook.

#### **Isolation Barrier**

The Si3035 achieves an isolation barrier through a low-cost, high-voltage capacitor in conjunction with Silicon Laboratories' proprietary ISOcap signal processing techniques. These techniques eliminate any signal degradation due to capacitor mismatches, common mode interference, or noise coupling. As shown in Figure 16 on page 15, the C1, C2, and C4 capacitors isolate the Si3021 (DSP-side) from the Si3012 (line-side). All transmit, receive, control, and caller ID data are communicated through this barrier.

The ISOcap inter-chip communication is disabled by default. To enable it, the PDL bit in Register 6 must be cleared. No communication between the Si3021 and Si3012 can occur until this bit is cleared. The clock generator *must* be programmed to an acceptable sample rate prior to clearing the PDL bit.

#### Off-Hook

The communication system generates an off-hook command by applying logic 0 to the OFHK pin or writing a logic 1 to bit 0 of control Register 5. The OFHK pin must be enabled by setting bit 1 (OHE) of Register 5. With OFHK at logic 0, the system is in an off-hook state. This state is used to seize the line for incoming/outgoing calls and can also be used for pulse dialing. With OFHK at logic 1, negligible DC current flows through the hookswitch. When a logic 0 is applied to the OFHK pin, the hookswitch transistor pair, Q1 and Q2, turn on. The net effect of the off-hook signal is the application of a termination impedance across TIP and RING and the flow of DC loop current. The termination impedance has both an AC and a DC component.

The AC termination impedance is a  $604-\Omega$  resistor, which is connected to the TX pin. The DC termination is a  $51-\Omega$  resistor, which is connected to the DCT pin.

When executing an off-hook sequence, the Si3035 requires 1548/Fs seconds to complete the off-hook and provide phone line data on the serial link. This includes the 12/Fs filter group delay. If necessary, for the shortest

delay, a higher Fs may be established prior to executing the off-hook, such as an Fs of 10.286 kHz. The delay allows line transients to settle prior to normal use.

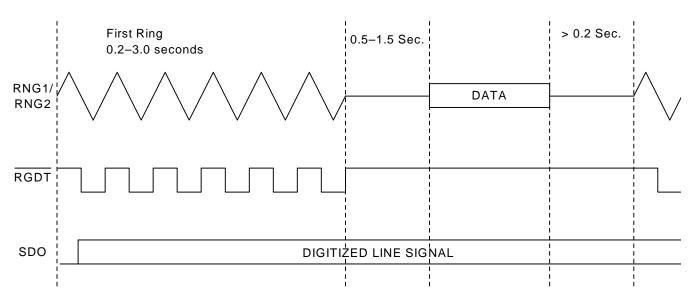

## **Ring Detect**

The ring signal enters the Si3035 through low value capacitors connected to TIP and RING. RGDT is a clipped, half-wave rectified version of the ringing waveform. See Figure 18 for a timing diagram of the RGDT pin.

The integrated ring detect of the Si3035 allows the device to present the ring signal to the DSP, through the serial port, with no additional signaling required. The signal sent to the DSP is a clipped version of the original ring signal. In addition, the Si3035 passes through the caller ID data unaltered.

The system can also detect an occurring ring by the status of the RDT bit of Register 5. This bit is a read-only bit that is set when the line-side device detects a ring signal at RNG1 and RNG2. The RDT bit clears when the system either goes off-hook or 4.5 to 9 seconds after the last ring is detected.

If caller ID is supported in the system, the designer can enable the Si3035 to pass this information to the SDO output. Following the completion of the first ring, the system should set the ONHM bit (Register 5, bit 3). This bit must be cleared at the conclusion of the receipt of the caller ID data and prior to the next ring burst.

The Si3021 can support a wake-up-on-ring function using the RGDT signal. Refer to "Power Management" on page 24 for more details

## **Improved JATE Support**

The HYBD pin connects to a node on the internal hybrid cancellation circuit providing a pin for a balancing capacitor, C12. C23 adds the necessary transmit out-of-band filtering required to meet JATE out-of-band noise specifications. The addition of C23 alters the transmit path frequency response which must be balanced with capacitor C12 to obtain maximum hybrid cancellation.

Products using the Si3035 which have been submitted for JATE approval should document a waiver for the JATE DC Termination specification. This specification is met in the Si3034 global DAA device.

## **Digital Interface**

The Si3035 has two serial interface modes that support most standard modem DSPs. The M0 and M1 mode pins select the interface mode. The key difference between these two serial modes is the operation of the FSYNC signal. Table 16 summarizes the serial mode definitions.

**Table 16. Serial Modes**

| Mode | M1 | МО | Description                   |

|------|----|----|-------------------------------|

| 0    | 0  | 0  | FSYNC frames data             |

| 1    | 0  | 1  | FSYNC pulse starts data frame |

| 2    | 1  | 0  | Slave mode                    |

| 3    | 1  | 1  | Reserved                      |

Figure 18. Ring Detect Timing

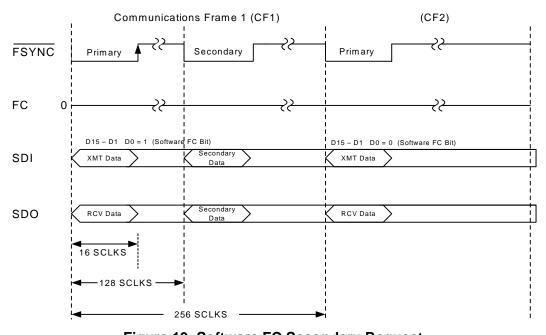

The digital interface consists of a single, synchronous serial link which communicates both telephony and control data.

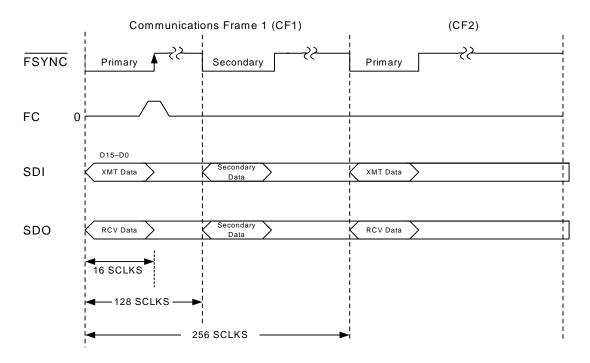

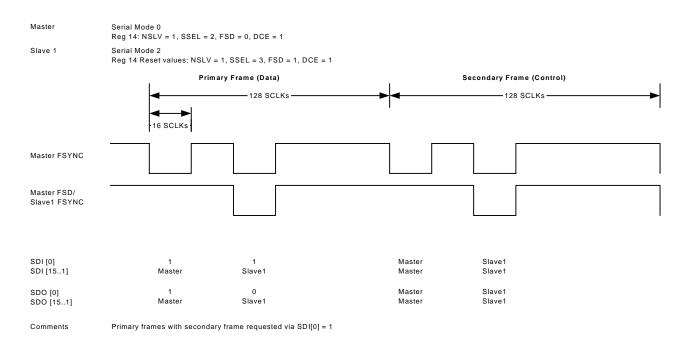

In Serial mode 0 or 1, the Si3021 operates as a master, where the master clock (MCLK) is an input, the serial data clock (SCLK) is an output, and the frame sync signal (FSYNC) is an output. The MCLK frequency and the value of the sample rate control registers 7, 8, 9, and 10 determine the sample rate (Fs). The serial port clock, SCLK, runs at 256 bits per frame, where the frame rate is equivalent to the sample rate. Refer to "Clock Generation Subsystem" on page 20 for more details on programming sample rates.

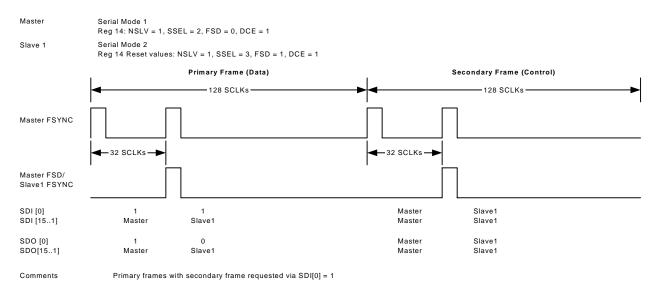

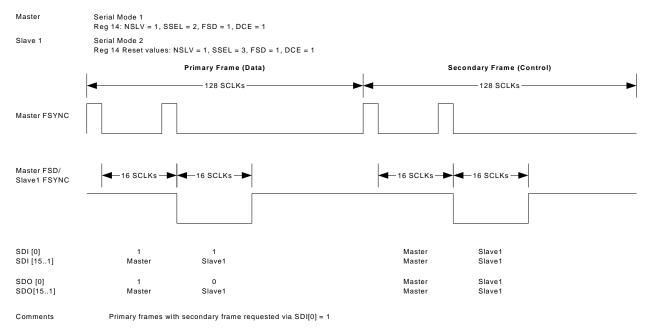

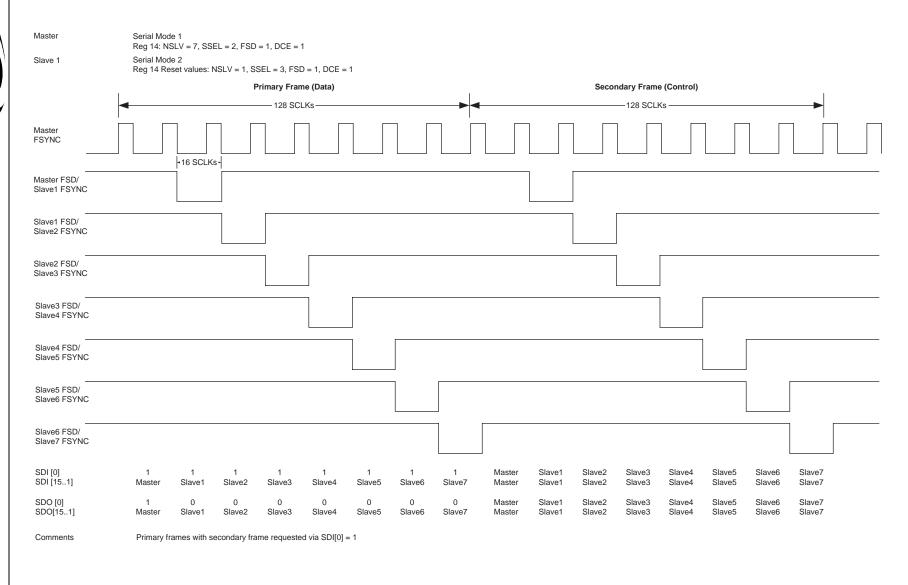

The Si3035 transfers 16-bit or 15-bit telephony data in the primary timeslot and 16-bit control data in the secondary timeslot. Figure 19 and Figure 20 show the relative timing of the serial frames. Primary frames occur at the frame rate and are always present. To minimize overhead in the external DSP, secondary frames are present only when requested.

Two methods exist for transferring control information in the secondary frame. The default power-up mode uses the LSB of the 16-bit transmit (TX) data word as a flag to request a secondary transfer. In this mode, only 15-bit TX data is transferred, resulting in a loss of SNR but allowing software control of the secondary frames. As an alternative method, the FC pin can serve as a hardware flag for requesting a secondary frame. The external DSP can turn on the 16-bit TX mode by setting the SB bit of Register 1. In the 16-bit TX mode, the hardware FC pin must be used to request secondary transfers.

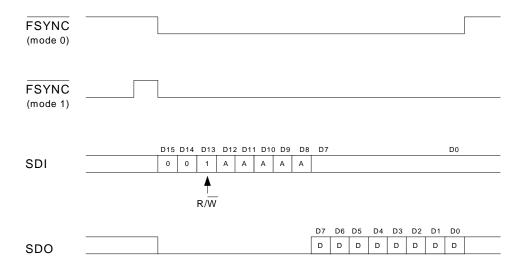

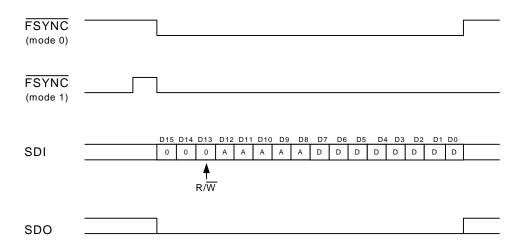

Figure 21 and Figure 22 illustrate the secondary frame read cycle and write cycle, respectively. During a read cycle, the R/W bit is high and the 5-bit address field contains the address of the register to be read. The contents of the 8-bit control register are placed on the SDO signal. During a write cycle, the R/W bit is low and the 5-bit address field contains the address of the register to be written. The 8-bit data to be written immediately follows the address on SDI. Only one register can be read or written during each secondary frame. See "Control Registers" on page 34 for the register addresses and functions.

In serial mode 2, the Si3021 operates as a slave device, where the MCLK is an input, the SCLK is a no connect (except for the master device for which it is an output), and the FSYNC is an input. In addition, the RGDT/FSD pin operates as a delayed frame sync (FSD) and the FC/RGDT pin operates as ring detect (RGDT). In this mode, FC operation is not supported. For further details on operating the Si3021 as a slave device, refer to "Multiple Device Support" on page 25.

## **Clock Generation Subsystem**

The Si3035 contains an on-chip clock generator. Using a single MCLK input frequency, the Si3035 can generate all the desired standard modem sample rates, as well as the common 11.025 kHz rate for audio playback.

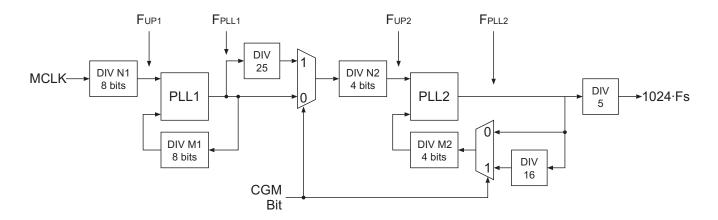

The clock generator consists of two PLLs (PLL1 and PLL2) that achieve the desired sample frequencies. Figure 23 on page 22 illustrates the clock generator.

Figure 19. Software FC Secondary Request

SILICUN LA HORATURIES

Figure 20. Hardware FC Secondary Request

Figure 21. Secondary Communication Data Format—Read Cycle

Figure 22. Secondary Communication Data Format—Write Cycle

Figure 23. Clock Generation Subsystem

The architecture of the dual PLL scheme allows for fast lock time on initial start-up, fast lock time when changing modem sample rates, high noise immunity, and the ability to change modem sample rates with a single register write. A large number of MCLK frequencies between 1 MHz and 60 MHz are supported. MCLK should be from a clean source, preferably directly from a crystal with a constant frequency and no dropped pulses.

In serial mode 2, the Si3021 operates as a slave device. The clock generator is configured (by default) to set the SCLK output equal to the MCLK input. The net effect is the clock generator multiplies the MCLK input by 20. For further details of slave mode operation, refer to "Multiple Device Support" on page 25.

## **Programming the Clock Generator**

As noted in Figure 23, the clock generator must output a clock equal to 1024 • Fs, where Fs is the desired sample rate. The 1024 • Fs clock is determined through programming of the following registers:

Register 7-N1 divider, 8 bits.

Register 8-M1 divider, 8 bits.

Register 9—N2/M2 dividers, 4 bits/4 bits.

Register 10—CGM, 1 bit.

When using the Si3035 for modem applications, the clock generator can be programmed to allow for a single register write to change the modem sampling rate. These standard sample rates are shown in Table 17. The programming method is described below.

Table 17. N2, M2 Values (CGM = 0, 1)

| Fs (Hz) | N2 | M2 |

|---------|----|----|

| 7200    | 2  | 2  |

| 8000    | 9  | 10 |

| 8229    | 7  | 8  |

| 8400    | 6  | 7  |

| 9000    | 4  | 5  |

| 9600    | 3  | 4  |

| 10286   | 7  | 10 |

The main design consideration is the generation of a base frequency, defined as the following:

$$F_{\text{Base}} = \frac{F_{\text{MCLK}} \cdot M1}{N1} = 36.864 \text{MHz}, CGM = 0$$

$$F_{\text{Base}} = \frac{F_{\text{MCLK}} \cdot M1 \cdot 16}{N1 \cdot 25} = 36.864 \text{MHz}, \text{CGM} = 1$$

N1 (Register 7) and M1 (Register 8) are 8-bit unsigned values.  $F_{MCLK}$  is the clock provided to the MCLK pin. Table 18 lists several standard crystal oscillator rates that could be supplied to MCLK. This list simply represents a sample of MCLK frequency choices. Many more are possible.

After the first PLL has been setup, the second PLL can be programmed easily. The values for N2 and M2 (Register 9) are shown in Table 17. N2 and M2 are 4-bit unsigned values.

When programming the registers of the clock generator, the order of register writes is important. For PLL1 updates, N1 (Register 7) must always be written first, immediately followed by a write to M1 (Register 8). For PLL2, the CGM bit must be set as desired prior to writing N2/M2 (Register 9). Changes to the CGM bit only take effect when N2/M2 are written.

Note: The values shown in Table 17 and Table 18 satisfy the equations above. However, when programming the registers for N1, M1, N2, and M2, the value placed in these registers must be one less than the value calculated from the equations. For example, for CGM = 0 with a MCLK of 48.0 MHz, the values placed in the N1 and M1 registers would be 0x7C and 0x5F, respectively. If CGM = 1, a non-zero value must be programmed to Register 9 in order for the 16/25 ratio to take effect.

Table 18. MCLK Examples

| MCLK (MHz) | N1  | M1  | CGM |

|------------|-----|-----|-----|

| 1.8432     | 1   | 20  | 0   |

| 4.0000     | 5   | 72  | 1   |

| 4.0960     | 1   | 9   | 0   |

| 5.0688     | 11  | 80  | 0   |

| 6.0000     | 5   | 48  | 1   |

| 6.1440     | 1   | 6   | 0   |

| 8.1920     | 32  | 225 | 1   |

| 9.2160     | 1   | 4   | 0   |

| 10.0000    | 25  | 144 | 1   |

| 10.3680    | 9   | 32  | 0   |

| 11.0592    | 3   | 10  | 0   |

| 12.288     | 1   | 3   | 0   |

| 14.7456    | 2   | 5   | 0   |

| 16.0000    | 5   | 18  | 1   |

| 18.4320    | 1   | 2   | 0   |

| 24.5760    | 32  | 75  | 1   |

| 25.8048    | 7   | 10  | 0   |

| 33.8688    | 147 | 160 | 0   |

| 44.2368    | 96  | 125 | 1   |

| 46.0800    | 5   | 4   | 0   |

| 47.9232    | 13  | 10  | 0   |

| 48.0000    | 125 | 96  | 0   |

| 56.0000    | 35  | 36  | 1   |

| 60.0000    | 25  | 24  | 1   |

#### **PLL Lock Times**

The Si3035 changes sample rates very quickly. However, lock time will vary based on the programming of the clock generator. The major factor contributing to PLL lock time is the CGM bit. When the CGM bit is used (set to 1), PLL2 will lock slower than when CGM is 0. The following relationships describe the boundaries on PLL locking time:

PLL1 lock time < 1 ms (CGM = 0,1)

PLL2 lock time: 100 us to 1 ms (CGM = 0)

PLL2 lock time <1 ms (CGM = 1)

For modem designs, it is recommended that PLL1 be programmed during initialization. No further programming of PLL1 is necessary. The CGM bit and PLL2 can be programmed for the desired initial sample

rate, typically 7200 Hz. All further sample rate changes are then made by simply writing to Register 9 to update PLL2.

The final design consideration for the clock generator is the update rate of PLL1. The following criteria must be satisfied in order for the PLLs to remain stable:

$$F_{UP1} = \frac{F_{MCLK}}{N1} \ge 144 \text{ kHz}$$

Where F<sub>UP1</sub> is shown in Figure 23 on page 22.

## **Setting Generic Sample Rates**

The above clock generation description focuses on the common modem sample rates. An application may require a sample rate not listed in Table 17, such as the common audio rate of 11.025 kHz. The restrictions and equations above still apply; however, a more generic relationship between MCLK and Fs (the desired sample rate) is needed. The following equation describes this relationship:

$$\frac{M1 \cdot M2}{N1 \cdot N2} = \text{ratio} \cdot \frac{5 \cdot 1024 \cdot Fs}{MCLK}$$

where Fs is the sample frequency, ratio is 1 for CGM = 0 and 25/16 for CGM = 1, and all other symbols are shown in Figure 23 on page 22.

By knowing the MCLK frequency and desired sample rate, the values for the M1, N1, M2, N2 registers can be determined. When determining these values, remember to consider the range for each register as well as the minimum update rate for the first PLL.

The values determined for M1, N1, M2, and N2 must be adjusted by minus one when determining the value written to the respective registers. This is due to internal logic, which adds one to the value stored in the register. This addition allows the user to write a zero value in any of the registers and the effective divide by is one. A special case occurs when both M1 and N1 and/or M2 and N2 are programmed with a zero value. When Mx and Nx are both zero, the corresponding PLLx is bypassed. Note that if M2 and N2 are set to zero, the ratio of 25/16 is eliminated and cannot be used in the above equation. In this condition the CGM bit has no effect.

## **Power Management**

The Si3035 supports four basic power management operation modes: normal operation, reset operation, sleep, and full power down. The power management modes are controlled by the PDN and PDL bits of Register 6.

On power up, or following a reset, the Si3035 is in reset operation. In this mode, the PDL bit is set, while the

PDN bit is cleared. The Si3021 is fully operational, except for the ISOcap link. No communication between the Si3021 and Si3012 can occur during reset operation. Any bits associated with the Si3012 are not valid in this mode.

The most common mode of operation is the normal operation. In this mode, the PDL and PDN bits are cleared. The Si3021 is fully operational and the ISOcap link is passing information between the Si3021 and the Si3012. The clock generator must be programmed to a valid sample rate prior to entering this mode.

The Si3035 supports a low-power sleep mode. This mode supports the popular wake-up-on-ring feature of many modems. The clock generator registers 7, 8, and 9 must be programmed with valid non-zero values prior to enabling sleep mode. Then, the PDN bit must be set and the PDL bit cleared. When the Si3035 is in sleep mode, the MCLK signal may be stopped or remain active, but it *must* be active before waking up the Si3035. The Si3021 is non-functional except for the ISOcap and RGDT signal. To take the Si3035 out of sleep mode, pulse the reset pin (RESET) low.

In summary, the power down/up sequence for sleep mode is as follows:

- 1. Registers 7, 8, and 9 must have valid non-zero values.

- 2. Set the PDN bit (Register 6, bit 3) and clear the PDL bit (Register 6, bit 4).

- 3. MCLK may stay active or stop.

- 4. Restore MCLK before initiating the power-up sequence.

- 5. Reset the Si3035 using RESET pin (after MCLK is present).

- 6. Program registers to desired settings.

The Si3035 also supports an additional power-down mode. When both the PDN (Register 6, bit 3) and PDL (Register 6, bit 4) are set, the chipset enters a complete power-down mode and draws negligible current (deep sleep mode). PLL2 should be turned off prior to entering deep sleep mode (i.e., set Register 9 to 0 and then Register 6 to 0x18). In this mode, the RGDT pin does not function. Normal operation may be restored using the same process for taking the chipset out of sleep mode.

## **Analog Output**

The Si3035 supports an analog output (AOUT) for driving the call progress speaker found with most of today's modems. AOUT is an analog signal that is comprised of a mix of the transmit and receive signals. The receive portion of this mixed signal has a 0 dB gain, while the transmit signal has a gain of –20 dB.

The AOUT level can be adjusted via the ATM and ARM bits in control Register 6. The transmit portion of the

AOUT signal can be set to -20 dB, -26 dB, -32 dB, or mute. The receive portion of the AOUT signal can be set to 0 dB, -6 dB, -12 dB, or mute. Figure 17 on page 17 illustrates a recommended application circuit. In the configuration shown, the LM386 provides a gain of 26 dB. Additional gain adjustments may be made by varying the voltage divider created by R1 and R3 of Figure 17.

#### **On-Hook Line Monitor**

The Si3035 allows the user to detect line activity when the device is in an on-hook state. When the system is on-hook, the line data can be passed to the DSP across the serial port while drawing a small amount of DC current from the line. This feature is similar to the passing of line information (such as caller ID), while on-hook, following a ring signal detection. To activate this feature, set the ONHM bit in Register 5.

The on-hook line monitor can also be used to detect whether a phone line is physically connected to the Si3012 and associated circuitry. When the on-hook line monitor is activated (if no line is connected), the output of SDO will move towards a negative full scale value (–32768). The value is guaranteed to be at least 89% of negative full scale.

If a line is present while in on-hook line monitor mode, SDO will have a near zero value. The designer must allow for the group delay of the receive filter (12/Fs) before making a decision.

#### **Loop Current Monitor**

When the system is in an off-hook state, the LCS bits of Register 12 indicate the approximate amount of DC loop current that is flowing in the loop. The LCS is a 4-bit value ranging from zero to fifteen. Each unit represents approximately 6 mA of loop current from LCS codes 1–14. The typical LCS transfer function is shown in Figure 24.

Figure 24. Typical LCS Transfer Function

An LCS value of zero means the loop current is less than required for normal operation and the system should be on-hook. Typically, an LCS value of 15 means the loop current is greater than 155 mA.

The LCS detector has a built-in hysteresis of 2 mA of current. This allows for a stable LCS value when the loop current is near a transition level. The LCS value is a rough approximation of the loop current, and the designer is advised to use this value in a relative means rather than an absolute value.

This feature enables the host processor to detect if an additional line has "picked up" while the modem is transferring information. In the case of a second phone going off-hook, the loop current falls approximately 50% and is reflected in the value of the LCS bits.

## **Multiple Device Support**

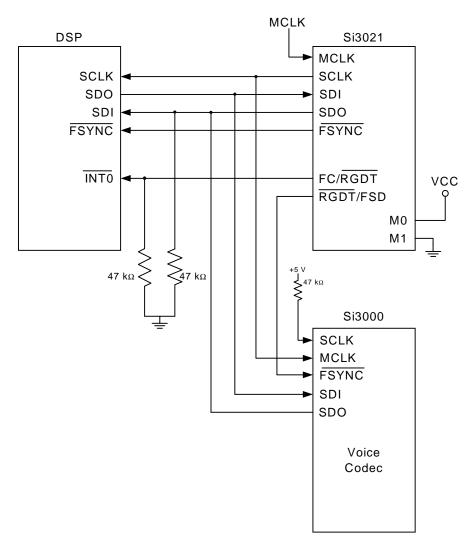

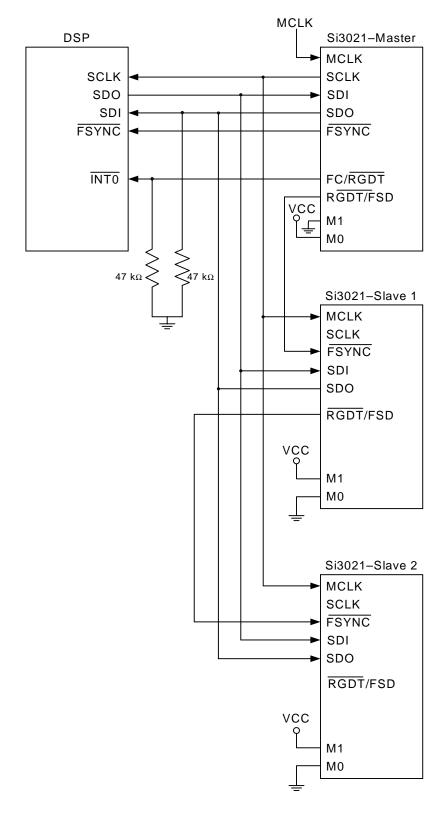

The Si3035 supports the operation of up to seven additional devices on a single serial interface. Figure 25 on page 27 shows the typical connection of the Si3035 and one additional serial voice codec (Si3000).

The Si3035 must be the master in this configuration. The secondary codec should be configured as a slave device with SCLK and  $\overline{\mbox{FSYNC}}$  as inputs. On power up, the Si3035 master will be unaware of the additional codec on the serial bus. The FC/RGDT pin is an input, operating as the hardware control for secondary frames. The RGDT/FSD pin is an output, operating as the active low ring detection signal. It is recommended that the master device be programmed for master/slave mode prior to enabling the ISOcap, because a ring signal would cause a false transition to the slave device's  $\overline{\mbox{FSYNC}}.$

Register 14 provides the necessary control bits to configure the Si3035 for master/slave operation. Bit 0 (DCE) sets the Si3035 in master/slave mode, also referred to as daisy-chain mode. When the DCE bit is set, the  $\overline{FC/RGDT}$  pin becomes the ring detect output and the  $\overline{RGDT/FSD}$  pin becomes the frame sync delay output.

Bits 7:5 (NSLV2:NSLV0) set the number of slaves to be supported on the serial bus. For each slave, the Si3035 will generate a FSYNC to the DSP. In daisy-chain mode, the polarity of the ring signal can be controlled by bit 1 (RPOL). When RPOL = 1, the ring detect signal (now output on the FC/RGDT pin) is active high.

The Si3035 supports a variety of codecs (e.g., Si3000) as well as additional Si3035s. The type of slave codec(s) used is set by bits 4:3 (SSEL1:SSEL0). These bits determine the type of signalling used in the LSB of SDO. This assists the DSP in isolating which data stream is the master and which is the slave. If the LSB is used for

signalling, the master device will have a unique setting relative to the slave devices. The <u>DSP</u> can use this information to determine which FSYNC marks the beginning of a sequence of data transfers.

The delayed frame sync (FSD) of each device is supplied as the FSYNC of each subsequent slave device in the daisy chain. The master Si3035 will generate an FSYNC signal for each device every 16 or 32 SCLK periods. The delay period is set by Register 14, bit 2 (FSD). Figures 26-29 show the relative timing for daisy chaining operation. Primary communication frames occur in sequence, followed by secondary communication frames, if requested. When writing/reading the master device via a secondary frame, all secondary frames of the slave devices must be written as well. When writing/reading a slave device via a secondary frame, the secondary frames of the master and all other slaves must be written as well. "No operation" writes/reads to secondary frames are accomplished by writing/reading a zero value to address

If FSD is set for 16 SCLK periods between FSYNCs, only serial mode 1 can be used. In addition, the slave devices must delay the tri-state to active transition of their SDO sufficiently from the rising edge of SCLK to avoid bus contention.

The Si3035 supports the operation of up to eight Si3035 devices on a single serial bus. The master Si3035 must be configured in serial mode 1. The slave(s) Si3035 is configured in serial mode 2. Figure 30 shows a typical master/slave connection using three Si3035 devices.

When in serial mode 2, FSYNC becomes an input, RGDT/FSD becomes the delay frame sync output, and FC/RGDT becomes the ring detection output. In addition, the internal PLLs are fixed to a multiply by 20. This provides the desired sample rate when the master's SCLK is provided to the slave's MCLK. The SCLK of the slave is a no connect in this configuration. The delay between FSYNC input and delayed frame sync output (RGDT/FSD) will be 16 SCLK periods. The RGDT/FSD output has a waveform identical to the FSYNC signal in serial mode 0. In addition, the LSB of SDO is set to zero by default for all devices in serial mode 2.

## **Gain Control**

The Si3035 supports multiple gain and attenuation settings for the receive and transmit paths, respectively, via Register 13. When the ARX bit is set, 6 dB of gain is applied to the receive path. When the ATX bit is set, -3 dB of gain is applied to the transmit path.

Register 15 can be used to provide additional gain control. For Register 15 to have an effect on the receive and transmit paths, the ATX and ARX bits of

Register 13 must be 0.

The receive path can support gains of 0, 3, 6, 9, and 12 dB. The gain is selected by bits 2:0 (ARX2:ARX0). The receive path can also be muted by setting bit 3 (RXM). The transmit path can support attenuations of 0, 3, 6, 9, and 12 dB. The attenuation is selected by bits 6:4 (ATX2:ATX0). The transmit path can also be muted by setting bit 7 (TXM).

## **Filter Selection**

The Si3035 supports additional filter selections for the receive and transmit signals. When set, the IIRE bit of Register 16 enables the IIR filters defined in Table 12 on page 11. This filter provides a much lower, however non-linear, group delay than the default FIR filters.

Figure 25. Typical Connection for Master/Slave Operation (e.g., Data/Fax/Voice Modem)

Figure 26. Daisy Chaining of a Single Slave (Pulse FSD)

Figure 27. Daisy Chaining of a Single Slave (Frame FSD)

Figure 28. Daisy Chaining of Eight DAAs

Figure 29. Daisy Chaining with Framed FSYNC and Framed FSD

Figure 30. Typical Connection for Multiple Si3035s

#### **Revision Identification**

The Si3035 provides the system designer the ability to determine the revision of the Si3021 and/or the Si3012. Register 11 identifies the revision of the Si3021 with 4 bits named REVA. Register 13 identifies the revision of the Si3012 with 4 bits named REVB. Table 19 shows the values for the various revisions.

**Table 19. Revision Values**

| Revision | Si3021 | Si3012 |

|----------|--------|--------|

| А        | 1000   | _      |

| В        | 1001   | _      |

| С        | 1010   | _      |

| D        | _      | 0100   |

| E        | _      | 0101   |

| G        | _      | 0111   |

#### Calibration

The Si3035 initiates an auto-calibration by default whenever the device goes off-hook or experiences a loss in line power. Calibration is used to remove any offsets that may be present in the on-chip A/D converter which could affect the A/D dynamic range. Auto-calibration is typically initiated after the DAA DC termination stabilizes and takes 512/Fs seconds to complete. Due to the large variation in line conditions and line card behavior that may be presented to the DAA, it can be beneficial to use manual calibration in lieu of auto-calibration. Manual calibration should be executed as close as possible to 512/Fs seconds before valid transmit/receive data is expected.

The following steps should be taken to implement manual calibration:

- 1. The CALD (auto-calibration disable—Register 17) bit must be set to 1.

- 2. The MCAL (manual calibration) bit must be toggled to 1 and then 0 to begin and complete the calibration.

- 3. The calibration will be completed in 512/Fs seconds.

## **In-Circuit Testing**

The Si3035's advanced design provides the modem manufacturer with an increased ability to determine system functionality during production line tests, as well as support for end-user diagnostics. Four loopback modes exist allowing increased coverage of system components. For three of the test modes, a line-side power source is needed. While a standard phone line

can be used, the test circuit in Figure 1 on page 4 is adequate. In addition, an off-hook sequence must be performed to connect the power source to the line-side chip.

For the start-up test mode, no line-side power is necessary and no off-hook sequence is required. The start-up test mode is enabled by default. When the PDL bit (Register 6, bit 4) is set (the default case), the line side is in a power-down mode and the DSP-side is in a digital loop-back mode. In this mode, data received on SDI is passed through the internal filters and transmitted on SDO. This path will introduce approximately 0.9 dB of attenuation on the SDI signal received. The group delay of both transmit and receive filters will exist between SDI and SDO. Clearing the PDL bit disables this mode and the SDO data is switched to the receive data from the line side. When the PDL bit is cleared the FDT bit (Register 12, bit 6) will indicating become active. the successful communication between the line-side and DSP-side. This can be used to verify that the ISOcap link is

The remaining test modes require an off-hook sequence to operate. The following sequence defines the off-hook requirement:

- 1. Power up or reset.

- 2. Program clock generator to desired sample rate.

- 3. Enable line-side by clearing PDL bit.

- 4. Issue off-hook

Rev. 1.2

- 5. Delay 1548/Fs to allow calibration to occur.

- 6. Set desired test mode.

The ISOcap digital loopback mode allows the data pump to provide a digital input test pattern on SDI and receive that digital test pattern back on SDO. To enable this mode, set the DL bit of Register 1. In this mode, the isolation barrier is actually being tested. The digital stream is delivered across the isolation capacitor, C1 of Figure 16 on page 15, to the line-side device and returned across the same barrier. In this mode, the 0.9 dB attenuation and filter group delays also exist.

The analog loopback mode allows an external device to drive the RX pin of the line-side chip and receive the signal from the TX pin. This mode allows testing of external components connecting the RJ-11 jack (TIP and RING) to the line side of the Si3035. To enable this mode, set the AL bit of Register 2.

The final testing mode, internal analog loopback, allows the system to test the basic operation of the transmit/receive path of the line side and the external components R4, R18, R21, and C5 of Figure 16 on page 15. In this test mode, the data pump provides a

32

digital test waveform on SDI. This data is passed across the isolation barrier, looped from the TX to the RX pin, passed back across the isolation barrier, and presented to the data pump on SDO. To enable this mode, clear the HBE bit of Register 2.

Clearing the HBE bit will cause a DC offset which affects the signal swing of the transmit signal. In this test mode, it is recommended that the transmit signal be 12 dB lower than normal transmit levels. This lower level will eliminate clipping caused by the DC offset which results from disabling the hybrid. It is assumed in this test that the line AC impedance is nominally  $600~\Omega$ .

**Note:** All test modes are mutually exclusive. If more than one test mode is enabled concurrently, the results are unpredictable.

## **Exception Handling**

The Si3035 provides several mechanisms to determine if an error occurs during operation. Through the secondary frames of the serial link, the controlling DSP can read several status bits. The bit of highest importance is the frame detect bit (FDT, Register 12, bit 6). This bit indicates that the DSP-side (Si3021) and line-side (Si3012) devices are communicating. During normal operation, the FDT bit can be checked before reading any bits that indicate information about the line side. If FDT is not set, the following bits related to the line-side are invalid: RDT, LCS, CBID, and REVB. The RGDT operation will also be non-functional.

Following power-up and reset, the FDT bit is not set because the PDL bit (Register 6, bit 4) defaults to 1. In this state, the ISOcap link is not operating and no information about the line-side can be determined. The user must program the clock generator to a valid configuration for the system and clear the PDL bit to activate the ISOcap link. While the Si3021 and Si3012 are establishing communication, the Si3035 will not generate FSYNC signals. Establishing communication will take less than 10 ms. Therefore, if the controlling DSP serial interface is interrupt driven, based on the FSYNC signal, the controlling DSP does not require a special delay loop to wait for this event to complete.

The FDT bit can also indicate if the line-side executes an off-hook request successfully. If the line-side is not connected to a phone line (i.e., the user fails to connect a phone line to the modem), the FDT bit remains cleared. The controlling DSP must allow sufficient time for the line-side to execute the off-hook request. The maximum time for FDT to be valid following an off-hook request is 10 ms. At this time, the LCS bits indicate the amount of loop current flowing. For more information, see "Loop Current Monitor" on page 25. If the FDT bit fails to be set following an off-hook request, the line-side

chip must be reset. This is accomplished by setting the PDL bit for at least 1 ms.

Another useful bit is the communication link error (CLE) bit (Register 12, bit 7). The CLE bit indicates a time-out error for the ISOcap link following a change to either PLL1 or PLL2. For more information, see "Clock Generation Subsystem" on page 20. When the CLE bit is set, the DSP-side chip has failed to receive verification from the line side that the clock change has been accepted in an expected period of time (less than 10 ms). This condition indicates a severe error in programming the clock generator or possibly a defective line-side chip.

# **Control Registers**

Any register not listed here is reserved and should not be written.

## **Table 20. Register Summary**

| Register | Name                      | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3                  | Bit 2 | Bit 1  | Bit 0 |

|----------|---------------------------|--------------|-------|-------|-------|------------------------|-------|--------|-------|

| 1        | Control 1                 | SR           |       |       |       |                        |       | DL     | SB    |

| 2        | Control 2                 |              |       |       |       | AL                     |       | HBE    | RXE   |

| 3        | Control 3                 |              |       |       |       |                        |       |        |       |

| 4        | Control 4                 |              |       |       |       |                        |       |        |       |

| 5        | DAA Control 1             |              |       |       | OPOL  | ONHM                   | RDT   | OHE    | ОН    |

| 6        | DAA Control 2             | CPE          | ATM1  | ARM1  | PDL   | PDN                    |       | ATM0   | ARM0  |

| 7        | PLL1 Divide N1            |              |       |       | N1[   | [7:0]                  |       |        |       |

| 8        | PLL1 Multiply<br>M1       |              |       |       | M1[   | [7:0]                  |       |        |       |

| 9        | PLL2 Div./Mult.<br>N2/M2  | N2[3:0] M2[3 |       |       |       |                        | [3:0] |        |       |

| 10       | PLL Control               |              |       |       |       |                        |       |        | CGM   |

| 11       | Chip Revision             |              |       |       |       |                        | REVA  | A[3:0] |       |

| 12       | Line Side Status          | CLE          | FDT   |       |       |                        | LCS   | [3:0]  |       |

| 13       | Transmit and Receive Gain |              | CBID  |       | REVI  | B[3:0]                 |       | ARX    | ATX   |

| 14       | Daisy-Chain<br>Control    | NSLV2        | NSLV1 | NSLV0 | SSEL1 | EL1 SSEL0 FSD RPOL DCE |       |        | DCE   |

| 15       | TX/RX Gain<br>Control     | TXM          | ATX2  | ATX1  | ATX0  | RXM                    | ARX2  | ARX1   | ARX0  |

| 16       | IIR Filter Control        | 0            | 0     | 0     | IIRE  | 1                      | 0     | 0      | 0     |

| 17       | Calibration               | 0            | MCAL  | CALD  |       |                        |       |        |       |

# Register 1. Control 1

| Bit  | D7  | D6 | D5 | D4 | D3 | D2 | D1  | D0  |

|------|-----|----|----|----|----|----|-----|-----|

| Name | SR  |    |    |    |    |    | DL  | SB  |

| Туре | R/W |    |    |    |    |    | R/W | R/W |

Reset settings = 0000\_0000

| Bit | Name     | Function                                                                                                                                                                                                                                                                                             |

|-----|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SR       | Software Reset.  0 = Enables chip for normal operation.  1 = Sets all registers to their reset value.                                                                                                                                                                                                |

| 6:2 | Reserved | Read returns zero.                                                                                                                                                                                                                                                                                   |

| 1   | DL       | Isolation Digital Loopback.  0 = Disables digital loopback mode across the isolation barrier.  1 = Enables digital loopback mode across the isolation barrier.                                                                                                                                       |

| 0   | SB       | Serial Digital Interface Mode.  0 = Operation is in 15-bit mode and the LSB of the data field indicates whether a secondary frame is required.  1 = The serial port is operating in 16-bit mode and requires use of the secondary frame sync signal, FC/RGDT, to initiate control data reads/writes. |

# Register 2. Control 2

| Bit  | D7 | D6 | D5 | D4 | D3  | D2 | D1  | D0  |

|------|----|----|----|----|-----|----|-----|-----|

| Name |    |    |    |    | AL  |    | HBE | RXE |

| Туре |    |    |    |    | R/W |    | R/W | R/W |

Reset settings = 0000\_0011

| Bit | Name     | Function                                                                                        |  |  |  |

|-----|----------|-------------------------------------------------------------------------------------------------|--|--|--|

| 7:4 | Reserved | Read returns zero.                                                                              |  |  |  |