- Meets EIA Standards RS-422-A, RS-423-A, RS-485, and CCITT V.11

- Designed to Operate With Pulse Durations as Short as 20 ns

- Designed for Multipoint Transmission on Long Bus Lines in Noisy Environments

- Input Sensitivity . . . ±200 mV

- Low-Power Consumption . . . 20 mA Max

- Open-Circuit Fail-Safe Design

- Common-Mode Input Voltage Range of –7 V to 12 V

## description

The SN55LBC175 is a monolithic quadruple differential line receiver with 3-state outputs and is designed to meet the requirements of the EIA Standards RS-422-A, RS-423-A, RS-485, and CCITT V.11. This device is optimized for balanced multipoint bus transmission at data rates up to and exceeding 10 million bits per second. The receivers are enabled in pairs with an active-high enable input. Each differential receiver input features high impedance, hysteresis for increased noise immunity, and sensitivity of ±200 mV over a common-mode input voltage range of 12 V to -7 V. Fail-safe design ensures that if the inputs are open-circuited, the outputs are always high. This device is designed using the Texas Instruments proprietary LinBiCMOS™ technology allowing low power consumption, high switching speeds, and robustness.

**FK PACKAGE**

NC - No internal connection

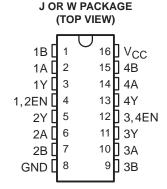

This device offers optimum performance when used with the SN55LBC174 quadruple line driver. The SN55LBC175 is available in the 16-pin CDIP (J) package, a 16-pin CPAK (W) package, or a 20-pin LCCC (FK) package.

The SN55LBC175 is characterized over the military temperature range of -55°C to 125°C.

## FUNCTION TABLE (each receiver)

| DIFFERENTIAL INPUTS<br>A-B                              | ENABLE | OUTPUT<br>Y |

|---------------------------------------------------------|--------|-------------|

| V <sub>ID</sub> ≥ 0.2 V                                 | Н      | Н           |

| $-0.2 \text{ V} < \text{V}_{\text{ID}} < 0.2 \text{ V}$ | Н      | ?           |

| V <sub>ID</sub> ≤ -0.2 V                                | Н      | L           |

| X                                                       | L      | Z           |

| Open circuit                                            | Н      | Н           |

H = high level, L = low level, X = irrelevant, Z = high impedance (off), ? = indeterminate

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinBiCMOS is a trademark of Texas Instruments.

## logic symbol†

#### 1,2EN ΕN \_ D 3 1A 1Y 1B 6 2A 2Y 2B 3,4EN ΕN 10 ⅎ 11 3A 3Y 9 3B 14 4A 13 15 4B

Pin numbers shown are for the J or W package.

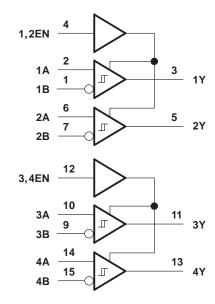

## logic diagram (positive logic)

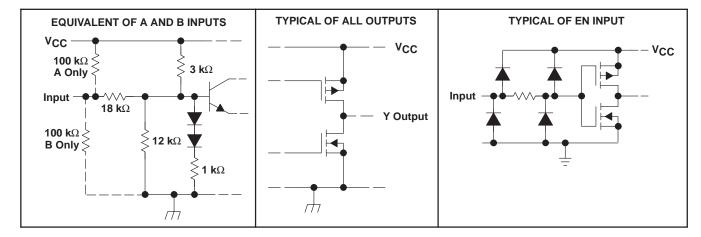

## schematics of inputs and outputs

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

## SN55LBC175 QUADRUPLE LOW-POWER DIFFERENTIAL LINE RECEIVER

SGLS083A - MARCH 1995 - REVISED JUNE 2000

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, V <sub>CC</sub> (see Note 1)           | –0.3 V to 7 V                |

|--------------------------------------------------------------|------------------------------|

| Input voltage, A or B inputs, V <sub>I</sub>                 | ±25 V                        |

| Differential input voltage, V <sub>ID</sub> (see Note 2)     | ±25 V                        |

| Data and control voltage range                               |                              |

| Continuous total dissipation                                 | See Dissipation Rating Table |

| Operating free-air temperature range, T <sub>A</sub>         | –55°C to 125°C               |

| Storage temperature range, T <sub>Stq</sub>                  | 65°C to 150°C                |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{A}} \le 25^{\circ}\mbox{C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 125°C<br>POWER RATING |

|---------|----------------------------------------------------|------------------------------------------------|----------------------------------------|

| FK      | 1375 mW                                            | 11.0 mW/°C                                     | 275 mW                                 |

| J       | 1375 mW                                            | 11.0 mW/°C                                     | 275 mW                                 |

| W       | 1000 mW                                            | 8.0 mW/°C                                      | 200 mW                                 |

## recommended operating conditions

|                                                |                                 | MIN | NOM | MAX  | UNIT |

|------------------------------------------------|---------------------------------|-----|-----|------|------|

| Supply voltage, V <sub>CC</sub>                | Supply voltage, V <sub>CC</sub> |     | 5   | 5.25 | V    |

| Common-mode input voltage, V <sub>IC</sub>     |                                 | -7  |     | 12   | V    |

| Differential input voltage, V <sub>ID</sub>    |                                 |     |     | ±6   | V    |

| High-level input voltage, V <sub>IH</sub>      | TNI inpute                      | 2   |     |      | V    |

| Low-level input voltage, V <sub>IL</sub>       | EN inputs                       |     |     | 0.8  | V    |

| High-level output current, IOH                 |                                 |     |     | -8   | mA   |

| Low-level output current, IOL                  |                                 |     |     | 16   | mA   |

| Operating free-air temperature, T <sub>A</sub> |                                 | -55 |     | 125  | °C   |

NOTES: 1. All voltage values are with respect to GND.

<sup>2.</sup> Differential input voltage is measured at the noninverting input with respect to the corresponding inverting input.

SGLS083A - MARCH 1995 - REVISED JUNE 2000

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                   | PARAMETER                              |                    | TE                          | ST CONDITIO              | ONS                    | MIN  | TYP  | MAX  | UNIT |

|-------------------|----------------------------------------|--------------------|-----------------------------|--------------------------|------------------------|------|------|------|------|

| V <sub>IT+</sub>  | Positive-going input thresho           | ld voltage         | $I_O = -8 \text{ mA}$       |                          |                        |      | 0.2  | V    |      |

| V <sub>IT</sub> - | Negative-going input thresh            | old voltage        | $I_O = 8 \text{ mA}$        |                          |                        | -0.2 |      |      | V    |

| V <sub>hys</sub>  | Hysteresis voltage (V <sub>IT+</sub> - | V <sub>IT</sub> -) |                             |                          |                        |      | 45   |      | mV   |

| VIK               | Enable input clamp voltage             |                    | $I_{I} = -18 \text{ mA}$    |                          |                        |      | -0.9 | -1.5 | V    |

| Vон               | High-level output voltage              |                    | $V_{ID} = 200 \text{ mV},$  | I <sub>OH</sub> = -8 m/  | 4                      | 3.5  | 4.5  |      | V    |

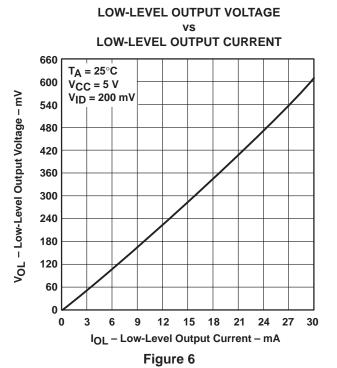

| \/                | Low lovel output voltage               |                    | $V_{ID} = -200 \text{ mV},$ | $I_{OL} = 8 \text{ mA}$  |                        |      | 0.3  | 0.5  | V    |

| VOL               | Low-level output voltage               |                    | $V_{ID} = -200 \text{ mV},$ | $I_{OL} = 8 \text{ mA},$ | T <sub>A</sub> = 125°C |      |      | 0.7  | V    |

| loz               | High-impedance-state output            | ut current         | $V_O = 0 V to V_{CC}$       |                          |                        |      |      | ±20  | μΑ   |

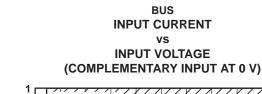

|                   |                                        |                    | V <sub>IH</sub> = 12 V,     | $V_{CC} = 5 V$ ,         | Other inputs at 0 V    |      | 0.7  | 1    |      |

| l                 | Bus input current                      | A or B             | V <sub>IH</sub> = 12 V,     | $V_{CC} = 0 V$ ,         | Other inputs at 0 V    |      | 0.8  | 1    | mA   |

| '1                | bus input current                      | inputs             | $V_{IH} = -7 V$ ,           | $V_{CC} = 5 V$ ,         | Other inputs at 0 V    |      | -0.5 | -0.8 | IIIA |

|                   |                                        |                    | $V_{IH} = -7 V$ ,           | $V_{CC} = 0 V$ ,         | Other inputs at 0 V    |      | -0.4 | -0.8 |      |

| lн                | High-level enable input curr           | ent                | V <sub>IH</sub> = 5 V       |                          |                        |      |      | ±20  | μΑ   |

| I <sub>IL</sub>   | Low-level enable input curre           | ent                | V <sub>IL</sub> = 0 V       |                          |                        |      |      | -20  | μΑ   |

| los               | Short-circuit output current           |                    | V <sub>O</sub> = 0          |                          |                        | ·    | -80  | -120 | mA   |

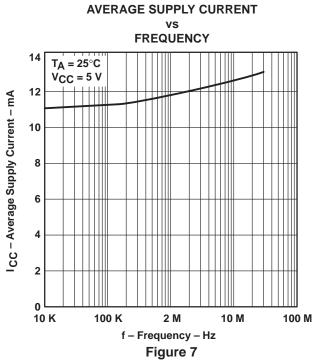

| laa               | Supply current                         |                    | Outputs enabled,            | $I_{O} = 0$ ,            | V <sub>ID</sub> = 5 V  |      | 11   | 20   | mA   |

| Licc              | ICC Supply current                     |                    | Outputs disabled            |                          |                        |      | 0.9  | 1.4  | IIIA |

<sup>&</sup>lt;sup>†</sup> All typical values are at  $V_{CC}$  = 5 V and  $T_A$  = 25°C.

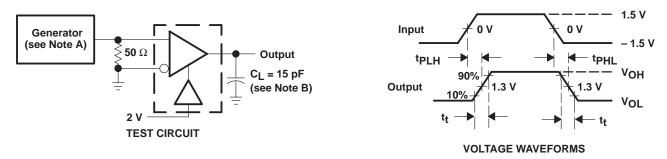

## switching characteristics, $V_{CC} = 5 \text{ V}$ , $C_L = 15 \text{ pF}$

|                  | PARAMETER                                                 | TEST CONDITIONS                              | TA             | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------------------------------------|----------------------------------------------|----------------|-----|-----|-----|------|

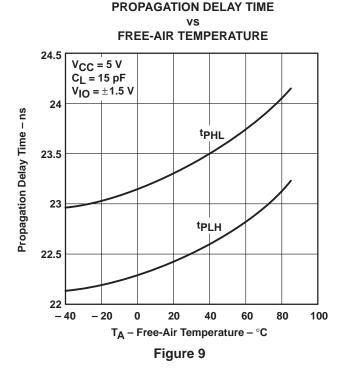

| tn               | Propagation delay time high to law level output           | $V_{ID} = -1.5 \text{ V to } 1.5 \text{ V},$ | 25°C           | 11  | 22  | 30  | ns   |

| PHL              | tem Propagation delay time. high- to low-level output 1 — |                                              | −55°C to 125°C |     |     | 35  | 115  |

| tour             | Propagation delay time, low- to high-level output         | $V_{ID} = -1.5 \text{ V to } 1.5 \text{ V},$ | 25°C           | 11  | 22  | 30  | ns   |

| <sup>t</sup> PLH | 1 Topagation delay time, low- to high-level output        | See Figure 1                                 | -55°C to 125°C |     |     | 35  | ns   |

| t                | 4 Outrot anable time to binb lovel                        | 25°C                                         |                | 17  | 40  | ne  |      |

| <sup>t</sup> PZH | Output enable time to high level                          | See Figure 2                                 | -55°C to 125°C |     |     | 45  | ns   |

|                  | Output enable time to low level                           | Soo Eiguro 2                                 | 25°C           |     | 18  | 30  | ns   |

| tPZL             | Output enable time to low level                           | See Figure 3                                 | -55°C to 125°C |     |     | 35  | 115  |

|                  | Output dipable time from high level                       | See Figure 2                                 | 25°C           |     | 30  | 40  | 20   |

| tPHZ             | Output disable time from high level                       | See Figure 2                                 | -55°C to 125°C |     |     | 55  | ns   |

| ·                | Output disable time from low level                        | See Figure 3                                 | 25°C           |     | 23  | 30  | no   |

| <sup>t</sup> PLZ | Output disable time from low level                        | See Figure 3                                 | -55°C to 125°C |     |     | 45  | ns   |

| 4                | Con Firms 4                                               | 25°C                                         |                | 4   | 6   |     |      |

| tsk(p)           | Pulse skew ( tpHL - tpLH )                                | See Figure 1                                 | -55°C to 125°C |     |     | 7   | ns   |

| +.               | The control of the c                                      | See Figure 1                                 | 25°C           |     | 3   | 10  | no   |

| t <sub>t</sub>   | Transition time                                           |                                              | −55°C to 125°C |     |     | 16  | ns   |

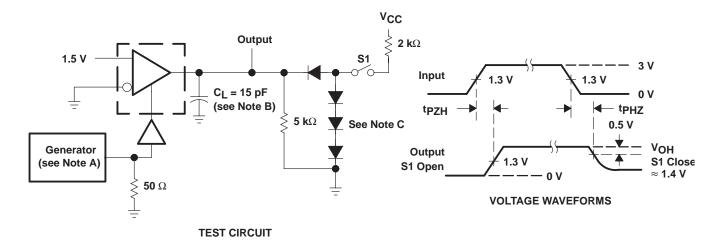

#### PARAMETER MEASUREMENT INFORMATION

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, duty cycle  $\leq$  50%,  $t_{\text{f}} \leq$  6 ns,  $t_{\text{f}} \leq$  7 ns,  $t_{\text{f}} \leq$  8 ns,  $t_{\text{f}} \leq$  9 ns, t

- B. C<sub>I</sub> includes probe and jig capacitance.

Figure 1. tpLH and tpHL Test Circuit and Voltage Waveforms

NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, duty cycle  $\leq$  50%,  $t_f \leq$  6 ns,  $t_f \leq$  7 ns,  $t_f \leq$  8 ns,  $t_f \leq$  9 ns,  $t_$

- B. C<sub>L</sub> includes probe and jig capacitance.

- C. All diodes are 1N916 or equivalent.

Figure 2. t<sub>PHZ</sub> and t<sub>PZH</sub> Test Circuit and Voltage Waveforms

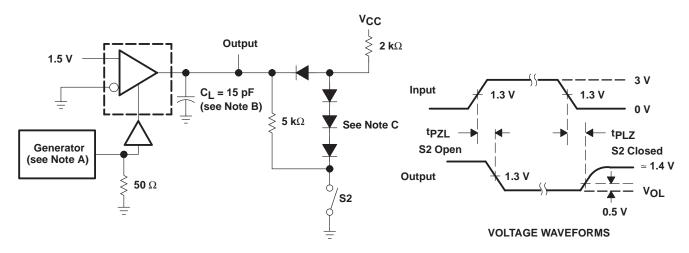

#### PARAMETER MEASUREMENT INFORMATION

**TEST CIRCUIT**

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR = 1 MHz, duty cycle  $\leq$  50%,  $t_{\Gamma} \leq$  6 ns,  $t_{f} \leq$  6 ns,  $t_{O} =$  50  $\Omega$ .

- B. C<sub>L</sub> includes probe and jig capacitance.

- C. All diodes are 1N916 or equivalent.

Figure 3. tpzL and tpLZ Test Circuit and Voltage Waveforms

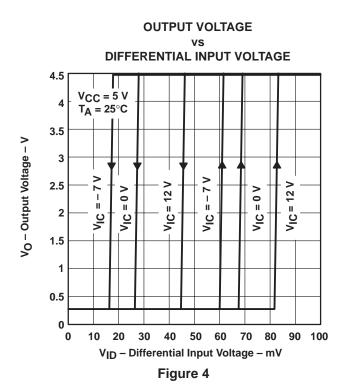

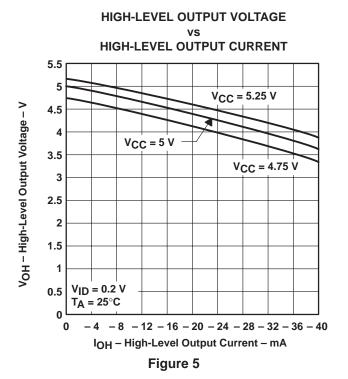

#### TYPICAL CHARACTERISTICS

#### TYPICAL CHARACTERISTICS

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated