# MICROCIRCUIT DATA SHEET

Original Creation Date: 05/18/95 Last Update Date: 08/24/98 Last Major Revision Date: 09/02/97

# LOW POWER LOW OFFSET VOLTAGE DUAL COMPARATORS

# General Description

MNLM193A-X REV 1A2

The LM193A consists of two independent precision voltage comparators with an offset voltage specification as low as 2.0mV max for two comparators which were designed specifically to operate from a single power supply over a wide range of voltages. Operation from split power supplies is also possible and the low power supply current drain is independent of the magniture of the power supply voltage. These comparators also have a unique characteristic in that the input common-mode voltage range includes ground, even though operated from a single power supply voltage.

Application areas include limit comparators, simple analog to digital converters; pulse, squarewave and time delay generators; wide range VCO; MOS clock timers; multivibrators and high voltage digital logic gates. The LM193A was designed to directly interface with TTL and CMOS. When operated from both plus and minus power supplies, the LM193A will directly interface with MOS logic where their low power drain is a distinct advantage over standard comparators.

# Industry Part Number

NS Part Numbers

LM193A

LM193AH-QMLV\*\* LM193AH/883\* LM193AJ-QMLV\*\*\* LM193AJ/883\*\*\*\*

### Prime Die

LM193A

### Controlling Document

See Features Page

| Processing                     | Subgrp | Description         | Temp ( $^{\circ}$ C) |

|--------------------------------|--------|---------------------|----------------------|

| MIL-STD-883, Method 5004       | 1      | Static tests at     | +25                  |

|                                | 2      | Static tests at     | +125                 |

|                                | 3      | Static tests at     | -55                  |

| Quality Conformance Inspection | 4      | Dynamic tests at    | +25                  |

| 2                              | 5      | Dynamic tests at    | +125                 |

| MIL-STD-883, Method 5005       | 6      | Dynamic tests at    | -55                  |

| MIL BID 003, Meellod 3003      | 7      | Functional tests at | +25                  |

|                                | 8A     | Functional tests at | +125                 |

|                                | 8B     | Functional tests at | -55                  |

|                                | 9      | Switching tests at  | +25                  |

|                                | 10     | Switching tests at  | +125                 |

|                                | 11     | Switching tests at  | -55                  |

# **Features**

| - Wide sup | pply |

|------------|------|

|------------|------|

- Voltage range 2.0Vdc to 36Vdc - Single or dual supplies  $\pm 1.0$ Vdc to  $\pm 18$ Vdc

- Very low supply current drain (0.4mA) independent of supply voltage

- Low input biasing current 25nA Typ - Low input offset current  $\pm 3nA$  Typ

- Input common-mode voltage range includes ground

- Differential input voltage range equal to the power supply voltage

- Low output saturation voltage 250mV at 4mA Typ

- Output voltage compatible with TTL, DTL, ECL, MOS and CMOS logic systems

- SMD : 5962-9452602MGA\*, VGA\*\*, VPA\*\*\*, MPA\*\*\*\*

# (Absolute Maximum Ratings)

(Note 1)

Supply Voltage, V+ 36Vdc or  $\pm 18Vdc$ Differential Input Voltage (Note 6) 36Vdc Input Voltage -0.3Vdc to +36VdcInput Current (Vin < -0.3 Vdc)</pre> (Note 5) 50mA Maximum Junction Temperature 150 C Power Dissipation (Note 2, 3) METAL CAN 660mW CERDIP 780mW Output Short-Circuit to Gnd (Note 4) Continuous Operating Temperature Range -55 C to +125 C Thermal Resistance ThetaJA METAL CAN (Still Air) 174 C/W (500LF/Min Air flow) 99 C/W CERDIP (Still Air) 146 C/W 85 C/W (500LF/Min Air flow) ThetaJC METAL CAN 44 C/W CERDIP 33 C/W Lead Temperature (Soldering, 10 seconds) +260 C ESD Tolerance (Note 7) 500V

- Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- Note 2: The maximum power dissipation must be derated at elevated temperatures and is dictated by Tjmax (maximum junction temperature), ThetaJA (package junction to ambient thermal resistance), and TA (ambient temperature). The maximum allowable power dissipation at any temperature is Pdmax = (Tjmax TA)/ThetaJA or the number given in the Absolute Maximum Ratings, whichever is lower.

- given in the Absolute Maximum Ratings, whichever is lower.

Note 3: The LM193A must be derated based on a 150 C maximum junction temperature. The low bias dissipation and the ON-OFF characteristic of the outputs keeps the chip dissipation very small (PD<100mV), provided the output transistors are allowed to saturate.

- Note 4: Short circuits from the output to V+ can cause excessive heating and eventual destruction. When considering short circuits to ground, the maximum output current is approximately 20mA independent of the magnitude of V+.

# (Continued)

- Note 5: This input current will only exist when the voltage at any of the input leads is driven negative. It is due to the collector-base junction of the input PNP transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V+ voltage level (or to ground for a large overdrive) for the time duration that an input is driven negative. This is not destructive and normal output states will re-establish when the input voltage, which was negative, again returns to a value greater than -0.3Vdc.

- Note 6: Positive excursions of input voltage may exceed the power supply level. As long as the other voltage remains within the common-mode range, the comparator will provide a proper output state. The low input voltage state must not be less than -0.3Vdc (or 0.3Vdc below the magnitude of the negative power supply, if used).

- Note 7: Human body model, 1.5K Ohms in series with 100pF.

# Electrical Characteristics

# DC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) DC: V+=5V, Vcm=0

| SYMBOL |                                 |                                               |   |  | MIN   | MAX  | UNIT | SUB-<br>GROUPS |

|--------|---------------------------------|-----------------------------------------------|---|--|-------|------|------|----------------|

| Icc    | Supply Current                  | Rl = Infinity                                 |   |  |       | 1.0  | mA   | 1, 2,          |

|        |                                 | V+ = 36V, Rl = Infinity                       |   |  |       | 2.5  | mA   | 1, 2,          |

| Icex   | Output Leakage<br>Current       | V+ = 30V, Vin+ = 1V, Vo = 30, Vin- = 0        |   |  | -0.65 | 0.65 | uA   | 1              |

|        |                                 |                                               |   |  | -1.0  | 1.0  | uA   | 2, 3           |

| Isink  | Output Sink<br>Current          | Vo = 1.5V, Vin- = 1V, Vin+ = 0                |   |  | 6.0   |      | mA   | 1              |

|        |                                 |                                               |   |  | 4.0   |      | mA   | 2, 3           |

| Vsat   | Output Saturation<br>Voltage    | Isink = 4mA, Vin- = 1V, Vin+ = 0              |   |  |       | 0.4  | V    | 1              |

|        |                                 |                                               |   |  |       | 0.7  | V    | 2, 3           |

| Vio    | Input Offset<br>Voltage         |                                               |   |  | -2.0  | 2.0  | mV   | 1              |

|        |                                 |                                               |   |  | -4.0  | 4.0  | mV   | 2, 3           |

|        |                                 | V+ = 30V, $Vcm = 0$                           |   |  | -2.0  | 2.0  | mV   | 1              |

|        |                                 |                                               |   |  | -4.0  | 4.0  | mV   | 2, 3           |

|        |                                 | V+ = 30V, Vcm = 28.5V                         |   |  | -2.0  | 2.0  | mV   | 1              |

|        |                                 | V+ = 30V, Vcm = 28.0V                         |   |  | -4.0  | 4.0  | mV   | 2, 3           |

| Iib+   | Input Bias<br>Current           | Vout = 1.5V                                   |   |  | -100  | -1   | nA   | 1              |

|        | Carrene                         |                                               |   |  | -300  | -1   | nA   | 2, 3           |

| Iib-   | Input Bias<br>Current           | Vout = 1.5V                                   |   |  | -100  | -1   | nA   | 1              |

|        | Carrene                         |                                               |   |  | -300  | -1   | nA   | 2, 3           |

| Iio    | Input offset<br>Current         | Rs = 50 Ohms, Vout = 1.5V                     |   |  | -25   | 25   | nA   | 1              |

|        |                                 |                                               |   |  | -100  | 100  | nA   | 2, 3           |

| Vcm    | Common Mode<br>Voltage          | V+ = 30V                                      | 1 |  |       | 28.5 | V    | 1              |

|        |                                 |                                               | 1 |  |       | 28   | V    | 2, 3           |

| PSRR   | Power Supply<br>Rejection Ratio | V+ = 5V to 30V, Rs = 50 Ohms                  |   |  | 60    |      | dB   | 1              |

| CMRR   | Common Mode<br>Rejection Ratio  | V+ = 30V, Vcm = 0V to 28.5V,<br>Rs = 50 Ohms  |   |  | 60    |      | dB   | 1              |

| Vdiff  | Differential<br>Input Voltage   | V+ = 30V, +Vin = 36V, -Vin = 0V               |   |  |       | 500  | nA   | 1, 2,          |

|        |                                 | V+ = 30V, +Vin = 0V, -Vin = +36V              |   |  |       | 500  | nA   | 1, 2,          |

| Avs    | Voltage Gain                    | V+ = 15V, 1V <= Vout <= 11V,<br>RPULLUP = 15K | 2 |  | 50    |      | V/mV | 4              |

|        |                                 | 10000 - 100                                   | 2 |  | 25    |      | V/mV | 5, 6           |

# Electrical Characteristics

# AC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) AC: Vcc = 5V, Vcm = 0

| SYMBOL | PARAMETER     | CONDITIONS           | NOTES | PIN-<br>NAME | MIN | MAX | UNIT | SUB-<br>GROUPS |

|--------|---------------|----------------------|-------|--------------|-----|-----|------|----------------|

| tRLH   | Response Time | V+ = 5V, $Vod = 5mV$ | 3     |              |     | 5.0 | uS   | 9              |

|        |               | V+ = 5V, Vod = 50mV  | 3     |              |     | 0.8 | uS   | 9              |

| tRHL   | Response Time | V+ = 5V, $Vod = 5mV$ | 3     |              |     | 2.5 | uS   | 9              |

|        |               | V+ = 5V, Vod = 50mV  | 3     |              |     | 0.8 | uS   | 9              |

# DC PARAMETERS: DRIFT VALUES

(The following conditions apply to all the following parameters, unless otherwise specified.) DC: V+ = 5V, Vcm = 0. "Delta calculations performed on Jan S and QMLV devices at Group B, Subgroup 5 ONLY."

| Vio  | Input Offset<br>Voltage | V+ = 30V, Vcm = 0 |  | -1  | 1  | mV | 1 |

|------|-------------------------|-------------------|--|-----|----|----|---|

| lib+ | Input Bias<br>Current   |                   |  | -15 | 15 | nA | 1 |

| Iib- | Input Bias<br>Current   |                   |  | -15 | 15 | nA | 1 |

Note 1: Parameter guaranteed by the Vio tests Note 2: Datalog reading in K = V/mV. Note 3: Bench Tested

# Graphics and Diagrams

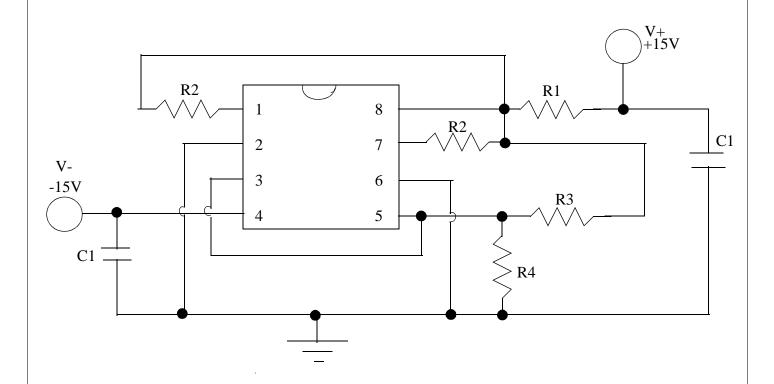

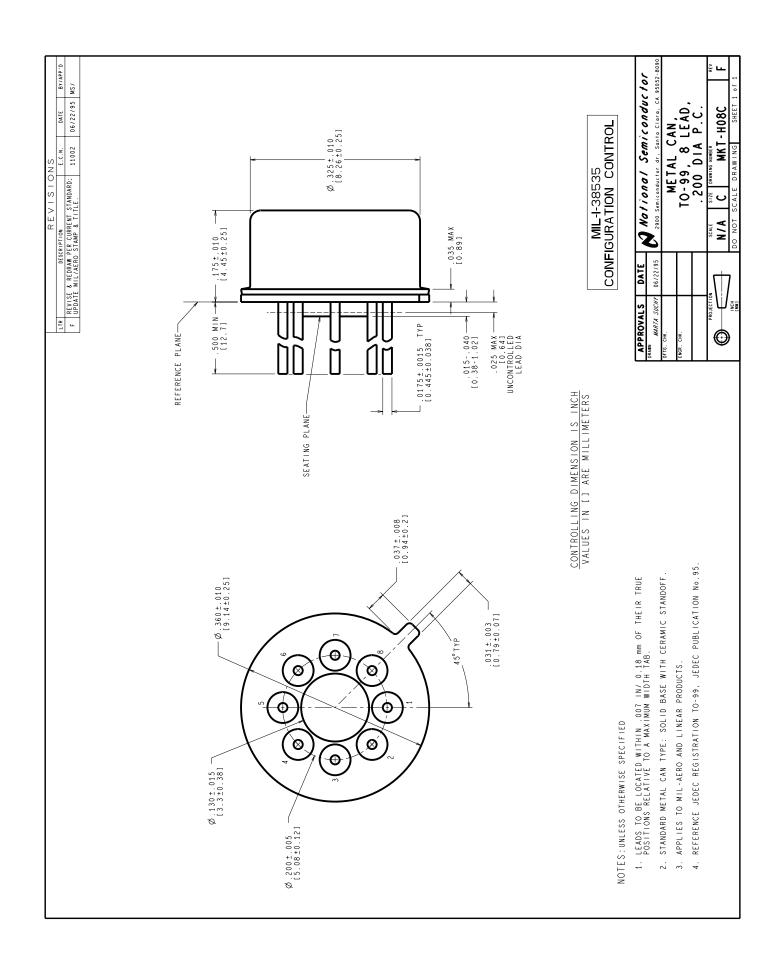

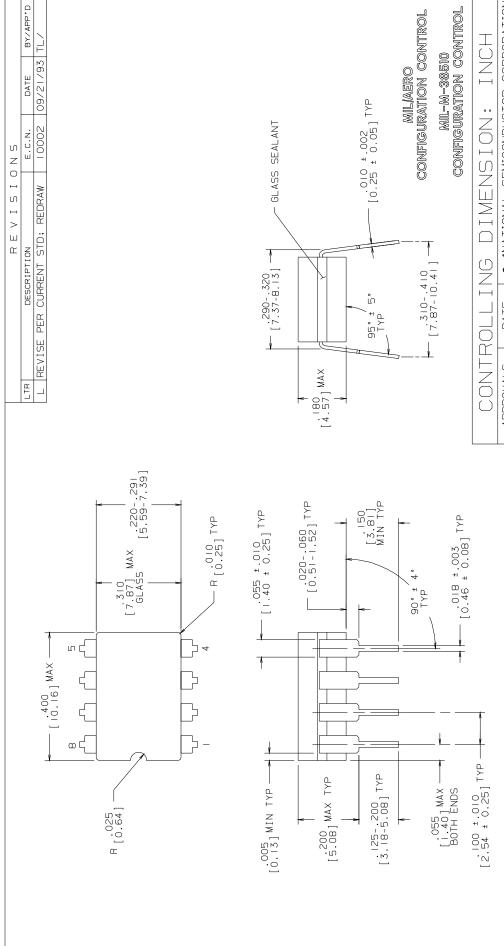

| GRAPHICS# | DESCRIPTION                                        |

|-----------|----------------------------------------------------|

| 05363HRA2 | METAL CAN (H), TO-99, 8LD, .200 DIA P.C. (B/I CKT) |

| 06048HRA2 | CERDIP (J), 8 LEAD (B/I CKT)                       |

| H08CRF    | METAL CAN (H), TO-99, 8LD, .200 DIA P.C. (P/P DWG) |

| J08ARL    | CERDIP (J), 8 LEAD (P/P DWG)                       |

| P000171A  | METAL CAN (H), TO-99, 8LD, .200 DIA P.C. (PINOUT)  |

| P000172B  | CERDIP (J), 8 LEAD (PINOUT)                        |

See attached graphics following this page.

GENERAL NOTES:

1. GENERIC - INDUSTRY TYPE DEVICES THAT MAY BE USED WITH THIS CIRCUIT SHALL BE AS SPECIFIED IN NSC BURN-IN CIRCUIT LIST R512B-04.

NSC BURN-IN CIRCUIT LIST RS12B-04.

2. ALL 1/4 AND 1/2 WATT RESISTORS SHALL BE METAL FILM.

ALL 1, 2, AND 3 WATT RESISTORS SHALL BE WIRE WOUND.

TOLERANCE SHALL BE +/-5% UNLESS OTHERWISE SPECIFIED.

3. ALL VOLTAGES SPECIFIED SHALL BE MEASURED AT THE

"DEVICE UNDER TEST" PIN AND SHALL BE MINIMUM VALUES

UNLESS OTHERWISE SPECIFIED.

4. WHEN ADDITIONAL CONCEPTIONS SPECIFIED SHALL HAVES

WHEN APPLICABLE, CLOCK PULSES SPECIFIED SHALL HAVE 50% DUTY CYCLE.

5. THIS DRAWING COMPLIES WITH MIL-PRF-38535, WHEN APPLICABLE.

| ECN   | REV | APPROVALS | DATE   |

|-------|-----|-----------|--------|

| 03136 | A1  | R Wallace | 6/5/89 |

| 07375 | A2  | J. GOMEZ  | 9/2/97 |

| 0.0.0 |     |           |        |

|       |     |           |        |

|       |     |           |        |

|       |     |           |        |

|                | т        |      | L     | OUT CONDITIONS |      |      |         |        | PONENT | REQUIREMENTS PER POSITION |

|----------------|----------|------|-------|----------------|------|------|---------|--------|--------|---------------------------|

| YMBOL          | LIM      | ITS  | UNITS | CVADOL         | LI   | MITS | LINITEG | REF    | OTY    | DESCRIPTION               |

| IMBOL          | MIN.     | MAX. | UNIIS | SYMBOL         | MIN. | MAX. | UNITS   | DESIG. | QII    | DESCRIPTION               |

| $\mathbf{V}$ + | 15       | 17   | VOLTS |                |      |      |         | R1     | 1      | 100 OHM 1/4 WATT          |

| V-             | -17      | -15  | VOLTS |                |      |      |         | R2     | 2      | 7.5K OHM 1/2 WATT         |

|                |          |      |       |                |      |      |         | R3     | 1      | 15K OHM 1/4 WATT          |

|                |          |      |       |                |      |      |         | R4     | 1      | 1K OHM 1/4 WATT           |

|                |          |      |       |                |      |      |         | C1     | 2      | 0.1uF 20% X7R             |

|                |          |      |       |                |      |      |         |        |        |                           |

| OTES:          |          |      |       |                |      | •    |         |        |        |                           |

|                | DTNI 1 F | ,    |       |                |      |      |         |        |        |                           |

| DFC            | PIN 1,   | •    |       |                |      |      |         |        |        |                           |

|                |          |      |       |                |      |      |         | -      |        |                           |

|                |          |      |       |                |      |      |         |        |        |                           |

| National Semiconductor~                           |

|---------------------------------------------------|

| MIL/AEROSPACE OPERATIONS                          |

| 2900 SEMICONDUCTOR DRIVE<br>SANTA CLARA, CA 95050 |

| BURN-IN C  | IRCUIT |     |                 |   |     |     |      |            | SH 1     | OF      | 1         |

|------------|--------|-----|-----------------|---|-----|-----|------|------------|----------|---------|-----------|

| CUSTOMER   |        |     | PACKAGE<br>TYPE | D | /J8 | MIL |      | NSC LM193  | TEST CON | NDITION | C         |

| ORIGINATOR | DATE   | CHE | CKED BY         |   | DAT | E   | DRAW | ING NUMBER |          | REV     |           |

| J.GOMEZ    | 9/2/97 |     |                 |   |     |     |      | 060        | 048HR    |         | <b>A2</b> |

NATIONAL SEMICONDUCTOR CORPORATION 2900 Semiconductor Drive, Santa Clara, CA 95052-8090 MKT-J08A CERDIP (, 8 LEAD  $\forall$ | DRAWN\_T. LEQUANG | 09/21/93 DATE PROJECTION APPROVALS DFTG. CHK. ENGR. CHK. APPROVAL

> 1. LEAD FINISH TO BE 200 MICROINCHES / 5.08 MICROMETERS MINIMUM SOLDER MEASURED AT THE CREST OF THE MAJOR FLATS. 2. JEDEC REGISTRATION MO-036, VARIATION AA, DATED 04/1981.

NOTES: UNLESS OTHERWISE SPECIFIED

R V

DO NOT SCALE DRAWING SHEET

INC ME

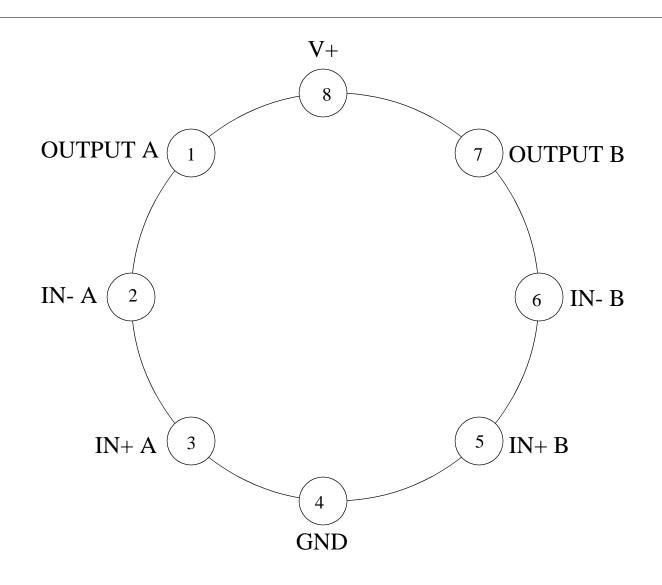

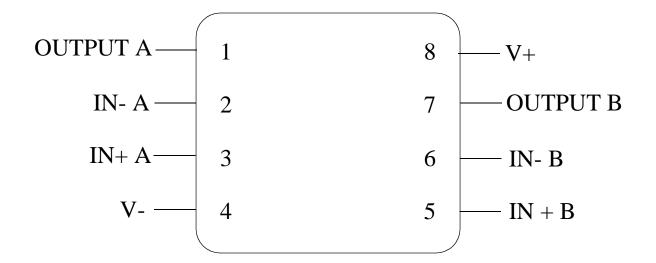

LM193AH, LM193H

8 - PIN METAL CAN

CONNECTION DIAGRAM

TOP VIEW

P000171A

# LM193J, LM193AJ 8 - LEAD DIP CONNECTION DIAGRAM TOP VIEW P000172B

# Revision History

| Rev | ECN #    | Rel Date | Originator    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|----------|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1A1 | M0002587 | 08/24/98 | Barbara Lopez | Changed MDS: MNLM193A-X Rev. 0C0 to MNLM193A-X Rev. 1A1. Added QMLV device types and SMD numbers on Main Table. Updated CERDIP power dissipation limit to 780ml in Absolute section. Added (Rl = Infinity) to Icc condition. Added (Vout = 1.5V) to Iib± and Iio condition. Changed drift values for Vio (from -0.5mV to -1mV min), and (0.5mV to 1mV max). Changed IIb± (from -10nA to -15nA min), and (10nA to 15nA max). Deleted Iio parmeter. Updated drift note. Added graphics for Burn-In (H and J Pkg). Added Pinouts for (H and J Pkg). Corrected Subgroup (7 to 9) to reflect MIL-STD-883. |

| 1A2 | M0002817 | 08/24/98 | Rose Malone   | Update MDS: MNLM193A-X, Rev. 1A1 to MNLM193A-X, Rev. 1A2. Main Table Adding reference to LM193AJ/883 and SMD number, B/I CKTS and Pin Out for J pkg.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |