# ISL6327

#### Data Sheet

#### April 21, 2006

FN9276.0

# Enhanced 6-Phase PWM Controller with 8-Bit VID Code and Differential Inductor DCR or Resistor Current Sensing

intercil

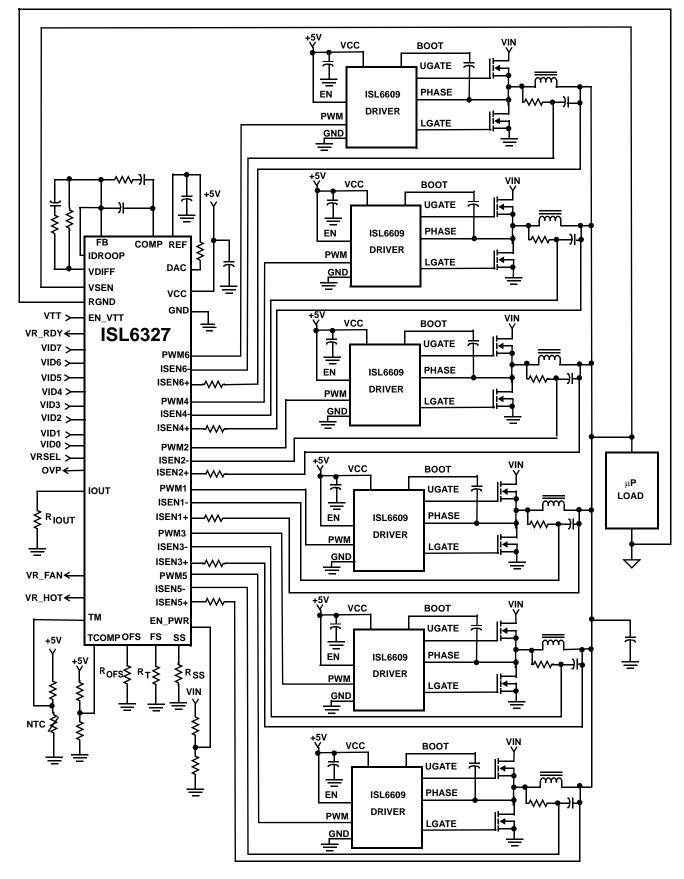

The ISL6327 controls microprocessor core voltage regulation by driving up to 6 synchronous-rectified buck channels in parallel. Multiphase buck converter architecture uses interleaved timing to multiply channel ripple frequency and reduce input and output ripple currents. Lower ripple results in fewer components, lower component cost, reduced power dissipation, and smaller implementation area.

Microprocessor loads can generate load transients with extremely fast edge rates. The ISL6327 utilizes Intersil's proprietary Active Pulse Positioning (APP) and Adaptive Phase Alignment (APA) modulation scheme to achieve the extremely fast transient response with fewer output capacitors.

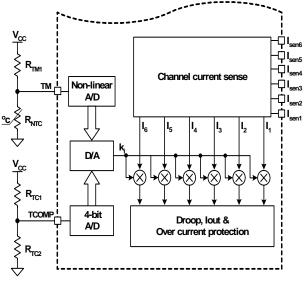

Today's microprocessors require a tightly regulated output voltage position versus load current (droop). The ISL6327 senses the output current continuously by utilizing patented techniques to measure the voltage across the dedicated current sense resistor or the DCR of the output inductor. Current sensing provides the needed signals for precision droop, channel-current balancing, and overcurrent protection. A programmable integrated temperature compensation function is implemented to effectively compensate the temperature variation of the current sense element. The current limit function provides the overcurrent protection for the individual phase.

A unity gain, differential amplifier is provided for remote voltage sensing. Any potential difference between remote and local grounds can be completely eliminated using the remote-sense amplifier. Eliminating ground differences improves regulation and protection accuracy. The threshold-sensitive enable input is available to accurately coordinate the start up of the ISL6327 with any other voltage rail. Dynamic-VID<sup>TM</sup> technology allows seamless on-the-fly VID changes. The offset pin allows accurate voltage offset settings that are independent of VID setting.

#### Features

- Proprietary Active Pulse Positioning and Adaptive Phase Alignment Modulation Scheme

- Precision Multiphase Core Voltage Regulation

- Differential Remote Voltage Sensing

- $\pm 0.5\%$  System Accuracy Over Life, Load, Line and Temperature

- Adjustable Precision Reference-Voltage Offset

- Precision Resistor or DCR Current Sensing

- Accurate Load-Line Programming

- Accurate Channel-Current Balancing

- Differential Current Sense

- Microprocessor Voltage Identification Input

- Dynamic VID™ Technology

- 8-Bit VID Input with Selectable VR11 code and Extended VR10 Code at 6.25mV Per Bit

- 0.5V to 1.600V Operation Range

- Thermal Monitoring

- Integrated Programmable Temperature Compensation

- · Overcurrent Protection and Channel Current Limit

- Overvoltage Protection with OVP Output Indication

- 2, 3, 4, 5 or 6 Phase Operation

- Adjustable Switching Frequency up to 1MHz Per Phase

- Package Option

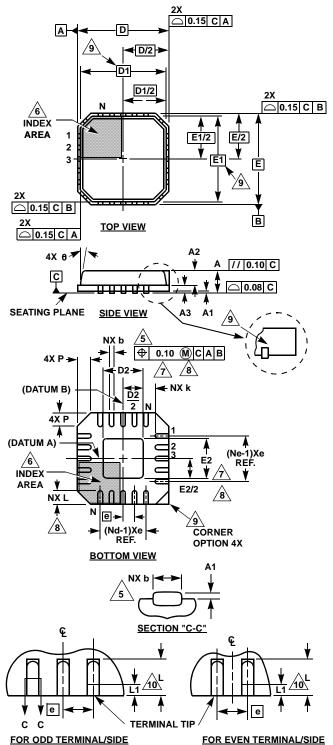

- QFN Compliant to JEDEC PUB95 MO-220 QFN Quad Flat No Leads - Product Outline

- QFN Near Chip Scale Package Footprint; Improves PCB Efficiency, Thinner in Profile

- Pb-Free Plus Anneal Available (RoHS Compliant)

# **Ordering Information**

| PART<br>NUMBER | PART<br>MARKING | TEMP.<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|----------------|-----------------|---------------|----------------------|----------------|

| ISL6327CRZ     | ISL6327CRZ      | 0 to70        | 48 Ld 7x7 QFN        | L48.7x7        |

| ISL6327IRZ     | ISL6327IRZ      | -40 to 85     | 48 Ld 7x7 QFN        | L48.7x7        |

Add "-T" suffix for tape and reel.

NOTE: Intersil Pb-free plus anneal products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate termination finish, which are RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

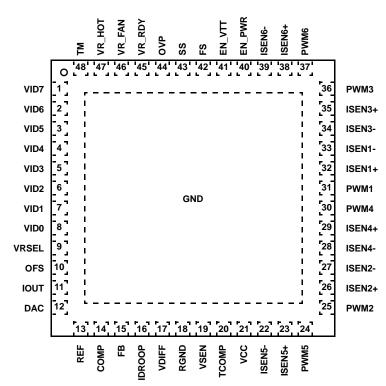

ISL6327 (48 LD QFN) TOP VIEW

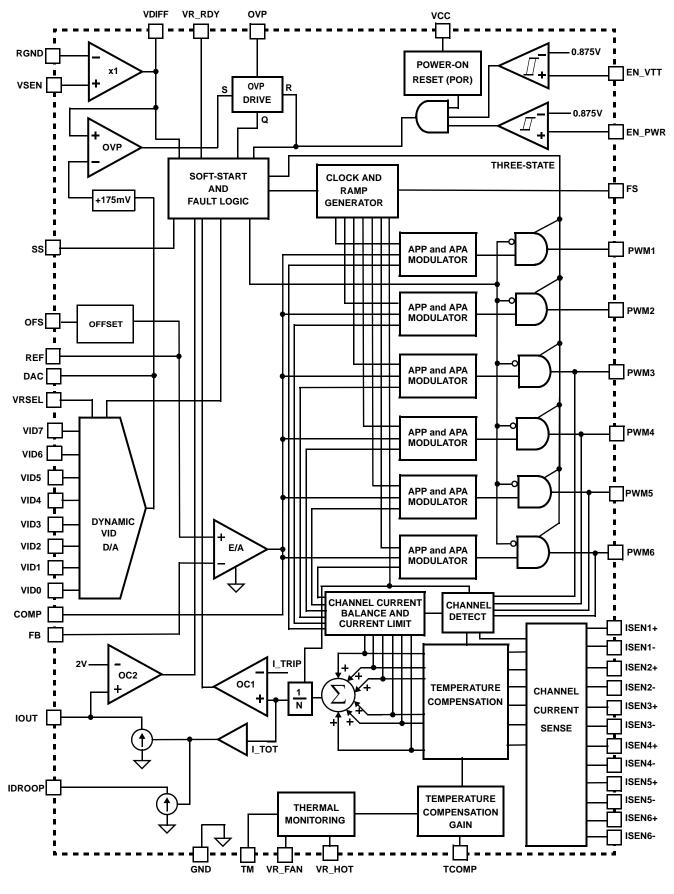

Typical Application - 6-Phase Buck Converter with DCR Sensing and External TCOMP

#### **Absolute Maximum Ratings**

| Supply Voltage, VCC                | +6V  |

|------------------------------------|------|

| All Pins GND -0.3V to $V_{CC}$ + ( | ).3V |

| ESD (Human Body Model)>            | 2kV  |

| ESD (Machine Model)>2              | .00V |

| ESD (Charged Device Model)>1       | 5kV  |

## **Operating Conditions**

| Supply Voltage, VCC +5                 | V ±5%  |

|----------------------------------------|--------|

| Ambient Temperature (ISL6327CRZ) 0°C t | o 70°C |

| Ambient Temperature (ISL6327IRZ)40°C t | o 85°C |

#### Thermal Information

| Thermal Resistance (Typical, Notes 1, 2)       | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |  |  |  |  |  |  |

|------------------------------------------------|------------------------|------------------------|--|--|--|--|--|--|

| QFN Package                                    | 32                     | 3.5                    |  |  |  |  |  |  |

| Maximum Junction Temperature                   |                        | 150°C                  |  |  |  |  |  |  |

| Maximum Storage Temperature Range65°C to 150°C |                        |                        |  |  |  |  |  |  |

| Maximum Lead Temperature (Soldering 1          | 0s)                    | 300°C                  |  |  |  |  |  |  |

CAUTION: Stress above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied.

#### NOTES:

- 1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

## **Electrical Specifications** Operating Conditions: VCC = 5V, Unless Otherwise Specified

| PARAMETER                                                                        | TEST CONDITIONS                                                                                                   | MIN      | ТҮР   | MAX   | UNITS |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|----------|-------|-------|-------|

| VCC SUPPLY CURRENT                                                               |                                                                                                                   |          |       |       |       |

| Nominal Supply                                                                   | VCC = 5VDC; EN_PWR = 5VDC; $R_T$ = 100k $\Omega$ ,<br>ISEN1 = ISEN2 = ISEN3 = ISEN4 = ISEN5 = ISEN6 = -70 $\mu$ A | -        | 18    | 26    | mA    |

| Shutdown Supply                                                                  | VCC = 5VDC; EN_PWR = 0VDC; $R_T = 100k\Omega$                                                                     | -        | 14    | 21    | mA    |

| POWER-ON RESET AND ENABLE                                                        |                                                                                                                   |          |       |       |       |

| POR Threshold                                                                    | VCC Rising                                                                                                        | 4.3      | 4.5   | 4.7   | V     |

|                                                                                  | VCC Falling                                                                                                       | 3.7      | 3.9   | 4.2   | V     |

| EN_PWR Threshold                                                                 | Rising                                                                                                            | 0.850    | 0.875 | 0.910 | V     |

|                                                                                  | Hysteresis                                                                                                        | -        | 130   | -     | mV    |

|                                                                                  | Falling                                                                                                           | 0.720    | 0.745 | 0.775 | V     |

| EN_VTT Threshold                                                                 | Rising                                                                                                            | 0.850    | 0.875 | 0.910 | V     |

|                                                                                  | Hysteresis                                                                                                        | -        | 130   | -     | mV    |

|                                                                                  | Falling                                                                                                           | 0.720    | 0.745 | 0.775 | V     |

| REFERENCE VOLTAGE AND DAC                                                        |                                                                                                                   | <b>I</b> |       |       |       |

| System Accuracy of ISL6327CRZ<br>(VID = 1V-1.6V), T <sub>J</sub> = 0°C to 70°C   | (Note 3)                                                                                                          | -0.5     | -     | 0.5   | %VID  |

| System Accuracy of ISL6327CRZ<br>(VID = 0.5V-1V), T <sub>J</sub> = 0°C to 70°C   | (Note 3)                                                                                                          | -0.9     | -     | 0.9   | %VID  |

| System Accuracy of ISL6327IRZ<br>(VID = 1V-1.6V), T <sub>J</sub> = -40°C to 85°C | (Note 3)                                                                                                          | -0.6     | -     | 0.6   | %VID  |

| System Accuracy of ISL6327IRZ<br>(VID = 0.5V-1V), T <sub>J</sub> = -40°C to 85°C | (Note 3)                                                                                                          | -1       | -     | 1     | %VID  |

| VID Pull Up                                                                      |                                                                                                                   | -60      | -40   | -20   | μA    |

| VID Input Low Level                                                              |                                                                                                                   | -        | -     | 0.4   | V     |

| VID Input High Level                                                             |                                                                                                                   | 0.8      | -     | -     | V     |

| VRSEL Input Low Level                                                            |                                                                                                                   | -        | -     | 0.4   | V     |

| VRSEL Input High Level                                                           |                                                                                                                   | 0.8      | -     | -     | V     |

| DAC Source Current                                                               |                                                                                                                   | -        | 4     | 7     | mA    |

# **Electrical Specifications** Operating Conditions: VCC = 5V, Unless Otherwise Specified (Continued)

| PARAMETER                                  | TEST CONDITIONS                                                        | MIN   | TYP   | MAX  | UNITS |

|--------------------------------------------|------------------------------------------------------------------------|-------|-------|------|-------|

| DAC Sink Current                           |                                                                        | -     | -     | 300  | μΑ    |

| REF Source Current                         |                                                                        | 45    | 50    | 55   | μA    |

| REF Sink Current                           |                                                                        | 45    | 50    | 55   | μA    |

| PIN-ADJUSTABLE OFFSET                      | 1                                                                      |       | 1     | •    |       |

| Voltage at OFS Pin                         | Offset resistor connected to ground                                    | 380   | 400   | 420  | mV    |

|                                            | Voltage below VCC, offset resistor connected to VCC                    | 1.55  | 1.60  | 1.65 | V     |

| OSCILLATORS                                |                                                                        |       |       |      | I     |

| Accuracy of Switching Frequency Setting    | $R_{T} = 100 k\Omega$                                                  | 225   | 250   | 275  | kHz   |

| Adjustment Range of Switching Frequency    | (Note 4)                                                               | 0.08  | -     | 1.0  | MHz   |

| Soft-Start Ramp Rate (Notes 5, 6)          | R <sub>SS</sub> = 100kΩ                                                | -     | 1.563 | -    | mV/μs |

| Adjustment Range of Soft-Start Ramp Rate   | (Note 4)                                                               | 0.625 | -     | 6.25 | mV/μs |

| PWM GENERATOR                              |                                                                        |       |       | I    | 1     |

| Sawtooth Amplitude                         |                                                                        | -     | 1.25  | -    | V     |

| ERROR AMPLIFIER                            |                                                                        |       |       |      | 1     |

| Open-Loop Gain                             | $R_L = 10k\Omega$ to ground (Note 4)                                   | -     | 96    | -    | dB    |

| Open-Loop Bandwidth                        | $C_L = 100 pF, R_L = 10 k\Omega$ to ground (Note 4)                    | -     | 80    | -    | MHz   |

| Slew Rate                                  | C <sub>L</sub> = 100pF (Note 4)                                        | -     | 25    | -    | V/µs  |

| Maximum Output Voltage                     |                                                                        | 3.8   | 4.3   | 4.9  | V     |

| Output High Voltage @ 2mA                  |                                                                        | 3.6   | -     | -    | V     |

| Output Low Voltage @ 2mA                   |                                                                        | -     | -     | 1.8  | V     |

| REMOTE-SENSE AMPLIFIER                     |                                                                        |       |       | I    | 1     |

| Bandwidth                                  | (Note 4)                                                               | -     | 20    | -    | MHz   |

| Output High Current                        | VSEN - RGND = 2.5V                                                     | -500  | -     | 500  | μA    |

| Output High Current                        | VSEN - RGND = 0.6V                                                     | -500  | -     | 500  | μA    |

| PWM OUTPUT                                 |                                                                        |       |       | I    | 1     |

| PWM Output Voltage LOW Threshold           | $Iload = \pm 500 \mu A$                                                | -     | -     | 0.5  | V     |

| PWM Output Voltage HIGH Threshold          | lload = ±500μA                                                         | 4.3   | -     | -    | V     |

| CURRENT SENSE AND OVERCURRENT              | PROTECTION                                                             |       |       | I    | 1     |

| Sensed Current Tolerance                   | ISEN1 = ISEN2 = ISEN3 = ISEN4 = ISEN5 = ISEN6 = 60µA                   | 57    | 60    | 63   | μA    |

| Overcurrent Trip Level for Average Current |                                                                        | 72    | 85    | 98   | μA    |

| Peak Current Limit for Individual Channel  |                                                                        | 100   | 120   | 140  | μA    |

| Maximum Voltage at IDROOP and IOUT<br>Pins |                                                                        | -     | 2.0   | -    | V     |

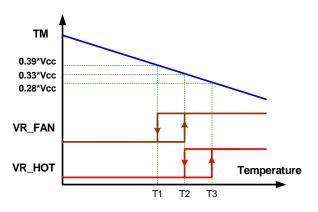

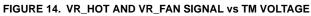

| THERMAL MONITORING                         |                                                                        | - I   |       |      | 1     |

| TM Input Voltage for VR_FAN Trip           |                                                                        | 1.55  | 1.65  | 1.75 | V     |

| TM Input Voltage for VR_FAN Reset          |                                                                        | 1.85  | 1.95  | 2.05 | V     |

| TM Input Voltage for VR_HOT Trip           |                                                                        | 1.3   | 1.4   | 1.5  | V     |

| TM Input Voltage for VR_HOT Reset          |                                                                        | 1.55  | 1.65  | 1.75 | V     |

| Leakage Current of VR_HOT                  | With external pull-up resistor connected to VCC                        | -     | -     | 30   | μA    |

| VR_HOT Low Voltage                         | With 1.25k $\Omega$ resistor pull up to Vcc, I <sub>VR HOT</sub> = 4mA | -     | -     | 0.4  | V     |

# ISL6327

#### Electrical Specifications Operating Conditions: VCC = 5V, Unless Otherwise Specified (Continued)

| PARAMETER                               | TEST CONDITIONS                                                        | MIN   | TYP   | MAX   | UNITS |

|-----------------------------------------|------------------------------------------------------------------------|-------|-------|-------|-------|

| Leakage Current of VR_FAN               | With external pull-up resistor connected to VCC                        | -     | -     | 30    | μΑ    |

| VR_FAN Low Voltage                      | With 1.25k $\Omega$ resistor pull up to Vcc, I <sub>VR_FAN</sub> = 4mA | -     | -     | 0.4   | V     |

| VR READY AND PROTECTION MONITO          | RS                                                                     | U     |       |       | r     |

| Leakage Current of VR_RDY               | With externally pull-up resistor connected to VCC                      | -     | -     | 30    | μΑ    |

| VR_RDY Low Voltage                      | I <sub>VR_RDY</sub> = 4mA                                              | -     | -     | 0.4   | V     |

| Undervoltage Threshold                  | VDIFF Falling                                                          | 48    | 50    | 52    | %VID  |

| VR_RDY Reset Voltage                    | VDIFF Rising                                                           | 58    | 60    | 62    | %VID  |

| Overvoltage Protection Threshold        | Before valid VID                                                       | 1.250 | 1.275 | 1.300 | V     |

|                                         | After valid VID, the voltage above VID                                 | 150   | 175   | 200   | mV    |

| Overvoltage Protection Reset Hysteresis |                                                                        | -     | 100   | -     | mV    |

| OVP Output Low Voltage                  | IOVP = 4mA                                                             | -     | -     | 0.4   | V     |

NOTES:

3. These parts are designed and adjusted for accuracy with all errors in the voltage loop included.

4. Spec guaranteed by design.

5. During soft-start, VDAC rises from 0 to 1.1V first and then ramp to VID voltage after receiving valid VID input.

6. Soft-start ramp rate is determined by the adjustable soft-start oscillator frequency at the speed of 6.25mV per cycle.

# Functional Pin Description

**VCC** - Supplies the power necessary to operate the chip. The controller starts to operate when the voltage on this pin exceeds the rising POR threshold and shuts down when the voltage on this pin drops below the falling POR threshold. Connect this pin directly to a +5V supply.

**GND** - Bias and reference ground for the IC. The bottom metal base of ISL6327 is the GND.

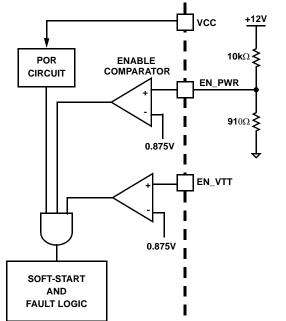

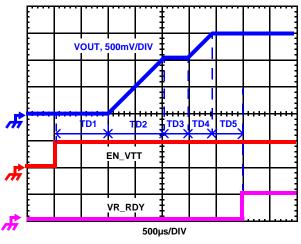

**EN\_PWR -** This pin is a threshold-sensitive enable input for the controller. Connecting the 12V supply to EN\_PWR through an appropriate resistor divider provides a means to synchronize power-up of the controller and the MOSFET driver ICs. When EN\_PWR is driven above 0.875V, the ISL6327 is active depending on status of EN\_VTT, the internal POR, and pending fault states. Driving EN\_PWR below 0.745V will clear all fault states and prime the ISL6327 to soft-start when re-enabled.

**EN\_VTT** - This pin is another threshold-sensitive enable input for the controller. It's typically connected to VTT output of VTT voltage regulator in the computer mother board. When EN\_VTT is driven above 0.875V, the ISL6327 is active depending on status of ENLL, the internal POR, and pending fault states. Driving EN\_VTT below 0.745V will clear all fault states and prime the ISL6327 to soft-start when re-enabled.

**FS** - Use this pin to set up the desired switching frequency. A resistor, placed from FS to ground will set the switching frequency. The relationship between the value of the resistor and the switching frequency will be described by an approximate equation.

**SS** - Use this pin to set up the desired start-up oscillator frequency. A resistor, placed from SS to ground will set up the soft-start ramp rate. The relationship between the value of the resistor and the soft-start ramp up time will be described by an approximate equation.

VID7, VID6, VID5, VID4, VID3, VID2, VID1 and VID0 -

These are the inputs to the internal DAC that generates the reference voltage for output regulation. Connect these pins either to open-drain outputs with or without external pull-up resistors or to active-pull-up outputs. All VID pins have 40uA internal pull-up current sources that diminish to zero as the voltage rises above the logic-high level. These inputs can be pulled up externally as high as VCC plus 0.3V.

**VRSEL -** VRSEL is the pin used to select the internal VID code. when it is connected to GND, the extended VR10 code is selected. VRSEL pin has 40µA internal pull-up current sources that diminish to zero as the voltage rises above the logic-high level. When it's floated or pulled to high, VR11 code is selected. This input can be pulled up as high as VCC plus 0.3V.

**VDIFF, VSEN, and RGND -** VSEN and RGND form the precision differential remote-sense amplifier. This amplifier

converts the differential voltage of the remote output to a single-ended voltage referenced to local ground. VDIFF is the amplifier's output and the input to the regulation and protection circuitry. Connect VSEN and RGND to the sense pins of the remote load. VDIFF is connected to FB through a resistor.

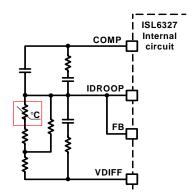

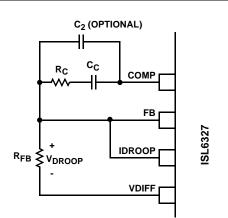

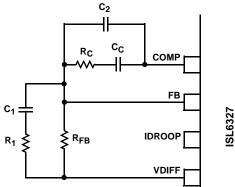

**FB and COMP -** The inverting input and the output of the error amplifier respectively. FB can be connected to VDIFF through a resistor. A properly chosen resistor between VDIFF and FB can set the load line (droop), when IDROOP pin is tied to FB pin. The droop scale factor is set by the ratio of the ISEN resistors and the inductor DCR or the dedicated current sense resistor. COMP is tied back to FB through an external R-C network to compensate the regulator.

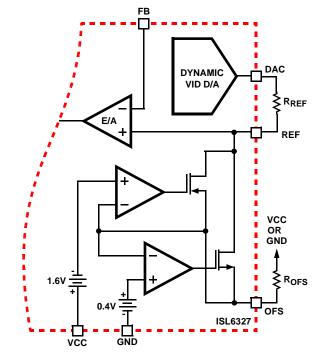

**DAC and REF** - The DAC pin is the output of the precision internal DAC reference. The REF pin is the positive input of the Error Amp. In typical applications, a  $1k\Omega$ , 1% resistor is used between DAC and REF to generate a precision offset voltage. This voltage is proportional to the offset current determined by the offset resistor from OFS to ground or VCC. A capacitor is used between REF and ground to smooth the voltage transition during Dynamic VID<sup>TM</sup> operations.

**PWM1, PWM2, PWM3, PWM4, PWM5, PWM6 -** Pulse width modulation outputs. Connect these pins to the PWM input pins of the Intersil driver IC. The number of active channels is determined by the state of PWM3, PWM4, PWM5, and PWM6.

Tie PWM3 to VCC to configure for 2-phase operation. Tie PWM4 to VCC to configure for 3-phase operation. Tie PWM5 to VCC to configure for 4-phase operation. Tie PWM6 to VCC to configure for 5-phase operation.

ISEN1+, ISEN1-; ISEN2+, ISEN2-; ISEN3+, ISEN3-; ISEN4+, ISEN4-; ISEN5+, ISEN5-; ISEN6+, ISEN6- - The ISEN+ and ISEN- pins are current sense inputs to individual differential amplifiers. The sensed current is used for channel current balancing, overcurrent protection, and droop regulation. Inactive channels should have their respective current sense inputs left open (for example, open ISEN6+ and ISEN6- for 5-phase operation).

For DCR sensing, connect each ISEN- pin to the node between the RC sense elements. Tie the ISEN+ pin to the other end of the sense capacitor through a resistor,  $R_{ISEN}$ . The voltage across the sense capacitor is proportional to the inductor current. Therefore, the sense current is proportional to the inductor current, and scaled by the DCR of the inductor and  $R_{ISEN}$ .

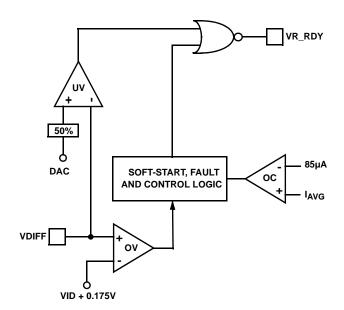

**VR\_RDY -** VR\_RDY indicates that the soft-start is completed and the output voltage is within the regulated range around VID setting. It is an open-drain logic output. When OCP or OVP occurs, VR\_RDY will be pulled to low. It will also be pulled low if the output voltage is below the undervoltage threshold. **OFS -** The OFS pin provides a means to program a DC offset current for generating a DC offset voltage at the REF input. The offset current is generated via an external resistor and precision internal voltage references. The polarity of the offset is selected by connecting the resistor to GND or VCC. For no offset, the OFS pin should be left unterminated.

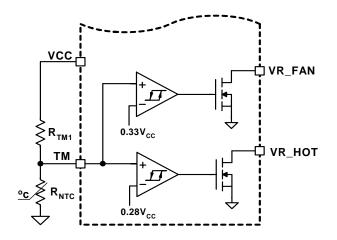

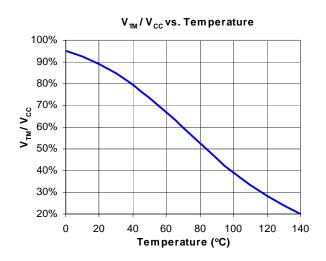

**TCOMP** - Temperature compensation scaling input. The voltage sensed on the TM pin is utilized as the temperature input to adjust ldroop and the overcurrent protection limit to effectively compensate for the temperature coefficient of the current sense element. To implement the integrated temperature compensation, a resistor divider circuit is needed with one resistor being connected from TCOMP to VCC of the controller and another resistor being connected from TCOMP to GND. Changing the ratio of the resistor values will set the gain of the integrated thermal compensation. When integrated temperature compensation function is not used, connect TCOMP to GND.

**OVP** - The Overvoltage protection output indication pin. This pin can be pulled to VCC and is latched when an overvoltage condition is detected. When the OVP indication is not used, keep this pin open.

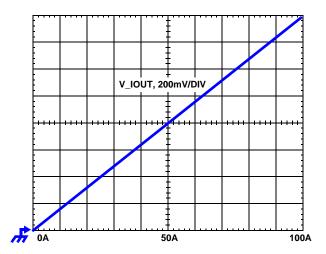

**IDROOP** - IDROOP is the output pin of the sensed average channel current which is proportional to the load current. In the application which does not require loadline, leave this pin open. In the application which requires load line, connect this pin to FB so that the sensed average current will flow through the resistor between FB and VDIFF to create a voltage drop which is proportional to the load current.

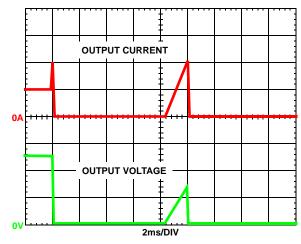

**IOUT -** IOUT has the same output as IDROOP with additional OCP adjustment function. In actual application, a resistor needs to be placed between IOUT and GND to ensure the proper operation. The voltage at IOUT pin will be proportional to the load current. If the voltage is higher than 2V, ISL6327 will go into the OCP mode, this means it will shut down first and then hiccup. The additional OCP trip level can be adjusted by changing the resistor value.

**TM** - TM is an input pin for VR temperature measurement. Connect this pin through NTC thermistor to GND and a resistor to Vcc of the controller. The voltage at this pin is reverse proportional to the VR temperature. ISL6327 monitors the VR temperature based on the voltage at the TM pin and the output signals at VR\_HOT and VR\_FAN.

**VR\_HOT -** VR\_HOT is used as an indication of high VR temperature. It is an open-drain logic output. It will be open when the measured VR temperature reaches a certain level.

**VR\_FAN -** VR\_FAN is an output pin with open-drain logic output. It will be open when the measured VR temperature reaches a certain level.

# Operation

## Multiphase Power Conversion

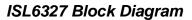

Microprocessor load current profiles have changed to the point that the advantages of multiphase power conversion are impossible to ignore. The technical challenges associated with producing a single-phase converter which is both cost-effective and thermally viable, have forced a change to the cost-saving approach of multiphase. The ISL6327 controller helps reduce the complexity of implementation by integrating vital functions and requiring minimal output components. The block diagrams on pages 3, 4, and 5 provide top level views of multiphase power conversion using the ISL6327 controller.

## Interleaving

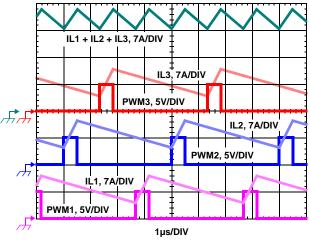

The switching of each channel in a multiphase converter is timed to be symmetrically out of phase with each of the other channels. In a 3-phase converter, each channel switches 1/3 cycle after the previous channel and 1/3 cycle before the following channel. As a result, the three-phase converter has a combined ripple frequency three times greater than the ripple frequency of any one phase. In addition, the peak-topeak amplitude of the combined inductor current is reduced in proportion to the number of phases (Equations 1 and 2). The increased ripple frequency and the lower ripple amplitude mean that the designer can use less per-channel inductance and lower total output capacitance for any performance specification.

Figure 1 illustrates the multiplicative effect on output ripple frequency. The three channel currents (IL1, IL2, and IL3) combine to form the AC ripple current and the DC load current. The ripple component has three times the ripple frequency of each individual channel current. Each PWM pulse is triggered 1/3 of a cycle after the start of the PWM pulse of the previous phase. The DC components of the inductor currents combine to feed the load.

FIGURE 1. PWM AND INDUCTOR-CURRENT WAVEFORMS FOR 3-PHASE CONVERTER

To understand the reduction of the ripple current amplitude in the multiphase circuit, examine the equation representing an individual channel's peak-to-peak inductor current.

$$I_{PP} = \frac{(V_{IN} - V_{OUT})V_{OUT}}{Lf_S V_{IN}}$$

(EQ. 1)

In Equation 1,  $V_{IN}$  and  $V_{OUT}$  are the input and the output voltages respectively, L is the single-channel inductor value, and  $f_S$  is the switching frequency.

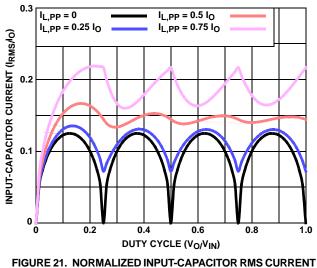

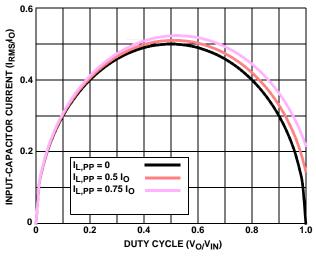

CAPACITOR RMS CURRENT FOR 3-PHASE CONVERTER

The output capacitors conduct the ripple component of the inductor current. In the case of multiphase converters, the capacitor current is the sum of the ripple currents from each of the individual channels. Compare Equation 1 to the expression for the peak-to-peak current after the summation of N symmetrically phase-shifted inductor currents in Equation 2. Peak-to-peak ripple current decreases by an amount proportional to the number of channels. Output-voltage ripple is a function of capacitance, capacitor equivalent series resistance (ESR), and inductor ripple current. Reducing the inductor ripple current allows the designer to use fewer or less costly output capacitors.

$$I_{C, PP} = \frac{(V_{IN} - N V_{OUT})V_{OUT}}{Lf_S V_{IN}}$$

(EQ. 2)

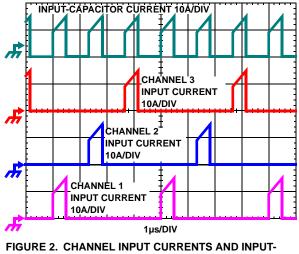

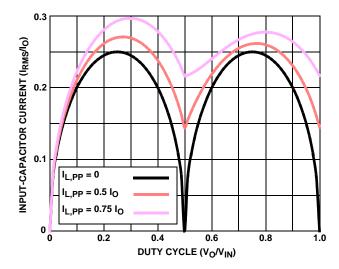

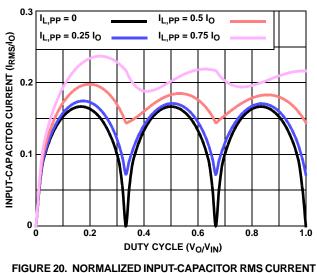

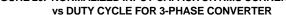

Another benefit of interleaving is to reduce the input ripple current. The input capacitance is determined in part by the maximum input ripple current. Multiphase topologies can improve the overall system cost and size by lowering the input ripple current and allowing the designer to reduce the cost of input capacitance. The example in Figure 2 illustrates the input currents from a three-phase converter combining to reduce the total input ripple current.

The converter depicted in Figure 2 delivers 36A to a 1.5V load from a 12V input. The RMS input capacitor current is 5.9A. Compare this to a single-phase converter also stepping down 12V to 1.5V at 36A. The single-phase converter has 11.9A

RMS input capacitor current. The single-phase converter must use an input capacitor bank with twice the RMS current capacity as the equivalent three-phase converter.

Figures 19, 20 and 21 in the section titled *Input Capacitor Selection* can be used to determine the input-capacitor RMS current based on the load current, the duty cycle, and the number of channels. They are provided as aids in determining the optimal input capacitor solution. Figure 22 shows the single phase input-capacitor RMS current for comparison.

## **PWM Modulation Scheme**

The ISL6327 adopts Intersil's proprietary Active Pulse Positioning (APP) modulation scheme to improve the transient performance. APP control is a unique dual-edge PWM modulation scheme with both PWM leading and trailing edges being independently moved to provide the best response to the transient loads. The PWM frequency, however, is constant and set by the external resistor between the FS pin and GND.

To further improve the transient response, the ISL6327 also implements Intersil's proprietary Adaptive Phase Alignment (APA) technique. APA, with sufficiently large load step currents, can turn on all phases together.

With both APP and APA control, ISL6327 can achieve excellent transient performance and reduce the demand on the output capacitors.

Under the steady state conditions the operation of the ISL6327 PWM modulator appears to be that of a conventional trailing edge modulator. Conventional analysis and design methods can therefore be used for steady state and small signal operation.

## **PWM Operation**

The timing of each converter is set by the number of active channels. The default channel setting for the ISL6327 is six. The switching cycle is defined as the time between PWM pulse termination signals of each channel. The cycle time of the pulse termination signal is the inverse of the switching frequency set by the resistor between the FS pin and ground. The PWM signals command the MOSFET drivers to turn on/off the channel MOSFETs.

In the default 6-phase operation, the PWM2 pulse happens 1/6 of a cycle after PWM1, the PWM3 pulse happens 1/6 of a cycle after PWM2, the PWM4 pulse happens 1/6 of a cycle after PWM3, the PWM5 pulse happens 1/6 of a cycle after PWM4, and the PWM6 pulse happens 1/6 of a cycle after PWM5.

The ISL6327 works in 2, 3, 4, 5, or 6 phase configuration. Connecting the PWM6 to VCC selects 5-phase operation and the pulse times are spaced in 1/5 cycle increments. Connecting the PWM5 to VCC selects 4-phase operation and the pulse times are spaced in 1/4 cycle increments. Connecting the PWM4 to VCC selects 3-phase operation and the pulse times are spaced in 1/3 cycle increments. Connecting the PWM3 to VCC selects 2-phase operation and the pulse times are spaced in 1/2 cycle increments.

## Switching Frequency

The switching frequency is determined by the selection of the frequency-setting resistor,  $R_T$ , which is connected from FS pin to GND (see the figures labelled Typical Applications on pages 4 and 5). Equation 3 is provided to assist in selecting the correct resistor value.

$$R_{T} = \frac{2.5 \times 10^{10}}{F_{SW}} - 600$$

(EQ. 3)

where  $\mathsf{F}_{SW}$  is the switching frequency of each phase.

## **Current Sensing**

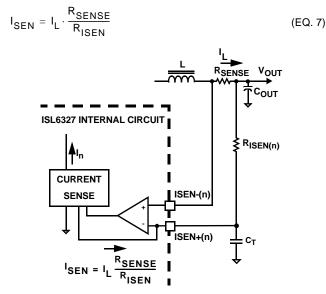

ISL6327 senses the current continuously for fast response. ISL6327 supports inductor DCR sensing, or resistive sensing techniques. The associated channel current sense amplifier uses the ISEN inputs to reproduce a signal proportional to the inductor current, I<sub>L</sub>. The sensed current, I<sub>SEN</sub>, is used for the current balance, the load-line regulation, and the overcurrent protection.

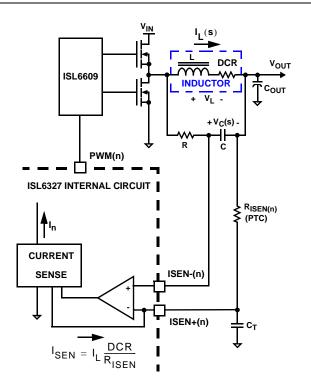

The internal circuitry, shown in Figures 3 and 4, represents one channel of an N-channel converter. This circuitry is repeated for each channel in the converter, but may not be active depending on the status of the PWM3, PWM4, PWM5, and PWM6 pins, as described in the *PWM Operation* section.

## INDUCTOR DCR SENSING

An inductor's winding is characteristic of a distributed resistance as measured by the DCR (Direct Current Resistance) parameter. Consider the inductor DCR as a separate lumped quantity, as shown in Figure 3. The channel current  $I_L$ , flowing through the inductor, will also pass through the DCR. Equation 4 shows the s-domain equivalent voltage across the inductor  $V_L$ .

$$V_{L} = I_{L} \cdot (s \cdot L + DCR)$$

(EQ. 4)

A simple R-C network across the inductor extracts the DCR voltage, as shown in Figure 3.

The voltage on the capacitor  $V_C$ , can be shown to be proportional to the channel current  $I_L$ , see Equation 5.

$$V_{C} = \frac{\left(s \cdot \frac{L}{DCR} + 1\right) \cdot (DCR \cdot I_{L})}{(s \cdot RC + 1)}$$

(EQ. 5)

FIGURE 3. DCR SENSING CONFIGURATION

If the R-C network components are selected such that the RC time constant (= R\*C) matches the inductor time constant (= L/DCR), the voltage across the capacitor V<sub>C</sub> is equal to the voltage drop across the DCR, i.e., proportional to the channel current.

With the internal low-offset current amplifier, the capacitor voltage V<sub>C</sub> is replicated across the sense resistor R<sub>ISEN</sub>. Therefore the current out of ISEN+ pin, I<sub>SEN</sub>, is proportional to the inductor current.

Because of the internal filter at ISEN- pin, one capacitor  $C_T$  is needed to match the time delay between the ISEN- and ISEN+ signals. Select the proper  $C_T$  to keep the time constant of  $R_{ISEN}$  and  $C_T$  ( $R_{ISEN} \times C_T$ ) close to 27ns.

Equation 6 shows that the ratio of the channel current to the sensed current  $I_{\text{SEN}}$  is driven by the value of the sense resistor and the DCR of the inductor.

$$I_{SEN} = I_{L} \cdot \frac{DCR}{R_{ISEN}}$$

(EQ. 6)

## **RESISTIVE SENSING**

For accurate current sense, a dedicated current-sense resistor  $R_{SENSE}$  in series with each output inductor can serve as the current sense element (see Figure 4). This technique is more accurate, but reduces overall converter efficiency due to the additional power loss on the current sense element  $R_{SENSE}$ .

The same capacitor C<sub>T</sub> is needed to match the time delay between ISEN- and ISEN+ signals. Select the proper C<sub>T</sub> to keep the time constant of R<sub>ISEN</sub> and C<sub>T</sub> (R<sub>ISEN</sub> x C<sub>T</sub>) close to 27ns.

Equation 7 shows the ratio of the channel current to the sensed current  $I_{\mbox{\scriptsize SEN}}.$

FIGURE 4. SENSE RESISTOR IN SERIES WITH INDUCTORS

The inductor DCR value will increase as the temperature increases. Therefore the sensed current will increase as the temperature of the current sense element increases. In order to compensate the temperature effect on the sensed current signal, a Positive Temperature Coefficient (PTC) resistor can be selected for the sense resistor R<sub>ISEN</sub>, or the integrated temperature compensation function of ISL6327 should be utilized. The integrated temperature compensation function is described in the *Temperature Compensation* section.

# Channel-Current Balance

The sensed current  $I_n$  from each active channel are summed together and divided by the number of active channels. The resulting average current  $I_{AVG}$  provides a measure of the total load current. Channel current balance is achieved by comparing the sensed current of each channel to the average current to make an appropriate adjustment to the PWM duty cycle of each channel with Intersil's patented current-balance method.

Channel current balance is essential in achieving the thermal advantage of multiphase operation. With good current balance, the power loss is equally dissipated over multiple devices and a greater area.

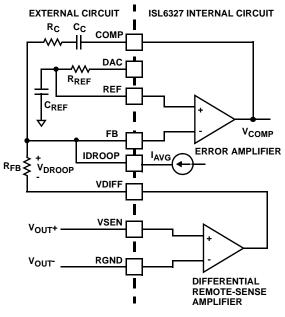

## Voltage Regulation

The compensation network shown in Figure 5 assures that the steady-state error in the output voltage is limited only to the error in the reference voltage (output of the DAC) and offset errors in the OFS current source, remote-sense and error amplifiers. Intersil specifies the guaranteed tolerance of the ISL6327 to include the combined tolerances of each of these elements.

The output of the error amplifier,  $V_{COMP}$ , is compared to the sawtooth waveforms to generate the PWM signals. The PWM signals control the timing of the Intersil MOSFET drivers and regulate the converter output to the specified reference voltage. The internal and external circuitries which control the voltage regulation are illustrated in Figure 5.

The ISL6327 incorporates an internal differential remotesense amplifier in the feedback path. The amplifier removes the voltage error encountered when measuring the output voltage relative to the local controller ground reference point resulting in a more accurate means of sensing output voltage. Connect the microprocessor sense pins to the noninverting input, VSEN, and inverting input, RGND, of the remote-sense amplifier. The remote-sense output, V<sub>DIFF</sub>, is connected to the inverting input of the error amplifier through an external resistor.

A digital-to-analog converter (DAC) generates a reference voltage based on the state of logic signals at pins VID7 through VID0. The DAC decodes the 8-bit logic signal (VID) into one of the discrete voltages shown in Table 1. Each VID input offers a  $45\mu$ A pull-up to an internal 2.5V source for use with open-drain outputs. The pull-up current diminishes to zero above the logic threshold to protect voltage-sensitive output devices. External pull-up resistors can augment the pull-up current sources in case the leakage into the driving device is greater than  $45\mu$ A.

FIGURE 5. OUTPUT VOLTAGE AND LOAD-LINE REGULATION WITH OFFSET ADJUSTMENT

# Load-Line Regulation

Some microprocessor manufacturers require a preciselycontrolled output resistance. This dependence of the output voltage on the load current is often termed "droop" or "load line" regulation. By adding a well controlled output impedance, the output voltage can effectively be level shifted in a direction which works to achieve the load-line regulation required by these manufacturers.

In other cases, the designer may determine that a more cost-effective solution can be achieved by adding droop. Droop can help to reduce the output-voltage spike that results from the fast changes of the load-current demand.

The magnitude of the spike is dictated by the ESR and ESL of the output capacitors selected. By positioning the no-load voltage level near the upper specification limit, a larger negative spike can be sustained without crossing the lower limit. By adding a well controlled output impedance, the output voltage under load can effectively be level shifted down so that a larger positive spike can be sustained without crossing the upper specification limit.

| TABLE 1. VR 10 VID TABLE (WITH 6.25MV EXTENSION) |               |               |              |              |                |                |                |  |  |

|--------------------------------------------------|---------------|---------------|--------------|--------------|----------------|----------------|----------------|--|--|

| VID4<br>400mV                                    | VID3<br>200mV | VID2<br>100mV | VID1<br>50mV | VID0<br>25mV | VID5<br>12.5mV | VID6<br>6.25mV | VOLTAGE<br>(V) |  |  |

| 0                                                | 1             | 0             | 1            | 0            | 1              | 1              | 1.6            |  |  |

| 0                                                | 1             | 0             | 1            | 0            | 1              | 0              | 1.59375        |  |  |

| 0                                                | 1             | 0             | 1            | 1            | 0              | 1              | 1.5875         |  |  |

| 0                                                | 1             | 0             | 1            | 1            | 0              | 0              | 1.58125        |  |  |

| 0                                                | 1             | 0             | 1            | 1            | 1              | 1              | 1.575          |  |  |

| 0                                                | 1             | 0             | 1            | 1            | 1              | 0              | 1.56875        |  |  |

| 0                                                | 1             | 1             | 0            | 0            | 0              | 1              | 1.5625         |  |  |

| 0                                                | 1             | 1             | 0            | 0            | 0              | 0              | 1.55625        |  |  |

| 0                                                | 1             | 1             | 0            | 0            | 1              | 1              | 1.55           |  |  |

| 0                                                | 1             | 1             | 0            | 0            | 1              | 0              | 1.54375        |  |  |

| 0                                                | 1             | 1             | 0            | 1            | 0              | 1              | 1.5375         |  |  |

| 0                                                | 1             | 1             | 0            | 1            | 0              | 0              | 1.53125        |  |  |

| 0                                                | 1             | 1             | 0            | 1            | 1              | 1              | 1.525          |  |  |

| 0                                                | 1             | 1             | 0            | 1            | 1              | 0              | 1.51875        |  |  |

| 0                                                | 1             | 1             | 1            | 0            | 0              | 1              | 1.5125         |  |  |

| 0                                                | 1             | 1             | 1            | 0            | 0              | 0              | 1.50625        |  |  |

| 0                                                | 1             | 1             | 1            | 0            | 1              | 1              | 1.5            |  |  |

| 0                                                | 1             | 1             | 1            | 0            | 1              | 0              | 1.49375        |  |  |

| 0                                                | 1             | 1             | 1            | 1            | 0              | 1              | 1.4875         |  |  |

| 0                                                | 1             | 1             | 1            | 1            | 0              | 0              | 1.48125        |  |  |

| 0                                                | 1             | 1             | 1            | 1            | 1              | 1              | 1.475          |  |  |

| 0                                                | 1             | 1             | 1            | 1            | 1              | 0              | 1.46875        |  |  |

| 1                                                | 0             | 0             | 0            | 0            | 0              | 1              | 1.4625         |  |  |

TABLE 1. VR10 VID TABLE (WITH 6.25mV EXTENSION)

#### TABLE 1. VR10 VID TABLE (WITH 6.25mV EXTENSION) (Continued)

| TABLE 1. VR10 VID TABLE (WITH 6.25mV EXTENSION) (Continued) |               |               |              |              |                |                |                |  |  |

|-------------------------------------------------------------|---------------|---------------|--------------|--------------|----------------|----------------|----------------|--|--|

| VID4<br>400mV                                               | VID3<br>200mV | VID2<br>100mV | VID1<br>50mV | VID0<br>25mV | VID5<br>12.5mV | VID6<br>6.25mV | VOLTAGE<br>(V) |  |  |

| 1                                                           | 0             | 0             | 0            | 0            | 0              | 0              | 1.45625        |  |  |

| 1                                                           | 0             | 0             | 0            | 0            | 1              | 1              | 1.45           |  |  |

| 1                                                           | 0             | 0             | 0            | 0            | 1              | 0              | 1.44375        |  |  |

| 1                                                           | 0             | 0             | 0            | 1            | 0              | 1              | 1.4375         |  |  |

| 1                                                           | 0             | 0             | 0            | 1            | 0              | 0              | 1.43125        |  |  |

| 1                                                           | 0             | 0             | 0            | 1            | 1              | 1              | 1.425          |  |  |

| 1                                                           | 0             | 0             | 0            | 1            | 1              | 0              | 1.41875        |  |  |

| 1                                                           | 0             | 0             | 1            | 0            | 0              | 1              | 1.4125         |  |  |

| 1                                                           | 0             | 0             | 1            | 0            | 0              | 0              | 1.40625        |  |  |

| 1                                                           | 0             | 0             | 1            | 0            | 1              | 1              | 1.4            |  |  |

| 1                                                           | 0             | 0             | 1            | 0            | 1              | 0              | 1.39375        |  |  |

| 1                                                           | 0             | 0             | 1            | 1            | 0              | 1              | 1.3875         |  |  |

| 1                                                           | 0             | 0             | 1            | 1            | 0              | 0              | 1.38125        |  |  |

| 1                                                           | 0             | 0             | 1            | 1            | 1              | 1              | 1.375          |  |  |

| 1                                                           | 0             | 0             | 1            | 1            | 1              | 0              | 1.36875        |  |  |

| 1                                                           | 0             | 1             | 0            | 0            | 0              | 1              | 1.3625         |  |  |

| 1                                                           | 0             | 1             | 0            | 0            | 0              | 0              | 1.35625        |  |  |

| 1                                                           | 0             | 1             | 0            | 0            | 1              | 1              | 1.35           |  |  |

| 1                                                           | 0             | 1             | 0            | 0            | 1              | 0              | 1.34375        |  |  |

| 1                                                           | 0             | 1             | 0            | 1            | 0              | 1              | 1.3375         |  |  |

| 1                                                           | 0             | 1             | 0            | 1            | 0              | 0              | 1.33125        |  |  |

| 1                                                           | 0             | 1             | 0            | 1            | 1              | 1              | 1.325          |  |  |

| 1                                                           | 0             | 1             | 0            | 1            | 1              | 0              | 1.31875        |  |  |

| 1                                                           | 0             | 1             | 1            | 0            | 0              | 1              | 1.3125         |  |  |

| 1                                                           | 0             | 1             | 1            | 0            | 0              | 0              | 1.30625        |  |  |

| 1                                                           | 0             | 1             | 1            | 0            | 1              | 1              | 1.3            |  |  |

| 1                                                           | 0             | 1             | 1            | 0            | 1              | 0              | 1.29375        |  |  |

| 1                                                           | 0             | 1             | 1            | 1            | 0              | 1              | 1.2875         |  |  |

| 1                                                           | 0             | 1             | 1            | 1            | 0              | 0              | 1.28125        |  |  |

| 1                                                           | 0             | 1             | 1            | 1            | 1              | 1              | 1.275          |  |  |

| 1                                                           | 0             | 1             | 1            | 1            | 1              | 0              | 1.26875        |  |  |

| 1                                                           | 1             | 0             | 0            | 0            | 0              | 1              | 1.2625         |  |  |

| 1                                                           | 1             | 0             | 0            | 0            | 0              | 0              | 1.25625        |  |  |

| 1                                                           | 1             | 0             | 0            | 0            | 1              | 1              | 1.25           |  |  |

| 1                                                           | 1             | 0             | 0            | 0            | 1              | 0              | 1.24375        |  |  |

| 1                                                           | 1             | 0             | 0            | 1            | 0              | 1              | 1.2375         |  |  |

| 1                                                           | 1             | 0             | 0            | 1            | 0              | 0              | 1.23125        |  |  |

| 1                                                           | 1             | 0             | 0            | 1            | 1              | 1              | 1.225          |  |  |

| 1                                                           | 1             | 0             | 0            | 1            | 1              | 0              | 1.21875        |  |  |

14

#### TABLE 1. VR10 VID TABLE (WITH 6.25mV EXTENSION) (Continued)

| VID4  | VID3  | VID 170 | VID1 | VID0 | VID5   | VID6   | VOLTAGE |

|-------|-------|---------|------|------|--------|--------|---------|

| 400mV | 200mV | 100mV   | 50mV | 25mV | 12.5mV | 6.25mV | (V)     |

| 1     | 1     | 0       | 1    | 0    | 0      | 1      | 1.2125  |

| 1     | 1     | 0       | 1    | 0    | 0      | 0      | 1.20625 |

| 1     | 1     | 0       | 1    | 0    | 1      | 1      | 1.2     |

| 1     | 1     | 0       | 1    | 0    | 1      | 0      | 1.19375 |

| 1     | 1     | 0       | 1    | 1    | 0      | 1      | 1.1875  |

| 1     | 1     | 0       | 1    | 1    | 0      | 0      | 1.18125 |

| 1     | 1     | 0       | 1    | 1    | 1      | 1      | 1.175   |

| 1     | 1     | 0       | 1    | 1    | 1      | 0      | 1.16875 |

| 1     | 1     | 1       | 0    | 0    | 0      | 1      | 1.1625  |

| 1     | 1     | 1       | 0    | 0    | 0      | 0      | 1.15625 |

| 1     | 1     | 1       | 0    | 0    | 1      | 1      | 1.15    |

| 1     | 1     | 1       | 0    | 0    | 1      | 0      | 1.14375 |

| 1     | 1     | 1       | 0    | 1    | 0      | 1      | 1.1375  |

| 1     | 1     | 1       | 0    | 1    | 0      | 0      | 1.13125 |

| 1     | 1     | 1       | 0    | 1    | 1      | 1      | 1.125   |

| 1     | 1     | 1       | 0    | 1    | 1      | 0      | 1.11875 |

| 1     | 1     | 1       | 1    | 0    | 0      | 1      | 1.1125  |

| 1     | 1     | 1       | 1    | 0    | 0      | 0      | 1.10625 |

| 1     | 1     | 1       | 1    | 0    | 1      | 1      | 1.1     |

| 1     | 1     | 1       | 1    | 0    | 1      | 0      | 1.09375 |

| 1     | 1     | 1       | 1    | 1    | 0      | 1      | OFF     |

| 1     | 1     | 1       | 1    | 1    | 0      | 0      | OFF     |

| 1     | 1     | 1       | 1    | 1    | 1      | 1      | OFF     |

| 1     | 1     | 1       | 1    | 1    | 1      | 0      | OFF     |

| 0     | 0     | 0       | 0    | 0    | 0      | 1      | 1.0875  |

| 0     | 0     | 0       | 0    | 0    | 0      | 0      | 1.08125 |

| 0     | 0     | 0       | 0    | 0    | 1      | 1      | 1.075   |

| 0     | 0     | 0       | 0    | 0    | 1      | 0      | 1.06875 |

| 0     | 0     | 0       | 0    | 1    | 0      | 1      | 1.0625  |

| 0     | 0     | 0       | 0    | 1    | 0      | 0      | 1.05625 |

| 0     | 0     | 0       | 0    | 1    | 1      | 1      | 1.05    |

| 0     | 0     | 0       | 0    | 1    | 1      | 0      | 1.04375 |

| 0     | 0     | 0       | 1    | 0    | 0      | 1      | 1.0375  |

| 0     | 0     | 0       | 1    | 0    | 0      | 0      | 1.03125 |

| 0     | 0     | 0       | 1    | 0    | 1      | 1      | 1.025   |

| 0     | 0     | 0       | 1    | 0    | 1      | 0      | 1.01875 |

| 0     | 0     | 0       | 1    | 1    | 0      | 1      | 1.0125  |

| 0     | 0     | 0       | 1    | 1    | 0      | 0      | 1.00625 |

| 0     | 0     | 0       | 1    | 1    | 1      | 1      | 1       |

#### TABLE 1. VR10 VID TABLE (WITH 6.25mV EXTENSION) (Continued)

| VID4  | VID3  | VID2  | VID1 | VID0 | VID5   | VID6   | VOLTAGE |

|-------|-------|-------|------|------|--------|--------|---------|

| 400mV | 200mV | 100mV | 50mV | 25mV | 12.5mV | 6.25mV | (V)     |

| 0     | 0     | 0     | 1    | 1    | 1      | 0      | 0.99375 |

| 0     | 0     | 1     | 0    | 0    | 0      | 1      | 0.9875  |

| 0     | 0     | 1     | 0    | 0    | 0      | 0      | 0.98125 |

| 0     | 0     | 1     | 0    | 0    | 1      | 1      | 0.975   |

| 0     | 0     | 1     | 0    | 0    | 1      | 0      | 0.96875 |

| 0     | 0     | 1     | 0    | 1    | 0      | 1      | 0.9625  |

| 0     | 0     | 1     | 0    | 1    | 0      | 0      | 0.95625 |

| 0     | 0     | 1     | 0    | 1    | 1      | 1      | 0.95    |

| 0     | 0     | 1     | 0    | 1    | 1      | 0      | 0.94375 |

| 0     | 0     | 1     | 1    | 0    | 0      | 1      | 0.9375  |

| 0     | 0     | 1     | 1    | 0    | 0      | 0      | 0.93125 |

| 0     | 0     | 1     | 1    | 0    | 1      | 1      | 0.925   |

| 0     | 0     | 1     | 1    | 0    | 1      | 0      | 0.91875 |

| 0     | 0     | 1     | 1    | 1    | 0      | 1      | 0.9125  |

| 0     | 0     | 1     | 1    | 1    | 0      | 0      | 0.90625 |

| 0     | 0     | 1     | 1    | 1    | 1      | 1      | 0.9     |

| 0     | 0     | 1     | 1    | 1    | 1      | 0      | 0.89375 |

| 0     | 1     | 0     | 0    | 0    | 0      | 1      | 0.8875  |

| 0     | 1     | 0     | 0    | 0    | 0      | 0      | 0.88125 |

| 0     | 1     | 0     | 0    | 0    | 1      | 1      | 0.875   |

| 0     | 1     | 0     | 0    | 0    | 1      | 0      | 0.86875 |

| 0     | 1     | 0     | 0    | 1    | 0      | 1      | 0.8625  |

| 0     | 1     | 0     | 0    | 1    | 0      | 0      | 0.85625 |

| 0     | 1     | 0     | 0    | 1    | 1      | 1      | 0.85    |

| 0     | 1     | 0     | 0    | 1    | 1      | 0      | 0.84375 |

| 0     | 1     | 0     | 1    | 0    | 0      | 1      | 0.8375  |

| 0     | 1     | 0     | 1    | 0    | 0      | 0      | 0.83125 |

| -     |       |       |      |      |        |        |         |

#### TABLE 2. VR11 VID 8 BIT

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOLTAGE |

|------|------|------|------|------|------|------|------|---------|

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | OFF     |

| 0    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | OFF     |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1.60000 |

| 0    | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1.59375 |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1.58750 |

| 0    | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1.58125 |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1.57500 |

| 0    | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1.56875 |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1.56250 |

| 0    | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1.55625 |

TABLE 2. VR11 VID 8 BIT (Continued)

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOLTAGE |

|------|------|------|------|------|------|------|------|---------|

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1.55000 |

| 0    | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1.54375 |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1.53750 |

| 0    | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1.53125 |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1.52500 |

| 0    | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1.51875 |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1.51250 |

| 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1.50625 |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1.50000 |

| 0    | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1.49375 |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1.48750 |

| 0    | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1.48125 |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1.47500 |

| 0    | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1.46875 |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1.46250 |

| 0    | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1.45625 |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1.45000 |

| 0    | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1.44375 |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1.43750 |

| 0    | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1.43125 |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1.42500 |

| 0    | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1.41875 |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1.41250 |

| 0    | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1.40625 |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1.40000 |

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1.39375 |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1.38750 |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1.38125 |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1.37500 |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1.36875 |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1.36250 |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1.35625 |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1.35000 |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1.34375 |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1.33750 |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1.33125 |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1.32500 |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1.31875 |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1.31250 |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1.30625 |

| TABLE 2. VR11 VID 8 BIT (Continued) |      |      |      |      |      |      |      |         |

|-------------------------------------|------|------|------|------|------|------|------|---------|

| VID7                                | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOLTAGE |

| 0                                   | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1.30000 |

| 0                                   | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1.29375 |

| 0                                   | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1.28750 |

| 0                                   | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1.28125 |

| 0                                   | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1.27500 |

| 0                                   | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1.26875 |

| 0                                   | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1.26250 |

| 0                                   | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1.25625 |

| 0                                   | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1.25000 |

| 0                                   | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1.24375 |

| 0                                   | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1.23750 |

| 0                                   | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1.23125 |

| 0                                   | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1.22500 |

| 0                                   | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1.21875 |

| 0                                   | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1.21250 |

| 0                                   | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 1.20625 |

| 0                                   | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 1.20000 |

| 0                                   | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 1.19375 |

| 0                                   | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 1.18750 |

| 0                                   | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 1.18125 |

| 0                                   | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 1.17500 |

| 0                                   | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 1.16875 |

| 0                                   | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 1.16250 |

| 0                                   | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 1.15625 |

| 0                                   | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 1.15000 |

| 0                                   | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 1.14375 |

| 0                                   | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 1.13750 |

| 0                                   | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 1.13125 |

| 0                                   | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 1.12500 |

| 0                                   | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 1.11875 |

| 0                                   | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 1.11250 |

| 0                                   | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 1.10625 |

| 0                                   | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 1.10000 |

| 0                                   | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 1.09375 |

| 0                                   | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 1.08750 |

| 0                                   | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 1.08125 |

| 0                                   | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 1.07500 |

| 0                                   | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 1.06875 |

| 0                                   | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 1.06250 |

|                                     | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 1.05625 |

TABLE 2. VR11 VID 8 BIT (Continued)

|      |      |      |      |      | -    |      |      |         |

|------|------|------|------|------|------|------|------|---------|

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOLTAGE |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 1.05000 |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 1.04375 |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 1.03750 |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 1.03125 |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 1.02500 |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 1.01875 |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 1.01250 |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 1.00625 |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 1.00000 |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 0.99375 |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 0.98750 |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 0.98125 |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 0.97500 |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 0.96875 |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 0.96250 |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 0.95625 |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 0.95000 |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 0.94375 |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 0.93750 |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 0.93125 |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 0.92500 |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0.91875 |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 0.91250 |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 0.90625 |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 0.90000 |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 0.89375 |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 0.88750 |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 0.88125 |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 0.87500 |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 0.86875 |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 0.86250 |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 0.85625 |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 0.85000 |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 0.84375 |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 0.83750 |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 0.83125 |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 0.82500 |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 0.81875 |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0.81250 |

| 1    | 0    | 0    | 0    | 0    | 0    | 0    | 1    | 0.80625 |

|      | -    | -    | -    | -    | -    | -    |      |         |

| TABLE 2. VR11 VID 8 BIT (Continued) |      |      |      |      |      |      |      |         |

|-------------------------------------|------|------|------|------|------|------|------|---------|

| VID7                                | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOLTAGE |

| 1                                   | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0.80000 |

| 1                                   | 0    | 0    | 0    | 0    | 0    | 1    | 1    | 0.79375 |

| 1                                   | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0.78750 |

| 1                                   | 0    | 0    | 0    | 0    | 1    | 0    | 1    | 0.78125 |

| 1                                   | 0    | 0    | 0    | 0    | 1    | 1    | 0    | 0.77500 |

| 1                                   | 0    | 0    | 0    | 0    | 1    | 1    | 1    | 0.76875 |

| 1                                   | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0.76250 |

| 1                                   | 0    | 0    | 0    | 1    | 0    | 0    | 1    | 0.75625 |

| 1                                   | 0    | 0    | 0    | 1    | 0    | 1    | 0    | 0.75000 |

| 1                                   | 0    | 0    | 0    | 1    | 0    | 1    | 1    | 0.74375 |

| 1                                   | 0    | 0    | 0    | 1    | 1    | 0    | 0    | 0.73750 |

| 1                                   | 0    | 0    | 0    | 1    | 1    | 0    | 1    | 0.73125 |

| 1                                   | 0    | 0    | 0    | 1    | 1    | 1    | 0    | 0.72500 |

| 1                                   | 0    | 0    | 0    | 1    | 1    | 1    | 1    | 0.71875 |

| 1                                   | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0.71250 |

| 1                                   | 0    | 0    | 1    | 0    | 0    | 0    | 1    | 0.70625 |

| 1                                   | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0.70000 |

| 1                                   | 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0.69375 |

| 1                                   | 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0.68750 |

| 1                                   | 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0.68125 |

| 1                                   | 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0.67500 |

| 1                                   | 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0.66875 |

| 1                                   | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0.66250 |

| 1                                   | 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0.65625 |

| 1                                   | 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0.65000 |

| 1                                   | 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0.64375 |

| 1                                   | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0.63750 |

| 1                                   | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0.63125 |

| 1                                   | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0.62500 |

| 1                                   | 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0.61875 |

| 1                                   | 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0.61250 |

| 1                                   | 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0.60625 |

| 1                                   | 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0.60000 |

| 1                                   | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0.59375 |

| 1                                   | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0.58750 |

| 1                                   | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0.58125 |

| 1                                   | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0.57500 |

| 1                                   | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0.56875 |

| 1                                   | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0.56250 |

| 1                                   | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0.55625 |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | VOLTAGE |

|------|------|------|------|------|------|------|------|---------|