TOSHIBA TC9328AF

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T C 9 3 2 8 A F

# PORTABLE AUDIO DTS CONTROLLER (DTS-21)

The TC9328AF is a single-chip DTS microcontroller for portable audio incorporating 230 MHz prescaler, PLL, and LCD driver. In addition to a 20-bit IF counter, 6-bit A/D converter, serial interface, and buzzer function, the device supports an interrupt function, 8-bit timer/ counter, and 8-bit pulse counter. The LCD driver features built-in 1/4 duty, 1/2 bias and a 3 V voltage doubler boosting circuit, implementing stable LCD.

The power supply voltage ranges from 0.9 to 1.8 V. Because of its low-current consumption (CPU : 80  $\mu$ A (max)), the device is suitable for use in digital tuning systems in portable equipment such as headphone stereos.

Weight: 0.45 g (Typ.)

#### **FEATURES**

CMOS DTS microcontroller LSI with built-in 230 MHz prescaler, PLL, and LCD driver

Operating voltage  $: V_{DD} = 0.9 \text{ to } 1.8 \text{ V (typ.} : 1.5 \text{ V)}$

Current dissipation : When CPU in operation :  $I_{DD} = 40 \,\mu\text{A}$  (typ.)

When PLL in operation :  $I_{DD} = 6 \text{ mA (typ.)}$  (VHF mode)

Operating temperature range : Ta = -10 to  $60^{\circ}C$ Program memory (ROM) : 16-bit × 8192 steps Data memory (RAM) : 4-bit  $\times$  512 words

Instruction execution time :  $40 \mu s$ Crystal oscillator frequency : 75 kHz Stack level

General-purpose IF counter : 20-bit (CMOS input supported)

A/D converter : 6-bit  $\times$  4 channel

LCD driver : 1/4 duty, 1/2 bias 88 segments (max.) I/O port : CMOS I/O ports

N-channel open drain I/O ports: 24 (max.)

Output-only port Input-only ports : 5 (max.)

Timer/counter : 8-bit (as timer clock : INTR1/INTR2, instruction cycle : 1 kHz selectable)

Pulse counter : 8-bit up/down counter (input via INTR2 pin)

Buzzer : Built-in four mode : 0.625 to 3 kHz (8 types), Continuous, Single-Shot,

10 Hz Intermittent, or 10 Hz Intermittent 1 Hz Interval

Package : QFP-80 (0.5 mm pitch, 1.4 mm thick)

980910EBA2

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

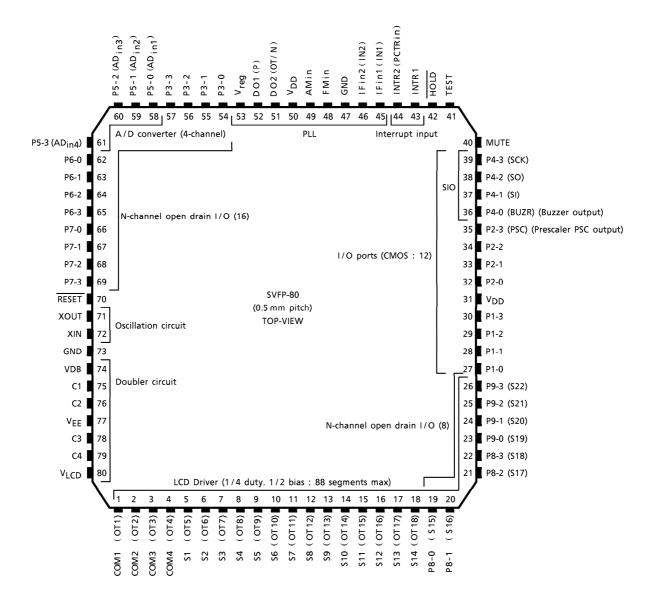

#### **PIN ASSIGNMENT**

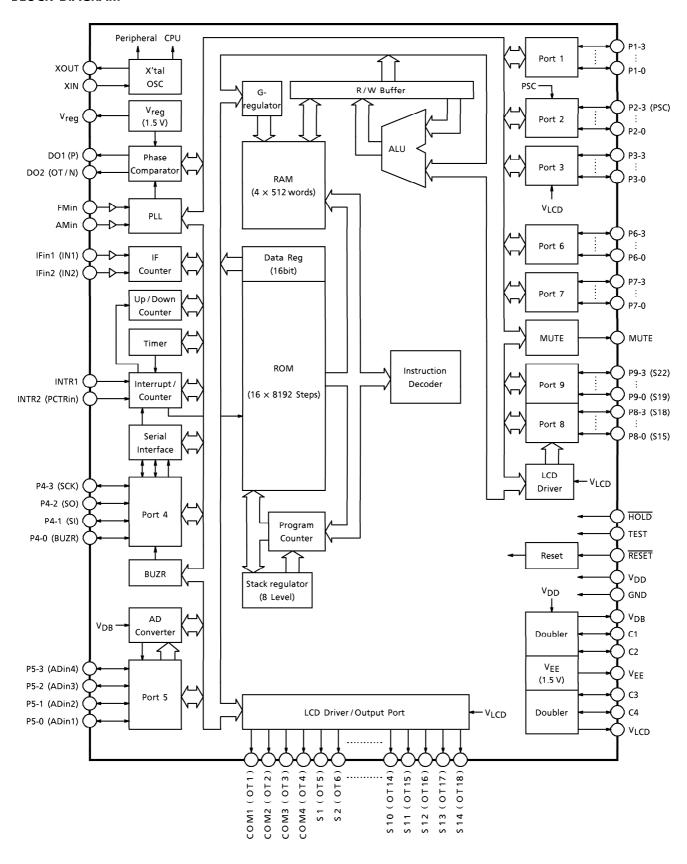

#### **BLOCK DIAGRAM**

# **DESCRIPTION OF PIN FUNCTION**

| PIN No. | SYMBOL                     | PIN NAME                               | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                      | REMARKS                          |

|---------|----------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1       | COM1/OT1                   | LCD common output / Output port C      | Output common signals to LCD panels.<br>Through a matrix with pins S1 to S22, a<br>maximum 88 segments can be displayed.                                                                                                                                                                                                                                                                                                                    |                                  |

| 2       | COM2/OT2                   |                                        | Three levels, V <sub>LCD</sub> , V <sub>EE</sub> , and GND, are output at 62.5 Hz every 2 ms.  V <sub>EE</sub> is output after system reset and                                                                                                                                                                                                                                                                                             | V <sub>LCD</sub> V <sub>EE</sub> |

| 3       | COM3/OT3                   |                                        | CLOCK STOP are released, and a common signal is output after the DISP OFF bit is set to "0".                                                                                                                                                                                                                                                                                                                                                | <i>"</i>                         |

| 4       | COM4/OT4                   |                                        | These pins can be programmed as output ports (Note).                                                                                                                                                                                                                                                                                                                                                                                        |                                  |

| 5~18    | \$1/OT5<br>\$<br>\$14/OT18 | LCD segment<br>output / Output<br>port | Segment signal output terminals for LCD panel. Together with COM1 to COM4, a matrix is formed that can display a maximum of 88 segments.  All pins from S1 to S14 can be programmed as output ports (Note), and all pins from S15 to S22 as I/O ports, in units of pins.  When the pins function as output ports, VLCD pin potential and GND potential are output to them. When the pins function as I/O ports, drain output is N-          | V <sub>LCD</sub>                 |

| 19~26   | P8-0/S15<br>\$<br>P9-3/S22 | LCD segment output/I/O port            | ch open. Because power is supplied from V <sub>LCD</sub> for the I/O ports, up to V <sub>LCD</sub> voltage (3 V) can be applied.  These data ports (OT1 to OT18) are incremented by 1 by instruction every time data are accessed. Therefore, they can be used for external memory address signals, facilitating data access.  (Note): After system reset, the output port pins are set to LCD output, the I/O port pins to I/O port input. | VLCD<br>VDD<br>Input instruction |

| 27~30   | P1-0~P1-3                  | I/O port 1                             | The input and output of these 4-bit I/O ports can be programmed in 1-bit units. These pins can be programmed to be pulled up or down. Thus, they can be used as key input pins.  By altering the input of I/O ports set to input, the CLOCK STOP mode or the WAIT mode can be released, and the MUTE bit of the MUTE pin can be set to "1".                                                                                                 | V <sub>DD</sub> V <sub>DD</sub>  |

| PIN No.        | SYMBOL     | PIN NAME                                        | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                 | REMARKS                                 |

|----------------|------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 32~34          | P2-0~P2-2  | I/O port 2                                      | The input and output of these 4-bit I/O ports can be programmed in 1-bit units. The P2-3 pin is also used as a PLL prescaler PSC signal output pin. A PLL                                                                                                                                                              | ₹ VDD                                   |

| 35             | P2-3 / PSC | I/O Port 2/<br>Prescaler/PSC<br>Output          | can be configured using an external prescaler. In such a case, set the pin to I /O port output.                                                                                                                                                                                                                        | V <sub>DD</sub>                         |

|                |            |                                                 | 4-bit I/O ports, allowing input and output to be programmed in 1 bit units. Pins P5-0 to P5-3 can also be used for analog input to the built-in 6-bit, 4-channel AD converter. The conversion time of the built-in AD converter using the successive                                                                   |                                         |

| 54~57<br>58~61 | 5          | I/O port 3  I/O port 5/ AD analog voltage input | comparison method is 280 $\mu$ s. The necessary pin can be programmed to AD analog input in 1-bit units. Up to the doubled voltage V <sub>DB</sub> (V <sub>DD</sub> × 2) can be input as the AD input voltage. The I/O                                                                                                 | To AD converter  VDD  Input instruction |

| 62~69          | P6-0~P7-3  | I/O port 6, 7                                   | ports are N-ch open drain output. Up to the V <sub>DB</sub> voltage can be applied to the AD input pins, and up to 3.6 V can be applied to the I/O port pins. I/O port 3 can obtain N-ch high-output current (2 mA typ.) even at low voltage. The AD converter and all associated controls are performed via sortware. |                                         |

| PIN No. | SYMBOL                                     | PIN NAME                                                                            | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | REMARKS                                                         |

|---------|--------------------------------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| 36~39   | P4-0 / BUZR P4-1 / SI P4-2 / SO P4-3 / SCK | I/O port 4 /Buzzer output /Serial data input /Serial data output / Serial clock I/O | 4-bit I/O ports, allowing input and output to be programmed in 1-bit units. The P4-0 pin is also used for buzzer output. P4-1 to P4-3 are also used as serial interface circuit (SIO) input/output pins.  The buzzer output can select 8 kinds of 0.625 to 3 kHz frequencies with 4 modes: continuous output, single-shot output, 10 Hz intermittent output, and 10 Hz intermittent 1 Hz interval output.  SIO functions for 4-bit or 8-bit serial data inputs from the SI pin and outputs from the SO pin at the SCK pin clock edge. The clock for serial operation (SCK) is capable of internal (SCK = 37.5 kHz)/external options and rise/fall shift options. The SO pin is also capable of switching to serial inputs (SI), facilitating the control of various LSI's and communication between controllers. When SIO interrupts are enabled, an interrupt is generated after SIO execution and the program jumps to address 4. This is useful for high-speed serial communications.  All SIO inputs use built-in Schmitt circuits. P3-3 pins also functions as the output for a built-in buzzer.  SIO, buzzer, and all associated controls can be programmed. | Input instruction (P4-0)  Input instruction + SIOon (P4-1~P4-3) |

| 40      | MUTE                                       | Muting output port                                                                  | 1-bit output port, normally used for muting control signal output. This pin can set the internal MUTE bit to "1" according to a change in the input of I/O port 1 and HOLD. MUTE bit output logic can be changed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>DD</sub>                                                 |

| 41      | TEST                                       | Test mode control input                                                             | Input pin used for controlling TEST mode. "H" (high) level indicates TEST mode, while "L" (low) indicates normal operation. The pin is normally used at low level or in NC (no connection) state. (A pull-down resistor is builtin).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | N <sub>IN2</sub> V <sub>DD</sub>                                |

| PIN No. | SYMBOL | PIN NAME                   | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | REMARKS |

|---------|--------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 42      | HOLD   | Hold mode<br>control input | Input pin for request/release hold mode. Normally, this pin is used to input radio mode selection signals or battery detection signals.  Hold mode includes CLOCK STOP mode (stops crystal oscillation) and WAIT mode (halts CPU). Setting is implemented with the CKSTP instruction or the WAIT instruction.  To request Clock Stop mode, either L-level detection on the HOLD pin or forced execution can be programmed. The mode is released by H-level detection on the HOLD pin or input change, respectively. Executing the CKSTP instruction stops the clock generator and the CPU, entering memory backup state. In memory backup state, current dissipation becomes low (1 mA or less) and the display output/CMOS output ports automatically become L level and N-ch open drain output Off. Regardless of this input state, Wait mode is executed in order to lower power dissipation. Either crystal oscillator only in operation, all displays are at L level and other pins are in hold state. For CPU suspension, the CPU stops and all others retain their states. Wait mode is released by changing HOLD input. | VDD     |

| PIN No.  | SYMBOL                     | PIN NAME                                                | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | REMARKS                              |

|----------|----------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 43<br>44 | INTR1<br>INTR2<br>/ PCTRin | External<br>interrupt input /<br>Pulse counter<br>input | External interrupt input pins. When interrupts are enabled and a 13.3~ 26.7 ms pulse or longer is input to the pin, interrupt INTR1/2 is generated and the program jumps to address 1/2. Input logic or rising/falling edge can be selected for each input interrupt. The internal 8-bit timer clock input can be selected as input to the pins. When the count value reaches the specified value, an interrupt is generated (address 3). The pin is also used for input of an 8-bit pulse counter. Input rising/falling or upcount/downcount can be selected for the counter. These inputs use built-in Schmitt circuits. The pins can also be used as input ports for input of remote control signals or a tape count. |                                      |

| 45<br>46 | IFin1/IN1<br>IFin2/IN2     | IF signal input<br>/Input port                          | IF signal input pin for the IF counter to count the IF signals of the FM and AM bands and to detect the automatic stop position.  The input frequency is between 0.3~ 12 MHz (0.2 V <sub>p-p min</sub> ). A built-in input amp. and C coupling allow operation at low-level input.  The IF counter is a 20-bit counter with optional gate times of 1, 4, 16 and 64 ms. 20 bits of data can be readily stored in memory. In Manual mode, gate On / Off can be performed using instruction.  The input pin can be programmed for use as an input port (IN port).  (Note): When a pin is set to IF input, the input is at high impedance in PLL Off mode or if the pins are not used for input.                             | R <sub>fIN2</sub><br>V <sub>DD</sub> |

| PIN No. | SYMBOL          | PIN NAME             | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                      | REMARKS         |

|---------|-----------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 31, 50  | V <sub>DD</sub> | Power-supply<br>pins | Pins to which power is applied.  Normally, V <sub>DD</sub> = 0.9~1.8 V is applied.  For the PLL, power for the prescaler in the programmable counter block and IF input amp can be individually programmed. By switching to different modes depending on the power supply voltage and the frequency used, current dissipation can be lowered.  In backup state (at execution of the CKSTP instruction), current dissipation | V <sub>DD</sub> |

| 47, 73  | GND             |                      | drops (1 mA or less) and the power supply voltage can be reduced to 0.75 V. If more than 0.9 V is applied when the pin voltage is 0, the device system is reset and the program starts from address "0". (Power on reset)  (Note): To operate the power on reset, the power supply should start up in 10~100 ms.  (Note): The power-on reset function can be enabled/disabled using the AI switch.                          | GND GND         |

| PIN No. | SYMBOL | PIN NAME                                | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                          | REMARKS                              |

|---------|--------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| 48      | FMin   | FM local<br>oscillation signal<br>input | Programmable counter input pin for FM / AM band. For FM input, mode can be switched between 1/2 + Pulse Swallow VHF and FM mode. For AM input, mode can be switched between Pulse Swallow (HF) and Direct Dividing (LF) mode. Normally, local oscillation output (Voltage-Controlled Oscillator: VCO output) of 50~230 MHz is input in VHF mode; 30~130 MHz in FM mode; 1 to 30 MHz in HF mode; 0.5~8 MHz in LF | R <sub>fIN1</sub> V <sub>DD</sub>    |

| 49      | AMin   | AM local<br>oscillation signal<br>input | mode.  A PLL can be configured using an external prescaler. In such a case, set the pin to LF, and connect the prescaler divider output to the AMin input pin and the PSC input to the P2-3 (PSC) output pin.  With an input amp incorporated, capacitive-coupling, small-amplitude operation.  (Note): The input is at high impedance in PLL Off mode or if the pins are not used for input.                   | R <sub>fIN2</sub><br>V <sub>DD</sub> |

| PIN No. | SYMBOL         | PIN NAME                                                                                           | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REMARKS |

|---------|----------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 52      | DO1/P DO2/OT/N | Phase comparator output / output port / P output  Phase comparator output / output port / N output | PLL phase comparator output pins. Tristate output. When the program counter divider output is higher than the reference frequency, H level is output; when lower, L level; and when they match, high impedance. For the phase comparator power supply, a 1.5 V constant voltage supply (Vreg pin) is used. Even if the power supply voltage drops, a stable PLL can be configured. Because DO1 and DO2 are output in parallel, a filter constant can be optimally designed for each FM/AM band. The DO2 pin can be programmed to high impedance or as an output port (OT). Therefore, using the DO1 and DO2 pins, lockup time can be improved or the pins can be effectively used as output ports. Also, the phase comparator charge pump control signal (P/N) can be output from the DO1/2 pin by program so a PLL using an external charge pump can be configured. In such a case, when the program counter divider output is higher than the reference frequency, P/N is output at H/L level; when lower, L/H level; and when they match, L/L level. When set to this mode, H level output becomes VDD level. (Note): For tristate output, the H level output uses a constant voltage supply. When H level output current is required, Toshiba recommend using an external power supply. |         |

| PIN No. | SYMBOL           | PIN NAME                                 | FUNCTION AND OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | REMARKS         |

|---------|------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 53      | V <sub>reg</sub> | Phase comparator constant voltage supply | Phase comparator constant voltage supply.  When the phase comparator output is tristate output, a constant voltage supply of 1.5 V (typ.) is output to the pin. For this output, connect a stabilizing capacitor (0.47 mF typ.). At constant voltage operation, the H level phase comparator output uses a constant voltage. Thus, when H level output current is required, Toshiba recommend using an external power supply. In such a case, externally apply 1.8~3.6 V to the pin.  When the phase comparator output is output using the charge pump control signal (P/N), the pin becomes the VDD level. Then, the phase comparator output operates using the power supply voltage. | Vreg            |

| 70      | RESET            | Reset input                              | Input pin for system reset signals.  RESET takes place while at low level; at high level, the program starts from address "0".  Normally, if more than 0.9 V is supplied to VDD when the voltage is 0, the system is reset (power on reset).  Accordingly, this pin should be set to high level during operation.  (Note): When the power-on reset function is enabled / disabled using the Al switch, reset by pin.                                                                                                                                                                                                                                                                   | V <sub>DD</sub> |

| PIN No. | SYMBOL          | PIN NAME                             | FUNCTION AND OPERATION                                                                                                                                                                          |                                                     |

|---------|-----------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 71      | XOUT            | Crystal oscillator                   | Crystal oscillator pins.  A reference 75 kHz crystal resonator is connected to the X <sub>IN</sub> and X <sub>OUT</sub> pins.  (Ci = Co = 15 pF)                                                | XOUT R <sub>f</sub> XT                              |

| 72      | XIN             | pin                                  | The oscillator stops oscillating during CKSTP instruction execution. The $V_{XT}$ pin is the power supply for the crystal oscillator. A stabilizing capacitor (0.47 $\mu$ F typ.) is connected. | XIN THE         |

| 74      | V <sub>DB</sub> |                                      | Voltage doubler boosting output pins. The V <sub>DB</sub> pin doubles the V <sub>DD</sub> pin voltage using the voltage doubler                                                                 |                                                     |

| 75      | C1              |                                      | boosting capacitor between C1 and C2. The doubled voltage is used for the AD converter and constant voltage circuit                                                                             |                                                     |

| 76      | C2              |                                      | (Vreg, V <sub>EE</sub> ) power supply.  The V <sub>EE</sub> pin supplies a constant voltage of 1.5 V from the V <sub>DB</sub> voltage. The                                                      | The V <sub>EE</sub> pin supplies a constant voltage |

| 77      | V <sub>EE</sub> | Voltage doubler boosting output pins | voltage is doubled (to 3 v) using the voltage doubler boosting capacitor between C3 and C4. The doubled voltage is then supplied to the V <sub>I CD</sub>                                       | O VLCD                                              |

| 78      | C3              |                                      | pin. The V <sub>EE</sub> potential and the V <sub>LCD</sub> potential are used to drive the LCD.  Connect a stabilizing capacitor between                                                       |                                                     |

| 79      | C4              |                                      | the $V_{DB}$ pin and GND (0.1 mF, 10 mF typ.), and between the $V_{LCD}$ pin and GND (0.1 mF typ.). Connect a voltage                                                                           |                                                     |

| 80      | $V_{LCD}$       |                                      | doubler boosting capacitor (0.1 mF typ.) between C1 and C2, and between C3 and C4. (Note 1)                                                                                                     |                                                     |

(Note 1): When the LCD pin is set as an output port, the H level output is the doubled voltage  $V_{LCD}$ . Therefore, disconnect the voltage doubler boosting capacitor but connect the  $V_{LCD}$  pin to the  $V_{DD}$  pin.

# **MAXIMUM RATINGS** (Ta = 25°C)

| CHARACTERISTIC                             | SYMBOL                    | RATING                      | UNIT |

|--------------------------------------------|---------------------------|-----------------------------|------|

| Supply Voltage                             | $V_{DD}$                  | -0.3~4.0                    | V    |

| Voltage Doubler Boosting<br>Voltage        | V <sub>DB</sub>           | -0.3~4.0                    | V    |

| Output Voltage 1<br>(N-channel Open Drain) | V <sub>O1</sub><br>(Note) | -0.3~4.0                    | V    |

| Output Voltage 2<br>(N-channel Open Drain) | V <sub>O2</sub><br>(Note) | -0.3~V <sub>DB</sub> + 0.3  | V    |

| Output Voltage 3<br>(N-channel Open Drain) | V <sub>O2</sub><br>(Note) | -0.3~V <sub>LCD</sub> + 0.3 | V    |

| Input Voltage                              | VIN                       | -0.3~V <sub>DD</sub> + 0.3  | V    |

| Power Dissipation                          | PD                        | 100                         | mW   |

| Operating Temperature                      | T <sub>opr</sub>          | <b>− 10~60</b>              | °C   |

| Storage Temperature                        | T <sub>stg</sub>          | <b>-65∼150</b>              | °C   |

(Note) :  $V_{O1}$ : P3-0~P3-3, P6-0~P6-3, P7-0~P7-3 pin

V<sub>O2</sub>: P5-0~P5-3 pin V<sub>O3</sub>: P8-0~P8-3, P9-0~P9-3 pin

# **ELECTRICAL CHARACTERISTICS** (Unless otherwise noted, Ta = 25°C, V<sub>DD</sub> = 3.0 V)

| CHARACTERISTIC                       | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                               |     | I TYP. | MAX | UNIT           |

|--------------------------------------|------------------|----------------------|--------------------------------------------------------------|-----|--------|-----|----------------|

| Range Of Operating                   | V <sub>DD1</sub> |                      | Under CPU operation (*)                                      | 0.9 | 9 ~    | 1.8 |                |

| Supply Voltage                       | V <sub>DD2</sub> | _                    | Under PLL operation (*)                                      | 0.  | 9 ~    | 1.8 | ] <sub>v</sub> |

| Range Of Memory<br>Retention Voltage | V <sub>HD</sub>  | _                    | Crystal oscillation stopped (CKSTP instruction executed) (*) | 0.7 | 5 ~    | 1.8 |                |

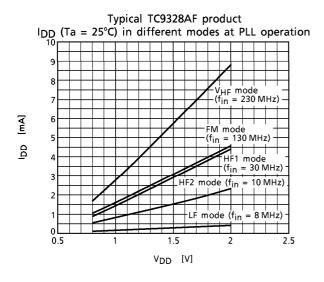

| Operating Current                    | I <sub>DD1</sub> | _                    | PLL operation (VHF mode) at input<br>FMin = 230 MHz          | -   | 6      | 10  | mA             |

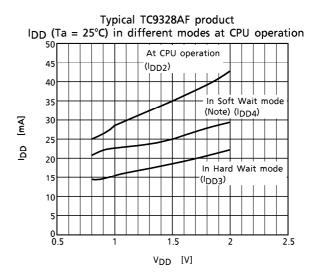

|                                      | I <sub>DD2</sub> | _                    | Under CPU operation only (PLL off, display turned on)        | _   | 40     | 80  |                |

|                                      | lDD3             | _                    | Hard Wait mode (crystal oscillator operating only)           | -   | 20     | 40  |                |

|                                      | I <sub>DD4</sub> | _                    | Soft Wait mode<br>(CPU stopped, PLL off)                     |     | 30     |     | $\mu$ A        |

| Memory Retention<br>Current          | lHD              | _                    | Crystal oscillation stopped (CKSTP instruction executed)     | -   | 0.1    | 1.0 |                |

| Crystal Oscillation<br>Frequency     | fXT              | _                    | (*)                                                          |     | 75     |     | kHz            |

| Crystal oscillation<br>Start-up Time | t <sub>ST</sub>  | _                    | Crystal oscillation f <sub>XT</sub> = 75 kHz                 | _   |        | 1.0 | s              |

For conditions marked by an asterisk (\*), guaranteed when  $V_{DD} = 0.9 \sim 1.8 \text{ V}$ , Ta =  $-10 \sim 60 ^{\circ}\text{C}$

# **VOLTAGE DOUBLER BOOSTING CIRCUIT**

| CHARACTERISTIC                                   | SYMBOL           | TEST<br>CIR-<br>CUIT | TEST CONDITION                                      | MIN  | TYP.                   | MAX  | UNIT  |

|--------------------------------------------------|------------------|----------------------|-----------------------------------------------------|------|------------------------|------|-------|

| Doubled Voltage                                  | V <sub>DB</sub>  | _                    | GND reference (V <sub>DB</sub> )                    | _    | V <sub>DD</sub><br>× 2 | _    | V     |

| Doubled voltage output current                   | IDB              | _                    | $V_{OH} = V_{DB} - 0.1 V (V_{DB})$                  | - 50 | - 200                  | _    | μΑ    |

| Doubled voltage reference voltage                | VEE              | _                    | GND reference (V <sub>EE</sub> )                    | 1.35 | 1.50                   | 1.65 | V     |

| Constant voltage for phase comparator            | V <sub>reg</sub> | _                    | GND reference (V <sub>reg</sub> )                   | 1.35 | 1.50                   | 1.65 | V     |

| Constant voltage temperature characteristic      | Dv               | _                    | GND reference (V <sub>DD</sub> , V <sub>reg</sub> ) | _    | - 5                    | _    | mV/°C |

| Power supply output current for phase comparator | I <sub>reg</sub> | _                    | $V_{OH} = V_{reg} - 0.1 V (V_{reg})$ (Note 1)       | - 50 | - 200                  | _    | μΑ    |

| Doubled voltage                                  | V <sub>LCD</sub> | _                    | GND reference (V <sub>LCD</sub> )                   | 2.7  | 3.0                    | 3.3  | V     |

| Doubled voltage output current                   | <sup>I</sup> LCD | _                    | $V_{OH} = V_{LCD} - 0.1 V (V_{LCD})$ (Note 1)       | - 50 | - 200                  | _    | μΑ    |

(Note 1) : The "H" level output current of the pin using the  $V_{\mbox{reg}}/V_{\mbox{LCD}}$  power supply must not exceed the power supply (doubled voltage :  $V_{\mbox{DB}}$ ) output current.

#### PROGRAMMABLE COUNTER/IF COUNTER OPERATING FREQUENCY RANGE

| CHARACTERISTIC          | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                    |     | MIN | TYP. | MAX | UNIT  |

|-------------------------|--------|----------------------|-------------------------------------------------------------------|-----|-----|------|-----|-------|

| FMin (VHF mode)         | f VHF  | _                    | $V_{IN} = 0.1 V_{p-p}$                                            | (*) | 50  | ~    | 230 |       |

| FMin (FM mode)          | f FM   | _                    | $V_{IN} = 0.1 V_{p-p}$                                            | (*) | 30  | ~    | 130 |       |

| AMin (HF mode)          | f HF1  | _                    | $V_{IN} = 0.1 V_{p-p}$                                            | (*) | 3.0 | ~    | 30  | NALL- |

| Awin (Hr mode)          | f HF2  | _                    | $V_{IN} = 0.1 V_{p-p}$                                            | (*) | 1.0 | ~    | 10  | MHz   |

| AMin (LF mode)          | f LF   | _                    | $V_{IN} = 0.1 V_{p-p}$                                            | (*) | 0.5 | ~    | 8   |       |

| IFin1, IFin2            | f IF   | _                    | $V_{IN} = 0.1 V_{p-p}$                                            | (*) | 0.3 | ~    | 12  |       |

| PSC transfer delay time | tpd    | _                    | (PSC) $C_L = 15 \text{ pF},$<br>$V_{DD} = 1.1 \sim 1.8 \text{ V}$ | (*) |     | _    | 400 | ns    |

#### PROGRAMMABLE COUNTER/IF COUNTER INPUT AMPLITUDE RANGE

| CHARACTERISTIC  | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION     |     | MIN | TYP. | MAX | UNIT             |

|-----------------|--------|----------------------|--------------------|-----|-----|------|-----|------------------|

| FMin (VHF mode) | V VHF  | _                    | Same as for f VHF  | (*) | 0.1 | ~    | 0.6 |                  |

| FMin (FM mode)  | V FM   | _                    | Same as for f FM   | (*) | 0.1 | ~    | 0.6 |                  |

| AMin (HF mode)  | V HF   | _                    | Same as for fHF1~2 | (*) | 0.1 | ~    | 0.6 | V <sub>p-p</sub> |

| AMin (LF mode)  | V LF   | _                    | Same as for f LF   | (*) | 0.1 | ~    | 0.6 |                  |

| IFin1, IFin2    | V IF   | _                    | Same as for f IF   | (*) | 0.1 | ~    | 0.6 |                  |

(\*) : Guaranteed when  $V_{DD} = 0.9 \sim 1.8 \text{ V}$ , Ta =  $-10 \sim 60 ^{\circ}\text{C}$ .

# LCD COMMON OUTPUT/SEGMENT OUTPUT (COM1~COM4, S1~S22)

| CHARACTERISTIC    |                           | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                        | MIN    | TYP.   | MAX  | UNIT |

|-------------------|---------------------------|--------|----------------------|-----------------------------------------------------------------------|--------|--------|------|------|

| ,,,,              | "II" I ovol               | IOH1   | _                    | $V_{LCD} = 3 V$ ,<br>$V_{OH} = V_{LCD} - 0.3 V$<br>$(COM1 \sim COM4)$ | - 0.10 | - 0.20 |      |      |

| Output Current    | Output Current  "L" Level | IOH2   | _                    | $V_{LCD} = 3 V,$<br>$V_{OH} = V_{LCD} - 0.3 V$<br>(\$1~\$22)          | - 0.05 | - 0.10 | ı    | mA   |

|                   |                           | IOL1   |                      | $V_{LCD} = 3 \text{ V}, V_{OL} = 0.3 \text{ V}$<br>(COM1~COM4)        | 0.10   | 0.30   | l    |      |

|                   |                           | IOL2   | _                    | $V_{LCD} = 3 \text{ V}, V_{OL} = 0.3 \text{ V}$ (\$1~\$22)            | 0.05   | 0.15   |      |      |

| Output Voltage 1/ | 2 Level                   | VBS    | _                    | No load (COM1~COM4)                                                   | 1.35   | 1.5    | 1.65 | ٧    |

# OUTPUT PORT, I/O PORT (OT1~OT18, P8-0~P8-3, P9-0~P9-3)

| CHARACTER          | ISTIC     | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                              | MIN                      | TYP.  | MAX                      | UNIT |

|--------------------|-----------|-----------------|----------------------|-----------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|

| Output Current     | "H" Level | ЮНЗ             |                      | $V_{LCD} = 3 V$ ,<br>$V_{OH} = V_{LCD} - 0.3 V$<br>(Note1, except I/O port) | - 1.5                    | - 3.0 | ı                        | mA   |

|                    | "L" Level | IOL3            | _                    | $V_{LCD} = 3 \text{ V}, V_{OL} = 0.3 \text{ V}$                             | 1.5                      | 3.0   |                          |      |

| Input Leak Current | t         | ILI             |                      | $V_{IH} = V_{LCD}$<br>$V_{IL} = 0 V$<br>(P8-0~P8-3, P9-0~P9-3)              | ı                        | I     | ± 1.0                    | μΑ   |

| Input Voltage      | "H" Level | V <sub>IH</sub> | _                    | (P8-0~P8-3, P9-0~P9-3)                                                      | V <sub>DD</sub><br>× 0.8 | ٧     | V <sub>DD</sub>          | V    |

| input voltage      | "L" Level | V <sub>IL</sub> | _                    | (P8-0~P8-3, P9-0~P9-3)                                                      | 0                        | ~     | V <sub>DD</sub><br>× 0.2 | V    |

I/O PORT (P1-0~P7-3)

| CHARACTER                       | ISTIC     | SYMBOL          | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                                             | MIN                   | TYP. | MAX                   | UNIT    |

|---------------------------------|-----------|-----------------|----------------------|--------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|---------|

|                                 | "H" level | IOH4            | _                    | $V_{DD} = 1.5 V,$<br>$V_{OH} = V_{DD} - 0.2 V$<br>(I/O port P2, P4)                        | -0.4                  | -0.8 | _                     |         |

|                                 |           | IOH5            | _                    | V <sub>DD</sub> = 0.9 V,<br>V <sub>OH</sub> = V <sub>DD</sub> - 0.2 V<br>(I/O port P2, P4) | - 0.04                | -0.2 | _                     |         |

| Output Current                  |           | IOL4            | _                    | V <sub>DD</sub> = 1.5 V,<br>V <sub>OL</sub> = 0.2 V<br>(except I/O port P3)                | 0.5                   | 1.0  | _                     | mA      |

|                                 |           | IOL5            | _                    | V <sub>DD</sub> = 0.9 V,<br>V <sub>OL</sub> = 0.2 V<br>(except I/O port P3)                | 0.1                   | 0.3  | _                     |         |

|                                 |           | IOL6            | _                    | $V_{DD} = 0.9 \sim 1.8 \text{ V},$<br>$V_{OL} = 0.2 \text{ V}$<br>(I/O port P3)            | 1.0                   | 2.0  | _                     |         |

|                                 |           |                 | _                    | $V_{IH} = V_{DD}, V_{IL} = 0 V$<br>(I/O port P1, P2, P4)                                   | _                     | _    | ± 1.0                 |         |

| Input Leak Current              | t         | ILI             | _                    | $V_{IH} = 3.6 \text{ V}, V_{IL} = 0 \text{ V}$ (I/O port P3, P6, P7)                       | _                     | _    | ± 1.0                 | $\mu$ A |

|                                 |           |                 | _                    | V <sub>IH</sub> = V <sub>DB</sub> , V <sub>IL</sub> = 0 V<br>(I/O port P5)                 | _                     | _    | ± 1.0                 |         |

| Innut Voltage                   | "H" level | V <sub>IH</sub> | _                    | _                                                                                          | V <sub>DD</sub> × 0.8 | ~    | $V_{DD}$              | V       |

| Input Voltage                   | "L" level | V <sub>IL</sub> | _                    | _                                                                                          | 0                     | ~    | V <sub>DD</sub> × 0.2 | V       |

| Input Pull-down R               | esistor   | RIN1            | _                    | When P1-0~P1-3 are set to pull-down or pull-up                                             | 30                    | 60   | 120                   | kΩ      |

| SCK Clock External<br>Frequency | Input     | fsio            | _                    | When I/O port P4-3 are set to serial clock input                                           | _                     | _    | 200                   | kHz     |

For conditions marked by an asterisk (\*), guaranteed when  $V_{DD} = 1.8 \sim 3.6 \text{ V}$ , Ta =  $-10 \sim 60 ^{\circ}\text{C}$

(Note 1) : The "H" level output current is the current when the pin power supply is fixed. Make sure that pins using  $V_{reg}/V_{LCD}$  power supply do not exceed the power supply (doubled voltage :  $V_{DB}$ ) output current.

# MUTE OUTPUT

| CHARACTERISTIC |           | SYMBOL | TEST<br>CIR-<br>CUIT                           | TEST CONDITION                                 | MIN   | TYP.  | MAX | UNIT |

|----------------|-----------|--------|------------------------------------------------|------------------------------------------------|-------|-------|-----|------|

|                | "H" level | IOH4   | _                                              | $V_{DD} = 1.5 V,$<br>$V_{OH} = V_{DD} - 0.2 V$ | -0.4  | - 0.8 | 1   |      |

| Output Current | IOH5      | _      | $V_{DD} = 0.9 V,$<br>$V_{OH} = V_{DD} - 0.2 V$ | -0.04                                          | - 0.2 | 1     | mA  |      |

|                | "L" level | IOL4   | _                                              | $V_{DD} = 1.5 V, V_{OL} = 0.2 V$               | 0.5   | 1.0   |     |      |

|                | Lievei    | IOL5   |                                                | $V_{DD} = 0.9 V, V_{OL} = 0.2 V$               | 0.1   | 0.3   |     |      |

# HOLD, INTR1/2, IN1/2 INPUT PORT, RESET INPUT

| CHARACTER         | ISTIC     | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION                     | MIN                      | TYP. | MAX                   | UNIT    |

|-------------------|-----------|--------|----------------------|------------------------------------|--------------------------|------|-----------------------|---------|

| Input Leak Curren | t         | ILI    | _                    | $V_{IH} = V_{DD}$ , $V_{IL} = 0 V$ | _                        | _    | ± 1.0                 | $\mu$ A |

| Input Voltage     | "H" level | VIH3   | _                    | _                                  | V <sub>DD</sub><br>× 0.8 | ?    | V <sub>DD</sub>       | V       |

|                   | "L" level | VIL3   |                      | _                                  | 0                        | ~    | V <sub>DD</sub> × 0.2 | V       |

# AD CONVERTER (ADin1~ADin4)

| CHARACTERISTIC             | SYMBOL | TEST<br>CIR-<br>CUIT | TEST CONDITION                                                             | MIN | TYP.  | MAX   | UNIT |

|----------------------------|--------|----------------------|----------------------------------------------------------------------------|-----|-------|-------|------|

| Analog Input Voltage Range | VAD    |                      | ADin1~ADin4                                                                | 0   | ~     | VDB   | ٧    |

| Resolution                 | VRES   | _                    | _                                                                          | _   | 6     | _     | bit  |

| Conversion Total Error     | _      | _                    | _                                                                          | _   | ± 0.5 | ± 1.0 | LSB  |

| Analog Input Leak          | ILI    | _                    | $V_{DD} = V_{DB}$ , $V_{IH} = V_{DB}$ ,<br>$V_{IL} = 0 V$<br>(ADin1~ADin4) |     | _     | ± 1.0 | μΑ   |

# DO1, DO2 OUTPUT

| CHARACTER                | ISTIC     | SYMBOL | TEST<br>CIR-<br>CUIT                                                   | TEST CONDITION                                                               | MIN  | TYP. | MAX   | UNIT |

|--------------------------|-----------|--------|------------------------------------------------------------------------|------------------------------------------------------------------------------|------|------|-------|------|

| Output Current "H" level | IOH4      | _      | $V_{reg} = 1.5 \text{ V},$ $V_{OH} = V_{reg} - 0.2 \text{ V}$ (Note 1) | -0.4                                                                         | -0.8 |      | mA    |      |

|                          | "L" level | IOL4   |                                                                        | $V_{reg} = 1.5 V, V_{OL} = 0.2 V$                                            | 0.5  | 1.0  | _     |      |

| Output Off Leak C        | Current   | ITL    | _                                                                      | V <sub>DD</sub> = 1.5 V,<br>V <sub>TLH</sub> = 1.5 V, V <sub>TLL</sub> = 0 V | -    | _    | ± 100 | nA   |

#### **OTHERS**

| CHARACTERISTIC                              | SYMBOL            | TEST<br>CIR-<br>CUIT | TEST CONDITION       | MIN | TYP. | MAX  | UNIT |

|---------------------------------------------|-------------------|----------------------|----------------------|-----|------|------|------|

| Input Pull-down Resistance                  | RIN2              | _                    | (TEST)               | 5   | 10   | 30   | kΩ   |

| X <sub>IN</sub> Amp. Feedback<br>Resistance | RfXT              | _                    | (XIN-XOUT)           | _   | 20   | _    | МΩ   |

| X <sub>OUT</sub> Output Resistance          | ROUT              | <b>—</b>             | (XOUT)               | _   | 4    | _    |      |

| Input Amp. Feedback                         | Rf <sub>IN1</sub> | _                    | (FMin)               | 100 | 200  | 400  | kΩ   |

| Resistance                                  | Rf <sub>IN2</sub> |                      | (AMin, IFin1, IFin2) | 300 | 600  | 1200 |      |

For conditions marked by an asterisk (\*), guaranteed when  $V_{DD}$  = 1.8 ~3.6 V,  $T_a = -10 \sim 60 ^{\circ} C$

(Note 1) : The "H" level output current is the current when the pin power supply is fixed. Make sure that pins using  $V_{reg}/V_{LCD}$  power supply do not exceed the power supply (doubled voltage :  $V_{DB}$ ) output current.

(Note): The I<sub>DD</sub> (operating current) in Soft Wait mode is the current dissipation value. The actual current dissipation value differs depending on the CPU execution state.

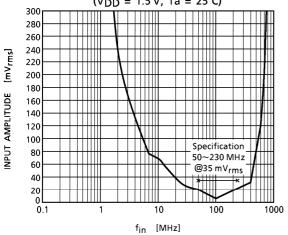

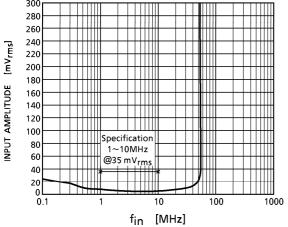

Typical TC9328AF product Input sensitivity VHF mode

(VDD = 1.5 V, Ta = 25°C)

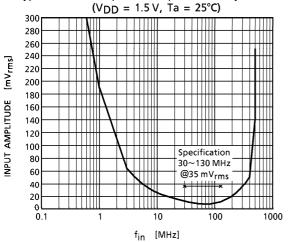

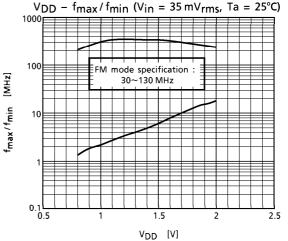

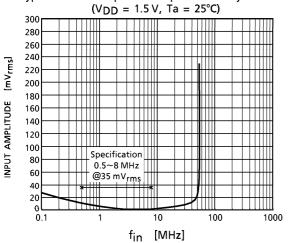

Typical TC9328AF product Input sensitivity FM mode

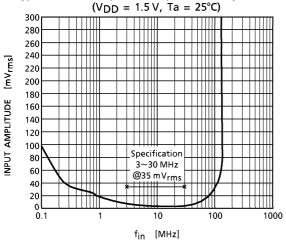

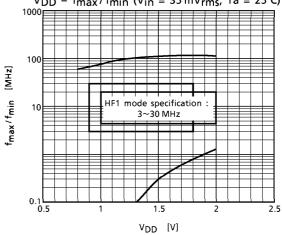

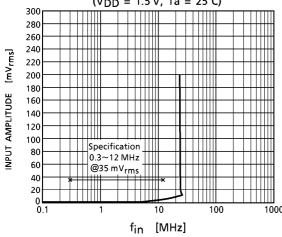

Typical TC9328AF product Input sensitivity HF1 mode  $(VDD = 1.5 \text{ V} \text{ Ta} = 25^{\circ}\text{C})$

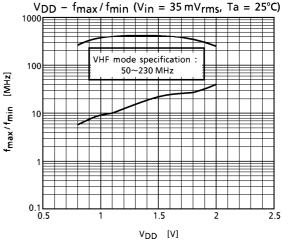

Typical TC9328AF product Input sensitivity VHF mode

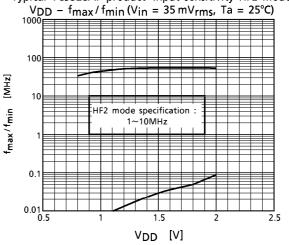

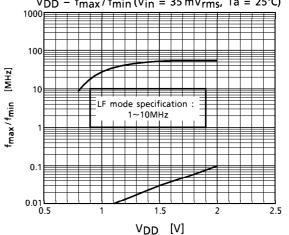

Typical TC9328AF product Input sensitivity FM mode VDD - fmax/fmin (Vin = 35 mVrms, Ta = 25°C)

Typical TC9328AF product Input sensitivity HF1 mode VDD - fmax/fmin (Vin = 35 mVrms, Ta = 25°C)

Typical TC9328AF product Input sensitivity LF mode

Typical TC9328AF product Input sensitivity IFin mode  $(V_{DD} = 1.5 V, Ta = 25 °C)$

Typical TC9328AF product Input sensitivity HF2 mode

Typical TC9328AF product Input sensitivity LF mode  $V_{DD} - f_{max}/f_{min} (V_{in} = 35 \text{ mV}_{rms}, Ta = 25^{\circ}\text{C})$

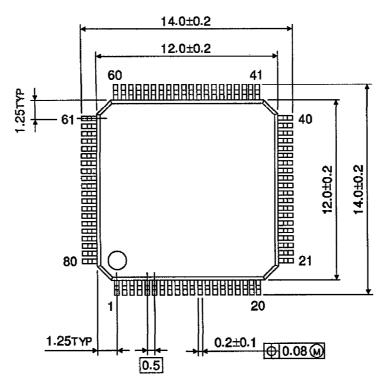

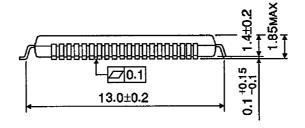

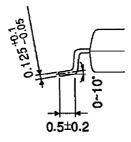

# **PACKAGE DIMENSIONS**

LQFP80-P-1212-0.50A

Unit: mm

Weight: 0.45 g (Typ.)