# TOSHIBA

8-bit Microcontroller TLCS-870/C Series Application Note (TMP86CM29)

Rev.1.0 22-May-2000

**TOSHIBA CORPORATION**

## Preface

Thank you very much for making use of TOSHIBA semiconductor products.

Toshiba has a broad range of microcomputers which are applicable to various fields ranging from consumer to industrial. The microcomputers have the development support systems and the reference application software to reduce application software development periods.

Toshiba 4-bit and 8-bit single chip microcomputers include wide range lineups from small-scale system 4-bit microcomputers, TLCS-47E series and 4-bit microcomputers, TLCS-47, 470 and 470A series which have various peripheral circuits and abundant types to 8-bit microcomputers, TLCS-870, 870/X, and 90 series which have large memory and realize high-level processing to support diverse applications and satisfy various needs.

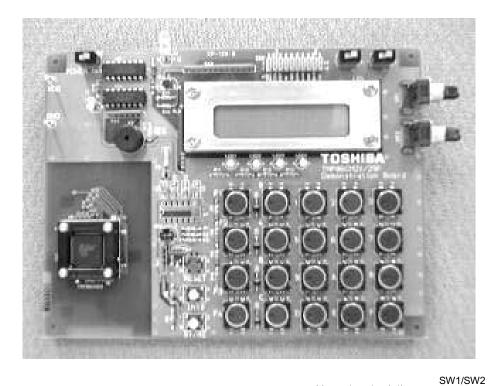

This document describes the specifications of the demonstration set for Toshiba original 8-bit microcontroller TMP86Cx29. Specific examples that can be referred to for software development are also provided.

TLCS-870/C series attains design optimization with TLCS-870/X series at a base, and has realized further low power consumption. In addition, it adopts the command system which has improved an object efficiency of the C language, and offers the high cost performance.

Toshiba intends the microcomputers which have one-time PROM to add to the lineup, which are used for program debugging, system evaluation and pre-production at the application system development stage. It enables operating in low voltage and low power consumption.

For any engineering questions of the product described in this document, please do not hesitate to contact the local Toshiba sales representative.

Toshiba endeavors to write exactly and includes the latest information in this document.

If any idea that may occur to your mind regarding this documentation, please do not hesitate to point out.

## Contents

| 1. Ove<br>1.1<br>1.2 | Overview           | w of Voltmeter Mode<br>w of Test Mode                             | 1  |

|----------------------|--------------------|-------------------------------------------------------------------|----|

| 1.3                  | Overview           | v of ROM/RAM Check Mode                                           | 1  |

| 2. Set               |                    | ating Mode                                                        |    |

| 3. Dis               | play and l         | Key Placement                                                     | 4  |

| 3.1                  | Key Plac           | cement and Names                                                  | 4  |

| 3.2                  |                    | Section                                                           |    |

|                      |                    |                                                                   |    |

| 4.1                  |                    | gnments                                                           |    |

| 4.2                  |                    | ctions (TMP86CM29F)                                               |    |

| 5. Son<br>5.1        |                    | cifications                                                       |    |

|                      |                    | erview                                                            |    |

|                      |                    | le Transition Diagram                                             |    |

| 5.1                  |                    | ailed Description of Each Mode of Voltmeter                       |    |

| Ę                    | 5.1.3.1            | Voltmeter Mode                                                    | 10 |

| Ę                    | 5.1.3.2            | Voltage Level Monitor Mode                                        | 11 |

| ŧ                    | 5.1.3.3            | Voltage Change Monitor Mode                                       | 14 |

| Ę                    | 5.1.3.4            | Voltage Level Compare Mode                                        | 15 |

| Ę                    | 5.1.3.5            | Power-Saving Mode                                                 |    |

| 5.1                  | 1.4 Infr           | ared Transmit Format                                              | 16 |

| Ę                    | 5.1.4.1            | Basic Format of Header and Data Sections                          | 16 |

| Ę                    | 5.1.4.2            | Common Rules of Infrared Transmit Data Format                     | 17 |

| ŧ                    | 5.1.4.3            | Infrared Transmit Data Format in Voltmeter Mode                   | 17 |

| ŧ                    | 5.1.4.4            | Infrared Transmit Data Format in Voltage Level Monitor Mode       | 17 |

| ŧ                    | 5.1.4.5            | Infrared Transmit Data Format in Voltage Change Monitor Mode      | 18 |

|                      | 5.1.4.6            | Infrared Transmit Data Format in Voltage Level Compare Mode       |    |

| 5.2                  |                    | le                                                                |    |

| • • •                |                    | erview                                                            |    |

|                      | 5.2.1.1            | Operation State in Test Mode                                      |    |

|                      | 5.2.1.2            | Description of LED Display in Test Mode                           |    |

|                      | 5.2.1.3            | LCD Display in Test Mode                                          |    |

|                      | 5.2.1.4<br>2.2 Tra | Key Input in Test Mode                                            |    |

|                      |                    | nsition of Test Mode State<br>cifications of Test Mode Test Items |    |

|                      | 5.2.3.1            | Time Base Timer Test [Test number: 0]                             | 22 |

|                      | 5.2.3.2            | Watchdog Timer Test [Test number: 1]                              |    |

|                      | 5.2.3.3            | Divider Output Test [Test number: 2]                              |    |

|                      | 5.2.3.4            | TC1 Test [Test number: 3]                                         |    |

|                      | 5.2.3.5            | TC3 Test [Test number: 4]                                         |    |

|                      | 5.2.3.6            | TC4 Test [Test number: 5]                                         |    |

|                      | 5.2.3.7            | 16-bit TC3 + 4 Test [Test number: 6]                              |    |

|                      | 5.2.3.8            | TC5 Test [Test number: 7]                                         |    |

|                      | 5.2.3.9            | TC6 Test [Test number: 8]                                         |    |

|                      | 5.2.3.10           | $16 \cdot \text{bit TC5} + 6 \text{ Test number: 9}$              |    |

|                      | 5.2.3.11           | UART Test [Test number: 10]                                       |    |

|                      | 5.2.3.12           | SIO Test [Test number: 11]                                        |    |

|                      | 5.2.3.13           | ADC Test [Test number: 12]                                        |    |

|                      | 5.2.3.14           | LCD Test [Test number: 12]                                        |    |

|                      | 5.2.3.15           | Continuous Test [Test number: 14]                                 |    |

|                      |                    |                                                                   |    |

| Į  | 5.3  | ROM/RAM Check Mode | 52 |

|----|------|--------------------|----|

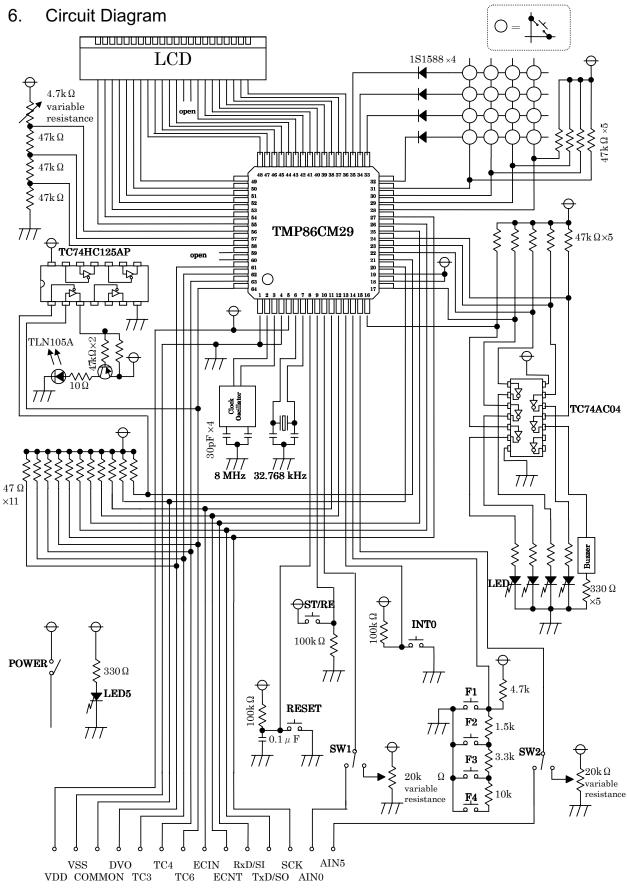

| 6. | Circ | uit Diagram        | 53 |

## 1. Overview

This system is used to perform demonstrations and tests for the TMP86Cx29. There are three types of operating modes as shown below:

- Voltmeter mode

- Test mode

- ROM/RAM Check mode

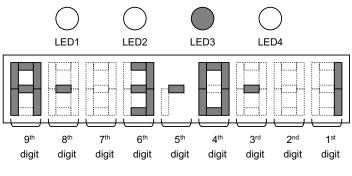

The operating mode of the system can be judged by LED1. When LED1 is "ON", the system is in Voltmeter mode. When LED1 is "OFF", the system is either in Test mode or ROM/RAM Check mode. For the position of LEDs, see "3.2 Display Section".

#### 1.1 Overview of Voltmeter Mode

In Voltmeter mode, a voltmeter is realized by using a 10-bit AD converter, LCD driver, etc. Voltmeter mode has the following four types of modes:

- Standard voltmeter mode

- Voltage level monitor mode

- Voltage change monitor mode

- Voltage level compare mode

Note also that if no key input is made for a fixed period of time (ca. 60 seconds), Voltage mode shifts to the "power-saving mode" to temporarily suspend the functions of the microcontroller.

#### 1.2 Overview of Test Mode

In Test mode, the waveforms of timer cycle, serial communication data, etc are measured by using an external connecting pin so that the system can check whether each function of the microcontroller is operating according to the set values.

Tests can be made on the following functions:

- TBT

- WDT

- TC1

- TC3

- TC4

- 16bit TC3 + 4

- TC5

- TC6

- 16bit TC5+6

- UART

- SIO

- AD converter

- Continuous test

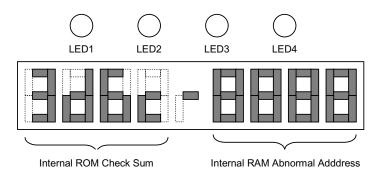

#### 1.3 Overview of ROM/RAM Check Mode

ROM/RAM Check mode is used to display the check sum of internal ROM and address in RAM where Read/Write are not performed properly.

Key operation is not available in this mode. After the check sum and abnormal RAM address are displayed, only "Reset Key" is accepted.

1

## 2. Setting Operating Mode

The operating mode can be selected by pressing an appropriate key at power-up/reset. When **Key0** is pressed at power-up/reset, it becomes Test mode. When **Key1** is pressed, it becomes ROM/RAM Check mode. When one of other keys or no key is pressed, Voltmeter mode is selected.

For the placement of keys, see "3.1 Key Placement and Names".

## 3. Display and Key Placement

## 3.1 Key Placement and Names

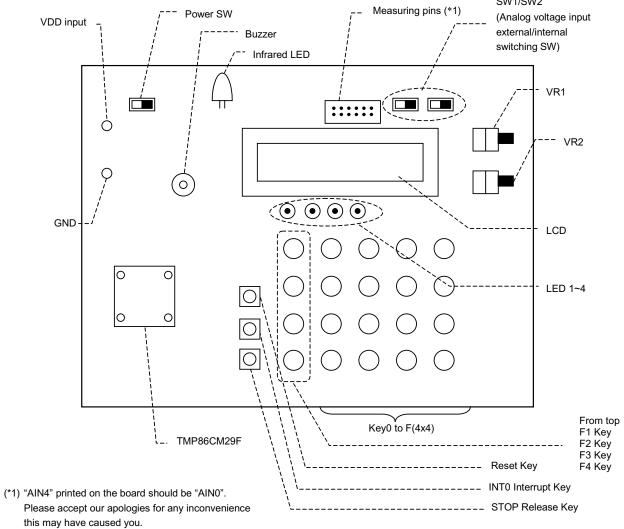

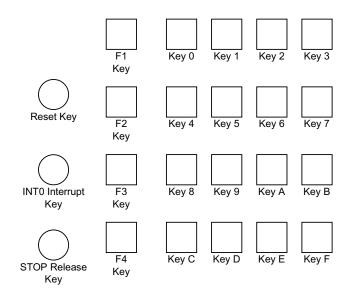

Figure 3.1.1 shows the key placement and key names.

Figure 3.1.1 Key Placement

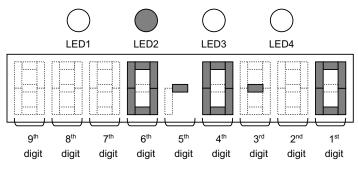

## 3.2 Display Section

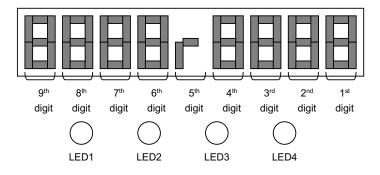

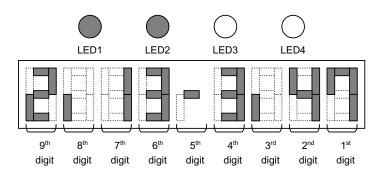

Figure 3.2.1 shows an external view of the display section.

Figure 3.2.1 External View of Display Section

## 4. I/O Port

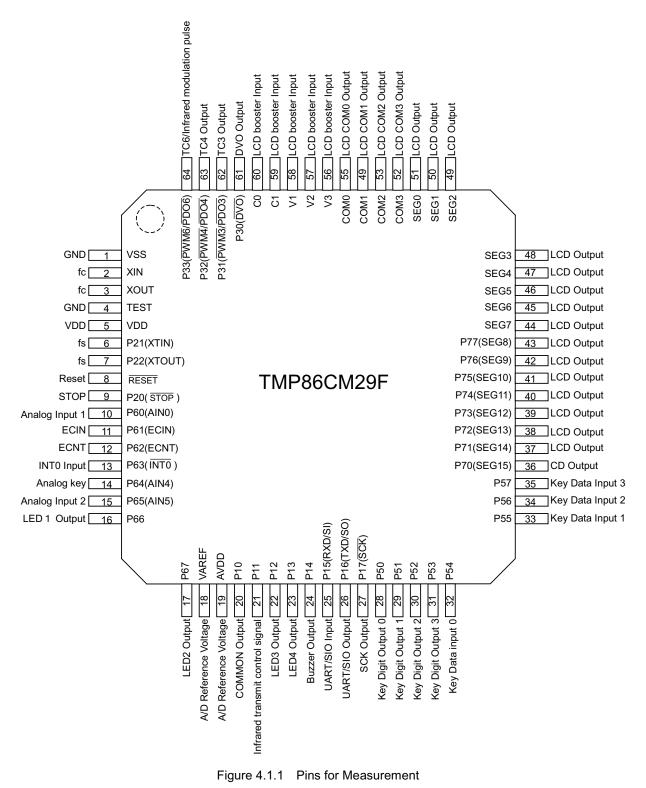

4.1 Pin Assignments

## 4.2 Pin Functions (TMP86CM29F)

| No | Pin Name           | Signal Name                            | Structure<br>(Initial Value) | Remarks                                 |

|----|--------------------|----------------------------------------|------------------------------|-----------------------------------------|

| 1  | VSS                | Ground                                 |                              |                                         |

| 2  | XIN                | High-frequency Resonator<br>Connection | —                            | 8MHz                                    |

| 3  | XOUT               | High-frequency Resonator<br>Connection | —                            | 8MHz                                    |

| 4  | TEST               | Test Input                             |                              | Not used (GND)                          |

| 5  | VDD                | Power Supply Input                     | —                            | VDD = 5[V]                              |

| 6  | P21(XTIN)          | Low-frequency Resonator<br>Connection  | SkOd(Z)                      | 32.768KHz                               |

| 7  | P22(XTOUT)         | Low-frequency Resonator<br>Connection  | SkOd(Z)                      |                                         |

| 8  | RESET              | Reset Input                            |                              | Reset input                             |

| 9  | P20( INT5 / STOP ) | STOP Input                             | SkOd(Z)                      |                                         |

| 10 | P60(AIN0)          | Analog Input 1                         | TriS(Z)                      | VR/external input to be switched by SW1 |

| 11 | P61(AIN1/ECIN)     | ECIN Output                            | TriS(Z)                      |                                         |

| 12 | P62(AIN2/ECNT)     | ECNT Output                            | TriS(Z)                      |                                         |

| 13 | P63(AIN3/ INT0 )   | INT0 Input                             | TriS(Z)                      |                                         |

| 14 | P64(AIN4/STOP2)    | Analog Key Input (AIN4)                | TriS(Z)                      |                                         |

| 15 | P65(AIN5/STOP3)    | Analog Input 2                         | TriS(Z)                      | VR/external input to be switched by SW2 |

| 16 | P66(AIN6/STOP4)    | LED 1 Output                           | TriS(Z)                      |                                         |

| 17 | P67(AIN7/STOP5)    | LED 2 Output                           | TriS(Z)                      |                                         |

| 18 | VAREF              | AD Reference Voltage                   |                              |                                         |

| 19 | AVDD               | AD Reference Voltage                   |                              |                                         |

| 20 | P10(SEG31)         | COMMON Output                          | SkOd(Z)                      |                                         |

| 21 | P11(SEG30)         | Infrared Transmit Control<br>Signal    | SkOd(Z)                      |                                         |

| 22 | P12(SEG29/INT1)    | LED3 Output                            | SkOd(Z)                      |                                         |

| 23 | P13(SEG28/INT2)    | LED4 Output                            | SkOd(Z)                      |                                         |

| 24 | P14(SEG27/INT3)    | Buzzer Output                          | SkOd(Z)                      |                                         |

| 25 | P15(SEG26/RXD/SI)  | UART/SIO Input                         | SkOd(Z)                      |                                         |

| 26 | P16(SEG25/TXD/SO)  | UART/SIO Output                        | SkOd(Z)                      |                                         |

| 27 | P17(SEG24/ SCK )   | SCK Output                             | SkOd(Z)                      |                                         |

| 28 | P50(SEG23)         | Key Digit Output 0                     | SkOd(Z)                      |                                         |

| 29 | P51(SEG22)         | Key Digit Output 1                     | SkOd(Z)                      |                                         |

| 30 | P52(SEG21)         | Key Digit Output 2                     | SkOd(Z)                      |                                         |

| 31 | P53(SEG20)         | Key Digit Output 3                     | SkOd(Z)                      |                                         |

| 32 | P54(SEG19)         | Key Data Input 0                       | SkOd(Z)                      |                                         |

| 33 | P55(SEG18)         | Key Data Input 1                       | SkOd(Z)                      |                                         |

| 34 | P56(SEG17)         | Key Data Input 2                       | SkOd(Z)                      |                                         |

| 35 | P57(SEG16)         | Key Data Input 3                       | SkOd(Z)                      |                                         |

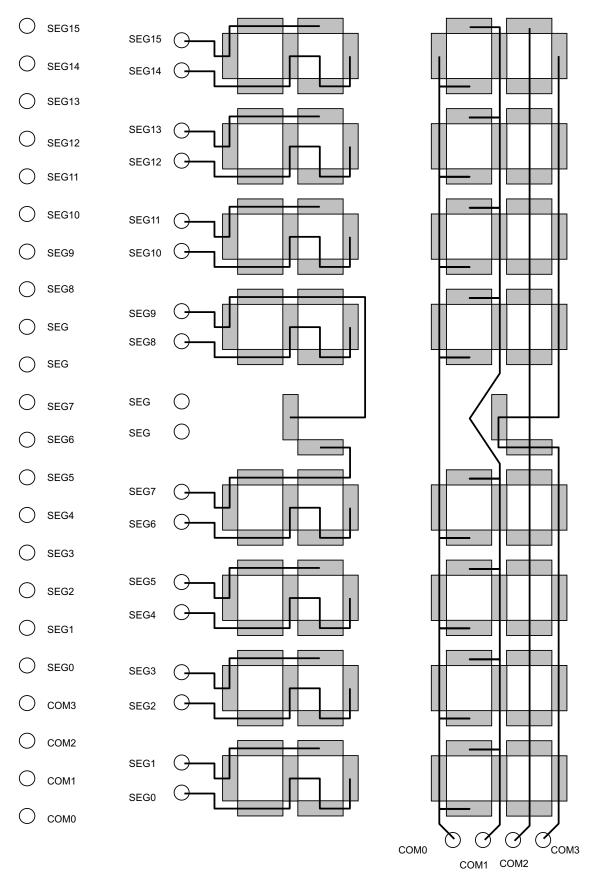

| 36 | P70(SEG15)         | LCD Data Output                        | SkOd(Z)                      |                                         |

| 37 | P71(SEG14)         | LCD Data Output                        | SkOd(Z)                      |                                         |

| 38 | P72(SEG13)         | LCD Data Output                        | SkOd(Z)                      |                                         |

| 39 | P73(SEG12)         | LCD Data Output                        | SkOd(Z)                      |                                         |

| 40 | P74(SEG11)         | LCD Data Output                        | SkOd(Z)                      |                                         |

| 41 | P75(SEG10)         | LCD Data Output                        | SkOd(Z)                      |                                         |

| 42 | P76(SEG9)          | LCD Data Output                        | SkOd(Z)                      |                                         |

| 43 | P77(SEG8)          | LCD Data Output                        | SkOd(Z)                      |                                         |

| Sk0d (Z) | Sink Open Drain (Z)                  |

|----------|--------------------------------------|

| TriS (Z) | Tri-state (Z)                        |

| PcPp (Z) | Push Pull with P-channel Control (Z) |

| No | Pin Name                       | Signal Name                   | Structure<br>(Initial Value) | Remarks              |

|----|--------------------------------|-------------------------------|------------------------------|----------------------|

| 44 | SEG7                           | LCD Data Output               | —                            |                      |

| 45 | SEG6                           | LCD Data Output               | _                            |                      |

| 46 | SEG5                           | LCD Data Output               | —                            |                      |

| 47 | SEG4                           | LCD Data Output               | —                            |                      |

| 48 | SEG3                           | LCD data Output               |                              |                      |

| 49 | SEG2                           | LCD data Output               | —                            |                      |

| 50 | SEG1                           | LCD data Output               | —                            |                      |

| 51 | SEG0                           | LCD data Output               | _                            |                      |

| 52 | COM3                           | LCD COM3 Output               | —                            |                      |

| 53 | COM2                           | LCD COM2 Output               |                              |                      |

| 54 | COM1                           | LCD COM1 Output               | —                            |                      |

| 55 | COM0                           | LCD COM0 Output               | —                            |                      |

| 56 | V3                             | Booster Pin for LCD Drive     | _                            |                      |

| 57 | V2                             | Booster Pin for LCD Drive     | —                            |                      |

| 58 | V1                             | Booster Pin for LCD Drive     | _                            |                      |

| 59 | C1                             | Booster Pin for LCD Drive     | _                            |                      |

| 60 | C0                             | Booster Pin for LCD Drive     | —                            |                      |

| 61 | P30( DVO )                     | DVO Output                    | PcPp(Z)                      |                      |

| 62 | P31( PWM3 / PDO3 / TC3)        | TC3 Output                    | PcPp(Z)                      |                      |

| 63 | P32( PWM4 / PDO4 / PPG4 / TC4) | TC4 Output                    | PcPp(Z)                      |                      |

| 64 | P33( PWM6 / PDO6 / PPG6 TC6)   | TC6/Infrared Modulation Pulse | PcPp(Z)                      | 38KHz carrier output |

Sk0d (Z) Sink Open Drain (Z)

TriS (Z) Tri-state (Z)

PcPp (Z)

Push Pull with P-channel Control (Z)

## 5. Software Specifications

#### 5.1 Digital Voltmeter by AD Converter

#### 5.1.1 Overview

A digital voltmeter is realized by using Analog Input 1 and Analog Input 2 of the 10-bit AD converter.

Analog Input 1 and Analog Input 2 are connected to the AIN0 and AIN5 pins of the microcontroller, respectively. With the AD input switching switches (SW1/SW2), "input from voltage value divided by VR1/VR2" and "external input" can be switched. The maximum input voltage to the AD converter is VDD.

This voltmeter has the four main modes:

- Standard voltmeter mode

- Voltage level monitor mode

- Voltage change monitor mode

- Voltage level compare mode

Analog Input 1 and Analog Input 2 can be selected in the standard mode and the voltage change monitor mode, respectively.

In the AD converter, the reference voltage is 0 to 5V, and the input voltage is sampled as shown in the following equation:

AD conversion value[bit] =  $10[bit] \times Input voltage [V]/5[V]$

Each analog input gets a sampling value per 0.1[ms] and a mean value is calculated after a certain times. Then processing is executed.

Values measured in each mode can be displayed on LCD. They can also be transmitted with "F4Key" input by using infrared LED. While data is transmitted, Key input is suspended. The infrared transmit data format will be shown in the description of each mode.

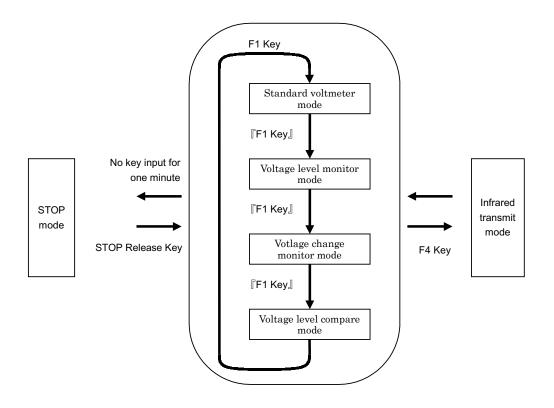

In this voltmeter, if no key operation is made for more than 1 minute, the power-saving mode is entered to suspend AD conversion, key operation, and LCD display. Only by pressing "STOP Release Key" can the power-saving mode be released to return to normal processing.

- Some infrared transmit data may cause other home appliance to malfunction. Please check before using this voltmeter.

- This voltmeter uses VDD input voltage (5V) as a reference voltage of AD conversion (VAREF). Note therefore that there may be a difference between an actual voltage and displayed voltage due to VDD input voltage.

## 5.1.2 Mode Transition Diagram

Figure 5.1.1 shows the transition of voltmeter modes.

Figure 5.1.1 Mode Transition Diagram

#### 5.1.3 Detailed Description of Each Mode of Voltmeter

#### 5.1.3.1 Voltmeter Mode

In this mode, a voltage from the specified analog input is measured and displayed on LCD.

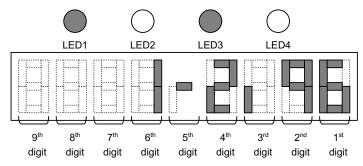

#### LED/LCD display

Only LED1 is "ON" and LED 2 to LED 4 are "OFF".

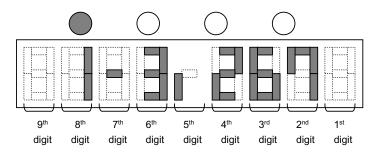

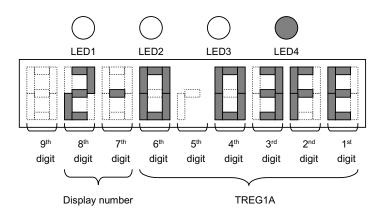

The 8<sup>th</sup> digit on LCD displays the analog input number currently selected. The 6<sup>th</sup> digit displays the first digit of a voltage measurement value, which is followed by up to the third decimal place.

In the initial state, Analog Input 1 is selected for analog input.

Figure 5.1.2 shows an example of LED/LCD display with Analog Input 1 and a voltage measurement value of 3.267[V].

Figure 5.1.2 Example of Display in Voltmeter Mode

#### Key operation

"F1 Key" input ends the voltmeter mode and the mode changes to the voltage level monitor mode.

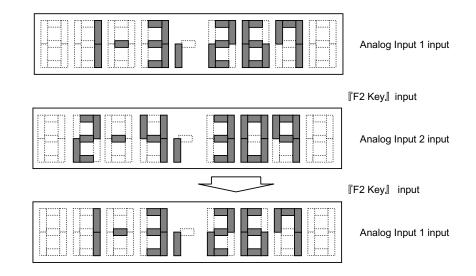

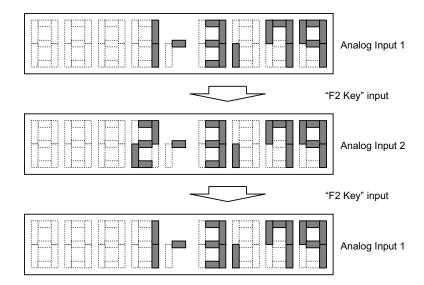

"F2 Key" input can be used to switch between Analog Input 1 and Analog Input 2. Switching updates the 8th digit on LCD and it displays the number of analog input currently used.

"F4 Key" input can be used to transmit the analog input number currently selected and a 10-bit AD measurement value by using infrared LED. For the transmit format, see "5.1.4 Infrared Transmit Format".

Figure 5.1.3 shows an example of display when "F2 Key" input is made.

Figure 5.1.3 Example of Switching Input in Voltmeter Mode

#### 5.1.3.2 Voltage Level Monitor Mode

In this mode, measurement values from analog input are monitored. When the value gets lower than the voltage monitor level, a buzzer sounds and LED 2 blinks as a warning.

#### LED/LCD display

LED2 is "ON" and LED 3 and LED 4 are "OFF".

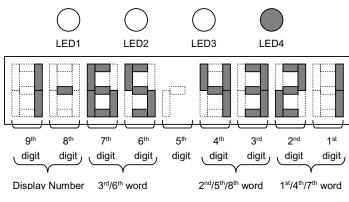

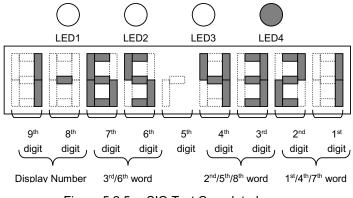

The 9<sup>th</sup> digit on LCD displays the first digit of the voltage monitor level, which is followed by up to the second decimal place. The 4<sup>th</sup> digit displays the first digit of a voltage measurement value, which is followed by up to the second decimal place. In the voltage level monitor mode, the analog input number is fixed to Analog Input 1.

Upon power-up and reset, the voltage monitor level is cleared to 0.00[V].

Figure 5.1.4 shows an example of LED/LCD display when the voltage monitor level is 2.13[V] and the voltage measurement value is 3.47[V].

Figure 5.1.4 Example of Display in Voltage Level Monitor Mode

#### Key operation

"F1 Key" input ends the voltage monitor mode and the mode changes to the voltage change monitor mode. At this time, the voltage monitor level that has been set is maintained.

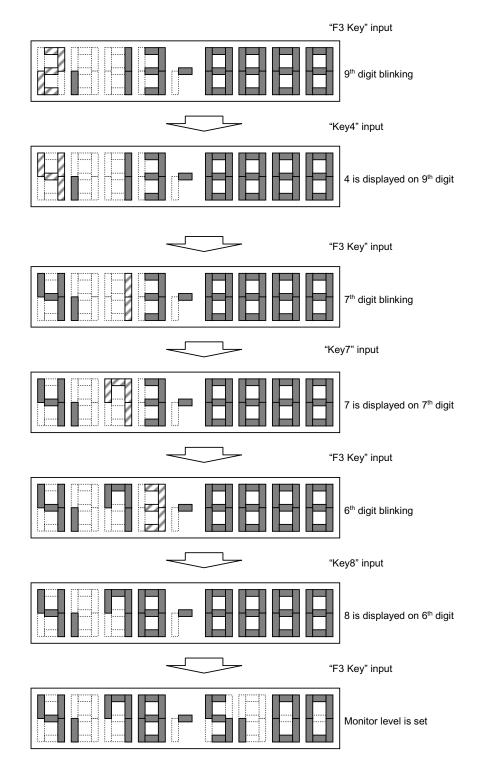

"F3 Key" input is used to enter the monitor level setting state. When this state is entered, monitoring of voltage level is stopped and the 9th digit on LCD starts blinking. The 4th to 1st digits that normally display a voltage measurement value are all lit during the monitor level setting state. When one of the keys from "Key0" to "Key9" is pressed while LCD is blinking ( "Key0 – Key5" while the 9th digit is blinking), the number of pressed key is input to the blinking digit and is temporarily set and displayed as the monitor level.

The voltage monitor level can be set to 0.00 to 5.00.

Once in the monitor level setting state, by further pressing "F3Key", the position of blinking digit moves from the 9th to the lower digits so that the 7th and 6th digits can be set. Note that when "5" is input to the 9th digit, "0" is automatically set to both the 7th and 6th digits.

When "F3 Key" is input while the 6th digit is blinking or "F3 Key" is input after "5" is input to while the 9th digit is blinking, LCD stops blinking and the values set to the 9th to 6th digits are fixed as the monitor level. The state then goes back to the voltage level monitor state.

The voltage monitor level is not fixed until "F3 Key" is input on the 6th digit or "F3 Key" is input after "5" is set to the 9<sup>th</sup> digit. Therefore, if "F1Key" is pressed to enter the voltage change monitor mode while the monitor level setting is performed, the monitor level before change is saved.

"F4 Key" input can be used to transmit a current voltage monitor level and a 10-bit A/D measurement value from Analog Input 1 by using infrared LED. For the transmit format, see "5.1.4 Infrared Transmit Format".

Figure 5.1.5 shows an example for setting the monitor level by "F3 Key" input.

Figure 5.1.5 Example of Setting Monitor Level

#### 5.1.3.3 Voltage Change Monitor Mode

In this mode, changes in the voltage measurement value from analog input are measured. If there is a change of more than fixed amount, a warming is issued.

In the voltage change monitor mode, the voltage AD value of the last sampling is always held. This value is compared with the new sampling value and if a difference is 0.04[V] or more, a buzzer sounds and LED3 blinks as a warning.

#### LED/LCD display

LED1 and LED3 are "ON" and LED2 and LED 4 are "OFF".

The 6<sup>th</sup> digit on LCD displays the analog input number currently selected. The 4<sup>th</sup> digit displays the first digit of a voltage measurement value from analog input, which is followed by up to the second decimal place.

Figure 5.1.6 shows an example of LED/LCD display with Analog Input 1 and a voltage measurement value of 2.96[V].

Figure 5.1.6 Example of Display in Voltage Change Monitor Mode

#### Key operation

"F1 Key" input ends the voltage change monitor mode and the mode changes to the voltage level compare mode.

"F2 Key" input can be used to switch between Analog Input 1 and Analog Input 2. Switching updates the 8the digit on LCD and it displays the number of analog input currently used.

"F4 Key" input can be used to transmit the analog input number currently selected and a 10-bit AD measurement value by using infrared LED. For the transmit format, see "5.1.4 Infrared Transmit Format".

Figure 5.1.7 shows an example of "F2 Key" input.

Figure 5.1.7 Example of Switching Input in Voltage Change Monitor Mode

#### 5.1.3.4 Voltage Level Compare Mode

In this mode, a voltage from Analog Input 1 and Analog Input 2 are measured. When measurement values of both inputs are the same, a buzzer sounds and LED4 blinks.

#### LED/LCD display

In the voltage level compare mode, LED1 and LED4 are "ON" and LED 2 and LED3 are "OFF".

The 9th digit on LCD displays the first digit of a measurement value of Analog Input 1, which is followed by up to the second decimal place.

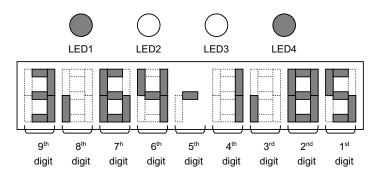

Figure 5.1.8 shows an example of LEC/LCD display when Analog Input 1 is 3.64[V] and Analog Input 2 is 1.85[V].

Figure 5.1.8 Example of Display in Voltage Level Compare Mode

#### Key operation

"F4 Key" input can be used to transmit 10-bit AD measurement values of Analog Input 1 and Analog Input 2 by using infrared LED. For the transmit format, see "5.1.4 Infrared Transmit Format".

"F1 Key" input ends the voltage level compare mode and the mode changes to the voltmeter mode.

#### 5.1.3.5 Power-Saving Mode

This voltmeter enters the power-saving mode when no key operation is made for about one minute. The power-saving mode suspends AD conversion, key input, and LCD/LED display. In this mode, only "STOP Release Key" input is accepted. By pressing "STOP Release Key", the voltmeter is restored to the previous Voltmeter mode and processing is continued.

#### 5.1.4 Infrared Transmit Format

#### 5.1.4.1 Basic Format of Header and Data Sections

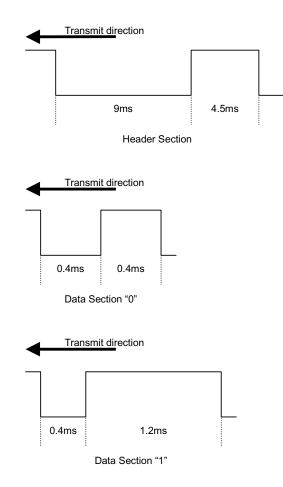

Figure 5.1.9 shows the basic format of transmit header and transmit data.

In transmitting, the transmit header is firstly transmitted. Then, 6-byte data (3byte data + 3-byte inverted data) is transmitted according to the infrared transmit data format of each Voltmeter mode.

#### 5.1.4.2 Common Rules of Infrared Transmit Data Format

- Measurement data is transmitted from the upper bit.

- Every1-byte data transmitted is followed by its inverted value. This method enables the receiving end to check if there is any data error.

- "1" is transmitted as a reserved bit.

- 10-bit AD measurement values are transmitted in the original format before being converted to volt units.

#### 5.1.4.3 Infrared Transmit Data Format in Voltmeter Mode

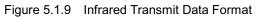

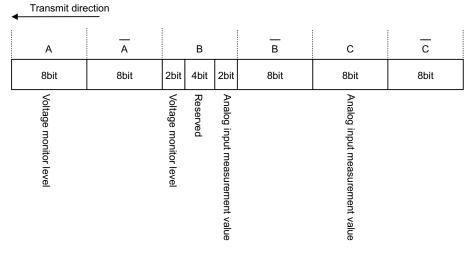

Figure 5.1.10 shows the infrared transmit data format in the voltmeter mode.

Figure 5.1.10 Infrared Transmit Format in Voltmeter Mode

For the analog input number, "001" is transmitted for Analog Input 1 and "010" is transmitted for Analog Input 2.

#### 5.1.4.4 Infrared Transmit Data Format in Voltage Level Monitor Mode

Figure 5.1.11 shows the infrared transmit data format in the voltage level monitor mode.

Figure 5.1.11 Infrared Transmit Format in Voltage Level Monitor Mode

For the voltage monitor level, the voltage value that is input at monitor level setting is transmitted after being converted to a 10-bit value. Conversion is performed by dividing the voltage value by 1024 with a reference voltage of 0 to 5V.

The voltage monitor level and measurement data are both transmitted from the upper bit.

#### 5.1.4.5 Infrared Transmit Data Format in Voltage Change Monitor Mode

Figure 5.1.12 shows the infrared transmit data format in the voltage change monitor mode.

Figure 5.1.12 Infrared Transmit Format in Voltage Change Monitor Mode

For the analog input number, "001" is transmitted for Analog Input 1 and "010" is transmitted for Analog Input 2.

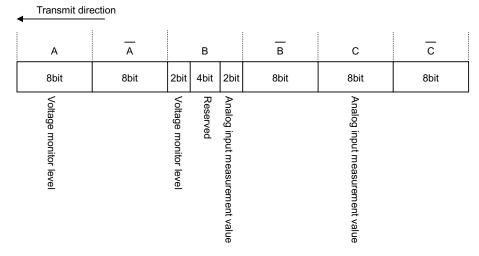

#### 5.1.4.6 Infrared Transmit Data Format in Voltage Level Compare Mode

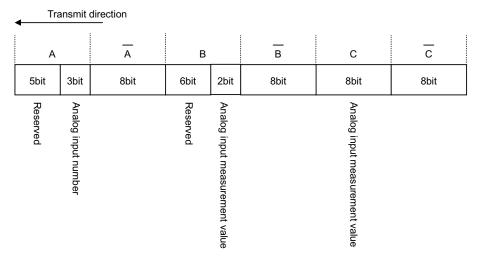

Figure 5.1.13 shows the infrared transmit data format in the voltage change compare mode.

Transmit direction

| А                                | Ā    |                                  | В        |                                  | B    | С                                | c    |

|----------------------------------|------|----------------------------------|----------|----------------------------------|------|----------------------------------|------|

| 8bit                             | 8bit | 2bit                             | 4bit     | 2bit                             | 8bit | 8bit                             | 8bit |

| Analog Input 1 measurement value |      | Analog Input 1 measurement value | Reserved | Analog Input 2 measurement value |      | Analog Input 2 measurement value |      |

Figure 5.1.13 Infrared Transmit Data Format in Voltage Level Compare Mode

#### 5.2 Test Mode

#### 5.2.1 Overview

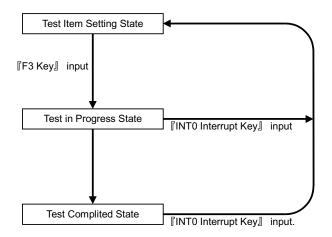

#### 5.2.1.1 Operation State in Test Mode

In Test mode, the three types of state are available: "test item setting state", "test in progress state", and "test completed state". The current state of Test mode is displayed by LED.

#### 5.2.1.2 Description of LED Display in Test Mode

LED display indicates the Test mode state in the following manner:

- LED1 off = Test mode

- LED2 on = Test item setting state

- LED3 on = Test in progress state

- LED4 on = Test completed state

Note that the  $2^{nd}$  to  $4^{th}$  digits are all "ON" when the interrupt cycle is shorter than the interrupt processing time and interrupts are continuously generated in the timer counter test, etc. This enables interrupt cycle errors to be detected.

#### 5.2.1.3 LCD Display in Test Mode

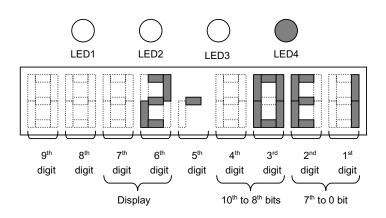

Figure 5.2.1 shows the initial display in Test mode.

Figure 5.2.1 External View of Test Mode

The  $6^{\rm th}$  and  $7^{\rm th}$  digits on LCD display the test number currently selected.

The  $4^{\text{th}}$  digit displays the mode number which shows the operating mode of the selected test.

Table 5.2.1 on the next page shows the test numbers and the test details for each mode number.

Displayed on the 1<sup>st</sup> and 2<sup>nd</sup> digits is the setting number for test execution, which enables the register values to be selected and set from predetermined settings when the test specified by the test and mode numbers is executed.

| Test No | Mode No | Des                | cription of Test          | Output Pin                                                  | Input Pin                                              |

|---------|---------|--------------------|---------------------------|-------------------------------------------------------------|--------------------------------------------------------|

| 0       | 0       | TBT test           | st Time Base Timer COMMON |                                                             |                                                        |

| 4       | 0       |                    | Interrupt request         | COMMON                                                      |                                                        |

| 1 1     |         | WDT test           | Reset output              | RESET                                                       | _                                                      |

| 2       | 0       | DVO test           | DVO                       | DVO                                                         |                                                        |

|         | 0       |                    | 18bit timer               | COMMON                                                      | _                                                      |

| 0       | 1       | TOLL               | 18bit event counter       | COMMON                                                      | ECIN                                                   |

| 3       | 2       | TC1 test           | Pulse width measurement   | COMMON, LCD display                                         | ECIN                                                   |

|         | 3       |                    | Frequency measurement     | COMMON, LCD display                                         | ECIN, ECNT                                             |

|         | 0       |                    | 8bit timer                | COMMON                                                      | _                                                      |

|         | 1       | TOOL               | 8bit event counter        | COMMON                                                      | TC3                                                    |

| 4       | 2       | TC3 test           | 8bit PDO                  | COMMON, TC3                                                 | _                                                      |

|         | 3       |                    | 8bit PWM                  | COMMON, TC3                                                 | _                                                      |

|         | 0       |                    | 8bit timer                | COMMON                                                      | _                                                      |

| r       | 1       |                    | 8bit event counter        | COMMON                                                      | TC4                                                    |

| 5       | 2       | TC4 test           | 8bit PDO                  | COMMON, TC4                                                 | _                                                      |

|         | 3       |                    | 8bit PWM                  | COMMON, TC4                                                 | _                                                      |

|         | 0       |                    | 16bit timer               | COMMON                                                      | _                                                      |

| 0       | 1       |                    | 16bit event counter       | COMMON                                                      | TC3                                                    |

| 6       | 2       | TC3 + 4 test       | 16bit PWM                 | COMMON,TC4                                                  | _                                                      |

|         | 3       |                    | 16bit PPG                 | COMMON,TC4                                                  | _                                                      |

| 7       | 0       | TC5 test           | 8bit timer                | COMMON                                                      | _                                                      |

|         | 0       |                    | 8bit timer                | COMMON                                                      | _                                                      |

| 0       | 1       | TOOL               | 8bit event counter        | COMMON                                                      | TC6                                                    |

| 8       | 2       | TC6 test           | 8bit PDO                  | COMMON, TC6                                                 | _                                                      |

|         | 3       |                    | 8bit PWM                  | COMMON,TC6                                                  | _                                                      |

|         | 0       |                    | 16bit timer               | COMMON                                                      | _                                                      |

| 9       | 1       | TC5 + 6 test       | 16bit PWM                 | COMMON, TC6                                                 | _                                                      |

|         | 2       |                    | 16bit PPG                 | COMMON,TC6                                                  | _                                                      |

| 10      | 0       |                    | Тх                        | TxD, LCD display                                            | _                                                      |

| 10      | 1       | UART test          | Rx                        | LCD display                                                 | RxD                                                    |

|         | 0       |                    | SIO Tx                    | SO, SCK, LCD display                                        | SCK                                                    |

| 11      | 1       | SIO test           | SIO Rx                    | SCK, LCD display                                            | SI, SCK                                                |

|         | 2       |                    | SIO TxRx                  | SO, SCK, LCD display                                        | SI, SCK                                                |

| 10      | 0       |                    | Single mode               | COMMON, LCD display                                         | AIN0                                                   |

| 12      | 1       | ADC test           | Repeat mode               | COMMON, LCD display                                         | AIN0                                                   |

| 13      | 0       | LCD test           | LCD operation check test  | LCD display                                                 |                                                        |

| 14      | 0       | Continuous<br>test | Continuous test           | COMMON, DVO, TC3,<br>TC4, TC6, TxD, SO, SCK,<br>LCD display | ECIN, ECNT,<br>TC3, TC4, TC6,<br>RxD, SCK, SI,<br>AIN0 |

Table 5.2.1 Description of Tests

#### 5.2.1.4 Key Input in Test Mode

In Test mode, "F1 Key" input is used to select the test number. Each time "F1 Key" is pressed, the test number on the  $6^{th}$  and  $7^{th}$  digits is incremented. The display number reaches 14, then it returns to 0.

"F2 Key" input is used to select the mode number. The mode number is selected on the  $4^{\rm th}$  digit in the same manner as the test number and each test number has its own range of numbers to choose from.

The setting number can be assigned for 16 settings (0 to 15) according to the combination of test number and mode number. The setting number can be set by using "Key 0 to Key F" and the specified number (0 to 15) is displayed on the  $1^{st}$  and  $2^{nd}$  digits on LCD.

"F3 Key" input sets each register value according to the selected test details and executes an operation test. When it is necessary to display register values to check operation results as in the case of pulse width measurement, frequency measurement, and serial transmit/receive, the test completed state is entered after each measurement or serial transmit/receive is completed. At this time, data is displayed on LCD so that operation can be checked.

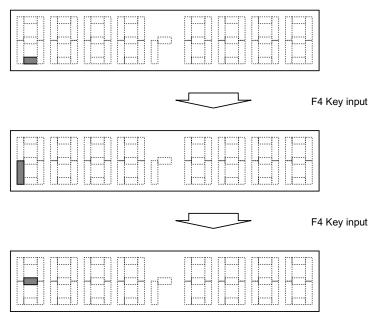

For tests that include the test completed state, data displayed on LCD can be switched with "F4 Key" input after test completion.

While tests are executed, only "INTO Interrupt Key" is accepted. When "INTO Interrupt Key" is pressed during test execution, the test is immediately stopped and the test item setting state is entered.

When "INTO Interrupt Key" is pressed for more than 3 seconds, 'IntO Err' is displayed on LCD and the test is stopped. In this case, press "Reset Key" and execute the test again.

#### 5.2.2 Transition of Test Mode State

Figure 5.2.2 Transition of Test Mode State

#### 5.2.3 Specifications of Test Mode Test Items

#### 5.2.3.1 Time Base Timer Test [Test number: 0]

In the Time Base Timer (TBT) test, TBT interrupts are generated and COMMON pin outputs are inverted in interrupt processing. By monitoring the COMMON pin, the interrupt cycle can be measured to check whether the TBT is operating according to the setting.

The test number of TBT test is 0. No mode selection is performed.

In the TBT test, each setting pattern specifies the operating mode (SYSCR2, NORMAL/SLOW), high-/low-frequency selection (DV7CK), and TBT interrupt frequency (TBTCR).

Table 5.2.2 shows the register set values for each setting pattern.

| Setting No | Operating Mode (SYSCR2) | Selected Output Frequency<br>(TBTCR) | TBT Interrupt Cycle |

|------------|-------------------------|--------------------------------------|---------------------|

| 0          |                         | (0x08)                               | 1.047s              |

| 1          |                         | (0x09)                               | 262ms               |

| 2          |                         | (0x0A)                               | 8.19ms              |

| 3          |                         | (0x0B)                               | 2.04ms              |

| 4          |                         | (0x0C)                               | 1.023ms             |

| 5          | NORMAL (0xC0)           | (0x0D)                               | 512µs               |

| 6          |                         | (0x0E)                               | 256µs               |

| 7          |                         | (0x0F)                               | 64ms                |

| 8          |                         | (0x1A)                               | 7.81ms              |

| 9          |                         | (0x1B)                               | 1.95ms              |

| 10         |                         | (0x1C)                               | 977µs               |

| 11         |                         | (0x1D)                               | 488µs               |

| 12         |                         | (0x1E)                               | 244µs               |

| 13         |                         | (0x1F)                               | 64µs                |

| 14         |                         | (0x08)                               | 1s                  |

| 15         | SLOW (0xE0)             | (0x09)                               | 250ms               |

Table 5.2.2 Register Set Values for TBT Test

#### 5.2.3.2 Watchdog Timer Test [Test number: 1]

The watchdog timer (WDT) test has the following two modes:

• WDT Output-Interrupt Request Mode

WDT interrupts are generated and the COMMON pin is inverted in WDT interrupt processing. By monitoring the COMMON pin, the WDT interrupt cycle is measured to check whether the WDT is operating according to the setting.

WDT Output- Reset Output Mode After the WDT test is started, not clearing the WDT counter activates the WDT and resets internal hardware. By measuring the time between test start and reset operation, whether operation is performed according to the setting can be checked.

The test number of WDT test is 1. Table 5.2.3 shows the mode numbers and setting items of WDT test.

| Mode Name         | Mode No | Setting Item                                                                 |  |  |  |  |  |

|-------------------|---------|------------------------------------------------------------------------------|--|--|--|--|--|

| Interrupt request | 0       | Operating mode, High-/Low-frequency selection, Watchdog timer detecting time |  |  |  |  |  |

| Reset output      | 1       | Operating mode, High-/Low-frequency selection, Watchdog timer detecting time |  |  |  |  |  |

Table 5.2.3

Modes and Setting Items of WDT Test

Table 5.2.4 and Table 5.2.5 show the register set values for each setting pattern.

High-/Low-Frequency Selection WDT Setting No Operating Mode (SYSCR2) (WDTCR1) (TBTCR) Reset Cycle 4.194s 0 (0x08) 1 (0x0A) 1.049s fc (0x00) 2 (0x0C) 262ms 3 (0x0E) 65.5ms NORMAL(0xC0) 4 (0x08) 4s 5 (0x0A) 1s fs (0x10) 6 (0x0C) 250ms 7 (0x0E) 62.5ms 8 (0x08) 4s 9 (0x0A) 1s SLOW(0xE0) fc (0x00) 10 (0x0C) 250ms 11 (0x0E) 62.5ms 12 For 13 NORMAL fc (0x00) continuous (0x0A) 1.049s (0xC0) 14 test 15

| Table 5 2 4 | Register Set Values for WDT Reset Output |

|-------------|------------------------------------------|

| Table 5.2.5 | Register Set Values for WDT | Interrupt Request |

|-------------|-----------------------------|-------------------|

|-------------|-----------------------------|-------------------|

| Setting No | Operating Mode (SYSCR2)   |                             | High-/Low-Frequency Selection<br>(TBTCR) | (WDTCR1) | WDT<br>Reset Cycle |

|------------|---------------------------|-----------------------------|------------------------------------------|----------|--------------------|

| 0          |                           |                             |                                          | (0x08)   | 4.194s             |

| 1          |                           |                             | fa (0:00)                                | (0x0A)   | 1.049s             |

| 2          |                           |                             | fc (0x00)                                | (0x0C)   | 262ms              |

| 3          | NODM                      |                             |                                          | (0x0E)   | 65.5ms             |

| 4          | NORIN                     | AL(0xC0)                    |                                          | (0x08)   | 4s                 |

| 5          |                           |                             | fa (0:10)                                | (0x0A)   | 1s                 |

| 6          |                           |                             | fs (0x10)                                | (0x0C)   | 250ms              |

| 7          |                           |                             |                                          | (0x0E)   | 62.5ms             |

| 8          |                           |                             |                                          | (0x08)   | 4s                 |

| 9          |                           |                             | f= (0:00)                                | (0x0A)   | 1s                 |

| 10         | 3101                      | V(0xE0)                     | fc (0x00)                                | (0x0C)   | 250ms              |

| 11         |                           |                             |                                          | (0x0E)   | 62.5ms             |

| 12         |                           |                             |                                          |          |                    |

| 13         | For<br>continuous<br>test | continuous NORMAL<br>(0xC0) | ( (0, 00)                                | (0x0A)   | 1.040              |

| 14         |                           |                             | fc (0x00)                                |          | 1.049s             |

| 15         |                           |                             |                                          |          |                    |

5.2.3.3 Divider Output Test [Test number: 2]

In the divider output test, duty-50% pulses are output from the DVO pin. By monitoring the DVO pin, whether the divider output is operating according to the setting can be checked.

The test number of divider output test is 2. No mode selection is performed.

In this test, each setting pattern specifies the operating mode (SYSCR2, NORMAL/SLOW), high-/low-frequency selection (DV7CK), and DVO output frequency.

Table 5.2.6 shows the register set values for the divider output test.

| Setting No | Operating Mode (SYSCR2) |                                                 | Output Frequency Selection<br>(TBTCR) | Divider Output Frequency/Cycle |

|------------|-------------------------|-------------------------------------------------|---------------------------------------|--------------------------------|

| 0          |                         |                                                 | 976.5Hz (0x80)                        | 1.024ms                        |

| 1          |                         |                                                 | 1.953KHz (0xA0)                       | 512µs                          |

| 2          |                         |                                                 | 3.9065KHz (0xC0)                      | 256µs                          |

| 3          | NODA                    |                                                 | 7.8125KHz (0xE0)                      | 128µs                          |

| 4          | NORMAL(0xC0)            |                                                 | 1.024KHz (0x90)                       | 977µs                          |

| 5          |                         |                                                 | 2.048KHz (0xB0)                       | 488µs                          |

| 6          |                         |                                                 | 4.096KHz (0xD0)                       | 244µs                          |

| 7          |                         |                                                 | 8.192KHz (0xF0)                       | 122µs                          |

| 8          |                         |                                                 | 1.024KHz (0x80)                       | 977µs                          |

| 9          |                         |                                                 | 2.048KHz (0xA0)                       | 488µs                          |

| 10         | SLO                     | N(0xE0)                                         | 4.096KHz (0xC0)                       | 244µs                          |

| 11         |                         |                                                 | 8.192KHz (0xE0)                       | 122µs                          |

| 12         |                         |                                                 |                                       |                                |

| 13         | -                       | For<br>continuous<br>test (0xC0) 976.5Hz (0x80) |                                       | 4.004                          |

| 14         | continuous<br>test      |                                                 | 976.5HZ (UX80)                        | 1.024ms                        |

| 15         | 1001                    |                                                 |                                       |                                |

Table 5.2.6 Register Set Values for Divider Output Test

#### 5.2.3.4 TC1 Test [Test number: 3]

The timer counter 1 (TC1) test has the following four modes:

• 18-bit Timer Mode

By activating the 18-bit timer, TC1 interrupts are generated and COMMON pin outputs are inverted in TC1 interrupt processing. By monitoring the COMMON pin, the TC1 interrupt cycle can be measured to check whether the TC1 18-bit timer counter is operating according to the setting.

• Event Counter Mode

By using the counter by input pulses from the ECIN pin, TC1 interrupts are generated and COMMON pin outputs are inverted in TC1 interrupt processing. By monitoring the COMMON pin, the TC1 interrupt cycle can be measured to check whether the TC1 event counter is operating according to the setting.

• Pulse Width Measurement Mode

By input pulse width measurements from the ECIN pin, TC1 interrupts are generated and COMMON pin outputs are inverted in TC1 interrupt processing. By displaying on LCD the pulse width measurement value of pulses input from the ECIN pin, whether TC1 pulse width measurement is operating according to the setting can be checked.

• Frequency Measurement Mode

By input pulse frequency measurements from the ECIN pin, TC1 interrupts are generated and COMMON pin outputs are inverted in TC1 interrupt processing. By displaying on LCD the frequency measurement value of pulses input from the ECIN pin, whether TC1 frequency measurement is operating according to the setting can be checked.

The test number of TC1 test is 3. Table 5.2.7 shows the mode numbers and setting items of TC1 test.

| Mode Name                      | Mode No | Setting Item                                                                                                                                                                                                              |

|--------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TC1 18bit Timer                | 0       | Operating mode, High-/Low-frequency selection, TREG1A、TC1 source clock                                                                                                                                                    |

| TC1 Event Counter              | 1       | Operating mode, TREG1A                                                                                                                                                                                                    |

| TC1 Pulse Width<br>Measurement | 2       | Operating mode, High-/Low-frequency selection,<br>Window gate pulse interrupt edge                                                                                                                                        |

| TC1 Frequency<br>Measurement   | 3       | High-/Low-frequency selection, ECIN edge selection, Window gate pulse selection,<br>Window gate pulse interrupt edge, Internal window gate pulse set register, TC6<br>operation clock, TC6 operating mode, TTREG6, PWREG6 |

Table 5.2.7 Modes and Setting Items of TC1 Test

In the TC1 pulse width measurement and TC1 frequency measurement modes, the test completed state is entered after measurement is performed three times. LCD displays the TREG1A value, which is the measurement result.

The display number (1 to 3) indicates the number of measurements and selected by "F4 Key" input.

If an overflow error occurs during a test, the  $6^{th}$  digit displays "E". In this case, change the set value and perform measurement again.

By pressing "INTO Interrupt Key" in the test completed state, the state returns to the test item setting state.

Figure 5.2.3 TC1 Test Result Display

| Setting No | Operating Mode (SYSCR2) | High-/Low-Frequency<br>Selection (TBTCR) | Frequency<br>Selection<br>(TC1CR1) | (TREG1A)   | TC1 Interrupt Cycle |

|------------|-------------------------|------------------------------------------|------------------------------------|------------|---------------------|

| 0          |                         |                                          |                                    | (0x0001F4) | 500µs               |

| 1          |                         |                                          | fa/03(0xE0)                        | (0x00C350) | 50ms                |

| 2          |                         |                                          | fc/23(0x58)                        | (0x0186A0) | 100ms               |

| 3          |                         |                                          |                                    | (0x00000A) | 10μs(*)             |

| 4          |                         | fc (0x00)                                | fc/27(0x54)                        | (0x000019) | 400µs               |

| 5          |                         |                                          | fc/211(0x50)                       | (0x000028) | 10.24ms             |

| 6          | NORMAL(0xC0)            |                                          | fc/213(0x4C)                       | (0x00000A) | 10.24ms             |

| 7          |                         |                                          | fc/223(0x48)                       | (0x00002)  | 2.096s              |

| 8          |                         |                                          | fs(0x44)                           | (0x000020) | 976µs               |

| 9          |                         |                                          | fs/2 <sup>3</sup> (0x50)           | (0x000029) | 10ms                |

| 10         |                         | fs (0x10)                                | fs/25(0x4C)                        | (0x000033) | 49.776ms            |

| 11         |                         |                                          | fs/215(0x48)                       | (0x00002)  | 2s                  |

| 12         |                         |                                          | fs/2 <sup>3</sup> (0x50)           | (0x000052) | 20ms                |

| 13         |                         | $f_{0}(0,0)$                             | fs/2 <sup>5</sup> (0x4C)           | (0x000033) | 49.776ms            |

| 14         | SLOW(0xE0)              | fc (0x00)                                | fs/215(0x48)                       | (0x000002) | 2s                  |

| 15         |                         |                                          | fc(0x40)                           | (0x027100) | 20ms                |

| Table 5.2.8 to Table 5.2.11 sh | now the register set values for | each setting pattern. |

|--------------------------------|---------------------------------|-----------------------|

|--------------------------------|---------------------------------|-----------------------|

Table 5.2.8

Register Set Values for TC1 18-bit Timer

\* In this setting, because the interrupt cycle is shorter than the interrupt processing time, interrupts are not generated according to the setting.

| Setting No | Operating Mode (SYSCR2) | (TC1CR1) | (TREG1A)   |

|------------|-------------------------|----------|------------|

| 0          |                         |          | (0x03FFFF) |

| 1          |                         |          | (0x010000) |

| 2          |                         |          | (0x00FFFF) |

| 3          |                         |          | (0x00F000) |

| 4          | NORMAL(0xC0)            |          | (0x000F00) |

| 5          | SLOW(0xE0)              |          | (0x0000FF) |

| 6          |                         | (0x5C)   | (0x00000F) |

| 7          |                         |          | (0x000001) |

| 8          |                         |          | (0x03FFFF) |

| 9          |                         |          | (0x010000) |

| 10         |                         |          | (0x00FFFF) |

| 11         |                         |          | (0x00F000) |

| 12         |                         |          | (0x000F00) |

| 13         |                         |          | (0x0000FF) |

| 14         |                         |          | (0x00000F) |

| 15         |                         |          | (0x00001)  |

Table 5.2.9 Register Set Values for TC1 18-bit Event Counter

| Setting No | Operating Mode<br>(SYSCR2) | High-/Low-Frequency<br>Selection (TBTCR) | Frequency<br>Selection<br>(TC1CR1) | Interrupt Edge<br>(TC1CR2) | Internal Clock |

|------------|----------------------------|------------------------------------------|------------------------------------|----------------------------|----------------|

| 0          |                            |                                          | fo(0)(42)                          | rising edge (0x00)         |                |

| 1          |                            |                                          | fc(0x42)                           | both edges (0x10)          | 8MHz           |

| 2          |                            |                                          | fs(0x46)                           |                            | 32.768KHz      |

| 3          |                            | fa (0::00)                               | fc/2 <sup>23</sup> (0x4A)          |                            | 0.953Hz        |

| 4          |                            | fc (0x00)                                | fc/2 <sup>13</sup> (0x4E)          | falling edge (0x00)        | 976.56Hz       |

| 5          |                            |                                          | fc/211(0x52)                       |                            | 3.906KHz       |

| 6          | NORMAL(0xC0)               |                                          | fc/2 <sup>7</sup> (0x56)           |                            | 62.5KHz        |

| 7          |                            |                                          | fc/23(0x5A)                        |                            | 4.096KHz       |

| 8          |                            |                                          | fs/2 <sup>15</sup> (0x4A)          |                            | 1Hz            |

| 9          |                            | fs (0x00)                                | IS/2 (0X4A)                        | both edges (0x10)          | IIIZ           |

| 10         |                            | IS (0x00)                                | fs/2 <sup>5</sup> (0x4E)           |                            | 1.024KHz       |

| 11         |                            |                                          | fs/2 <sup>3</sup> (0x52)           | falling edge (0x00)        | 4.096KHz       |

| 12         |                            |                                          | f= (215(0+4A)                      |                            | 411-           |

| 13         |                            | fo (0)(00)                               | fs/2 <sup>15</sup> (0x4A)          | both edges (0x10)          | 1Hz            |

| 14         | SLOW(0xE0)                 | fc (0x00)                                | fs/2 <sup>5</sup> (0x4E)           | falling adge (0x00)        | 1.024KHz       |

| 15         |                            |                                          | fs/2 <sup>3</sup> (0x52)           | falling edge (0x00)        | 4.096KHz       |

Table 5.2.10 Register Settings for TC1 Pulse Width Measurement

| Table 5.2.11 | Register Settings for TO | C1 Frequency Measurement |

|--------------|--------------------------|--------------------------|

|--------------|--------------------------|--------------------------|

| O attine a Nia | Operating Mode | (TO40D4) |        | (T      | C1CR2)  |                     |          |         |          |          |

|----------------|----------------|----------|--------|---------|---------|---------------------|----------|---------|----------|----------|

| Setting No     | (SYSCR2)       | (TC1CR1) |        | SEG     | SEGDG   | WGP                 | (TREG1B) | (TC6CR) | (TTREG6) | (PWREG6) |

| 0              |                |          | (0x00) | falling | falling |                     |          |         |          |          |

| 1              |                |          | (0x90) | both    | both    | FONT                | (0,,00)  |         |          |          |

| 2              |                |          | (0x10) | falling | both    | ECNT                | (0x00)   |         |          | (0x00)   |

| 3              |                |          | (0x80) | both    | falling |                     |          | (0,,00) | (0,00)   |          |

| 4              |                |          | (0x20) | falling | falling | 2 <sup>12</sup> /fc |          | (0x00)  | (0x00)   |          |

| 5              |                |          | (0xB0) | both    | both    | 2 <sup>12</sup> /fc |          |         |          |          |

| 6              | NORMAL(0xC0)   |          | (0x34) | falling | both    | 2 <sup>13</sup> /fc | (0xFF)   |         |          |          |

| 7              |                |          | (0xA8) | both    | falling | 2 <sup>14</sup> /fc |          |         |          |          |

| 8              |                | (0x5F)   | (0x22) | falling | falling |                     |          | (0x09)  | (0xFF)   | (0x00)   |

| 9              |                |          | (0xD2) | both    | both    | TOP                 | (0,,00)  | (0xB9)  | (0xFF)   | (0x00)   |

| 10             |                |          | (0x52) | falling | both    | TC6                 | (0x00)   | (0x19)  | (0xFF)   | (0x00)   |

| 11             |                |          | (0xC2) | both    | falling |                     |          | (0x2A)  | (0x00)   | (0xFF)   |

| 12             |                |          | (0x00) | falling | falling | FONT                | (0x00)   | (0x00)  |          |          |

| 13             |                |          | (0x90) | both    | both    | ECNT                | (0xFF)   | (0x00)  | (0x00)   | (0x00)   |

| 14             | SLOW(0xE0)     |          | (0x34) | falling | both    | 2⁵/fs               | (0xFF)   | (0x00)  |          |          |

| 15             |                |          | (0xC2) | both    | falling | TC6                 | (0x00)   | (0x09)  | (0xFF)   | (0x00)   |

#### 5.2.3.5 TC3 Test [Test number: 4]

The TC3 test has the following four modes:

• 8-bit Timer Mode

The 8-bit timer is activated and COMMON pin outputs are inverted in TC3 interrupt processing. By monitoring the COMMON pin, the TC3 interrupt cycle can be measured to check whether the TC3 8-bit timer mode is operating according to the setting.

• 8-bit Event Counter Mode

By using the counter by input pulses from the ECIN pin, TC3 interrupts are generated and COMMON pin outputs are inverted in TC3 interrupt processing. By monitoring the COMMON pin, the TC3 interrupt cycle can be measured to check whether the TC3 event counter mode is operating according to the setting.

• 8-bit PDO Mode

8-bit PDO is output to the TC3 pin and COMMON pin outputs are inverted in TC3 interrupt processing. By monitoring signals output from the COMMON and TC3 pins, whether the TC3 interrupt cycle and PDO output are operating according to the setting can be checked.

• 8-bit PWM Mode

8-bit PWM is output to the TC3 pin and COMMON pin outputs are inverted in TC3 interrupt processing. By monitoring signals output from the COMMON and C3 pins, whether the TC3 interrupt cycle and PWM output are operating according to the setting can be checked.

The test number of TC3 test is 4. Table 5.2.12 shows the mode numbers and setting items of TC3 test.

| Mode Name          | Mode No | Setting Item                                                                 |  |  |  |

|--------------------|---------|------------------------------------------------------------------------------|--|--|--|

| 8bit Timer         | 0       | Operating mode, High-/Low-frequency selection, TTREG3, TC3 source clock      |  |  |  |

| 8bit Event Counter | 1       | TTREG3                                                                       |  |  |  |

| 8bit PDO           | 2       | Operating mode, High-/Low-frequency selection, TTREG3, TC3 source clock, TTF |  |  |  |

| 8bit PWM           | 3       | Operating mode, High-/Low-frequency selection, TTREG3, TC3 source clock, TTF |  |  |  |

| Table 5.2.12 | Modes and Setting Items of TC3 Test |

|--------------|-------------------------------------|

|--------------|-------------------------------------|

Table 5.2.13 to Table 5.2.16 show the register set values for each setting pattern.

| Setting Item | Operating Mode<br>(SYSCR2) | High-/Low-Frequency<br>Selection (TBTCR)    | Frequency<br>Selection<br>(TC3CR) | (TTREG3) | TC3 Interrupt Cycle |

|--------------|----------------------------|---------------------------------------------|-----------------------------------|----------|---------------------|

| 0            |                            |                                             | f= (0 <sup>11</sup> (0, 00)       | (0x04)   | 1.024ms             |

| 1            |                            |                                             | fc/2 <sup>11</sup> (0x08)         | (0xC8)   | 51.2ms              |

| 2            |                            |                                             | fo/27(0+10)                       | (0x19)   | 400µs               |

| 3            |                            |                                             | fc/2 <sup>7</sup> (0x18)          | (0x3F)   | 1.0008ms            |

| 4            |                            | fc (0x00)                                   | fo/25(0x28)                       | (0x0E)   | 60µs                |

| 5            |                            |                                             | fc/2 <sup>5</sup> (0x28)          | (0x32)   | 200µs               |

| 6            |                            |                                             | fc/2 <sup>3</sup> (0x38)          | (0x01)   | 1µs(*)              |

| 7            | NORMAL(0xC0)               |                                             |                                   | (0x05)   | 5µs(*)              |

| 8            |                            |                                             |                                   | (0x32)   | 50µs                |

| 9            |                            |                                             |                                   | (0x64)   | 100µs               |

| 10           |                            |                                             |                                   | (0xC8)   | 200µs               |

| 11           |                            |                                             |                                   | (0xFF)   | 255µs               |

| 12           |                            | ( (0, 10) ( ( <sup>0</sup> <sup>3</sup> /0) | fo/2 <sup>3</sup> (0x08)          | (0x01)   | 244µs               |

| 13           |                            | fs (0x10)                                   | fs/2 <sup>3</sup> (0x08)          | (0x29)   | 10.004ms            |

| 14           |                            | fo (0x00)                                   | fo/03(0v08)                       | (0x01)   | 244µs(*)            |

| 15           | SLOW(0xE0)                 | fc (0x00)                                   | fs/2 <sup>3</sup> (0x08)          | (0x29)   | 10.004ms            |

Table 5.2.13

Register Setting for TC3 8-bit Timer

\* In these settings, because the interrupt cycle is shorter than the interrupt processing time, interrupts are not generated according to the setting.

| Setting No | Operating Mode (SYSCR2) | (TC3CR) | (TTREG3) |

|------------|-------------------------|---------|----------|

| 0          |                         |         | (0xFF)   |

| 1          |                         |         | (0x7F)   |

| 2          |                         |         | (0x3F)   |

| 3          |                         |         | (0x1F)   |

| 4          | NORMAL(0xC0)            |         | (0x0F)   |

| 5          |                         |         | (0x08)   |

| 6          |                         | (0x78)  | (0x02)   |

| 7          |                         |         | (0x01)   |

| 8          | SLOW(0xE0)              |         | (0xFF)   |

| 9          |                         |         | (0x7F)   |

| 10         |                         |         | (0x3F)   |

| 11         |                         |         | (0x1F)   |

| 12         |                         |         | (0x0F)   |

| 13         |                         |         | (0x08)   |

| 14         |                         |         | (0x02)   |

| 15         |                         |         | (0x01)   |

Table 5.2.14

Register Settings for TC3 8-bit Event Counter

| Table 5.2.15 | Register Settings  | for TC3 8-bit PDO Mode |

|--------------|--------------------|------------------------|

| 10010 0.2.10 | riogiotor ootanigo |                        |

| Setting No | Operating Mode | High-/Low-Frequency         | Frequency  | Selection (1      | C3CR)             | (TTREG3) | Inversion |

|------------|----------------|-----------------------------|------------|-------------------|-------------------|----------|-----------|

| Octaing No | (SYSCR2)       | Selection (TBTCR) Frequency |            | Frequency         | TFF               | (TINE00) | interval  |

| 0          |                |                             | (0x09)     |                   | CLR               | (0+04)   | 1.00.4    |

| 1          |                |                             | (0x89)     |                   | SET               | (0x04)   | 1.024ms   |

| 2          |                |                             |            | fc/211            |                   | (0x28)   | 10.24ms   |

| 3          |                |                             | (0x09)     |                   |                   | (0x64)   | 25.6ms    |

| 4          |                | fc (0x00)                   |            |                   |                   | (0xC8)   | 51.2ms    |

| 5          |                |                             | (0x19)     | fc/27             | CLR               | (0x3F)   | 1ms       |

| 6          | NORMAL(0xC0)   |                             |            |                   |                   | (0xFA)   | 4ms       |

| 7          |                |                             | (0x29)     | fc/2⁵             |                   | (0x05)   | 20µs(*)   |

| 8          |                |                             |            | 10/2*             | ULK               | (0x32)   | 200µs     |