#### **FEATURES**

High speed 800 MHz, -3 dB bandwidth 790 V/µs slew rate 8 ns settling time to 0.5% Wide supply range: 5 V to 12 V Low power: 6 mA 0.1 dB flatness: 125 MHz Differential gain: 0.02% Differential phase: 0.02° Low voltage offset: 3.5 mV (typ) High output current: 25 mA Power down

#### **APPLICATIONS**

Consumer video Professional video Broadband video ADC buffers Active filters

#### **GENERAL DESCRIPTION**

The ADA4860-1 is a low cost, high speed, current feedback op amp that provides excellent overall performance. The 800 MHz, -3 dB bandwidth, and 790 V/µs slew rate make this amplifier well suited for many high speed applications. With its combination of low price, excellent differential gain (0.02%), differential phase (0.02°), and 0.1 dB flatness out to 125 MHz, this amplifier is ideal for both consumer and professional video applications.

The ADA4860-1 is designed to operate on supply voltages as low as +5 V and up to  $\pm 5$  V using only 6 mA of supply current. To further reduce power consumption, the amplifier is equipped with a power-down feature that lowers the supply current to 0.25 mA.

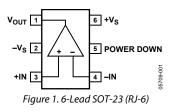

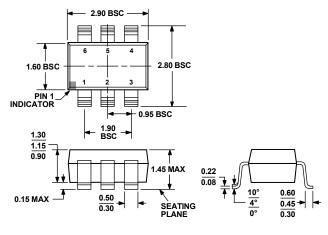

The ADA4860-1 is available in a 6-lead SOT-23 package and is designed to work over the extended temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

# High Speed, Low Cost, Op Amp ADA4860-1

#### PIN CONFIGURATION

Rev. PrC

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

## TABLE OF CONTENTS

| Features 1                          |

|-------------------------------------|

| Applications1                       |

| Pin Configuration1                  |

| General Description1                |

| Revision History                    |

| Specifications                      |

| Absolute Maximum Ratings5           |

| Thermal Resistance                  |

| ESD Caution                         |

| Typical Performance Characteristics |

| Applications14                      |

#### **REVISION HISTORY**

1/06—Revision PrC: Preliminary Version

| Power Supp    | ly Bypassing           | 14 |

|---------------|------------------------|----|

| Gain Config   | gurations              | 14 |

| Driving Cap   | pacitive Loads         | 15 |

| Power Down    | n Pin                  | 15 |

| Video Amp     | lifier                 | 15 |

| Optimizing    | Flatness and Bandwidth | 16 |

| Layout        |                        | 17 |

| Outline Dimer | nsions                 | 18 |

| Ordering G    | uide                   | 18 |

## **SPECIFICATIONS**

$V_{S} = +5 V (@T_{A} = 25^{\circ}C, G = +2, R_{L} = 150 \Omega, C_{L} = 4 pF, unless otherwise noted). For G = +2, R_{F} = R_{G} = 499 \Omega and for G = +1, R_{F} = 550 \Omega.$

| Parameter                                       | Conditions                                       | Min | Тур         | Max | Unit     |

|-------------------------------------------------|--------------------------------------------------|-----|-------------|-----|----------|

| DYNAMIC PERFORMANCE                             |                                                  |     |             |     |          |

| –3 dB Bandwidth                                 | $V_0 = 0.2 V p - p$                              |     | 460         |     | MHz      |

|                                                 | $V_0 = 2 V p - p$                                |     | 165         |     | MHz      |

|                                                 | $V_{0} = 0.2 \text{ V p-p}, R_{L} = 75 \Omega$   |     | 430         |     | MHz      |

|                                                 | $G = +1, V_0 = 0.2 V p-p$                        |     | 650         |     | MHz      |

| Bandwidth for 0.1 dB Flatness                   | $V_0 = 2 V p - p$                                |     | 58          |     | MHz      |

|                                                 | $V_0 = 2 V p - p, R_L = 75 \Omega$               |     | 45          |     | MHz      |

| +Slew Rate (Rising Edge)                        | $V_0 = 2 V p - p$                                |     | 695         |     | V/µs     |

| –Slew Rate (Falling Edge)                       | $V_0 = 2 V p - p$                                |     | 560         |     | V/µs     |

| Settling Time to 0.5%                           | $V_0 = 2 V \text{ step}$                         |     | 8           |     | ns       |

| NOISE/DISTORTION PERFORMANCE                    |                                                  |     |             |     |          |

| Harmonic Distortion HD2/HD3                     | $f_{c} = 1 \text{ MHz}, V_{o} = 2 \text{ V p-p}$ |     | -90/-102    |     | dBc      |

| Harmonic Distortion HD2/HD3                     | $f_c = 5 \text{ MHz}, V_0 = 2 \text{ V p-p}$     |     | -70/-76     |     | dBc      |

| Input Voltage Noise                             | f = 100  kHz                                     |     | 4.0         |     | nV/√Hz   |

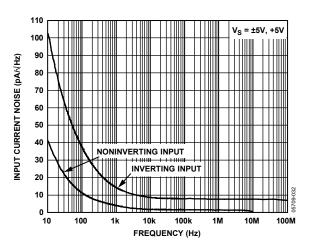

| Input Current Noise                             | f = 100  kHz, +IN/-IN                            |     | 1.5/7.7     |     | pA/√Hz   |

| Differential Gain                               | $R_{\rm L} = 150 \Omega$                         |     | 0.02        |     | %        |

| Differential Phase                              | $R_{L} = 150 \Omega$ $R_{L} = 150 \Omega$        |     | 0.02        |     | Degrees  |

| DC PERFORMANCE                                  | 11L - 150 12                                     |     | 0.05        |     | Degrees  |

| Input Offset Voltage                            |                                                  |     | -4.25       |     | mV       |

| +Input Bias Current                             |                                                  |     | -4.25       |     | μA       |

| –Input Bias Current                             |                                                  |     | +1.0        |     | μΑ<br>μΑ |

| -                                               |                                                  |     | +1.0<br>650 |     | μA<br>kΩ |

| Open-Loop Transresistance INPUT CHARACTERISTICS |                                                  |     | 050         |     | KL2      |

|                                                 | . 181                                            |     | 10          |     | MO       |

| Input Resistance                                | +IN                                              |     | 10          |     | MΩ       |

| la suit Casa aita a sa                          | -IN                                              |     | 85          |     | Ω        |

| Input Capacitance                               | +IN                                              |     | 1.5         |     | pF       |

| Input Common-Mode Voltage Range                 |                                                  |     | 1.2 to 3.7  |     | V        |

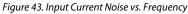

| Common-Mode Rejection Ratio                     | $V_{CM} = 2 V \text{ to } 3 V$                   |     | -56         |     | dB       |

| POWER DOWN PIN                                  |                                                  |     |             |     |          |

| Input Voltage                                   | Enabled                                          |     | 0.5         |     | V        |

|                                                 | Power down                                       |     | 1.8         |     | V        |

| Bias Current                                    | Enabled                                          |     | -200        |     | nA       |

|                                                 | Power down                                       |     | 60          |     | μΑ       |

| Turn-On Time                                    |                                                  |     | 200         |     | ns       |

| Turn-Off Time                                   |                                                  |     | 3.5         |     | μs       |

| OUTPUT CHARACTERISTICS                          |                                                  |     |             |     |          |

| Output Overdrive Recovery Time (Rise/Fall)      | $V_{IN} = +2.25 \text{ V to } -0.25 \text{ V}$   |     | 60/100      |     | ns       |

| Output Voltage Swing                            | $R_L = 75 \ \Omega$                              |     | 1.2 to 3.8  |     | V        |

|                                                 | $R_L = 150 \ \Omega$                             |     | 1 to 4      |     | V        |

|                                                 | $R_L = 1 \ k\Omega$                              |     | 0.8 to 4.2  |     | V        |

| Short-Circuit Current                           | Sinking and sourcing                             |     | 45          |     | mA       |

| POWER SUPPLY                                    |                                                  |     |             |     |          |

| Operating Range                                 |                                                  |     |             |     | V        |

| Total Quiescent Current                         | Enabled                                          |     | 5.2         |     | mA       |

| Quiescent Current                               | POWER DOWN pin = $+V_s$                          |     | 0.2         |     | mA       |

| Power Supply Rejection Ratio                    |                                                  |     |             |     |          |

| +PSR                                            | $+V_{s} = 4 V \text{ to } 6 V, -V_{s} = 0 V$     |     | -62         |     | dB       |

$V_{S}=\pm 5 \text{ V} (@ T_{A}=25^{\circ}\text{C}, G=+2, R_{L}=150 \Omega, C_{L}=4 \text{ pF}, \text{ unless otherwise noted}). For G=+2, R_{F}=R_{G}=499 \Omega \text{ and for } G=+1, R_{F}=550 \Omega.$

| Table 2. |

|----------|

|----------|

| Parameter                                  | Conditions                                        | Min Typ M    | ax Unit |

|--------------------------------------------|---------------------------------------------------|--------------|---------|

| DYNAMIC PERFORMANCE                        |                                                   |              |         |

| –3 dB Bandwidth                            | $V_0 = 0.2 V p - p$                               | 520          | MHz     |

|                                            | V <sub>0</sub> = 2 V p-p                          | 230          | MHz     |

|                                            | $V_{O} = 0.2 V p-p, R_{L} = 75 \Omega$            | 480          | MHz     |

|                                            | $G = +1, V_0 = 0.2 V p-p$                         | 800          | MHz     |

| Bandwidth for 0.1 dB Flatness              | $V_0 = 2 V p - p$                                 | 125          | MHz     |

|                                            | $V_0 = 2 V p - p, R_L = 75 \Omega$                | 70           | MHz     |

| +Slew Rate (Rising Edge)                   | $V_0 = 2 V p - p$                                 | 980          | V/µs    |

| –Slew Rate (Falling Edge)                  | $V_0 = 2 V p - p$                                 | 790          | V/μs    |

| Settling Time to 0.5%                      | $V_0 = 2 V \text{ step}$                          | 8            | ns      |

| NOISE/DISTORTION PERFORMANCE               | •                                                 |              |         |

| Harmonic Distortion HD2/HD3                | $f_{C} = 1 \text{ MHz}, V_{O} = 2 \text{ V } p-p$ | -90/-102     | dBc     |

| Harmonic Distortion HD2/HD3                | $f_c = 5 \text{ MHz}, V_0 = 2 \text{ V p-p}$      | -77/-94      | dBc     |

| Input Voltage Noise                        | f = 100  kHz                                      | 4.0          | nV/√Hz  |

| Input Current Noise                        | f = 100  kHz + IN / -IN                           | 1.5/7.7      | pA/√Hz  |

| Differential Gain                          | $R_{\rm L} = 150 \ \Omega$                        | 0.02         | %       |

| Differential Phase                         | $R_{\rm L} = 150 \ \Omega$                        | 0.02         | Degrees |

| DC PERFORMANCE                             | ML = 130 32                                       | 0.02         | Degrees |

| Input Offset Voltage                       |                                                   | -3.5         | mV      |

| +Input Bias Current                        |                                                   | -1.0         |         |

| –Input Bias Current                        |                                                   | +1.5         | μΑ      |

| -                                          |                                                   |              | μA      |

| Open-Loop Transresistance                  |                                                   | 700          | kΩ      |

|                                            |                                                   | 12           |         |

| Input Resistance                           | +IN                                               | 12           | MΩ      |

|                                            | -IN                                               | 90           | Ω       |

| Input Capacitance                          | +IN                                               | 1.5          | pF      |

| Input Common-Mode Voltage Range            |                                                   | -3.8 to +3.7 | V       |

| Common-Mode Rejection Ratio                | $V_{CM} = \pm 2 V$                                | -58          | dB      |

| POWER DOWN PIN                             |                                                   |              |         |

| Input Voltage                              | Enabled                                           | -4.4         | V       |

|                                            | Power down                                        | -3.2         | V       |

| Bias Current                               | Enabled                                           | -250         | nA      |

|                                            | Power down                                        | 130          | μA      |

| Turn-On Time                               |                                                   | 200          | ns      |

| Turn-Off Time                              |                                                   | 3.5          | μs      |

| OUTPUT CHARACTERISTICS                     |                                                   |              |         |

| Output Overdrive Recovery Time (Rise/Fall) | $V_{IN} = \pm 3.0 V$                              | 45/90        | ns      |

| Output Voltage Swing                       | $R_L = 75 \Omega$                                 | ±2           | V       |

|                                            | $R_L = 150 \ \Omega$                              | ±3.1         | V       |

|                                            | $R_L = 1 \ k\Omega$                               | ±4.1         | V       |

| Short-Circuit Current                      | Sinking and sourcing                              | 85           | mA      |

| POWER SUPPLY                               |                                                   |              |         |

| Operating Range                            |                                                   |              | V       |

| Total Quiescent Current                    | Enabled                                           | 6            | mA      |

| Quiescent Current                          | POWER DOWN pin = +Vs                              | 0.25         | mA      |

| Power Supply Rejection Ratio               |                                                   |              |         |

| +PSR                                       | $+V_{s} = +4 V \text{ to } +6 V, -V_{s} = -5 V$   | -64          | dB      |

| –PSR                                       | $+V_{s} = +5 V, -V_{s} = -4 V \text{ to } -6 V,$  | -61          | dB      |

| . 51                                       | $POWER DOWN pin = -V_s$                           |              |         |

#### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| Parameter                   | Rating                          |

|-----------------------------|---------------------------------|

| Supply Voltage              | 12.6 V                          |

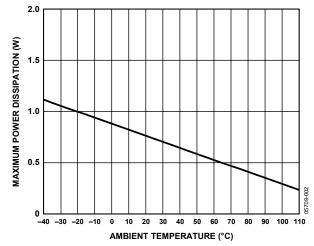

| Power Dissipation           | See Figure 3                    |

| Common-Mode Input Voltage   | $-V_{s} + 1 V to + V_{s} - 1 V$ |

| Differential Input Voltage  | ±Vs                             |

| Storage Temperature Range   | –65°C to +125°C                 |

| Operating Temperature Range | -40°C to +105°C                 |

| Lead Temperature            | JEDEC J-STD-20                  |

| Junction Temperature        | 150°C                           |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for device soldered in circuit board for surface-mount packages.

Table 4. Thermal Resistance

| Package Type  | θ <sub>JA</sub> | Unit |

|---------------|-----------------|------|

| 6-lead SOT-23 | 170             | °C/W |

#### **Maximum Power Dissipation**

The maximum safe power dissipation for the ADA4860-1 is limited by the associated rise in junction temperature ( $T_1$ ) on the die. At approximately 150°C, which is the glass transition temperature, the plastic changes its properties. Even temporarily exceeding this temperature limit can change the stresses that the package exerts on the die, permanently shifting the parametric performance of the amplifiers. Exceeding a junction temperature of 150°C for an extended period can result in changes in silicon devices, potentially causing degradation or loss of functionality. The power dissipated in the package  $(P_D)$  for a sine wave and a resistor load is the total power consumed from the supply minus the load power.

$P_D$  = Total Power Consumed – Load Power

$$P_D = \left( V_{SUPPLY \, VOLTAGE} \times I_{SUPPLY \, CURRENT} \right) - \frac{V_{OUT}^2}{R_s}$$

RMS output voltages should be considered.

Airflow increases heat dissipation, effectively reducing  $\theta_{JA}$ . In addition, more metal directly in contact with the package leads and through holes under the device reduces  $\theta_{JA}$ .

Figure 3 shows the maximum safe power dissipation in the package vs. the ambient temperature for the 6-lead SOT-23 (170°C/W) on a JEDEC standard 4-layer board.  $\theta_{JA}$  values are approximations.

Figure 3. Maximum Power Dissipation vs. Temperature for a 4-Layer Board

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$R_L = 150 \Omega$  and  $C_L = 4 pF$ , unless otherwise noted.

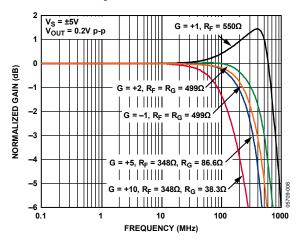

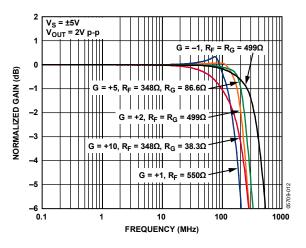

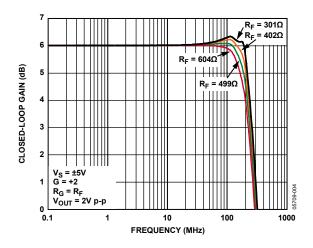

Figure 4. Small Signal Frequency Response for Various Gains

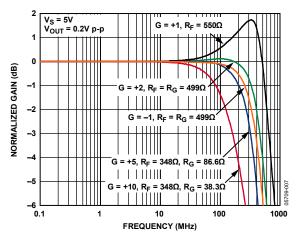

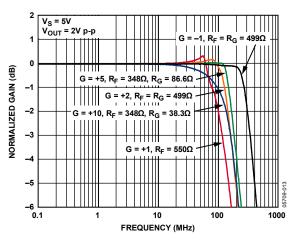

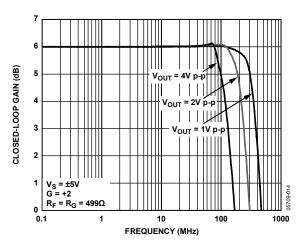

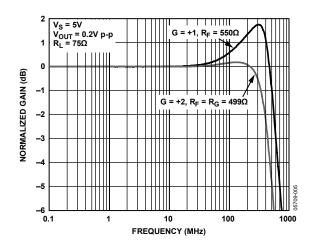

Figure 5. Large Signal Frequency Response for Various Gains

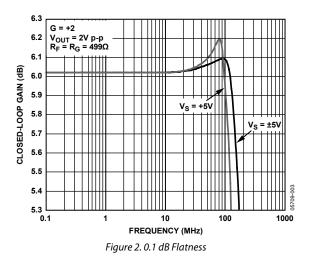

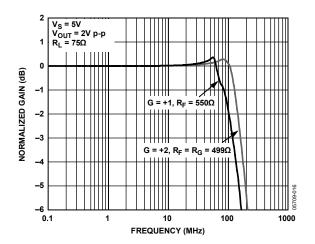

Figure 6. Large Signal 0.1 dB Flatness

Figure 7. Small Signal Frequency Response for Various Gains

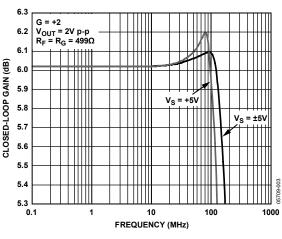

Figure 8. Large Signal Frequency Response for Various Supplies

Figure 9. Large Signal Frequency Response for Various Output Levels

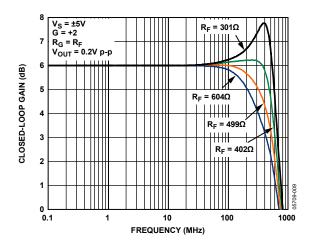

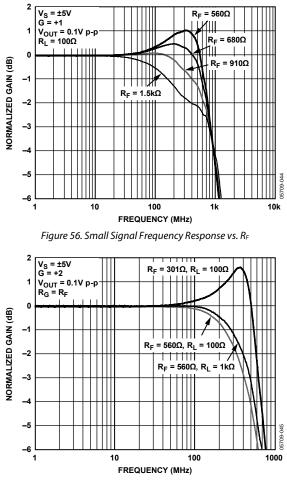

Figure 10. Small Signal Frequency Response vs. R<sub>F</sub>

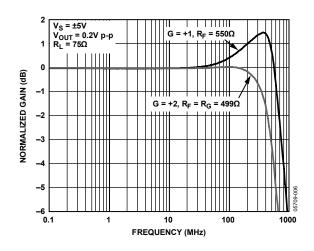

Figure 11. Small Signal Frequency Response for Various Gains

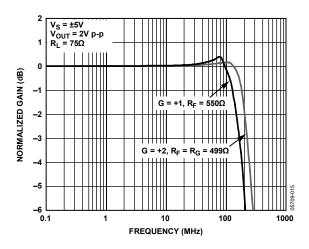

Figure 12. Large Signal Frequency Response for Various Gains

Figure 13. Large Signal Frequency Response vs. R<sub>F</sub>

Figure 14. Small Signal Frequency Response for Various Gains

Figure 15. Large Signal Frequency Response for Various Gains

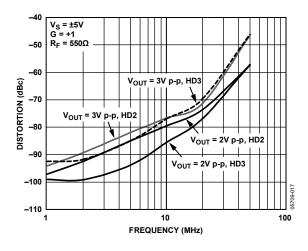

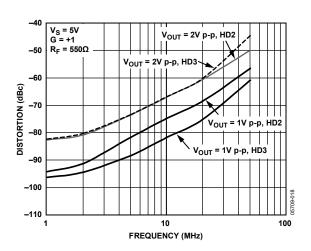

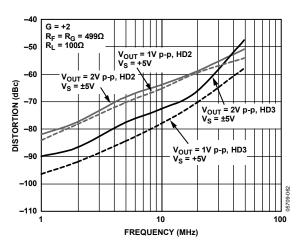

Figure 16. Harmonic Distortion vs. Frequency

Figure 17. Harmonic Distortion vs. Frequency

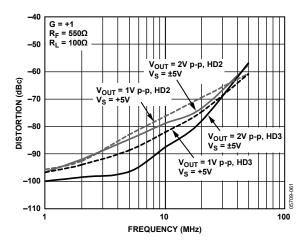

Figure 18. Harmonic Distortion vs. Frequency for Various Supplies

## **Preliminary Technical Data**

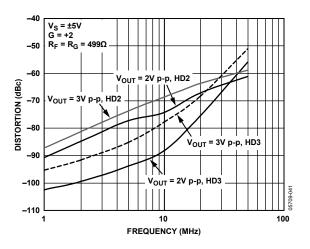

Figure 19. Harmonic Distortion vs. Frequency

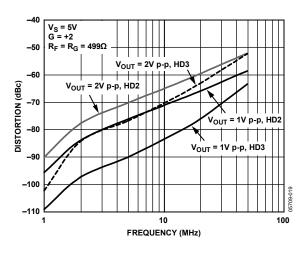

Figure 20. Harmonic Distortion vs. Frequency

Figure 21. Harmonic Distortion vs. Frequency for Various Supplies

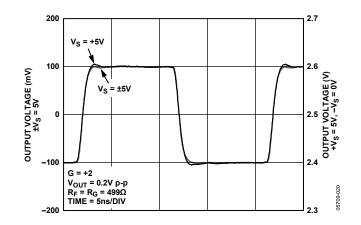

#### 200 2.7 ٧s = +5V 100 2.6 5.6 0UTPUT VOLTAGE (V) 5.2 4 V<sub>S</sub> = 5V, -V<sub>S</sub> = 0V OUTPUT VOLTAGE (mV) ±V<sub>S</sub> = 5V v<sub>s</sub> = ±5V 0 -100 2.4 G = +1 $V_{OUT} = 0.2V p-p$ $R_F = 550\Omega$ TIME = 5ns/DIV 05709-033 -200 2.3

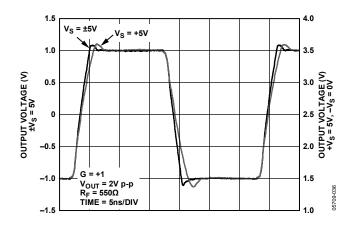

Figure 22. Small Signal Transient Response for Various Supplies

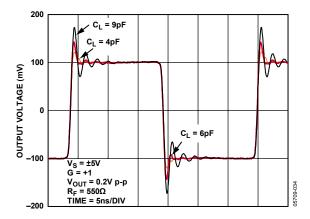

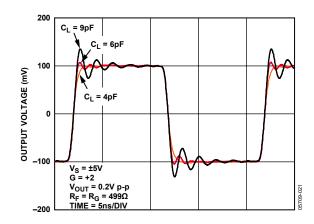

Figure 23. Small Signal Transient Response for Various Capacitor Loads

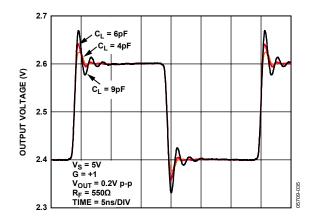

Figure 24. Small Signal Transient Response for Various Capacitor Loads

Figure 25. Small Signal Transient Response for Various Supplies

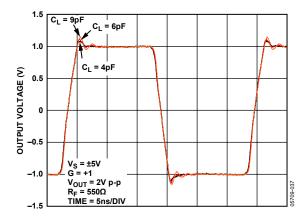

Figure 26. Small Signal Transient Response for Various Capacitor Loads

Figure 27. Small Signal Transient Response for Various Capacitor Loads

#### Rev. PrC | Page 9 of 20

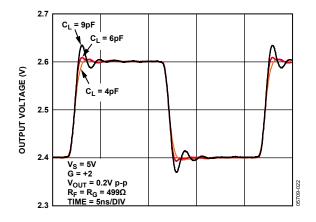

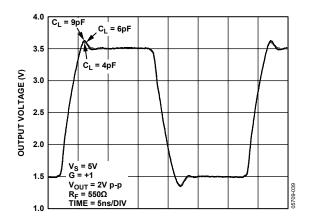

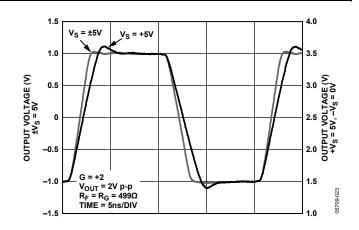

Figure 28. Large Signal Transient Response for Various Supplies

Figure 29. Large Signal Transient Response for Various Capacitor Loads

Figure 30. Large Signal Transient Response for Various Capacitor Loads

## Preliminary Technical Data

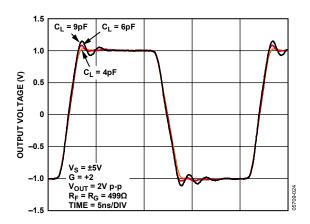

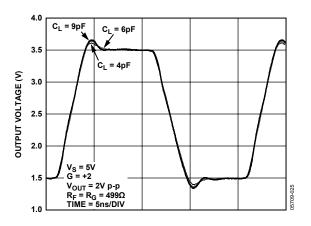

Figure 31. Large Signal Transient Response for Various Supplies

Figure 32. Large Signal Transient Response for Various Capacitor Loads

Figure 33. Large Signal Transient Response for Various Capacitor Loads

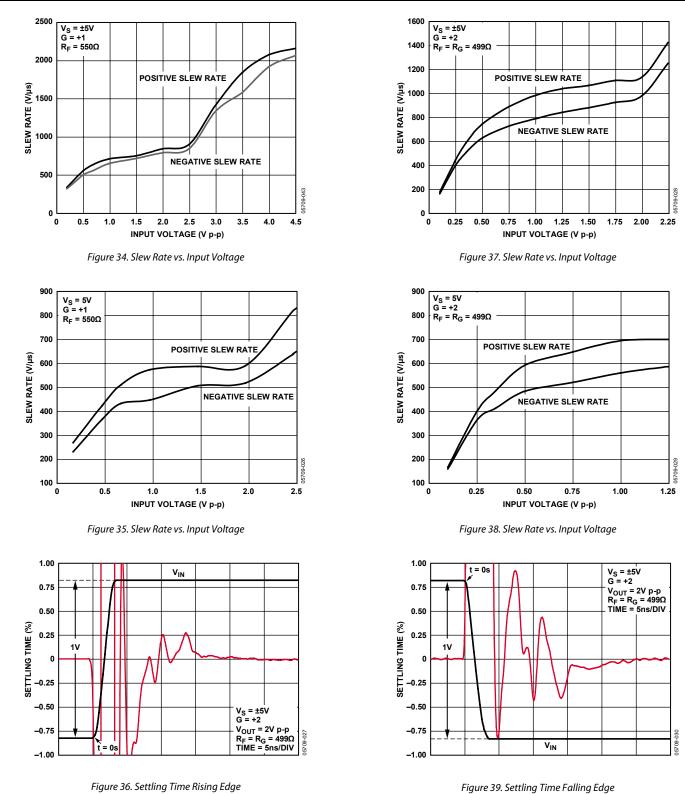

Figure 39. Settling Time Falling Edge

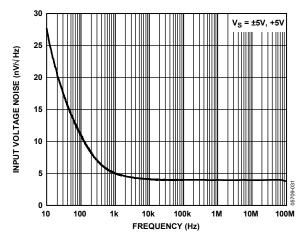

Figure 40. Input Voltage Noise vs. Frequency

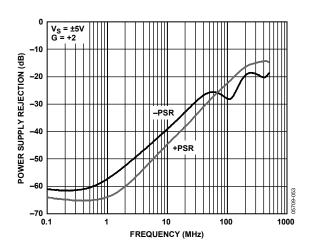

Figure 41. Power Supply Rejection vs. Frequency

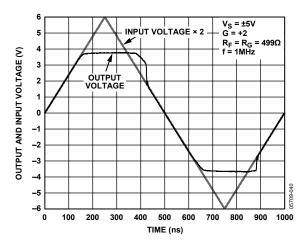

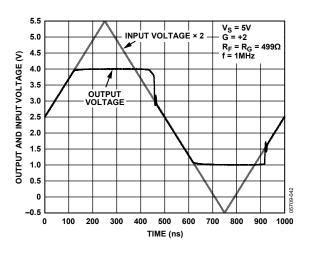

Figure 42. Output Overdrive Recovery

Figure 45. Output Overdrive Recovery

#### 1000 V<sub>S</sub> = ±5V G = +2 100 TRANSIMPEDANCE (kΩ) TRANSIMPEDANCE PHASE (Degrees) PH/ 10 90 1 135 0.54 05709-0.1 -180 0.1 1 10 100 1000 FREQUENCY (MHz)

Figure 46. Transimpedance and Phase vs. Frequency

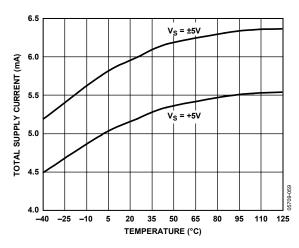

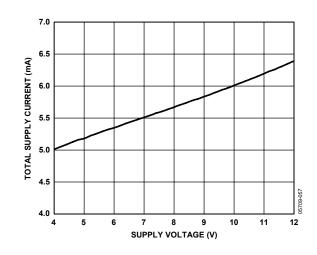

Figure 47. Supply Current at Various Supplies vs. Temperature

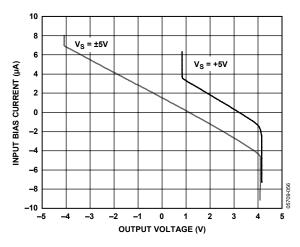

Figure 48. Inverting Input Bias Current vs. Output Voltage

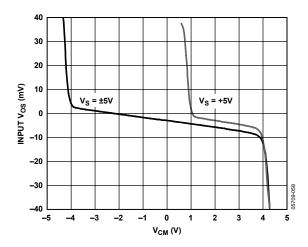

Figure 49. Input V<sub>os</sub> vs. Common-Mode Voltage

Figure 50. Supply Current vs. Supply Voltage

#### APPLICATIONS POWER SUPPLY BYPASSING

Attention must be paid to bypassing the power supply pins of the ADA4860-1. High quality capacitors with low equivalent series resistance (ESR), such as multilayer ceramic capacitors (MLCCs), should be used to minimize supply voltage ripple and power dissipation. A large, usually tantalum, 2.2  $\mu$ F to 47  $\mu$ F capacitor located in proximity to the ADA4860-1 is required to provide good decoupling for lower frequency signals. The actual value is determined by the circuit transient and frequency requirements. In addition, 0.1  $\mu$ F MLCC decoupling capacitors should be located as close to each of the power supply pins as is physically possible, no more than  $\frac{1}{3}$  inch away. The ground returns should terminate immediately into the ground plane. Locating the bypass capacitor return close to the load return minimizes ground loops and improves performance.

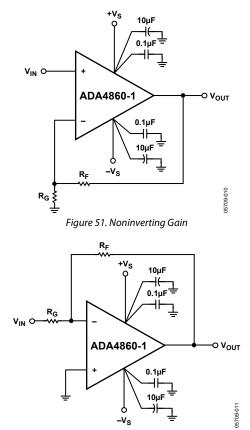

#### GAIN CONFIGURATIONS

The feedback resistor has a direct impact on the closed-loop bandwidth and stability of the current feedback op amp circuit. Reducing the resistance below the recommended value can make the amplifier response peak and even become unstable. Increasing the size of the feedback resistor reduces the closedloop bandwidth. Table 5 provides a convenient reference for quickly determining the feedback and gain set resistor values and bandwidth for common gain configurations.

| Gain | R <sub>F</sub> (Ω) | R <sub>G</sub> (Ω) | –3 dB<br>SS BW<br>(MHz) | –3 dB<br>LS BW<br>(MHz) | Large<br>Signal<br>0.1 dB<br>Flatness |

|------|--------------------|--------------------|-------------------------|-------------------------|---------------------------------------|

| +1   | 550                | N/A                | 800                     | 165                     | 40                                    |

| -1   | 499                | 499                | 400                     | 400                     | 80                                    |

| +2   | 499                | 499                | 520                     | 230                     | 125                                   |

| +5   | 348                | 86.6               | 335                     | 265                     | 100                                   |

| +10  | 348                | 38.3               | 165                     | 195                     | 28                                    |

$^1$  Conditions:  $V_S=\pm 5$  V,  $T_A=25^\circ C,$   $R_L=150$   $\Omega.$

Figure 51 and Figure 52 show the typical noninverting and inverting configurations and the recommended bypass capacitor values.

Figure 52. Inverting Gain

#### **DRIVING CAPACITIVE LOADS**

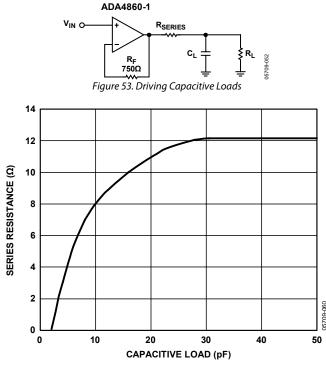

If driving loads with a capacitive component is desired, the best frequency response is obtained by the addition of a small series resistance, as shown in Figure 53. Figure 54 shows the optimum value for  $R_{\text{SERIES}}$  vs. capacitive load. The test was performed with a 50 MHz, 50% duty cycle pulse, with an amplitude of 200 mV p-p. The criteria for  $R_{\text{SERIES}}$  selection was based on maintaining approximately 1 dB of peaking in small signal frequency response. It is worth noting that the frequency response of the circuit can be dominated by the passive roll-off of  $R_{\text{SERIES}}$  and  $C_{\text{L}}$ .

Figure 54. Recommended R<sub>SERIES</sub> vs. Capacitive Load

#### **POWER DOWN PIN**

The ADA4860-1 is equipped with a power-down function. The POWER DOWN pin allows the user to reduce the quiescent supply current when the amplifier is not being used. The power-down threshold levels are derived from the voltage applied to the  $-V_S$  pin. When used in single-supply applications, this is especially useful with conventional logic levels. The amplifier is powered down when the voltage applied to the POWER DOWN pin is greater than  $(-V_S + 1 \text{ V})$ . The amplifier is enabled whenever the POWER DOWN pin is left open, or the voltage on the POWER DOWN pin is less than  $(-V_S + 1 \text{ V})$ . If the POWER DOWN pin is not used, it should be connected to the negative supply.

#### **VIDEO AMPLIFIER**

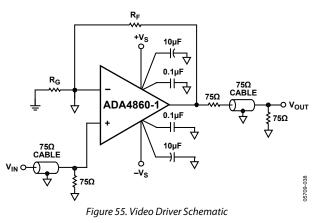

With low differential gain and phase errors and wide 0.1 dB flatness, the ADA4860-1 is an ideal solution for consumer and professional video applications. Figure 55 shows a typical video driver set for a noninverting gain of +2, where  $R_F = R_G = 499 \Omega$ . The video amplifier input is terminated into a shunt 75  $\Omega$  resistor. At the output, the amplifier has a series 75  $\Omega$  resistor for impedance matching to the video load.

#### **OPTIMIZING FLATNESS AND BANDWIDTH**

When using the ADA4860-1, the variety of circuit conditions and parasitics can affect peaking, gain flatness, and -3 dB bandwidth. This section discusses how the ADA4860-1 small signal responses can be dramatically altered with basic circuit changes and added stray capacitances.

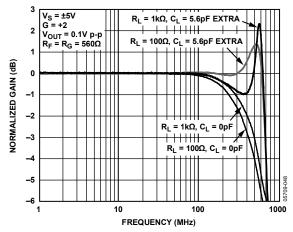

Particularly with low closed-loop gains, the feedback resistor ( $R_f$ ) effects peaking and gain flatness. However, with gain = +1, -3 dB bandwidth varies slightly, while gain = +2 has a much larger variation. For gain = +1, Figure 56 shows the effect that various feedback resistors have on frequency response. In Figure 56, peaking is wide ranging yet -3 dB bandwidth vary by only 6%. In this case, the user must pick what is desired: more peaking or flatter bandwidth. Figure 57 shows gain = +2 bandwidth and peaking variations vs.  $R_F$  vs.  $R_L$ . Bandwidth delta vs.  $R_L$  increase was approximately 17%. Also for Figure 57,  $R_L = 100 \Omega$ , the -3 dB bandwidth changed 49% as  $R_F$  was lowered with excessive compromises in peaking. For more gain = +2 bandwidth variations vs.  $R_F$ , see Figure 10 and Figure 13.

Figure 57. Small Signal Frequency Response vs. R<sub>F</sub> vs. R<sub>L</sub>

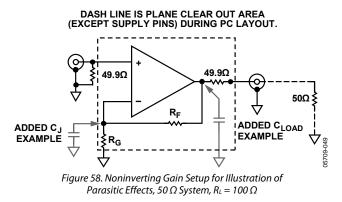

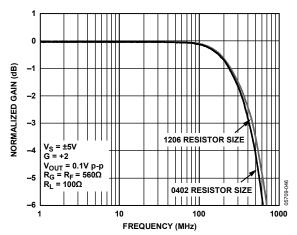

The impact of resistor case sizes was observed using the circuit drawn in Figure 58. The types and sizes chosen were 0402 case sized thin film and 1206 thick film. All other measurement conditions were kept constant except for the case size and resistor composition.

In Figure 59, a slight -3 dB bandwidth delta of approximately 10% can be seen going from a small-to-large case size. The increase in bandwidth with the larger 1206 case size is caused by an increase in parasitic capacitance across the chip resistor. This extra capacitance is known to extend amplifier frequency response. Therefore, while a variation in chip resistor case size causes small bandwidth shifts, this should not stifle the user's case size selections.

Figure 59. Small Signal Frequency Response vs. Resistor Size

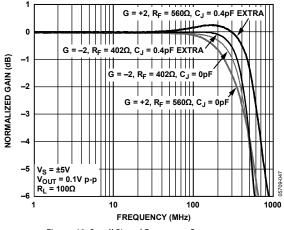

Initially, a small capacitor of 0.4 pF was added to the amplifier summing junction of two boards with equal and opposite gains of +2 and -2. The results are shown in Figure 60. In a second test, 5.6 pF of capacitance was added directly at the output of the gain = +2 amplifier. The results are shown in Figure 61.

Figure 60 reveals extra summing junction capacitance, which affects noninverting gain circuits vs. inverting gain. With gain = +2, the additional 0.4 pF of added capacitance created an extra 43% -3 dB bandwidth extension, plus some extra peaking. For gain = -2, a 5% increase in -3 dB bandwidth was created with an extra 0.4 pF on summing junction.

Extra output capacitive loading on the ADA4860-1 also causes bandwidth extensions, as seen in Figure 61. The effect on the gain = +2 circuit is more pronounced with lighter resistive loading (1 k $\Omega$ ). For pulse response behavior with added output capacitances, see Figure 23, Figure 24, Figure 26, Figure 27, Figure 29, Figure 30, Figure 32, and Figure 33.

Figure 60. Small Signal Frequency Response vs. Added Summing Junction Capacitance

Figure 61. Small Signal Frequency Response vs. Output Capacitive Load

Optimization of circuit performance is accomplished with signal amplitudes that are relevant to a specific application. For example, in video applications, the gain = +2 circuit can be optimized for output signal amplitudes of 2 V p-p. Minimizing ac peaking and obtaining highest frequency flatband characteristics should result in the best overall circuit performance.

#### LAYOUT

Careful attention to printed circuit board (PCB) layout prevents associated board parasitics from becoming problematic and affecting gain flatness and -3 dB bandwidth. In the printed circuit environment, parasitics around summing junction (inverting input) or output pins can alter pulse and frequency response. Parasitic capacitance can be unintentionally created on a PC board via two parallel metal planes with a small vertical separation (in FR4). To avoid parasitic problems near the summing junction signal lines connections between the feedback and gain resistors should be kept as short as possible to minimize the inductance and stray capacitance. For similar reasons, termination and load resistors should be located as close as possible to the respective inputs. Lastly, removing the ground plane on all layers from the area near and under the input and output pins reduces stray capacitance.

It is important to realize the impact of printed circuit board parasitics. The best performing current feedback amplifier circuit layouts mitigate stray board capacitances around the summing junction and outputs by isolating capacitive loads using low value output series resistors. For more information on high speed board layout, go to: www.analog.com and www.analog.com/library/analogDialogue/archives/39-09/layout.html.

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-178-AB Figure 62. 6-Lead Plastic Surface-Mount Package [SOT-23] (RJ-6) Dimensions shown in millimeters and (inches)

#### **ORDERING GUIDE**

| Model              | Temperature Range | Package Description | Ordering Quantity | Package Option | Branding |

|--------------------|-------------------|---------------------|-------------------|----------------|----------|

| ADA4860-1YRJZ-RL1  | -40°C to +105°C   | 6-Lead SOT-23       | 10,000            | RJ-6           | НКВ      |

| ADA4860-1YRJZ-RL71 | -40°C to +105°C   | 6-Lead SOT-23       | 3,000             | RJ-6           | НКВ      |

| ADA4860-1YRJZ-R21  | -40°C to +105°C   | 6-Lead SOT-23       | 250               | RJ-6           | НКВ      |

$^{1}$  Z = Pb-free part.

## NOTES

## NOTES

©2006 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. PR05709-0-1/06(PrC)

www.analog.com

Rev. PrC | Page 20 of 20