32768-word × 32-bit Synchronous Fast Static RAM with Burst Counter and Pipelined Data Output

# **HITACHI**

ADE-203-413 (Z) Preliminary Rev. 0.1 Oct. 30, 1996

#### **Features**

- 3.3 V core power supply

- 2.5 V I/O power supply

- Fast clock access time: 5/5.5 ns (max)

- Clock cycle times: 7.5/8.5/10 ns (min)

- Address data pipeline capability

- Internal input registers (Address, Data, Control)

- Internal data output registers

- Internal self-timed write cycle

- ADSP, ADSC and ADV burst control pins (Supports interleaving)

- Asynchronous output enable controlled three-state outputs

- Individual byte write control and global write

- Common data inputs and data outputs

- · High board density 100-lead LQFP package

#### **Ordering Information**

| Type No.       | Access time | CPU clock rate | Package                |

|----------------|-------------|----------------|------------------------|

| HM62P2321FP-7H | 5 ns        | 133 MHz        | LQFP 100-pin (FP-100H) |

| HM62P2321FP-8H | 5 ns        | 117 MHz        |                        |

| HM62P2321FP-10 | 5.5 ns      | 100 MHz        |                        |

Preliminary: The specification of this device are subject to change without notice. Please contact your nearest Hitachi's Sales Dept. regarding specification.

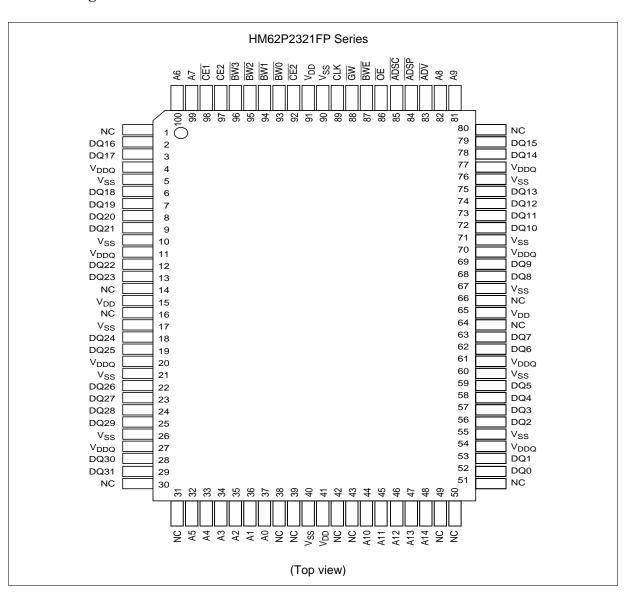

#### **Pin Arrangement**

# Pin Description (See Detailed Pin Description)

| Pin name           | Туре         | Function                                                                                                                   |

|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------|

| A0 to A14          | Input        | Address inputs                                                                                                             |

| BW0, BW1, BW2, BW3 | Input        | Byte write enables BW0 controls DQ0 to DQ7  BW1 controls DQ8 to DQ15  BW2 controls DQ16 to DQ23  BW3 controls DQ24 to DQ31 |

| GW                 | Input        | Global write                                                                                                               |

| BWE                | Input        | Byte write enable                                                                                                          |

| CLK                | Input        | Clock                                                                                                                      |

| CE1                | Input        | Enable                                                                                                                     |

| CE2, CE2           | Input        | Chip enable                                                                                                                |

| ŌĒ                 | Input        | Output enable                                                                                                              |

| ADV                | Input        | Address advance                                                                                                            |

| ADSP               | Input        | Address status processor                                                                                                   |

| ADSC               | Input        | Address status controller                                                                                                  |

| NC                 | _            | No connection                                                                                                              |

| DQ0 to DQ31        | Input/Output |                                                                                                                            |

| $V_{DD}$           | Supply       | Power supply                                                                                                               |

| $V_{DDQ}$          | I/O Supply   | I/O power supply                                                                                                           |

| V <sub>SS</sub>    | Supply       | Ground                                                                                                                     |

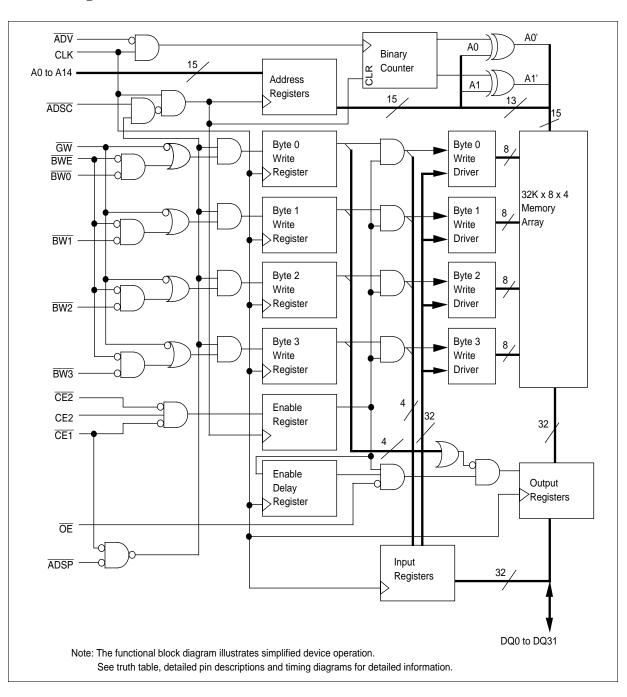

#### **Block Diagram**

#### Synchronous Truth Table

| Operation                    | Address  | CE1 | CE2 | CE2 | ADSP | ADSC | ADV | Write | ŌĒ | CLK | DQ     |

|------------------------------|----------|-----|-----|-----|------|------|-----|-------|----|-----|--------|

| Deselected cycle, power-down | None     | Н   | ×   | ×   | ×    | L    | ×   | ×     | ×  | L-H | High-Z |

| Deselected cycle, power-down | None     | L   | ×   | L   | L    | ×    | ×   | ×     | ×  | L-H | High-Z |

| Deselected cycle, power-down | None     | L   | Н   | ×   | L    | ×    | ×   | ×     | ×  | L-H | High-Z |

| Deselected cycle, power-down | None     | L   | ×   | L   | Н    | L    | ×   | ×     | ×  | L-H | High-Z |

| Deselected cycle, power-down | None     | L   | Н   | ×   | Н    | L    | ×   | ×     | ×  | L-H | High-Z |

| READ cycle, begin burst      | External | L   | L   | Н   | L    | ×    | ×   | ×     | L  | L-H | Q      |

| READ cycle, begin burst      | External | L   | L   | Н   | L    | ×    | ×   | ×     | Н  | L-H | High-Z |

| WRITE cycle, begin burst     | External | L   | L   | Н   | Н    | L    | ×   | L     | ×  | L-H | D      |

| READ cycle, begin burst      | External | L   | L   | Н   | Н    | L    | ×   | Н     | L  | L-H | Q      |

| READ cycle, begin burst      | External | L   | L   | Н   | Н    | L    | ×   | Н     | Н  | L-H | High-Z |

| READ cycle, continue burst   | Next     | ×   | ×   | ×   | Н    | Н    | L   | Н     | L  | L-H | Q      |

| READ cycle, continue burst   | Next     | ×   | ×   | ×   | Н    | Н    | L   | Н     | Н  | L-H | High-Z |

| READ cycle, continue burst   | Next     | Н   | ×   | ×   | ×    | Н    | L   | Н     | L  | L-H | Q      |

| READ cycle, continue burst   | Next     | Н   | ×   | ×   | ×    | Н    | L   | Н     | Н  | L-H | High-Z |

| WRITE cycle, continue burst  | Next     | ×   | ×   | ×   | Н    | Н    | L   | L     | ×  | L-H | D      |

| WRITE cycle, continue burst  | Next     | Н   | ×   | ×   | ×    | Н    | L   | L     | ×  | L-H | D      |

| READ cycle, suspend burst    | Current  | ×   | ×   | ×   | Н    | Н    | Н   | Н     | L  | L-H | Q      |

| READ cycle, suspend burst    | Current  | ×   | ×   | ×   | Н    | Н    | Н   | Н     | Н  | L-H | High-Z |

| READ cycle, suspend burst    | Current  | Н   | ×   | ×   | ×    | Н    | Н   | Н     | L  | L-H | Q      |

| READ cycle, suspend burst    | Current  | Н   | ×   | ×   | ×    | Н    | Н   | Н     | Н  | L-H | High-Z |

| WRITE cycle, suspend burst   | Current  | ×   | ×   | ×   | Н    | Н    | Н   | L     | ×  | L-H | D      |

| WRITE cycle, suspend burst   | Current  | Н   | ×   | ×   | ×    | Н    | Н   | L     | ×  | L-H | D      |

Notes: 1. H means logic HIGH, L means logic LOW. × means H or L. Write = L means any one or more byte write enable signals (BW0, BW1, BW2 or BW3) and BWE are LOW or GW is LOW. Write = H means all byte write enable signals and GW are HIGH.

- 2. BW0 enables write to Byte0 (DQ0 to DQ7). BW1 enables write to Byte1 (DQ8 to DQ15). BW2 enables write to Byte2 (DQ16 to DQ23). BW3 enables write to Byte3 (DQ24 to DQ31).

- All inputs except OE must meet setup and hold times around the rising edge (LOW to HIGH) of CLK.

- 4. Wait states are inserted by suspending burst.

- 5. For a write operation following a read operation,  $\overline{\text{OE}}$  must be HIGH before the input data required setup time and hold HIGH throughout the input data hold time.

- 6. ADSP = LOW always initiates an internal READ at the L-H edge of CLK. A WRITE is performed by setting one or more byte write enable signals and BWE LOW or GW LOW for the subsequent L-H edge of CLK. Refer to WRITE timing diagram for clarification.

## **Asynchronous Truth Table**

| Operation | ŌĒ | I/O status      |

|-----------|----|-----------------|

| Read      | L  | Data out        |

| Read      | Н  | High-Z          |

| Write     | ×  | High-Z, Data in |

| Deselect  | ×  | High-Z          |

Note: H means logic HIGH. L means logic LOW. × means H or L.

#### **Partial Truth Table for Writes**

| Operation       | GW | BWE | BW0 | BW1 | BW2 | BW3 |

|-----------------|----|-----|-----|-----|-----|-----|

| Read            | Н  | Н   | ×   | ×   | ×   | ×   |

| Read            | Н  | ×   | Н   | Н   | Н   | Н   |

| Write byte 0    | Н  | L   | L   | Н   | Н   | Н   |

| Write all bytes | Н  | L   | L   | L   | L   | L   |

| Write all bytes | L  | ×   | ×   | ×   | ×   | ×   |

Note: H means logic HIGH. L means logic LOW. × means H or L.

## **Interleave Sequence Table**

| Parameter            | A14 to A2 | Sequence 1<br>(A1, A0) | Sequence 2<br>(A1, A0) | Sequence 3 (A1, A0) | Sequence 4<br>(A1, A0) |

|----------------------|-----------|------------------------|------------------------|---------------------|------------------------|

| External address     | A14 to A2 | 0 0                    | 0 1                    | 1 0                 | 1 1                    |

| 1st internal address | A14 to A2 | 0 1                    | 0 0                    | 11                  | 1 0                    |

| 2nd internal address | A14 to A2 | 1 0                    | 11                     | 0 0                 | 0 1                    |

| 3rd internal address | A14 to A2 | 1 1                    | 1 0                    | 0 1                 | 0 0                    |

Note: Each Sequence wraps around to its initial state upon completion.

## **Absolute Maximum Ratings**

| Parameter                                                   | Symbol                     | Value                        | Unit |

|-------------------------------------------------------------|----------------------------|------------------------------|------|

| Supply voltage                                              | $V_{DD}$                   | -0.5 to +4.6                 | V    |

| Core I/O supply voltage                                     | V <sub>DDQ</sub>           | –0.5 to V <sub>DD</sub>      | V    |

| Voltage on any pins relative to $V_{SS}$ (Except $V_{DD}$ ) | V <sub>T</sub>             | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Power dissipation                                           | $P_{\scriptscriptstyle T}$ | 1.2                          | W    |

| Operating temperature                                       | Topr                       | 0 to +70                     | °C   |

| Storage temperature range (with bias)                       | Tstg (bias)                | -10 to +85                   | °C   |

| Storage temperature range                                   | Tstg                       | -55 to +125                  | °C   |

## **Recommended DC Operating Conditions** ( $Ta = 0 \text{ to } +70^{\circ}C$ )

| Parameter                                            | Symbol    | Min   | Max            | Unit | Notes |

|------------------------------------------------------|-----------|-------|----------------|------|-------|

| Supply voltage (Operating voltage range)             | $V_{DD}$  | 3.135 | 3.465          | V    |       |

| Core I/O Supply voltage<br>(Operating voltage range) | $V_{DDQ}$ | 2.375 | 2.900          | V    |       |

| Supply voltage to V <sub>SS</sub>                    | $V_{ss}$  | 0.0   | 0.0            | V    |       |

| Input high voltage                                   | $V_{IH}$  | 1.7   | $V_{DDQ}$ +0.3 | V    | 1     |

| Input low voltage                                    | $V_{IL}$  | -0.3  | 0.7            | V    | 2     |

Notes: 1.  $V_{DDQ}$  + 2.3 V for overshoot pulse width  $\leq t_{CYC}$  min/2.

2. -2.3 V for undershoot pulse width  $\leq$   $t_{CYC}$  min/2.

**DC Characteristics** (Ta = 0 to +70°C,  $V_{DD}$  = 3.3 V ±5 %,  $V_{DDQ}$  = 2.375 V to 2.9 V, unless otherwise noted.)

| Parameter              | Symbol           | Min | Max              | Unit | Test conditions                                                                                                                                                                              |

|------------------------|------------------|-----|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input leakage current  | l <sub>LI</sub>  | -2  | 2                | μΑ   | All inputs $Vin = V_{SS}$ to $V_{DDQ}$                                                                                                                                                       |

| Output leakage current | I <sub>LO</sub>  | -2  | 2                | μΑ   | $\overline{OE} = V_{IH}$ , Vout = $V_{SS}$ to $V_{DDQ}$                                                                                                                                      |

| Supply current         | I <sub>DD</sub>  | _   | 220              | mA   | Device selected lout = 0 mA,<br>all inputs = $V_{IH}$ or $V_{IL}$ ,<br>Cycle time = $t_{CYC}$ min.<br>$V_{DD} = Max$                                                                         |

| Standby current        | I <sub>SB</sub>  | _   | 40* <sup>1</sup> | mA   | Device deselected lout = 0 mA, all inputs = fixed and all inputs $\geq$ V <sub>DDQ</sub> $-$ 0.2 V or $\leq$ 0.2 V, Cycle time = t <sub>CYC</sub> min.                                       |

|                        |                  | _   | 35*2             |      |                                                                                                                                                                                              |

|                        |                  | _   | 30*3             |      |                                                                                                                                                                                              |

|                        | I <sub>SB1</sub> | _   | 5                | mA   | Device deselected, Output disabled all inputs = fixed and all inputs $\geq V_{DDQ} - 0.2 \text{ V or}$ $\leq 0.2 \text{ V, } V_{DD} = \text{Max, Cycle time}$ = $\infty$ (Frequency = 0 MHz) |

| Output low voltage     | V <sub>OL</sub>  | _   | 0.4              | V    | I <sub>OL</sub> = 1 mA                                                                                                                                                                       |

|                        | V <sub>OL</sub>  | _   | 0.7              | V    | I <sub>OL</sub> = 2 mA                                                                                                                                                                       |

| Output high voltage    | $V_{OH}$         | 2.0 | _                | V    | $I_{OH} = -1 \text{ mA}$                                                                                                                                                                     |

|                        | V <sub>OH</sub>  | 1.7 | _                | V    | $I_{OH} = -2 \text{ mA}$                                                                                                                                                                     |

Notes: 1. This characteristic is guaranteed only for -7H version.

2. This characteristic is guaranteed only for -8H version.

3. This characteristic is guaranteed only for -10 version.

## **Capacitance** (Ta = 25 $^{\circ}$ C, f = 1.0 MHz, $V_{DD}$ = 3.3 V, $V_{DDO}$ = 2.5 V)

| Parameter                | Symbol           | Min | Тур | Max | Unit | Note |

|--------------------------|------------------|-----|-----|-----|------|------|

| Input capacitance        | Cin              | 2   | 4   | 5   | pF   | 1    |

| Input/output capacitance | C <sub>I/O</sub> | 4   | 7   | 8   | pF   | 1    |

Note: 1. This parameter is sampled and not 100% tested.

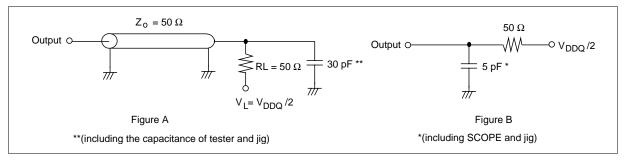

**AC Characteristics** (Ta = 0 to +70°C,  $V_{DD}$  = 3.3 V ±5 %,  $V_{DDQ}$  = 2.375 V to 2.9 V, unless otherwise noted.)

#### **Test Conditions**

- Input timing measurement reference level:  $V_{\text{DDQ}}$  / 2

- Input pulse levels: 0 V to V<sub>DDO</sub>

- Input rise and fall time: 1.5 ns (20 % to 80 %)

- Output timing reference level: V<sub>DDQ</sub> / 2

- Output load: See figure A unless otherwise noted

|                                |                            |                   | HM62 | 2P232 | 1   |     |     |     |      |       |

|--------------------------------|----------------------------|-------------------|------|-------|-----|-----|-----|-----|------|-------|

|                                | Symbol                     |                   | -7H  |       | -8H |     | -10 |     | _    |       |

| Parameter                      | Standard                   | Alternate         | Min  | Max   | Min | Max | Min | Max | Unit | Notes |

| Cycle time                     | t <sub>kHKH</sub>          | t <sub>cyc</sub>  | 7.5  | _     | 8.5 | _   | 10  | _   | ns   |       |

| Clock access time              | t <sub>KHQV</sub>          | t <sub>ACK</sub>  | _    | 5.0   | _   | 5.0 | _   | 5.5 | ns   |       |

| Output enable to output valid  | t <sub>GLQV</sub>          | t <sub>OE</sub>   | _    | 5.0   | _   | 5.0 | _   | 5.0 | ns   | 4     |

| Clock high to output active    | t <sub>KHQX1</sub>         | t <sub>CLZ</sub>  | 1.0  | _     | 1.0 | _   | 1.0 | _   | ns   |       |

| Clock high to output change    | t <sub>KHQX2</sub>         | t <sub>coh</sub>  | 1.5  | _     | 1.5 | _   | 1.5 | _   | ns   |       |

| Output enable to output active | t <sub>GLQZ</sub>          | t <sub>OLZ</sub>  | 0    | _     | 0   | _   | 0   | _   | ns   |       |

| Output disable to Q High-Z     | t <sub>GHQZ</sub>          | t <sub>OHZ</sub>  | _    | 4.5   | _   | 4.5 | _   | 4.5 | ns   | 1     |

| Clock high to Q High-Z         | t <sub>KHQZ</sub>          | t <sub>CHZ</sub>  | _    | 5.0   | _   | 5.0 | _   | 5.0 | ns   | 1     |

| Clock high pulse width         | t <sub>KHKL</sub>          | t <sub>ch</sub>   | 1.9  | _     | 2.5 | _   | 3.2 | _   | ns   |       |

| Clock low pulse width          | t <sub>KLKH</sub>          | t <sub>CL</sub>   | 1.9  | _     | 2.5 | _   | 3.2 | _   | ns   |       |

| Setup Times:                   |                            |                   | 2.0  | _     | 2.0 | _   | 2.0 | _   | ns   | 2, 3  |

| Address                        | t <sub>AVKH</sub>          | t <sub>sa</sub>   |      |       |     |     |     |     |      |       |

| Address Status                 | t <sub>ADSVKH</sub>        | t <sub>SADS</sub> |      |       |     |     |     |     |      |       |

| Input Data                     | t <sub>DVKH</sub>          | t <sub>SD</sub>   |      |       |     |     |     |     |      |       |

| Write                          | t <sub>wvkh</sub>          | t <sub>sw</sub>   |      |       |     |     |     |     |      |       |

| Address Advance                | t <sub>ADVVK</sub>         | t <sub>SADV</sub> |      |       |     |     |     |     |      |       |

| Chip Enable                    | t <sub>evkh</sub>          | t <sub>SCE</sub>  |      |       |     |     |     |     |      |       |

| Hold Times:                    |                            |                   | 0.5  | _     | 0.5 | _   | 0.5 | _   | ns   | 2, 3  |

| Address                        | $t_{KHAX}$                 | $t_{HA}$          |      |       |     |     |     |     |      |       |

| Address Status                 | <b>t</b> <sub>KHADSX</sub> | t <sub>hads</sub> |      |       |     |     |     |     |      |       |

| Input Data                     | $\mathbf{t}_{KHDX}$        | t <sub>HD</sub>   |      |       |     |     |     |     |      |       |

| Write                          | $\mathbf{t}_{KHWX}$        | $t_{HW}$          |      |       |     |     |     |     |      |       |

| Address Advance                | t <sub>KHADVX</sub>        | t <sub>HADV</sub> |      |       |     |     |     |     |      |       |

| Chip Enable                    | t <sub>KHEX</sub>          | t <sub>HCE</sub>  |      |       |     |     |     |     |      |       |

Notes: 1. Transition is measured  $\pm$  200mV from steady-state voltage with load of FigureB. This parameter is sampled.

- 2. A READ cycle is defined by byte write enables all HIGH or ADSP LOW for the required setup and hold times. A WRITE cycle is defined by at least one byte write enable LOW and ADSP HIGH for the required setup and hold times.

- 3. This is a synchronous device. All address must meet the specified setup and hold times for all rising edges of CLK when either ADSP or ADSC is LOW and chip enabled. All other Synchronous inputs must meet the setup and hold times with stable logic levels for all rising edges of clock (CLK) when chip is enabled. Chip enable must be valid at each rising edge of CLK (when either ADSP or ADSC is LOW) to remain enabled.

- 4. OE is a " H or L " when a byte write enable is sampled LOW.

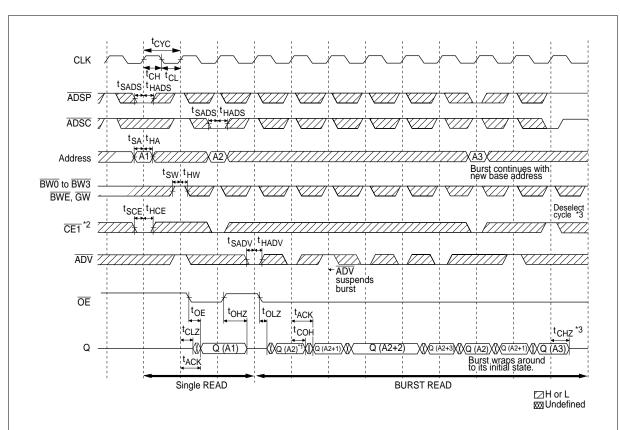

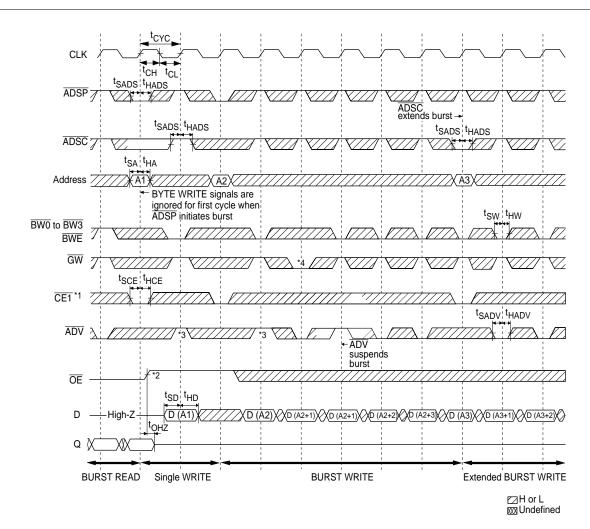

#### **Timing Waveforms**

#### **Example of Read Timing**

Notes: 1. Q (A2) refers to output from address A2. Q (A2 + 1) refers to output from next internal burst address following A2.

- 2. CE2 and CE2 have timing identical to CE1. On this diagram, when CE1 is LOW, CE2 is LOW and CE2 is HIGH. When CE1 is HIGH, CE2 is HIGH and CE2 is LOW.

- 3. Outputs are disabled within one clock cycle after deselect.

#### **Example of Write Timing**

- Notes: 1.  $\overline{\text{CE2}}$  and CE2 have timing identical to  $\overline{\text{CE1}}$ . On this diagram, when  $\overline{\text{CE1}}$  is LOW,  $\overline{\text{CE2}}$  is LOW and CE2 is HIGH. When  $\overline{\text{CE1}}$  is HIGH,  $\overline{\text{CE2}}$  is HIGH and CE2 is LOW.

- 2.  $\overline{\text{OE}}$  must be HIGH before the input data setup and held HIGH throughout the data hold time. This prevents input/output data contention for the time period prior to the byte write enable inputs being sampled.

- 3. ADV must be HIGH to permit a WRITE to the loaded address.

- 4. Full width WRITE can be initiated by  $\overline{GW}$  is LOW or  $\overline{GW}$  is HIGH and  $\overline{BWE}$ ,  $\overline{BW0}$  to  $\overline{BW3}$  are LOW.

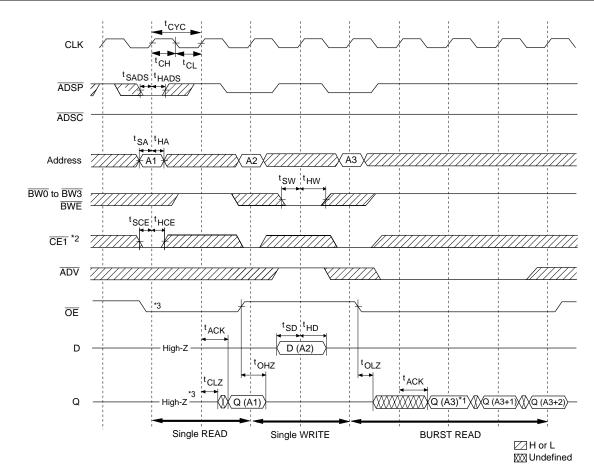

### **Example of Read/Write Timing**

Notes: 1. Q (A3) refers to output from address A3. Q (A3 + 1) refers to output from next internal burst address following A3. 2. CE2 and CE2 have timing identical to CE1. On this diagram, when CE1 is LOW, CE2 is LOW and CE2 is

- HIGH. When CE1 is HIGH, CE2 is HIGH and CE2 is LOW.

- 3. Timing is shown assuming that the device was not enabled before entering into this sequence. OE does not cause Q to be driven until after the following clock rising edge.

- 4.  $\overline{\text{GW}}$  is HIGH.

## **Detailed Pin Description**

| LQFP pin number(s)                                          | Symbol               | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------|----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37, 36, 35, 34, 33, 32, 100, 99, 82, 81, 44, 45, 46, 47, 48 | A0 to A14            | Input | Synchronous Address Inputs: These inputs are registered and must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                                                                                                                                             |

| 93, 94, 95, 96                                              | BW0, BW1<br>BW2, BW3 | Input | Synchronous Byte Write Enables: These active LOW inputs allow individual bytes to be written and must meet the setup and hold times around the rising edge of CLK. A byte write enable is LOW for a WRITE cycle and HIGH for a READ cycle. BW0 controls DQ0 to DQ7. BW1 controls DQ8 to DQ15. BW2 controls DQ16 to DQ23. BW3 controls DQ24 to DQ31. Data I/O are tri-stated if any of these four inputs are LOW.      |

| 88                                                          | GW                   | Input | Synchronous Global Write: This active LOW input allows a full 32 bit Write to occur independent of the BWE and BWi lines and must meet the setup and hold times around the rising edge of CLK. System must connect pin to V <sub>DD</sub> when not used.                                                                                                                                                              |

| 87                                                          | BWE                  | Input | Synchronous Byte Write Enable: This active LOW input permits byte write operations and must meet the setup and hold times around the rising edge of CLK. System must connect pin to $V_{\rm SS}$ when not used.                                                                                                                                                                                                       |

| 89                                                          | CLK                  | Input | Clock: This signal latches the address, data, chip enables, byte write enables and burst control inputs on its rising edge. All synchronous inputs must meet setup and hold times around the clock's rising edge.                                                                                                                                                                                                     |

| 98                                                          | CE1                  | Input | Synchronous Chip Enables: This active LOW input is used to enable the device and conditions internal use of ADSP. This input is sampled only when a new external address is load.                                                                                                                                                                                                                                     |

| 92                                                          | CE2                  | Input | Synchronous Chip Enable: This active LOW input is used to enable the device. This input is sampled only when a external address is loaded. This input can be used for memory depth expansion.                                                                                                                                                                                                                         |

| 97                                                          | CE2                  | Input | Synchronous Chip Enable: This active HIGH input is used to enable the device. This input sampled only when a new external address is load. This input can be used for memory depth expansion.                                                                                                                                                                                                                         |

| 86                                                          | ŌĒ                   | Input | Output Enable: This active LOW asynchronous input enables the data I/O output drivers.                                                                                                                                                                                                                                                                                                                                |

| 83                                                          | ĀDV                  | Input | Synchronous Address Advance: This active LOW input is used to advance the internal burst counter, controlling burst access after the external address is loaded. A HIGH on this pin effectively causes wait status to be generated (no address advance). This pin must be HIGH at the rising edge of the first clock after an ADSP cycle is initiated if a write cycle is desired (to ensure use of correct address). |

### HITACHI

## **Detailed Pin Description** (cont)

| LQFP pin number(s)                                                                                                       | Symbol          | Type   | Description                                                                                                                                                                                                                                                                                                                                              |  |

|--------------------------------------------------------------------------------------------------------------------------|-----------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 84                                                                                                                       | ADSP            | Input  | Synchronous Address Status Processor: This active LOW input interrupts any ongoing burst, causing a new external address to be latched. A READ performed using the new address, independent of the byte write enables and ADSC but dependent upon CE2 and CE2. ADSP is ignored if CE1 is HIGH. Power-down state is entered if CE2 is HIGH or CE2 is LOW. |  |

| 85                                                                                                                       | ADSC            | Input  | Synchronous Address Status Controller: This active LOW input interrupts any ongoing burst and causes a new external address to be latched. A READ or WRITE is performed using the new address if all chip enables are active. Powerdown state is entered if one or more chip enabled are inactive.                                                       |  |

| 1, 14, 16, 30, 31, 38, 39, 42, 43,49, 50, 51, 64, 66, 80                                                                 | NC              | _      | No Connect: These signals are internally not connected.                                                                                                                                                                                                                                                                                                  |  |

| 52, 53, 56, 57, 58, 59, 62, 63, 68, 69, 72, 73, 74, 75, 78, 79, 2, 3, 6, 7, 8, 9, 12, 13, 18, 19, 22, 23, 24, 25, 28, 29 | DQ0 to<br>DQ31  | •      | SRAM Data I/O: Byte 0 is DQ0 to DQ7; Byte 1 is DQ8 to DQ15; Byte 2 is DQ16 to DQ23; Byte 3 is DQ24 to DQ31. Input data must meet setup and hold times around the rising edge of CLK.                                                                                                                                                                     |  |

| 15, 41, 65, 91                                                                                                           | $V_{DD}$        | Supply | Power Supply: +3.3 V ±5 %                                                                                                                                                                                                                                                                                                                                |  |

| 4, 11, 20, 27, 54, 61, 70, 77                                                                                            | $V_{DDQ}$       | Supply | V I/O Power Supply: +2.5 V +16 %/–5 %                                                                                                                                                                                                                                                                                                                    |  |

| 5, 10, 17, 21, 26, 40, 55, 60, 67, 71, 76, 90                                                                            | V <sub>ss</sub> | Supply | Ground: GND                                                                                                                                                                                                                                                                                                                                              |  |

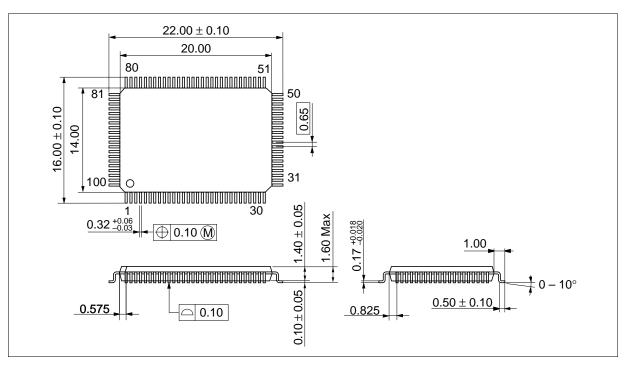

### **Package Dimensions**

#### HM62P2321FP Series (FP-100H)

Unit: mm

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

# HITACHI

#### Hitachi, Ltd.

Semiconductor & IC Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100, Japan

Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109

#### For further information write to:

Hitachi America, Ltd. Semiconductor & IC Div. 2000 Sierra Point Parkway Brisbane, CA. 94005-1835

Tel: 415-589-8300 Fax: 415-583-4207 Hitachi Europe GmbH Electronic Components Group Continental Europe Dornacher Straße 3 D-85622 Feldkirchen München

Tel: 089-9 91 80-0 Fax: 089-9 29 30 00 Hitachi Europe Ltd.

Electronic Components Div.

Northern Europe Headquarters

Whitebrook Park

Lower Cookham Road

Maidenhead

Berkshire SL6 8YA

United Kingdom

Tel: 0628-585000

Fax: 0628-778322

Hitachi Asia Pte. Ltd. 16 Collyer Quay #20-00 Hitachi Tower Singapore 0104 Tel: 535-2100 Fax: 535-1533

Hitachi Asia (Hong Kong) Ltd. Unit 706, North Tower, World Finance Centre, Harbour City, Canton Road Tsim Sha Tsui, Kowloon Hong Kong

Tel: 27359218 Fax: 27306071

## **Revision Record**

| Rev. | Date          | Contents of Modification                                                               | Drawn by | Approved by |

|------|---------------|----------------------------------------------------------------------------------------|----------|-------------|

| 0.0  | Oct. 15, 1996 | Initial issue                                                                          | K. Nagai | A. Hiraishi |

| 0.1  | Oct. 28, 1996 | Change of Asynchronous Truth Table Timing Waveforms Deletion of notes4 or 5: ZZ is Low |          |             |