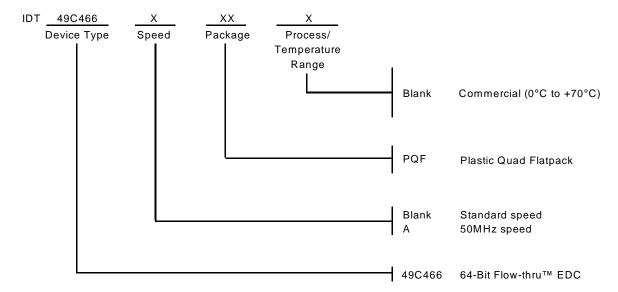

# 64-BIT FLOW-THRU ERROR DETECTION AND CORRECTION UNIT

# IDT49C466 IDT49C466A

## **FEATURES:**

- 64-bit wide Flow-thruEDC™

- Separate System and Memory Data Input/Output Buses

- Error Detect Time: 10nsError Correct Time: 15ns

- Corrects all single bit errors; Detects all double bit errors and some multiple bit errors

- Configurable 16-deep bus read/write FIFOs with flags

- Simultaneous check bit generation and correction of memory data

- Supports partial word writes on byte boundaries

- Low noise output

- Sophisticated error diagnostics and error logging

- Parity generation on system data bus

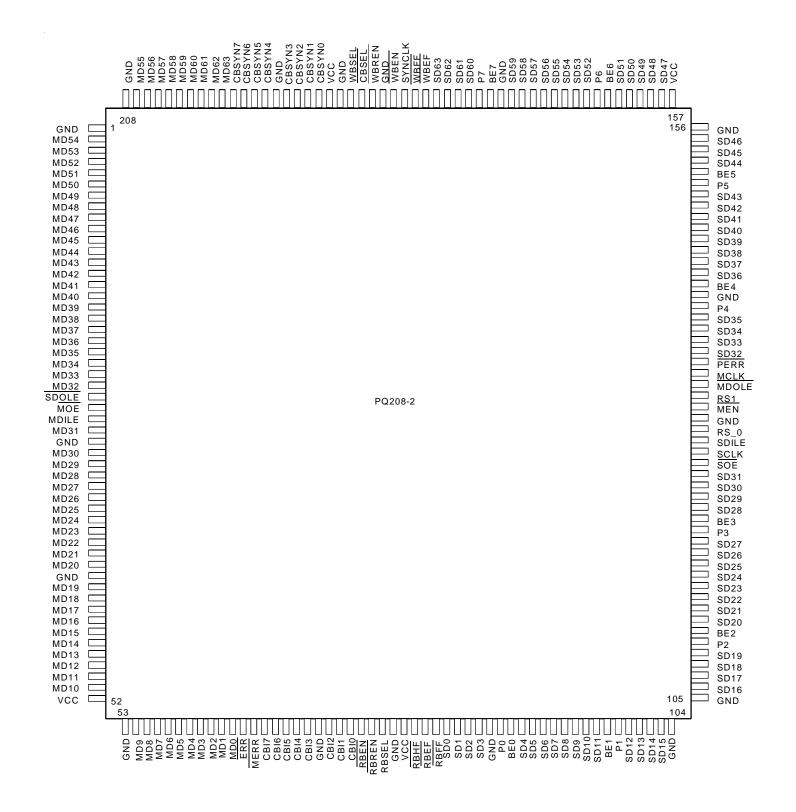

- 208-pin Plastic Quad Flatpack

# **DESCRIPTION:**

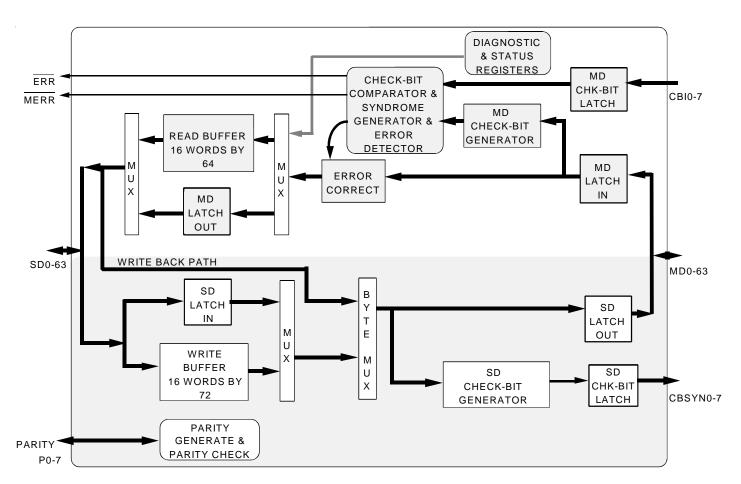

The IDT49C466/A 64-bit Flow-thruEDC is a high-speed error detection and correction unit that ensures data integrity in memory systems. The flow-thru architecture, with separate system and memory data buses, is ideally suited for pipelined memory systems.

Implementing a modified Hamming code, the IDT49C466/A corrects all single bit hard and soft errors, and detects all double bit errors. The read/write FIFOs can store up to sixteen words. FIFO full and empty flags indicate whether additional data can be written to or read from the EDC.

Check bit generation for partial word writes on byte boundaries is supported on the  $\ensuremath{\mathsf{IDT49C466/A}}$ .

Diagnostic features include a check bit register, syndrome registers, a four bit error counter which logs up to fifteen errors, and an error data register which stores the complete error data word. Parity can be generated and checked on the system bus by the IDT49C466/A.

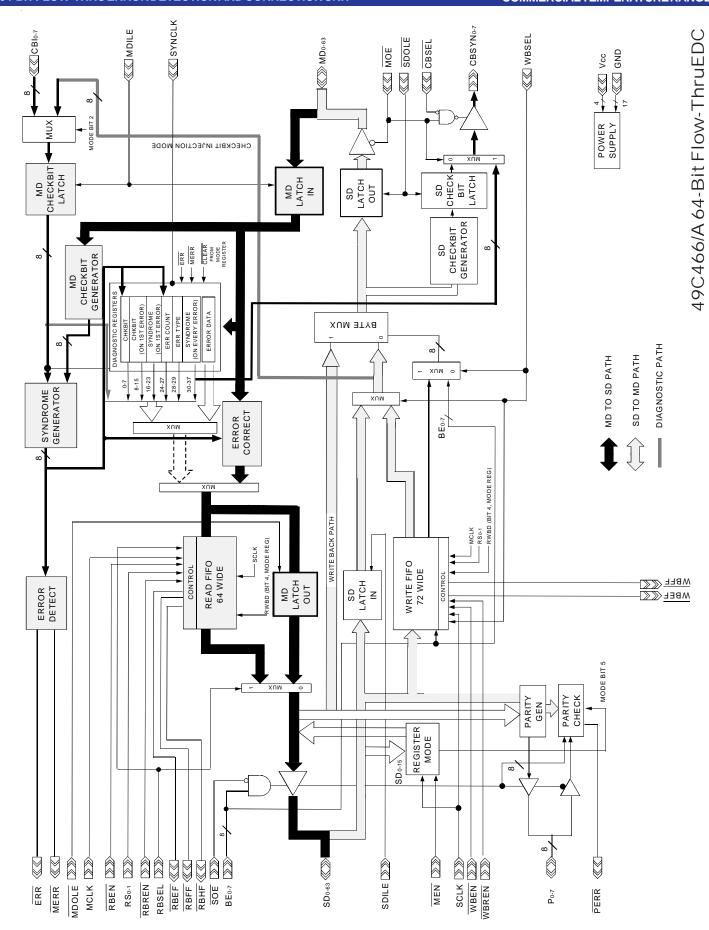

## FUNCTIONAL BLOCK DIAGRAM

$\label{thm:continuous} The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, of \, Integrated \, Device \, Technology, \, Inc. \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, is \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, a \, registered \, trademark \, determine \, The \, IDT \, logo \, a$

COMMERCIAL TEMPERATURE RANGE

FEBRUARY 2000

## **PIN CONFIGURATION**

PQFP TOP VIEW

# **PIN DESCRIPTION**

| Pin Name         | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SD0-63           | I/O | System Data Bus: is a bidirectional 64-bit bus interfacing to the system or CPU. When System Output Enable, SOE, is HIGH or Byte Enable, BEo-7, is LOW, data can be input. When System Output Enable, SOE, is LOW and Byte Enable, BEo-7, is HIGH, the SD bus output drivers are enabled.                                                                                                                                      |  |  |  |  |  |

| MD0-63           | 1/0 | Memory Data Bus: is a bidirectional 64-bit bus interfacing to the memory. During a read cycle, (MOE HIGH) memory data is input for error detection and correction. Data is output on the Memory Data Bus, when MOE is LOW.                                                                                                                                                                                                     |  |  |  |  |  |

| CBI0-7           | I   | Check Bit Inputs: interface to the check bit memory.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| CBSYN0-7         | 0   | Check Bit/Syndrome Output: when $\overline{\text{MOE}}$ is LOW, the generated check bits are output. When CBSEL is HIGH and $\overline{\text{MOE}}$ is HIGH, the syndrome bits are output. The bus is tristated when $\overline{\text{MOE}}$ = 1 and CBSEL = 0.                                                                                                                                                                |  |  |  |  |  |

| P <sub>0-7</sub> | I/O | Parity for bytes 0 to 7: these pins are parity inputs when the corresponding Byte Enable (BE) is LOW or SOE is HIGH, and are used to generate the parity error signal (PERR). These pins are outputs when the corresponding Byte Enable (BE) is HIGH and SOE is LOW.                                                                                                                                                           |  |  |  |  |  |

| Control Inputs   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| SOE              | I   | System Output Enable: enables system data bus output drivers if the corresponding Byte Enable (BEo-7) is HIGH.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

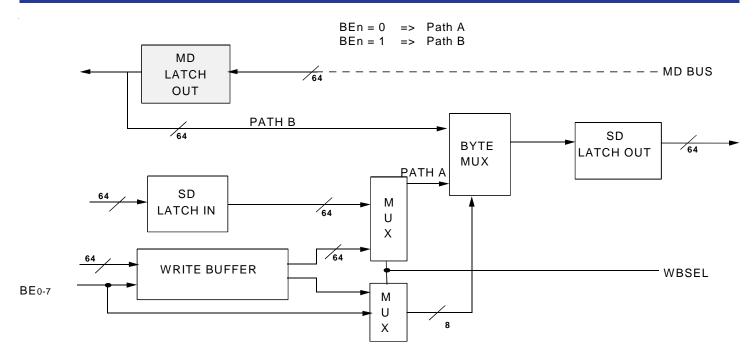

| BE0-7            | I   | Byte Enable: is used along with SOE to enable the System Data outputs for a particular byte. For example, if BE1 is HIGH, the System data outputs for byte 1 (SD8-15) are enabled. The BE0-7 pins also control the byte mux. If a particular BE is HIGH during a memory read cycle, that byte is fed back to the memory data bus. This is used during partial word write operations and writing corrected data back to memory. |  |  |  |  |  |

| MOE              | 1   | Memory Output Enable: when LOW, enables the output buffers of the memory data bus (MD) and CBSYN bus. It also controls the CBSYN mux. When LOW, checkbits are selected, when HIGH, syndrome is selected.                                                                                                                                                                                                                       |  |  |  |  |  |

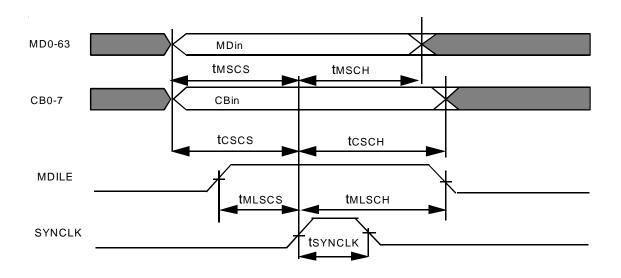

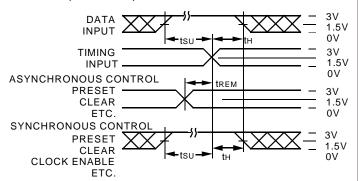

| MDILE            | 1   | <b>Memory Data Input Latch Enable:</b> on the HIGH-to-LOW transition, latches MD and CBI in MD input latch and MD check bit latch respectively. The latches are transparent when MDILE is HIGH.                                                                                                                                                                                                                                |  |  |  |  |  |

| MDOLE            | I   | Memory Data Output Latch Enable: latches data in the MD output latch on the LOW-to-HIGH transition of MDOLE. When MDOLE is LOW, the MD output latch is transparent.                                                                                                                                                                                                                                                            |  |  |  |  |  |

| SDOLE            | I   | System Data Output Latch Enable: latches data in the SD output latch and the SD checkbit latch on the LOW-to-HIGH transition of SDOLE. The latch is transparent when SDOLE is LOW.                                                                                                                                                                                                                                             |  |  |  |  |  |

| SDILE            | I   | System Data Input Latch Enable: latches SD in the SD input latch on the HIGH-to-LOW transition. When SDILE is HIGH, the SD input latch is transparent.                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| WBSEL            | I   | Write FIFO Select: when HIGH, the write FIFO is selected. When WBSEL is LOW, the SD input latch is selected.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| WBEN             | ı   | Write FIFO Enable: when LOW, allows SD data to be written to the write FIFO on the SCLK rising edge.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| WBREN            | ı   | Write FIFO Read Enable: when LOW, allows data to be read from the the write FIFO on MCLK rising edge.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| RS0-1            | ı   | Reset and Select pins (read and write FIFO FIFOs)  RS1 RS0 Function 0 0 Reset 16-deep FIFO or first 8-deep FIFO 0 1 Reset second 8-deep FIFO 1 0 Select 16-deep FIFO or first 8-deep FIFO 1 Select second 8-deep FIFO                                                                                                                                                                                                          |  |  |  |  |  |

# PIN DESCRIPTION (cont.)

| Pin Name       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBSEL          | 1   | Read FIFO Select: when HIGH, read FIFO is selected (data goes through read FIFO, not MD output latch). When LOW, the MD output latch is selected.                                                                                                                                                                                                                                |

| RBEN           | I   | Read FIFO Enable: when LOW, allows data to be written into the read FIFO on the LOW-to-HIGH transition of the memory clock.                                                                                                                                                                                                                                                      |

| RBREN          | I   | Read FIFO Enable: when LOW, allows data to be read from the read FIFO on the LOW-to-HIGH transition of SCLK.                                                                                                                                                                                                                                                                     |

| CBSEL          | I   | Checkbit Syndrome Output Enable: controls the CBSYN output buffer. When HIGH, the buffer is enabled. When CBSEL is LOW, MOE controls the buffer.                                                                                                                                                                                                                                 |

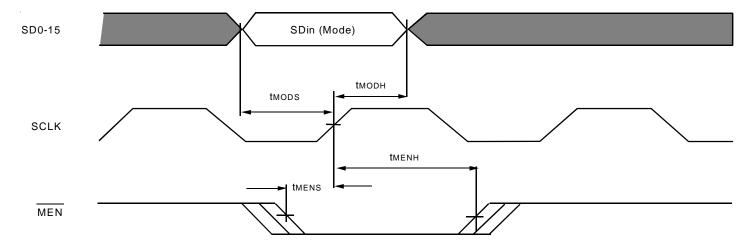

| MEN            | I   | Mode Enable Input: when LOW, SD0-15 is loaded into the EDC mode register on the LOW-to-HIGH transition of the SCLK. This pin must be held LOW for the entire SCLK HIGH period, as shown in Figure 4.                                                                                                                                                                             |

| Clock Inputs   |     |                                                                                                                                                                                                                                                                                                                                                                                  |

| MCLK           | I   | Memory Clock: on the LOW-to-HIGH transition of MCLK, memory data is written to the read FIFO when RBEN is LOW. Data is read from the write FIFO when WBREN is LOW, on the LOW-to-HIGH transition of MCLK.                                                                                                                                                                        |

| SCLK           | I   | System Clock: on the LOW-to-HIGH transition of the SCLK, data is read from the read FIFO when RBREN is LOW. Data on the system data bus is written into the write FIFO when WBEN is LOW on the LOW-to-HIGH transition of SCLK. Clocks data into mode register when MEN is LOW.                                                                                                   |

| SYNCLK         | I   | Syndrome Clock: used to load diagnostic registers. When an error occurs, Error Counter is incremented on the rising SYNCLK edge (up to 15 errors). On the first error after a diagnostic reset, SYNCLK rising edge clocks data into Check Bit, Syndrome, Error Type and Error Data registers. One of the syndrome registers has new data clocked in on every SYNCLK rising edge. |

| Status Outputs |     |                                                                                                                                                                                                                                                                                                                                                                                  |

| WBEF           | 0   | Write FIFO Empty Flag: when LOW, indicates that the write FIFO is empty. After a reset, the WBEF goes LOW.                                                                                                                                                                                                                                                                       |

| WBFF           | 0   | Write FIFO Full Flag: when LOW, indicates that the write FIFO is full. After a reset, WBFF goes HIGH.                                                                                                                                                                                                                                                                            |

| RBEF           | 0   | Read FIFO Empty Flag: when LOW, indicates that the read FIFO is empty. After a reset, the RBEF goes LOW.                                                                                                                                                                                                                                                                         |

| RBHF           | 0   | Read FIFO Half-full Flag: when LOW, indicates that there are eight or more data words (in the 16-deep configuration) or four or more data words (in the dual 8-deep configuration) in the read FIFO. The flag will return HIGH when less than eight (or four) data words are in the FIFO.                                                                                        |

| RBFF           | 0   | Read FIFO Full Flag: when LOW, indicates that the read FIFO is full. After a reset, RBFF goes HIGH.                                                                                                                                                                                                                                                                              |

| ERR            | 0   | Error Flag: when ERR is LOW, a data error is indicated. The ERR is not latched internally.                                                                                                                                                                                                                                                                                       |

| MERR           | 0   | Multiple Error Flag: when MERR is LOW, a multiple data error is indicated. The MERR is not latched internally.                                                                                                                                                                                                                                                                   |

| PERR           | 0   | Parity Error Flag: when LOW, indicates a parity error on the system data bus input.                                                                                                                                                                                                                                                                                              |

| Power Supply   | -   |                                                                                                                                                                                                                                                                                                                                                                                  |

| Vcc            | Р   | Power Supply Voltage.                                                                                                                                                                                                                                                                                                                                                            |

| GND            | Р   | Ground.                                                                                                                                                                                                                                                                                                                                                                          |

# DETAILED DESCRIPTION —

# 64-BIT MODIFIED HAMMING CODE - CHECKBIT ENCODING CHART<sup>(1, 2)</sup>

| Generated                                                                |                                                                                                                                                                                | Participating Data Bits               |                                       |                                       |             |                                       |                                       |                          |                            |                   |               |                                       |                                       |                     |                                       |                   |    |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------|---------------------------------------|-------------|---------------------------------------|---------------------------------------|--------------------------|----------------------------|-------------------|---------------|---------------------------------------|---------------------------------------|---------------------|---------------------------------------|-------------------|----|

| Checkbits                                                                | Parity                                                                                                                                                                         | 0                                     | 1                                     | 2                                     | 3           | 4                                     | 5                                     | 6                        | 7                          | 8                 | 9             | 10                                    | 11                                    | 12                  | 13                                    | 14                | 1! |

| CB0                                                                      | Even (XOR)                                                                                                                                                                     |                                       | Х                                     | Х                                     | Х           |                                       | Х                                     |                          |                            | Х                 | Х             |                                       | Х                                     |                     |                                       | Х                 |    |

| CB1                                                                      | Even (XOR)                                                                                                                                                                     | Х                                     | Х                                     | Х                                     |             | Х                                     |                                       | Х                        |                            | Х                 |               | Х                                     |                                       | Х                   |                                       |                   |    |

| CB2                                                                      | Odd (XNOR)                                                                                                                                                                     | Х                                     |                                       |                                       | Х           | Х                                     |                                       |                          | Χ                          |                   | Χ             | Х                                     |                                       |                     | Х                                     |                   |    |

| CB3                                                                      | Odd (XNOR)                                                                                                                                                                     | Х                                     | Х                                     |                                       |             |                                       | Х                                     | Х                        | Х                          |                   |               |                                       | Х                                     | Х                   | Х                                     |                   |    |

| CB4                                                                      | Even (XOR)                                                                                                                                                                     |                                       |                                       | Х                                     | Х           | Х                                     | Х                                     | Х                        | Х                          |                   |               |                                       |                                       |                     |                                       | Χ                 |    |

| CB5                                                                      | Even (XOR)                                                                                                                                                                     |                                       |                                       |                                       |             |                                       |                                       |                          |                            | Х                 | Х             | Х                                     | Х                                     | Х                   | Х                                     | Х                 |    |

| CB6                                                                      | Even (XOR)                                                                                                                                                                     | Х                                     | Х                                     | Х                                     | Х           | Х                                     | Х                                     | Х                        | Х                          |                   |               |                                       |                                       |                     |                                       |                   |    |

| CB7                                                                      | Even (XOR)                                                                                                                                                                     | Х                                     | Х                                     | Х                                     | Х           | Х                                     | Х                                     | Х                        | Х                          |                   |               |                                       |                                       |                     |                                       |                   | Г  |

| Generated                                                                |                                                                                                                                                                                |                                       | •                                     | •                                     | •           | •                                     | •                                     | Part                     | icipatii                   | ng Data           | Bits          | -                                     | •                                     | •                   | •                                     |                   |    |

| Checkbits                                                                | Parity                                                                                                                                                                         | 16                                    | 17                                    | 18                                    | 19          | 20                                    | 21                                    | 22                       | 23                         | 24                | 25            | 26                                    | 27                                    | 28                  | 29                                    | 30                | Γ  |

| CB0                                                                      | Even (XOR)                                                                                                                                                                     |                                       | Х                                     | Х                                     | Х           |                                       | Х                                     |                          |                            | Х                 | Х             |                                       | Х                                     |                     |                                       | Х                 | Г  |

| CB1                                                                      | Even (XOR)                                                                                                                                                                     | X                                     | Х                                     | Х                                     |             | Х                                     |                                       | Х                        |                            | Х                 |               | Х                                     |                                       | Х                   |                                       |                   | T  |

| CB2                                                                      | Odd (XNOR)                                                                                                                                                                     | X                                     |                                       |                                       | Х           | Х                                     |                                       |                          | Х                          |                   | Х             | Х                                     |                                       |                     | Х                                     |                   | H  |

| CB3                                                                      | Odd (XNOR)                                                                                                                                                                     | X                                     | Х                                     |                                       |             |                                       | Х                                     | Х                        | Х                          |                   |               |                                       | Х                                     | Х                   | Х                                     |                   | Н  |

| CB4                                                                      | Even (XOR)                                                                                                                                                                     |                                       |                                       | Х                                     | Х           | Х                                     | Х                                     | Х                        | Х                          |                   |               |                                       |                                       |                     |                                       | Х                 | H  |

| CB5                                                                      | Even (XOR)                                                                                                                                                                     | +                                     |                                       |                                       |             |                                       |                                       |                          |                            | Х                 | Х             | Х                                     | Х                                     | Х                   | Х                                     | Х                 | H  |

| CB6                                                                      | Even (XOR)                                                                                                                                                                     | +                                     |                                       |                                       |             |                                       |                                       |                          |                            | Х                 | Х             | Х                                     | Х                                     | Х                   | Х                                     | Х                 | H  |

| CB7                                                                      | Even (XOR)                                                                                                                                                                     |                                       |                                       |                                       |             |                                       |                                       |                          |                            | Х                 | Х             | Х                                     | Х                                     | Х                   | Х                                     | Х                 | H  |

| Generated                                                                |                                                                                                                                                                                | +                                     |                                       |                                       |             |                                       |                                       | Dari                     | icinatii                   | ng Data           | Rite          |                                       |                                       |                     |                                       |                   |    |

|                                                                          |                                                                                                                                                                                |                                       |                                       |                                       |             |                                       |                                       | I air                    | icipatii                   | <del></del>       |               |                                       |                                       |                     |                                       |                   | _  |

| Checkbits                                                                | Parity                                                                                                                                                                         | 32                                    | 33                                    | 34                                    | 35          | 36                                    | 37                                    | 38                       | 39                         | 40                | 41            | 42                                    | 43                                    | 44                  | 45                                    | 46                |    |

| Checkbits<br>CB0                                                         | Parity Even (XOR)                                                                                                                                                              | 32<br>X                               | 33                                    | 34                                    | 35          | 36<br>X                               | 37                                    | <b>38</b>                | <b>39</b>                  | 40                | 41            | <b>42</b>                             | 43                                    | <b>44</b> X         | <b>45</b>                             | 46                |    |

| CB0                                                                      | Even (XOR)                                                                                                                                                                     | Х                                     |                                       |                                       | 35          | Х                                     | 37                                    | Х                        | 39<br>X                    |                   | 41            | Х                                     | 43                                    | Х                   | <b>4</b> 5                            | 46                |    |

| CB0<br>CB1                                                               | Even (XOR)<br>Even (XOR)                                                                                                                                                       | X                                     | 33<br>X                               | 34<br>X                               |             | X                                     | 37                                    | _                        | Х                          | 40<br>X           |               | X                                     | 43                                    |                     | Х                                     | 46                |    |

| CB0<br>CB1<br>CB2                                                        | Even (XOR) Even (XOR) Odd (XNOR)                                                                                                                                               | X<br>X<br>X                           | Х                                     |                                       | 35<br>X     | Х                                     |                                       | X                        | X                          |                   | 41<br>X       | Х                                     |                                       | X                   | X                                     | 46                |    |

| CB0<br>CB1<br>CB2<br>CB3                                                 | Even (XOR) Even (XOR) Odd (XNOR) Odd (XNOR)                                                                                                                                    | X                                     |                                       | Х                                     | X           | X<br>X<br>X                           | X                                     | X                        | X                          |                   |               | X                                     | 43<br>X                               | Х                   | Х                                     |                   |    |

| CB0<br>CB1<br>CB2                                                        | Even (XOR) Even (XOR) Odd (XNOR) Odd (XNOR) Even (XOR)                                                                                                                         | X<br>X<br>X                           | Х                                     |                                       |             | X                                     |                                       | X                        | X                          |                   | X             | X<br>X<br>X                           | X                                     | XXX                 | X                                     | 46<br>X           |    |

| CB0<br>CB1<br>CB2<br>CB3<br>CB4                                          | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)                                                                                                         | X<br>X<br>X                           | Х                                     | Х                                     | X           | X<br>X<br>X                           | X                                     | X                        | X                          | X                 |               | X                                     |                                       | X                   | X                                     | X                 |    |

| CB0 CB1 CB2 CB3 CB4 CB5                                                  | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)                                                                                             | X<br>X<br>X                           | X                                     | X                                     | X           | X<br>X<br>X                           | X                                     | X<br>X<br>X              | X<br>X<br>X                | X                 | X             | X<br>X<br>X                           | X                                     | XXX                 | X                                     | X                 |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7                                          | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)                                                                                                         | X<br>X<br>X                           | X                                     | X                                     | X           | X<br>X<br>X                           | X                                     | X<br>X<br>X<br>X         | X<br>X<br>X<br>X           | X                 | X             | X<br>X<br>X                           | X                                     | X X X               | X<br>X<br>X                           | X                 |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated                               | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)                                                                                 | X<br>X<br>X<br>X                      | X                                     | X                                     | X           | X<br>X<br>X                           | X<br>X                                | X<br>X<br>X<br>X         | X<br>X<br>X<br>X           | X<br>X<br>X       | X X Bits      | X<br>X<br>X                           | X                                     | X<br>X<br>X         | X<br>X<br>X                           | X<br>X            |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated Checkbits                     | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Parity                                                                         | X X X X X X X X X X X X X X X X X X X | X                                     | X                                     | X           | X<br>X<br>X<br>X<br>X                 | X                                     | X X X X Part             | X X X X X icipatin         | X                 | X             | X<br>X<br>X<br>X<br>X                 | X                                     | X X X X X X         | X X X X X X                           | X                 |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated Checkbits CB0                 | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Parity  Even (XOR)                                                             | X X X X X X X X X X X X X X X X X X X | X X X X 49                            | X X X 50                              | X           | X<br>X<br>X<br>X<br>X                 | X<br>X                                | X X X X Part             | X<br>X<br>X<br>X           | X X X ng Data     | X X Bits      | X X X X X X X X X X X X X X X X X X X | X                                     | X X X X X X X X X   | X<br>X<br>X                           | X<br>X            |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7 Generated Checkbits CB0 CB1              | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Parity  Even (XOR)  Even (XOR)                                                 | X X X X X X X X X X X X X X X X X X X | X                                     | X                                     | X X X 51    | X X X X X X X X X X X X X X X X X X X | X<br>X                                | X X X X Part             | X X X X X icipatii         | X<br>X<br>X       | X X X Bits    | X X X X X X X X X X X X X X X X X X X | X                                     | X X X X X X         | X X X X X X X X X X X X X X X X X X X | X<br>X            |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated Checkbits CB0 CB1 CB2         | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Odd (XNOR)                                             | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X 50                              | X           | X<br>X<br>X<br>X<br>X                 | X X X X 53                            | X X X X X Part           | X X X X X Sicipatin        | X X X ng Data     | X X Bits      | X X X X X X X X X X X X X X X X X X X | X X X 59                              | X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X<br>X            |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated Checkbits CB0 CB1 CB2 CB3     | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Odd (XNOR)                                 | X X X X X X X X X X X X X X X X X X X | X X X X 49                            | X X X X X X X X X X X X X X X X X X X | X X X X X X | X X X X X X X X X X X X X             | X X X X X X X X X X X X X X X X X X X | X X X X X Part X X X X X | X X X X X icipatii  55 X X | X X X ng Data     | X X X Bits    | X X X X X X X X X X X X X X X X X X X | X                                     | X X X X X X X X X   | X X X X X X X X X X X X X X X X X X X | X<br>X<br>X       |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated Checkbits CB0 CB1 CB2 CB3 CB4 | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Parity  Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR) | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X 50                              | X X X 51    | X X X X X X X X X X X X X X X X X X X | X X X X 53                            | X X X X X Part           | X X X X X Sicipatin        | X X X Ang Data 56 | X X X Bits 57 | X X X X X X X X X                     | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X | X X X X X X X X X X X                 | X X X X X X X X X |    |

| CB0 CB1 CB2 CB3 CB4 CB5 CB6 CB7  Generated Checkbits CB0 CB1 CB2 CB3     | Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Even (XOR)  Odd (XNOR)  Odd (XNOR)  Odd (XNOR)                                 | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X X X X X X | X X X X X X X X X X X X X             | X X X X X X X X X X X X X X X X X X X | X X X X X Part X X X X X | X X X X X icipatii  55 X X | X X X ng Data     | X X X Bits    | X X X X X X X X X X X X X X X X X X X | X X X 59                              | X X X X X X X X X X | X X X X X X X X X X X X X X X X X X X | X<br>X<br>X       |    |

<sup>1.</sup> The table indicates the data bits participating in the checkbit generation. For example, checkbit CB0 is the Exclusive-OR function of the 64 data input bits marked with an "X".

<sup>2.</sup> The checkbit is generated as either an XOR or an XNOR of the 64 data bits noted by an "X" in the table.

# DETAILED DESCRIPTION —

64-BIT SYNDROME DECODE TO BIT-IN-ERROR<sup>(1)</sup>

|     |    |      |      |    | HEX        | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | Α  | В  | С | D | Е  | F  |

|-----|----|------|------|----|------------|----|----|----|----|----|----|----|----|----|----|----|----|---|---|----|----|

|     |    |      |      |    | <b>S7</b>  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1 | 1 | 1  | 1  |

|     |    |      |      |    | S6         | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | 0  | 0  | 0  | 1 | 1 | 1  | 1  |

|     |    | Synd | rome |    | <b>S</b> 5 | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0 | 0 | 1  | 1  |

|     |    | Bi   | ts   |    | <b>S</b> 4 | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0 | 1 | 0  | 1  |

| HEX | S3 | S2   | S1   | S0 |            |    |    |    |    |    |    |    |    |    |    |    |    |   |   |    |    |

| 0   | 0  | 0    | 0    | 0  |            | *  | C4 | C5 | Т  | C6 | Т  | T  | 62 | C7 | Т  | T  | 46 | Т | М | М  | Т  |

| 1   | 0  | 0    | 0    | 1  |            | C0 | T  | T  | 14 | Τ  | М  | М  | T  | T  | М  | М  | T  | М | T | T  | 30 |

| 2   | 0  | 0    | 1    | 0  |            | C1 | T  | T  | М  | T  | 34 | 56 | T  | T  | 50 | 40 | T  | М | T | T  | М  |

| 3   | 0  | 0    | 1    | 1  |            | Т  | 18 | 8  | T  | М  | Т  | Т  | М  | М  | Т  | Т  | М  | Т | 2 | 24 | Т  |

| 4   | 0  | 1    | 0    | 0  |            | C2 | T  | T  | 15 | T  | 35 | 57 | T  | T  | 51 | 41 | Т  | М | T | T  | 31 |

| 5   | 0  | 1    | 0    | 1  |            | T  | 19 | 9  | Т  | М  | Т  | Т  | 63 | М  | Т  | T  | 47 | Т | 3 | 25 | Т  |

| 6   | 0  | 1    | 1    | 0  |            | T  | 20 | 10 | Т  | М  | Т  | Т  | М  | М  | Т  | T  | М  | Т | 4 | 26 | Т  |

| 7   | 0  | 1    | 1    | 1  |            | M  | T  | Τ  | М  | Т  | 36 | 58 | T  | T  | 52 | 42 | T  | М | Т | T  | М  |

| 8   | 1  | 0    | 0    | 0  |            | C3 | T  | Τ  | М  | Т  | 37 | 59 | T  | T  | 53 | 43 | T  | М | Т | T  | М  |

| 9   | 1  | 0    | 0    | 1  |            | Т  | 21 | 11 | Т  | М  | Т  | Т  | М  | М  | Т  | Т  | М  | Т | 5 | 27 | Т  |

| А   | 1  | 0    | 1    | 0  |            | Т  | 22 | 12 | Т  | 33 | Т  | Т  | М  | 49 | Т  | T  | М  | Т | 6 | 28 | Т  |

| В   | 1  | 0    | 1    | 1  |            | 17 | Т  | Т  | М  | Т  | 38 | 60 | Т  | Т  | 54 | 44 | T  | 1 | Т | Т  | М  |

| С   | 1  | 1    | 0    | 0  |            | Т  | 23 | 13 | Т  | М  | Т  | Т  | М  | М  | Т  | Т  | М  | Т | 7 | 29 | Т  |

| D   | 1  | 1    | 0    | 1  |            | М  | Т  | Т  | М  | Т  | 39 | 61 | Т  | Т  | 55 | 45 | T  | М | Т | Т  | М  |

| Е   | 1  | 1    | 1    | 0  |            | 16 | Т  | Т  | М  | Т  | М  | М  | Т  | Т  | М  | М  | T  | 0 | Т | Т  | М  |

| F   | 1  | 1    | 1    | 1  |            | T  | М  | М  | T  | 32 | Т  | Т  | М  | 48 | T  | Т  | М  | Т | М | М  | Т  |

#### NOTES:

- 1. The table indicates the decoding of the eight syndrome bits to identify the bit-in-error for a single-bit error, or whether a double or triple-bit error was detected. The all-zero case indicates no error detected.

- \* = No errors detected

- # = The number of the single data bit-in-error

- T = Two errors detected

- M = Three or more detected

- C# = The number of the single checkbits in error

## IDT49C466 OPERATION

The EDC is involved in two types of operation — memory reads and memory writes. With the IDT49C466, both these can be accomplished by utilizing either of two possible data paths — one incorporating the FIFO and the other without the FIFO. These operations are treated separately below.

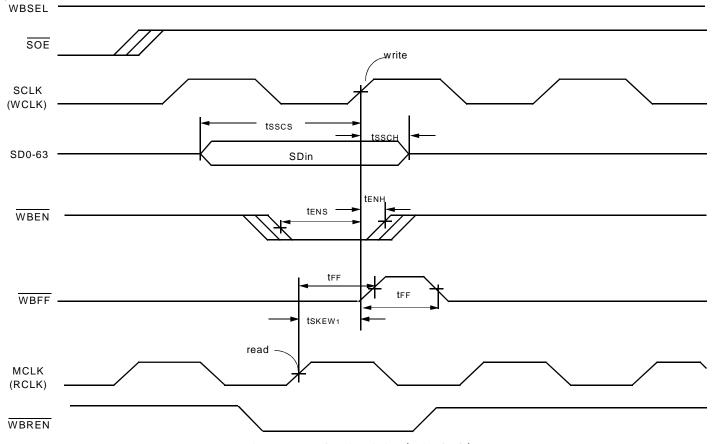

#### **Memory Write**

The involvement of the EDC in this type of operation is relatively minimal since it does not call for any error checking. It only generates the check bits associated with each 64-bit wide data word. The EDC can be in generate-detect or normal mode for this operation.

When a write operation is performed, it must be ensured that the SD output buffer (enabled by  $\overline{SOE}$  and BE0-7) is disabled so that no attempt is made to simultaneously transfer read data onto the System Data (SD) Bus.

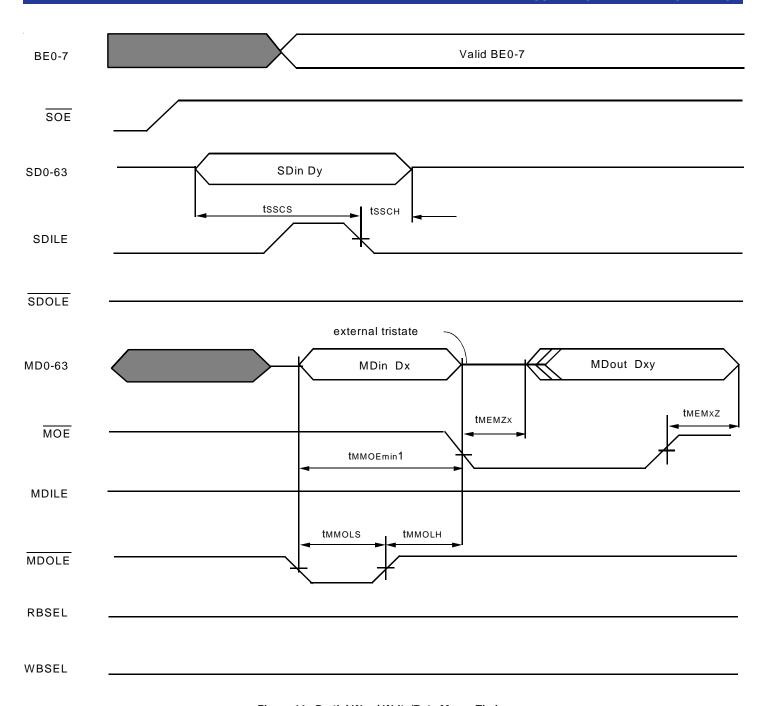

When the write FIFO (WFIFO) is bypassed (WBSELLOW), data passes through the SD Latch In. To latch data, the SDILE signal should be pulled LOW. The special case of a partial word write or byte merge is discussed

later. Here it is assumed that all 64 bits are being written. Consequently, BE<sub>0-7</sub> must all be LOW.

The data is fed to the SD Checkbit generator where appropriate checkbits are generated. Both system data and the generated checkbits can be latched by pulling the  $\overline{SDOLE}$  signal HIGH. Asserting  $\overline{MOE}$  enables the MD output buffer and data is output to the Memory Data (MD) bus.  $\overline{CBSEL}$  (=1) or  $\overline{MOE}$ (=0) need to be asserted to enable the CBSYN output buffer and output checkbits on CBSYN0-7.

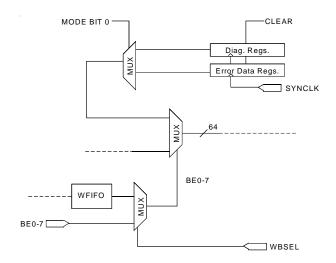

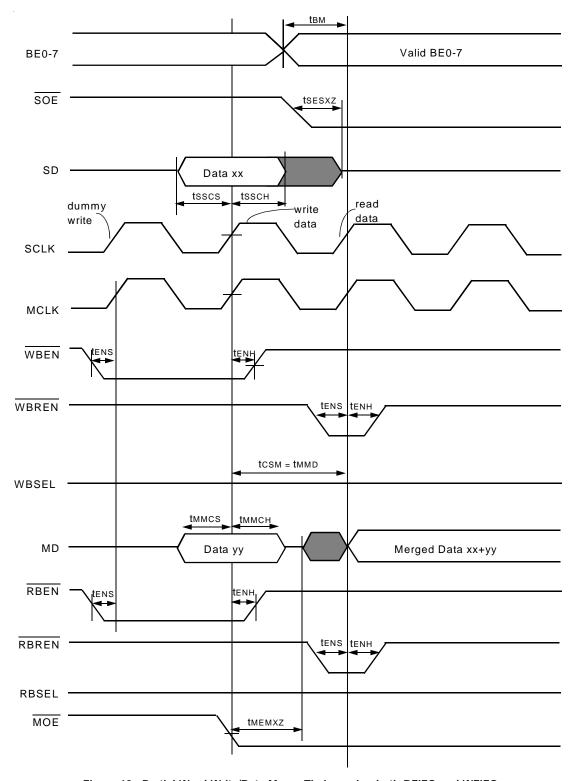

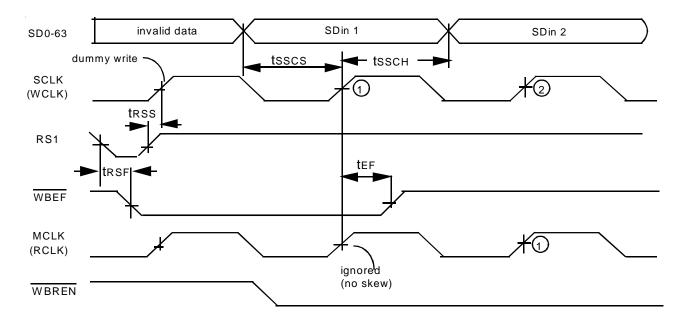

When the write FIFO is selected (WBSEL = 1), instead of asserting SDILE,  $\overline{WBEN}$  is asserted and data is clocked into the write FIFO on the rising edge of SCLK.  $\overline{WBFF}$  is asserted when the WFIFO is full and this inhibits further write attempts (see section on "Clock Skew" and "R/W FIFO Operation at Boundaries") to the WFIFO. When  $\overline{WBREN}$  is asserted, data can be clocked out of the write FIFO on the rising edge of MCLK.  $\overline{WBEF}$  is asserted when the WFIFO is empty and this inhibits further read attempts (see section on "Clock Skew") from the WFIFO.

Figure 1. Byte Merge

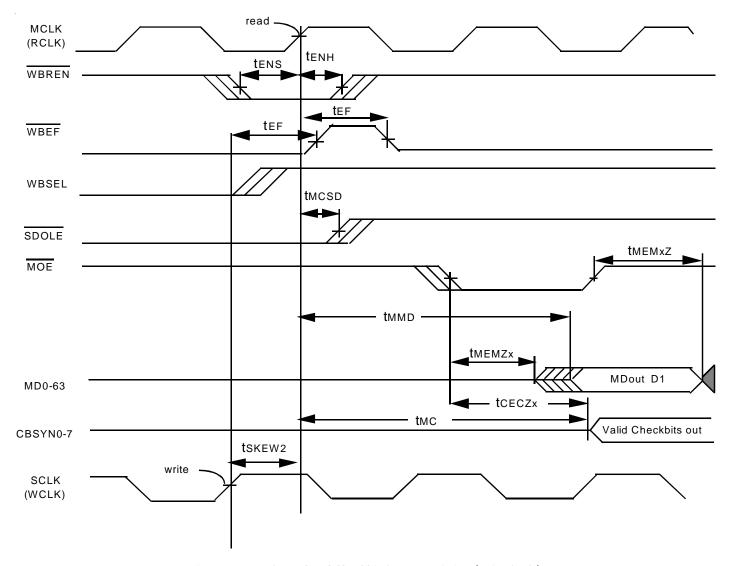

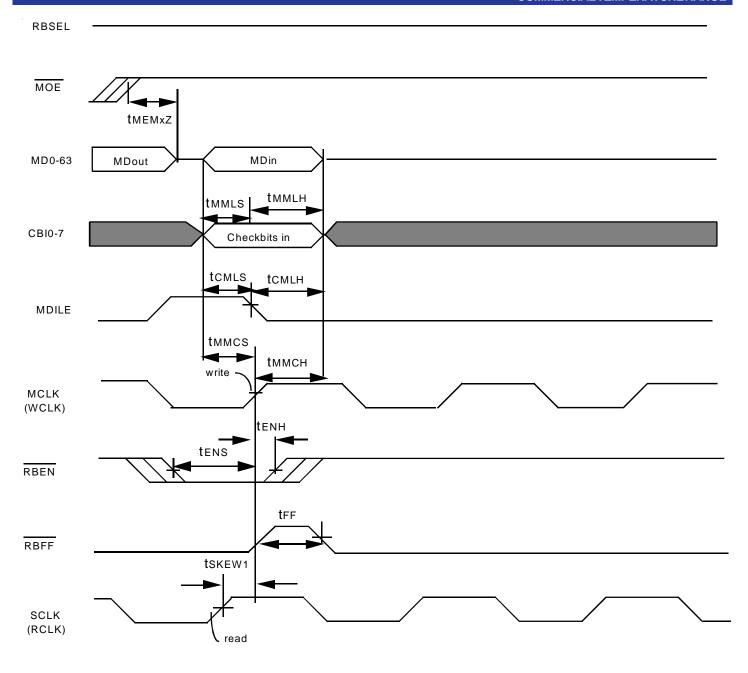

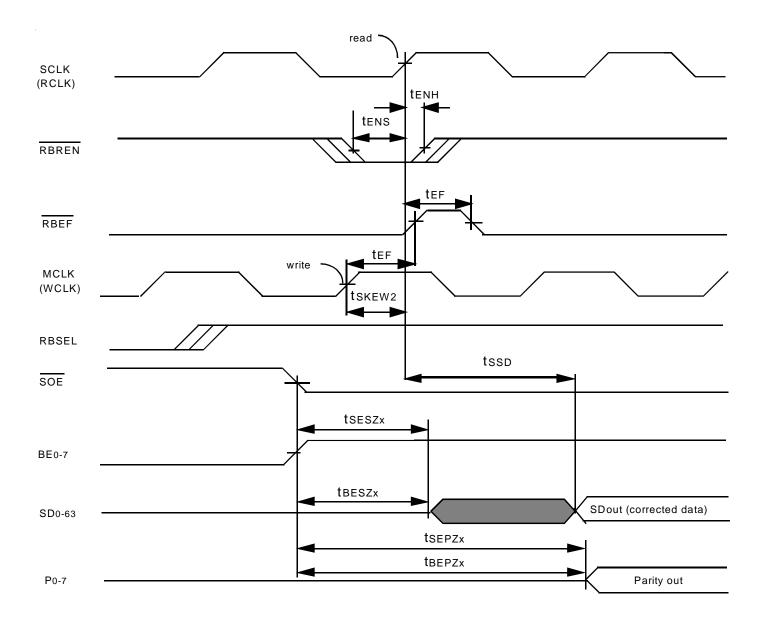

#### Memory Read

During a memory read, data and the corresponding input checkbits are read from the MD bus and CBlo-7, respectively. The memory and checkbit data may both be latched as they come in (MD Latch In and MD Checkbit latch) by the MDILE signal. Memory data is sent to the MD checkbit generator (where checkbits corresponding to the input data are generated) and to the error correct circuitry. The generated checkbits are X-ORed with the input checkbits to produce the syndrome word. This is sent to the error correction circuitry which generates the corrected data (normal mode). The corrected data is output to the SD bus via either of two data paths. When RBSEL is LOW, data flows through MD Latch Out. Pulling  $\overline{\text{MDOLE}}$  HIGH latches this data. The output buffer is enabled by asserting  $\overline{\text{SOE}}$  (=0) and BE0-7 (=1). Corrected data can be written back to memory by enabling the MD output buffer. In order to ensure selection of the write back path (Path B in figure 1) at the byte mux, BEO-7 should be all 1's while WBSEL = 0. If WBSEL = 1, buffered BEO-7 from the output of the write FIFO controls the byte mux.

If the read FIFO (RFIFO) is selected (RBSEL HIGH), data is clocked into the FIFO (Read\_FIFO Write) when  $\overline{RBEN}$  is LOW, on the rising edge of MCLK.  $\overline{RBFF}$  is asserted when the RFIFO is full and this inhibits further write attempts to the RFIFO (see section on "Clock Skew" and "R/W FIFO operation at Boundaries"). Data is clocked out of the FIFO (Read\_FIFO Read) when  $\overline{RBREN}$  is LOW on the rising edge of SCLK.  $\overline{RBEF}$  is asserted when the RFIFO is empty and this inhibits further read attempts (see section on "Clock Skew") from the RFIFO.

**Note**: In case of multiple error, SD should be ignored in correct mode.

#### Clock Skew

A skew between the read and write clocks, as specified by tskew, is recommended. This specification is not a stringent one, in the manner of setup and hold times, but is important in preempting latencies at FIFO boundaries. For example – When a word is written to an empty FIFO, there is a finite delay before the FIFO is recognized as no longer being empty and hence allowing a read from the same FIFO. Similarly when a word is read from a full FIFO, there is a delay before a write can successfully be attempted. The tskew specification accounts for these cases. During cycles other than on full/empty FIFO boundaries, the clock skew is not required and the device functions correctly even when the reads and writes occur simultaneously. If the tskew specification is ignored and SCLK and MCLK were permanently tied together, there is an extra cycle latency in the cases mentioned above. Clock skew violation is illustrated in Figure 13.

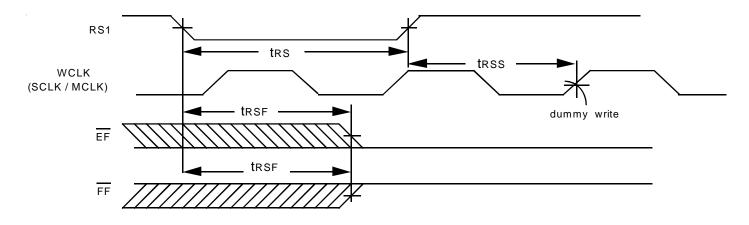

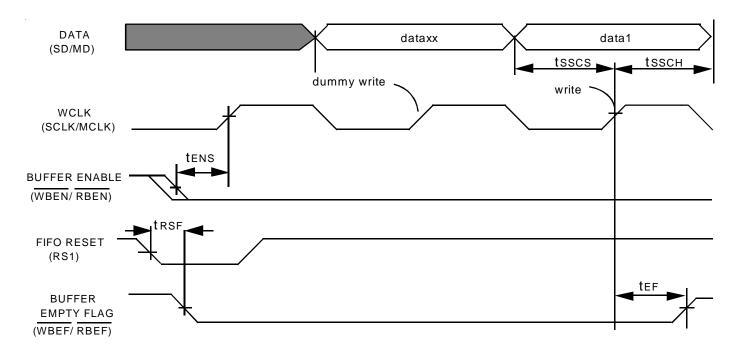

## FIFO Write Latency

The first data written to either of the (read or write) FIFOs, after the FIFO is reset, suffers a single clock latency. Data that is set-up with respect to the first clock is ignored and the data that is set-up with respect to the second clock edge after the reset, is stored as the first data in the FIFO (Refer to Figures 9 and 10). The empty-flag is deasserted after this second clock edge and 15 more data words (in a 16 deep configuration) can be written to the FIFO after this.

The latency can be reduced or eliminated by providing a "dummy" or "set-up" clock edge before the actual write to the FIFO. The dummy write clock can be provided any time after reset and before the next buffer write operation takes place. The latency described here (shown in Figures 10 and 13) occurs only after a FIFO reset. In other cases where the FIFO becomes empty there is no latency.

## R/W FIFO Operation At Boundaries

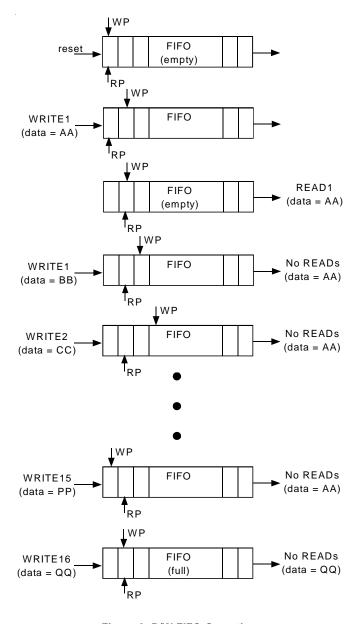

In the 49C466 the write pointer is incremented on every FIFO write. Similarly the read pointer is incremented on every FIFO read. In most cases on a FIFO read, the last data read remains at the output of the FIFO, until the read pointer is further incremented. On the last (the write that fills the FIFO) FIFO write after the FIFO read, however, this last read data is overwritten by the 16th write following the empty condition and consequently the data at the FIFO output is liable to change. The situation is depicted in the diagram below.

The diagram in figure 2 progresses from the FIFO initialization(reset) through a sequence of write operations. After the first write, a read is executed which establishes the data at the FIFO output (AA). On the last write to the FIFO(the write that fills the FIFO), the location of the last read data is overwritten and the FIFO output changes from AA to the data just written, namely QQ.

This operation needs to be taken into account in the design of the system. In case of a burst operation where FIFO data is output at a much slower rate than the rate at which data is input and the full flag is expected to inhibit further writes, the user cannot expect the FIFO output to remain static through the 16th write of the burst. If this is a requisite to the design, the FIFO output should be latched. In the case of the write FIFO this can be accomplished on-chip by latching the FIFO output in the SD output latch. For the read FIFO, the FIFO output must be latched externally to accomplish the same thing, since there is no latch on-chip following the FIFO. If this cannot be done and the situation described above is expected to occur in normal operation, the write must be inhibited one cycle before the FIFO becomes full.

Figure 2. R/W FIFO Operation

## Partial Word Write/Byte Merge

Writing a word shorter than 64 bits to memory is treated as a special case. The checkbits generated for a data word shorter than 64 bits and written to a particular memory location differ from the checkbits that would be generated by the entire 64-bit data word at the same location. Hence, the byte merge operation requires reading of the contents of the memory location to be written to, merging the byte/bytes being written (from SD side) with the other component bytes previously at that memory location (from MD side), generating a checkbit word for this composite word and writing both the composite data word and the generated checkbits to memory. The BEn bits supplied by the user determine the bytes that come from SD and those that come from MD, as illustrated in Figure 1.

#### **EDC Modes**

The IDT49C466 has five modes of operation. Refer to the Operating Mode Description table for a description of the modes.

The **Error Data Output** mode is useful for memory initialization as described below. In **Checkbit Injection mode**, the MD Checkbit Latch is loaded with data from the System Bus. This serves to verify the functioning of the EDC. Any discrepancy between the injected checkbits and generated checkbits should result in assertion of the  $\overline{\text{ERR}}$ ,  $\overline{\text{MERR}}$  signals.

These modes and certain other features such as clear, buffer configuration, etc., can be selected by appropriately loading the Mode Register. The Mode Register can be written to by asserting  $\overline{\text{MEN}}$ . Then SD0-15 is clocked into the mode register on the rising edge of SCLK.

# MODE REGISTER CONFIGURATION

| 15     | 7 6   | 5    | 4    | 3     | 2       | 0 |

|--------|-------|------|------|-------|---------|---|

| UNUSED | RMODE | PSEL | RWBD | CLEAR | EDCM0-2 |   |

| EDCM2 | EDCM1 | EDCM0 | OPERATION                                                                                              |

|-------|-------|-------|--------------------------------------------------------------------------------------------------------|

| 0     | 0     | 0     | ERROR-DATA OUTPUT MODE DIAGNOSTIC-OUTPUT MODE GENERATE-DETECT MODE NORMAL MODE CHECKBIT-INJECTION MODE |

| 0     | 0     | 1     |                                                                                                        |

| 0     | 1     | 0     |                                                                                                        |

| 0     | 1     | 1     |                                                                                                        |

| RMODE | OPERATION                    |

|-------|------------------------------|

| 0     | NOP                          |

| 1     | READ MODE REGISTER ON SD BUS |

| RWBD | OPERATION        |

|------|------------------|

| 0    | DUAL FIFOS (8)   |

| 1    | SINGLE FIFO (16) |

| CLEAR | OPERATION                      |

|-------|--------------------------------|

| 0     | NOP                            |

| 1     | CLEAR ALL DIAGNOSTIC REGISTERS |

|        | •                         |

|--------|---------------------------|

| PSEL   | OPERATION                 |

| 0<br>1 | EVEN PARITY<br>ODD PARITY |

## OPERATING MODE DESCRIPTION

| Mode   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODE 0 | <b>Error-Data Output Mode:</b> This mode allows the uncorrected data captured from an error event by the Error-Data Register to be read by the system for diagnostic purposes. The Error-Data Register is cleared by setting the mode register "clear"-bit.                                                                                                                                                                                                                                                                                                                  |

| MODE 1 | <b>Diagnostic-Output Mode:</b> In this mode, contents of latch and five internal registers are read by the system for diagnostic and error logging purposes. Internal data paths allow output from the CBI LATCH to be read directly by the system bus for diagnostic purposes. The contents of the internal diagnostic checkbit register, syndrome registers, error count register and error-type register are also output on the SD bus.                                                                                                                                   |

| MODE 2 | <b>Generate-Detect Mode:</b> (Detect-Only) The EDC performs checkbit generation during a memory write, and performs error detection only during a memory read.                                                                                                                                                                                                                                                                                                                                                                                                               |

| MODE 3 | Normal Mode: The EDC performs checkbit generation during memory writes and error detection and correction during memory reads.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| MODE 4 | Checkbit-Injection Mode: In this mode, the checkbit latch is loaded with desired 8-bit data from the SD bus. This eight bit data passes through SD Latch in or write FIFO to the MD check bit latch. By inserting various checkbit values, correct functioning of the EDC can be verified "onboard". The rest of the operation is similar to regular memory reads. The EDC compares the injected checkbits against the internally generated checkbits. Any discrepancy in the injected checkbits and the internally generated checkbits will cause the ERR / MERR to go LOW. |

# **Memory Initialization**

Memory initialization involves clearing all memory data locations and writing the corresponding checkbits (checkbits corresponding to all zero data = \$0C) to checkbit memory. This can be done using the 49C466 to first create an "all-zero-data" source. This is done by setting the CLEAR bit in the mode register. This clears all diagnostic registers. Then this data can be written back to memory in the Error-Data output (Mode 0) mode. In order to wrap the all-zero data back to the MD bus, BE0-7 should be high and WBSEL =0.

Fig 3. Memory Initialization using Diagnostic Output/Error Data Output Mode

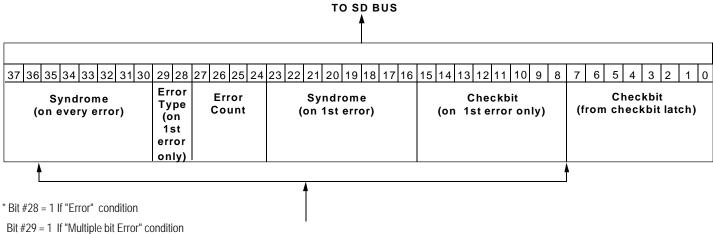

# DIAGNOSTIC OUTPUT DATA FORMAT

#### FROM DIAGNOSTIC REGISTERS

#### **Diagnostics**

The diagnostic ability of the IDT49C466 rests on a set of 6 registers that provide error logging information. These include the checkbit register, error count register, error type register, two syndrome registers and the error data register. Data is clocked into each of these registers by SYNCLK. The error data register, checkbit register, error type register and one of the syndrome registers are reloaded only in the case of the first error after a clear. The other syndrome register and the error count register are reloaded on every error condition SYNCLK edge. The contents of the Error Data register can be read only in Error Data Output mode. The contents of the other diagnostic registers as well as the checkbit latch can be read in Diagnostic Output mode.

#### **Parity**

The IDT49C466 provides a parity check and generation facility. On a memory read the EDC generates parity bits for each data byte and outputs the parity byte on the parity bus, P0-7. During a memory write, parity is checked by comparing the parity bits input on P0-7 and the parity bits generated from the input data word. A discrepancy between these two causes the PERR flag to be asserted. In the case of partial word writes, the PERR flag is based on the parity bits Px and data bytes input on SD bus.

| DIAG.<br>REGISTER               | LOADED<br>BY | CONDITION                              | ОИТРИТ  |

|---------------------------------|--------------|----------------------------------------|---------|

| CHECKBIT                        | SYNCLK ↑     | ONLY ON 1st<br>ERROR                   | SD8-15  |

| SYNDROME<br>(On 1st ERR)        | SYNCLK↑      | ONLY ON 1st<br>ERROR                   | SD16-23 |

| ERR CNT                         | SYNCLK ↑     | ON EVERY<br>ERROR (Up to<br>15 ERRORS) | SD24-27 |

| ERR TYPE                        | SYNCLK↑      | ONLY ON 1st<br>ERROR                   | SD28-29 |

| SYNDROME<br>(On every<br>ERROR) | SYNCLK ↑     | ON EVERY<br>ERROR                      | SD30-37 |

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol | Rating                                     | Com'l.               | Unit |

|--------|--------------------------------------------|----------------------|------|

| Vcc    | Power Supply Voltage                       | -0.5 to +7           | V    |

| VTERM  | Terminal Voltage with<br>Respect to Ground | -0.5 to<br>Vcc + 0.5 | V    |

| TBIAS  | Temperature Under Bias                     | -55 to +125          | °C   |

| Tstg   | Storage Temperature                        | -55 to +125          | °C   |

| Іоит   | DC Output Current                          | 30                   | mA   |

#### NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to Absolute Maximum Ratings for extended periods of time may affect reliability.

## CAPACITANCE (TA = +25°C, f = 1.0 MHz)

| Symbol | Parameter <sup>(1)</sup> | Conditions |      | Тур. | Unit |

|--------|--------------------------|------------|------|------|------|

| CIN    | Input                    | VIN = 0V   | PQFP | 5    | pF   |

|        | Capacitance              |            |      |      |      |

| Соит   | Output                   | Vout = 0V  | PQFP | 7    | pF   |

|        | Capacitance              |            |      |      |      |

#### NOTE:

1. This parameter is sampled and not 100% tested.

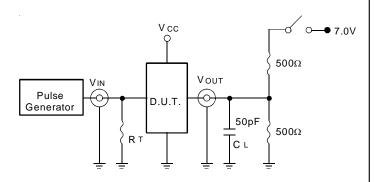

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

The following conditions apply unless otherwise specified:

Commercial: TA =  $0^{\circ}$ C to +70°C, Vcc = 5.0V ± 5%

| Symbol | Parameter                     | Test Cond                              | ditions <sup>(1)</sup> | Min. | Typ. <sup>(2)</sup> | Max. | Unit |

|--------|-------------------------------|----------------------------------------|------------------------|------|---------------------|------|------|

| VIH    | Input HIGH Level              | Guaranteed Logic HIGH Level            |                        | 2    | _                   | _    | V    |

| VIL    | Input LOW Level               | Guaranteed Logic LOW Level             |                        | _    | _                   | 0.8  | V    |

| Іін    | Input HIGH Current            | VCC = Max., VIN = 2.7V                 |                        |      | 0.1                 | 5    | μA   |

| lıL    | Input LOW Current             | VCC = Max., VIN = 0.5V                 | Vcc = Max., Vin = 0.5V |      | -0.1                | -5   | μΑ   |

| loz    | Off State (Hi-Z)              | Vcc = Max.                             | Vo = 0V                | _    | -0.1                | -10  | μA   |

|        | Output Current                |                                        | Vo = 3V                |      | 0.1                 | 10   |      |

| los    | Short Circuit Current         | Vcc = Max. <sup>(3)</sup> , Vout= 0V   |                        | -20  | _                   | -150 | mA   |

| Vон    | Output HIGH Voltage           | Vcc = Min.                             | IOH = -2mA             | 2.4  | 3.6                 | _    | V    |

|        |                               | VIN = VIH or VIL                       |                        |      |                     |      |      |

| Vol    | Output LOW Voltage            | Vcc = Min.                             | IoL = 8mA              |      | 0.3                 | 0.5  | V    |

|        |                               | VIN = VIH or VIL                       |                        |      |                     |      |      |

| VH     | Input Hysteresis on input con | nput Hysteresis on input control lines |                        |      | 200                 | _    | mV   |

#### NOTES:

- 1. For conditions shown as min. or max., use appropriate Vcc value.

- 2. Typical values are at Vcc = 5.0V, +25°C ambient temperature.

- 3. Not more than one output should be shorted at a time. Duration of the short circuit test should not exceed one second.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE (cont.)

The following conditions apply unless otherwise specified:

Commercial:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $VCC = 5.0V \pm 5\%$

| Symbol | Parameter                                          | Test Conditions <sup>(1)</sup>        | Min. | Тур.(2) | Max. | Unit         |

|--------|----------------------------------------------------|---------------------------------------|------|---------|------|--------------|

| Iccac  | Quiescent Power Supply Current                     | VIN = VCC, or VIN = GND<br>VCC = Max. | -    | 3       | 15   | mA           |