# 32-Bit Bus-Watch EDAC Error Detection And Correction unit

### 1. Description

The 29C532E EDAC is a very low power bus-watch 32-bit Error Detection And Correction unit (EDAC). EDAC is used in a high integrity system for monitoring and correcting data values coming from the memory space. Such a bus-watch EDAC is connected as a peripheral on the data bus and watches on and controls the integrity of the data memory.

During a processor write cycle, at each memory location (32-bit width), EDAC calculated checkword (7 or 8-bit width) is added. When performing a read operation from memory, the 29C532E verifies the entire checkword and data combination. It detects and can correct 100% of all the single-bit errors and it detects all multi-bit errors but can not correct them. All the errors are reported to the master system to allow the processor to take action as required. In case of single-bit error, the Correctable ERRor flag is set and the single-bit in error is complemented (corrected). Then, the data can be

substituted to the corrupted data on the system data bus. In case of multi-bit error, the Non-Correctable ERRor flag is set, the data can not be repaired. Note that when multi-bit errors occur, there are some bit patterns which may appear as possible correctable errors. Therefore, if the environment produces this type of error, the EDAC must be used in detect-only-without-correction configuration. Data and syndrome analysis must be rapidly done.

Because the 29C532E latches the data, byte or 16-bit word write operations are possible if they take place in a read-modify-write accesses to the memory space.

When the 29C532E uses 7-checkbit, it can detect any errors on any single 1 or 4-bit memory chip. The 8-checkbit option gives the additional capability to detect all errors on any 8-bit memory chip.

### 2. Features

- 32-bit Operation (7 or 8 Check Bits)

- Bus Watch Architecture

- Fast Error Detection: 32 ns

- Fast Error Correction: 39 ns

- Corrects All Single-Bit Errors

Detects All Double-Bit Errors

Detects Some Multi-Bit Errors

Detects Chip Error (x1, x4 & x8 RAM Format)

- Correctable and Non-Correctable Error Flags

- Very Low Power CMOS

- TTL Compatible

- Single  $5V \pm 10\%$  Power Supply

- High Drive Capability on Bus: 12.8 mA

- 100-Pin Multi-Layer Quad Flatpack

### 3. Interface

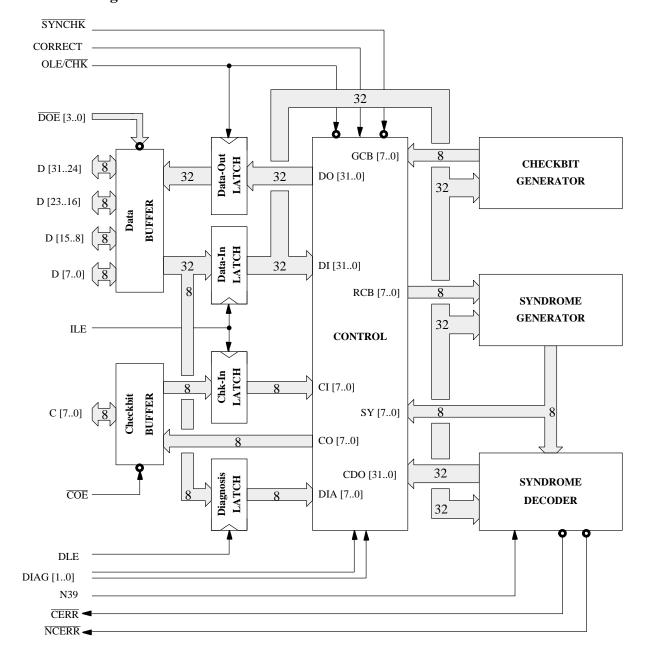

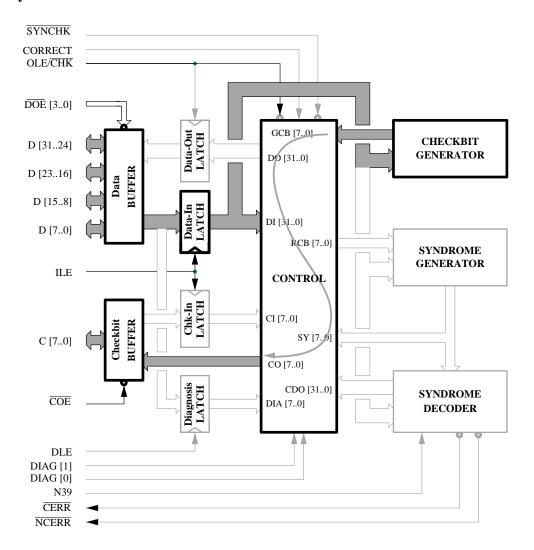

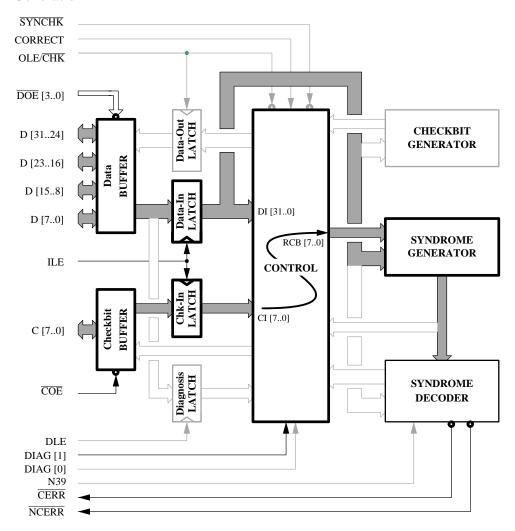

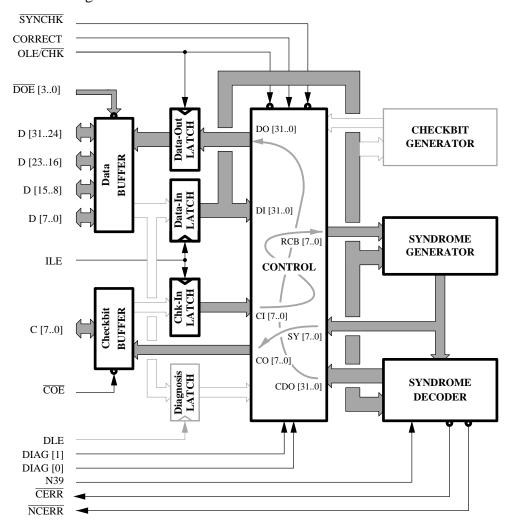

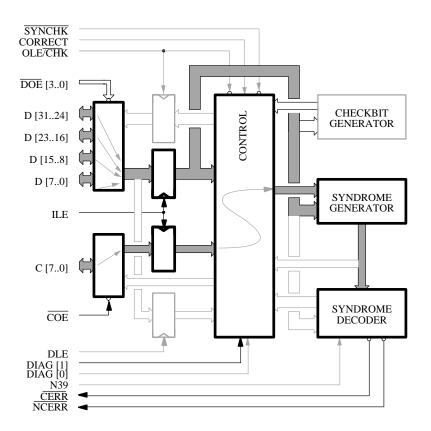

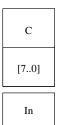

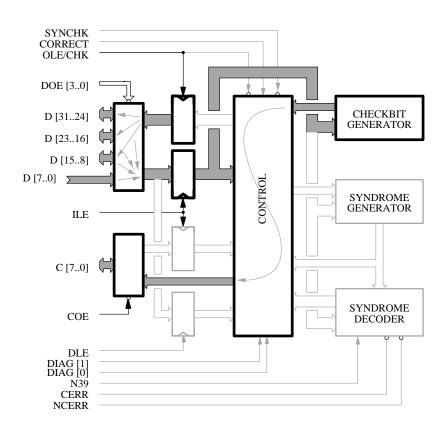

### 3.1. Block Diagram

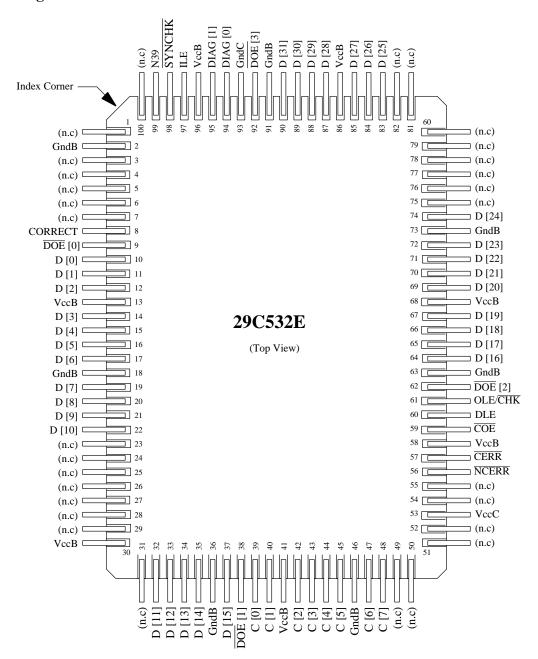

### 3.2. Pin Configuration

Rev. B-26 February, 1997

3

### **Preliminary Information**

### 3.3. Pin Description

| Name     | Pin Nb.                           | I/O | Active |                | Description                                                                                                                    |

|----------|-----------------------------------|-----|--------|----------------|--------------------------------------------------------------------------------------------------------------------------------|

| Buses    | •                                 |     |        |                |                                                                                                                                |

| D [3124] | 90, 89, 88, 87,<br>85, 84, 83, 74 |     |        |                |                                                                                                                                |

| D [2316] | 72, 71, 70, 69,<br>67, 66, 65, 64 | I/O |        |                | s. put data on D [3124] bus is controlled by <del>DOE</del> [3]. put data on D [2316] bus is controlled by <del>DOE</del> [2]. |

| D [158]  | 37, 35, 34, 32,<br>31, 22, 21, 20 | 1/0 | -      | Out            | put data on D [158] bus is controlled by $\overline{DOE}$ [1]. put data on D [70] bus is controlled by $\overline{DOE}$ [0].   |

| D [70]   | 19, 17, 16, 15,<br>14, 12, 11, 10 |     |        |                |                                                                                                                                |

| C [70]   | 48, 47, 45, 44,<br>43, 42, 40, 39 | I/O | -      | Checkbi<br>Out | t bus. put checkbit on C [70] bus is controlled by $\overline{\text{COE}}$ .                                                   |

| Flags    |                                   |     |        |                |                                                                                                                                |

| CERR     | 57                                | О   | Low    | Correcta       | able ERror.                                                                                                                    |

| NCERR    | 56                                | О   | Low    | UnCorre        | ectable ERror.                                                                                                                 |

| Controls |                                   |     |        |                |                                                                                                                                |

| DOE [3]  | 9                                 |     |        | Data Ou        | tput Enable for D [3124] bus.                                                                                                  |

| DOE [2]  | 38                                | I   | Low    | Data Ou        | tput Enable for D [2316] bus.                                                                                                  |

| DOE [1]  | 62                                | 1   | Low    | Data Ou        | tput Enable for D [158] bus.                                                                                                   |

| DOE [0]  | 92                                |     |        | Data Ou        | tput Enable for D [70] bus.                                                                                                    |

| COE      | 59                                | I   | Low    | Checkbi        | t Output Enable for C [70] bus.                                                                                                |

| OLD FINE |                                   |     |        | OLE            | Output Latch Enable for DO [310] internal bus: 1: transparent, 0: latched.                                                     |

| OLE/CHK  | 61                                | I   | H/L    | СНК            | CHecKbit enable. Only if DIAG [0] = 0 (non active):<br>0: CO [70] = GCB [70].<br>1: CO [70] = SY [70].                         |

| ILE      | 97                                | I   | High   |                | atch Enable to produce DI [310] and CI [70] internal buses respectively [310] and C [70]: 1: transparent, 0: latched.          |

| DLE      | 60                                | I   | High   | Diagnos        | is Latch Enable to produce DIA [70] internal bus from D [70] bus:  1: transparent,  0: latched.                                |

| Name               | Pin Nb.                       | I/O | Active   | Description                                                                                                                  |

|--------------------|-------------------------------|-----|----------|------------------------------------------------------------------------------------------------------------------------------|

| Controls           |                               | •   | •        |                                                                                                                              |

|                    |                               |     |          | SYNdrome & CHecKbit enable. During a read mode: 0: DO [3124] = DIA [70],                                                     |

|                    |                               |     |          | DO [2316] = SY [70],                                                                                                         |

| SYNCHK             | 98                            | I   | Low      | DO [158] = CI [70],                                                                                                          |

|                    |                               |     |          | DO [70] = DIA [70].                                                                                                          |

|                    |                               |     |          | 1: DO [310] = CDO [310].                                                                                                     |

| CORRECT            | 8                             | I   | High     | CORRECTion enable. Only if <u>SYNCHK</u> = 1 (non active):<br>1: DO [310] = CDO [310].<br>0: DO [310] = DI [310].            |

| N39                | 99                            | I   | High     | Code leNgth equals 39:  1: the EDAC uses 7 check bits.  0: the EDAC uses 8 check bits.                                       |

| DIAG [1]           | 95                            |     |          | DIAGnosis mode 1. Diagnosis detect & correct:  1: RCB [70] = DIA [70].  0: RCB [70] = CI [70].                               |

| DIAG [0]           | 94                            | I   | High     | DIAGnosis mode 0. Diagnosis generate:  1: CO [70] = DIA [70].  0: CO [70] = SY [70] or GCB [70] following the OLE/CHK value. |

| Power (Buffers)    |                               |     | <u> </u> |                                                                                                                              |

| VccB               | 13, 30, 41, 58,<br>68, 86, 96 | -   | -        | Buffers supply (5V nominal)                                                                                                  |

| $Gnd_{B}$          | 2, 18, 36, 46,<br>63, 73, 91  | -   | -        | Buffers 0V reference                                                                                                         |

| Power (Core)       |                               |     |          |                                                                                                                              |

| VccC               | 53                            | -   | -        | Core supply (5V nominal)                                                                                                     |

| $Gnd_{\mathbb{C}}$ | 93                            | -   | -        | Core 0V reference                                                                                                            |

All I/O and I buffers have a pull-up resistor  $\simeq$  100  $\Omega$

### 4. Checkbit Generation

The checkbit generator produces 8 checkbits (whatever N39 value) from the incoming data DI [31..0] according the following table.

Table 1: Checkbit generation (x indicates bit of D [31..0] used in the parity calculation)

| GCB  | Parity        |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Γ  | )I [3 | 310 | ]  |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|------|---------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-------|-----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| [70] | rarity        | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16    | 15  | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0    | Even<br>(XOR) | x  | x  | x  | x  |    |    |    | x  |    |    | x  | x  | х  |    |    |       | х   |    |    |    | x  | х  | х | x |   |   | x | х |   |   | x |   |

| 1    | Even<br>(XOR) |    | x  |    | x  |    |    | х  | x  |    |    |    | x  |    |    | x  | х     | x   |    | x  | х  |    |    | х | x | х | x |   | x | х |   |   |   |

| 2    | Odd<br>(NXOR) | x  |    |    |    |    | х  |    |    |    | x  |    |    | х  | х  |    | х     | х   | x  |    |    |    | х  |   | x |   | x | x | х | х | х | x |   |

| 3    | Even<br>(XOR) | x  | x  |    |    | x  |    |    |    | x  | x  |    |    | х  |    |    |       | х   | x  | x  | х  |    | х  | х | x | х |   |   | х |   |   |   | x |

| 4    | Odd<br>(NXOR) |    | x  | x  |    | x  | х  | х  | x  |    |    | x  |    | х  |    | x  |       |     |    |    | х  |    | х  | х |   |   |   |   | х | х | х |   | x |

| 5    | Even<br>(XOR) | x  |    |    |    |    | х  | х  |    | х  |    | х  | х  |    | х  |    |       |     | х  | x  |    | х  | х  | х | х |   | x | х |   |   |   |   | x |

| 6    | Even<br>(XOR) | x  | x  | x  | х  | х  |    |    |    | x  | x  |    |    | х  | х  | X  | x     | х   |    |    |    | x  |    |   |   | х |   |   |   |   | х | x |   |

| 7    | Odd<br>(NXOR) |    |    |    |    | x  | х  | х  | х  |    | х  | х  |    |    |    | x  | х     |     | x  |    | х  | х  |    |   |   | х | x |   |   |   | х | x | x |

### **Example**

To create GCB [3], bit 31, 30, 27, 23, 22, 19, 15, 14, 13, 12, 10, 9, 8, 7, 4 and 0 of DI [31..0] are 3ORed together.If SRAM devices 1 or 4-bit are used in a memory system controlled by the 29C532E EDAC, it is only necessary to

store 39 bits (D [31..0] & C [6..0]).If SRAM devices 8-bit are used in a memory system controlled by the 29C532E EDAC, 40 bits (D [31..0] & C [7..0]) must be stored.

### **5. Syndrome Generation**

The syndrome generator produces 8 syndrome-bits (whatever N39 value) from the incoming data DI [31..0] and the associated checkbit RCB [7..0] (via CI [7..0] or DIA [7..0] following DIAG [1] value) according the following table.

Table 2: Checkbit generation (x indicates bit of D [x1..0] used in the parity calculation)

| SY   | Parity        |    |    |    |    |    |    |    |    |    | DI | [ [x1. | .0] |    |    |    |    |    |    |    |    |    |

|------|---------------|----|----|----|----|----|----|----|----|----|----|--------|-----|----|----|----|----|----|----|----|----|----|

| [70] |               | 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21     | 20  | 19 | 18 | 18 | 17 | 16 | 15 | 14 | 1x | 12 |

| 0    | Even (XOR)    | X  | х  | х  | х  |    |    |    | х  |    |    | х      | х   | X  |    |    |    |    | X  |    |    |    |

| 1    | Even (XOR)    |    | х  |    | х  |    |    | х  | х  |    |    |        | х   |    |    |    | х  | х  | X  |    | X  | х  |

| 2    | Odd<br>(NXOR) | X  |    |    |    |    | х  |    |    |    | х  |        |     | X  | X  | х  |    | х  | X  | х  |    |    |

| 3    | Even<br>(XOR) | X  | х  |    |    | х  |    |    |    | х  | х  |        |     | X  |    |    |    |    | X  | X  | X  | x  |

| 4    | Odd<br>(NXOR) |    | х  | х  |    | х  | х  | х  | х  |    |    | х      |     | X  |    |    | х  |    |    |    |    | х  |

| 5    | Even<br>(XOR) | X  |    |    |    |    | х  | х  |    | х  |    | х      | х   |    | X  | х  |    |    |    | X  | X  |    |

| 6    | Even<br>(XOR) | x  | х  | x  | х  | х  |    |    |    | х  | х  |        |     | X  | X  | х  | х  | х  | X  |    |    |    |

| 7    | Odd<br>(NXOR) |    |    |    |    | х  | х  | х  | х  |    | х  | х      |     |    |    |    | х  | х  |    | х  |    | х  |

**Table 2: (continue)**

| SY   | Parity        |    |    |   |   |   | DI [x | x10] |   |   |   |   |   | Parity        |   |   | ] | RCB | [70] |   |   |   |

|------|---------------|----|----|---|---|---|-------|------|---|---|---|---|---|---------------|---|---|---|-----|------|---|---|---|

| [70] | Failty        | 11 | 10 | 9 | 8 | 7 | 6     | 5    | 4 | 3 | 2 | 1 | 0 | rainy         | 7 | 6 | 5 | 4   | 3    | 2 | 1 | 0 |

| 0    | Even<br>(XOR) | x  | X  | х | х |   |       | х    | х |   |   | х |   | Evn<br>(XOR)  |   |   |   |     |      |   |   | х |

| 1    | Even<br>(XOR) |    |    | х | х | х | х     |      | х | х |   |   |   | Even<br>(XOR) |   |   |   |     |      |   | х |   |

| 2    | Odd<br>(NXOR) |    | X  |   | х |   | х     | х    | х | х | х | X |   | Even<br>(XOR) |   |   |   |     |      | X |   |   |

| 3    | Even<br>(XOR) |    | х  | х | х | х |       |      | х |   |   |   | x | Even<br>(XOR) |   |   |   |     | х    |   |   |   |

| 4    | Odd<br>(NXOR) |    | х  | х |   |   |       |      | х | х | х |   | x | Even<br>(XOR) |   |   |   | х   |      |   |   |   |

| 5    | Even<br>(XOR) | х  | х  | х | х |   | х     | х    |   |   |   |   | х | Even<br>(XOR) |   |   | х |     |      |   |   |   |

| 6    | Even<br>(XOR) | х  |    |   |   | х |       |      |   |   | х | х |   | Even<br>(XOR) |   | X |   |     |      |   |   |   |

| 7    | Odd<br>(NXOR) | х  |    |   |   | х | х     |      |   |   | х | х | х | Even<br>(XOR) | х |   |   |     |      |   |   |   |

The syndrome bit SY[x] is the XOR of the received checkbit RCB[x] and the parity calculation on DI [31..0]. Example:

To create SY [1], bit 30, 28, 25, 24, 20, 17, 16, 15, 13, 12, 9, 8, 7, 6, 4 and 3 of DI [31..0] are NXORed together. Then, the result is XORed with the associated checkbit RCB [1] of the checkbit byte read at the same address than the data word DI [31..0].

If SRAM devices 1 or 4-bit are used in a memory system controlled by the 29C532E EDAC, only 39 bits (D [31..0] & C [6..0]) are checked and the generated syndrome word is 7-bit width.

If SRAM devices 8-bit are used in a memory system controlled by the 29C532E EDAC, 40 bits (D [31..0] & C [7..0]) are checked, the generated syndrome word is 8-bit width.

### 6. Syndrome Decoding

The syndrome decoder generates the error flags  $\overline{CERR}$ (Correctable ERror) and NCERR (Non-Correctable ERror). It mainly provides corrected data word to the system bus if a correctable error occurs.

In case of single bit-error, using the syndrome value, this block decodes which bit is in error and complements it to correct the data word. This correction is only made on the 32 bits of data not on the checkbit word.

The inputs of the syndrome decoder are:

- the 32 bits of data coming from the system data bus,

- the syndrome coming from the syndrome generator,

- the control signal N39. N39 signal controls if 39 or 40 bits will be decoded from the entire word.

Rev. B – 26 February, 1997

Table 3: 7-bit syndrome word to bit-in-error (N39=1)

|     |               |     |   | hex |   | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7 |

|-----|---------------|-----|---|-----|---|-------|-------|-------|-------|-------|-------|-------|---|

| S   | yndro         | ome |   |     | 7 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 |

| 9   | bit<br>SY [7. | 01  |   |     | 6 | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1 |

|     | J             | 01  |   |     | 5 | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1 |

| hex | 3             | 2   | 1 | 0   | 4 | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1 |

| 0   | 0             | 0   | 0 | 0   |   | N.E.D | C [4] | C [5] |       | C [6] |       | D[11] |   |

| 1   | 0             | 0   | 0 | 1   |   | C [0] |       |       | D[21] |       | D[29] |       |   |

| 2   | 0             | 0   | 1 | 0   |   | C [1] |       |       | D[25] |       | D[17] |       |   |

| 3   | 0             | 0   | 1 | 1   |   |       | D[24] | D[20] |       | D[28] |       |       |   |

| 4   | 0             | 1   | 0 | 0   |   | C [2] |       |       | D[26] |       | D[2]  | D[18] |   |

| 5   | 0             | 1   | 0 | 1   |   |       |       | D[5]  |       | D[1]  |       |       |   |

| 6   | 0             | 1   | 1 | 0   |   |       | D[3]  | D[6]  |       | D[16] |       |       |   |

| 7   | 0             | 1   | 1 | 1   |   |       |       |       |       |       |       |       |   |

| 8   | 1             | 0   | 0 | 0   |   | C [3] |       |       | D[0]  |       | D[27] | D[23] |   |

| 9   | 1             | 0   | 0 | 1   |   |       |       |       |       |       |       |       |   |

| A   | 1             | 0   | 1 | 0   |   |       | D[12] | D[13] |       | D[7]  |       |       |   |

| В   | 1             | 0   | 1 | 1   |   |       |       |       | D[9]  |       | D[30] |       |   |

| С   | 1             | 1   | 0 | 0   |   |       |       | D[14] |       | D[22] |       |       |   |

| D   | 1             | 1   | 0 | 1   |   |       |       |       | D[10] |       | D[19] | D[31] |   |

| Е   | 1             | 1   | 1 | 0   |   |       |       |       |       |       |       |       |   |

| F   | 1             | 1   | 1 | 1   |   |       | D[4]  | D[8]  |       | D[15] |       |       |   |

Note:

N.E.D

=

No Error Detected,

D [x] =

Data bit-in-error,

C [x] =

Check bit-in-error

=

Multi-bit-in-error

Rev. B – 26 February, 1997

9

## **Preliminary Information**

Table 4: 8-bit syndrome word to bit-in-error (N39=0)

|     |     |    |    | hex | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7 | 8     | 9     | A     | В     | С     | D     | Е     | F |

|-----|-----|----|----|-----|-------|-------|-------|-------|-------|-------|-------|---|-------|-------|-------|-------|-------|-------|-------|---|

| Syn | dre | om | ne | 7   | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0 | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1 |

| SY  | bit | t  |    | 6   | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1 | 0     | 0     | 0     | 0     | 1     | 1     | 1     | 1 |

| 51  | Ľ   | 0  | J  | 5   | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1 | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1 |

| hex | 3   | 2  | 1  | 0 4 | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1 | 0     | 1     | 0     | 1     | 0     | 1     | 0     | 1 |

| 0   | 0   | 0  | 0  | 0   | N.E.D | C [4] | C [5] |       | C [6] |       |       |   | C [7] |       |       |       |       |       | D[11] |   |

| 1   | 0   | 0  | 0  | 1   | C [0] |       |       |       |       | D[29] |       |   |       |       |       | D[21] |       |       |       |   |

| 2   | 0   | 0  | 1  | 0   | C [1] |       |       |       |       |       |       |   |       |       |       | D[25] |       | D[17] |       |   |

| 3   | 0   | 0  | 1  | 1   |       |       | D[20] |       | D[28] |       |       |   |       | D[24] |       |       |       |       |       |   |

| 4   | 0   | 1  | 0  | 0   | C [2] |       |       |       |       |       | D[18] |   |       |       |       | D[26] |       | D[2]  |       |   |

| 5   | 0   | 1  | 0  | 1   |       |       | D[5]  |       |       |       |       |   |       |       |       |       | D[1]  |       |       |   |

| 6   | 0   | 1  | 1  | 0   |       | D[3]  |       |       |       |       |       |   |       |       | D[6]  |       | D[16] |       |       |   |

| 7   | 0   | 1  | 1  | 1   |       |       |       |       |       |       |       |   |       |       |       |       |       |       |       |   |

| 8   | 1   | 0  | 0  | 0   | C [3] |       |       |       |       |       | D[23] |   |       |       |       | D[0]  |       | D[27] |       |   |

| 9   | 1   | 0  | 0  | 1   |       |       |       |       |       |       |       |   |       |       |       |       |       |       |       |   |

| A   | 1   | 0  | 1  | 0   |       |       | D[13] |       |       |       |       |   |       | D[12] |       |       | D[7]  |       |       |   |

| В   | 1   | 0  | 1  | 1   |       |       |       | D[9]  |       | D[30] |       |   |       |       |       |       |       |       |       |   |

| С   | 1   | 1  | 0  | 0   |       |       |       |       |       |       |       |   |       |       | D[14] |       | D[22] |       |       |   |

| D   | 1   | 1  | 0  | 1   |       |       |       | D[10] |       | D[19] | D[31] |   |       |       |       |       |       |       |       |   |

| Е   | 1   | 1  | 1  | 0   |       |       |       |       |       |       |       |   |       |       |       |       |       |       |       |   |

| F   | 1   | 1  | 1  | 1   |       | D[4]  | D[8]  |       | D[15] |       |       |   |       |       |       |       |       |       |       |   |

Note: N.E.D = No Error Detected,

D[x] = Data bit-in-error,

C[x] = Check bit-in-error

= Multi-bit-in-error

### 7. 7-Bit Syndrome Word

This feature is available when the N39 pin is driven at a high level.

#### 7.1. No Error

If there is no error in the read data or checkbit, all the syndrome word is "00". The EDAC flags are inactive.

| No Error | SY= 0x00 |

|----------|----------|

|----------|----------|

### 7.2. Single Bit-In-Error

When the Memory Data word (D [31..0] & C[6..0]) read has one bit-in-error, the 20C532E EDAC develops a code (syndrome) which indicates the bit in error (each bit have its own syndrome value). In this case, the syndrome decoder sets low the correctable error flag  $\overline{\text{CERR}}$ , but  $\overline{\text{NCERR}}$  flag remains at high level.

In case of single bit-error on D [31..0], if the control lines  $\overline{SYNCHK}$  = non active and CORRECT = active, the

corrected value (CDO [31..0]) is available on DO [31..0] internal bus and the syndrome word is available on CO [6..0]. The corrected value is obtains to complement the bit-in-error.

In same conditions, if a single bit-error occurs on C [6..0], the corrected value of the checkbit is not available in the device.

Table 5: 7-bit syndrome word for single bit-error.

| D[3116] | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| SY      | 0x6D | 0x5B | 0x51 | 0x4x | 0x58 | 0x34 | 0x32 | 0x13 | 0x68 | 0x4C | 0x31 | 0x23 | 0x5D | 0x64 | 0x52 | 0x46 |

|         |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| D[150]  | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| SY      | 0x4F | 0x2C | 0x2A | 0x1A | 0x60 | 0x3D | 0x3B | 0x2F | 0x4A | 0x26 | 0x25 | 0x1F | 0x16 | 0x54 | 0x45 | 0x38 |

| C[70] | - | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|---|------|------|------|------|------|------|------|

| SY    |   | 0x40 | 0x20 | 0x10 | 0x08 | 0x04 | 0x02 | 0x01 |

### 7.3. Double Bit-In-Error

When the Memory Data word (D [31..0] & C[6..0]) read has two bit-in-error, the 20C532E EDAC develops a syndrome different of 0x00. The syndrome value generated by a double bit-in-error never takes place of a syndrome value generated by a single bit-in-error. In this case, the syndrome decoder sets low the non correctable

error flag  $\overline{NCERR}$  and  $\overline{CERR}$  flag remains at high level. Example :

If data D [12] and D [9] are incorrect, syndrome bit SY [5] and SY [0] are set to one (SY= 0x21),  $\overline{NCERR}$  flag is set low ( $\overline{CERR}$  flag remains at high level).

### 7.4. Triple Bit-In-Error

When the Memory Data word (D [31..0] & C[6..0]) read has three bit-in-error, the 20C532E EDAC develops a syndrome different of 0x00. The syndrome value

generated by a triple bit-in-error can have any value, even a syndrome value normally generated by a single

bit-in-error.  $\overline{NCERR}$  flag or  $\overline{CERR}$  flag can be activated following the value of the generated syndrome.

#### Example:

If data D [28], D [18] and D [1] are incorrect, syndrome bit SY [6], SY [5] and SY [1] are set to one (SY= 0x62), NCERR flag is set low (CERR flag remains at high level). Fault example:

If data D [24], D [12] and D [3] are incorrect, syndrome bits SY [4..0] are set to one (SY= 0x1F). The syndrome is decoded by the 29C532E EDAC has being a correctable error on D [4]. Then,  $\overline{\text{CERR}}$  flag is set low and  $\overline{\text{NCERR}}$  flag remains at high level. A correction would cause more errors.

### 7.5. Multi Bit-In-Error

When the Memory Data word (D [31..0] & C[6..0]) read has four or more bit-in-error, the 20C532E EDAC develops a non controlled syndrome. This syndrome can take any value, from 0x00 (No Error Detected) to specific syndrome value of single bit-in-error.

#### Example:

If the data read = 0x00000000 instead of 0xFFFFFFFF, the generated syndrome is 0x00. Then, no error flag is actived.

### 7.6. 4-Bit Wide Memory Error

The 7 checkbit code can be used to provide error detection for up to four errors occurring in the following fields:

- D [31..28],

- D [27..24],

- D [23..20],

- D [19..16],

- D [15..12],

- D [11..8],

- D [7..4],

- D [3..0],

- C [6..4],

- C [3..0].

The 29C532E EDAC can flag any number of errors in 4-bit wide memory chip. If the one device returns from one to four bit-in error, the CERR and NCERR flags are generated following the error type and the generated syndrome takes a value which never overlaps the code of a single bit-in-error. This is a restriction to triple and multi bit-in-error.

#### Example:

If the device controlling D [23..20] generates error, the 15 possible codes are different of 0x00 and of those describing a single bit-in-error.

| Bit in error | 23   | 22   | 21   | 20   | 23<br>22 | 23<br>21 | 23<br>20 | 22<br>21 | 22<br>20 | 21<br>20 | 23<br>22<br>21 | 23<br>22<br>20 | 23<br>21<br>20 | 22<br>21<br>20 | 23<br>22<br>21<br>20 |

|--------------|------|------|------|------|----------|----------|----------|----------|----------|----------|----------------|----------------|----------------|----------------|----------------------|

| SY           | 0x68 | 0x4C | 0x31 | 0x23 | 0x24     | 0x59     | 0x4B     | 0x7D     | 0x67     | 0x12     | 0x15           | 0x07           | 0x00           | 0x7A           | 0x36                 |

| CERR         | х    | х    | х    | Х    | -        | -        | -        | -        | -        | -        | -              | -              | -              | -              | -                    |

| NCERR        | -    | -    | -    | -    | Х        | Х        | Х        | Х        | Х        | Х        | Х              | Х              | Х              | Х              | х                    |

### 8. 8-Bit Syndrome Word

This feature is available when the N39 pin is driven at a low level.

### 8.1. No Error

12

If there is no error in the read data or checkbit, all the syndrome word is "00". The EDAC flags are inactive.

| No Error S | SY = 0x00 |

|------------|-----------|

|------------|-----------|

Rev. B – 26 February, 1997

### 8.2. Single Bit-In-Error

When the Memory Data word (D [31..0] & C[7..0]) read has one bit-in-error, the 20C532E EDAC develops a code (syndrome) which indicates the bit in error (each bit have its own syndrome value). In this case, the syndrome decoder sets low the correctable error flag  $\overline{\text{CERR}}$ , but  $\overline{\text{NCERR}}$  flag remains at high level.

In case of single bit-error on D [31..0], if the control lines  $\overline{SYNCHK}$  = non active and CORRECT = active, the

corrected value (CDO [31..0]) is available on DO [31..0] internal bus and the syndrome word is available on CO [7..0]. The corrected value is obtains to complement the bit-in-error.

In same conditions, if a single bit-error occurs on C [7..0], the corrected value of the checkbit is not available in the device.

Table 6: 8-bit syndrome word for single bit-error.

| D[3116] | 31   | 30   | 29   | 28   | 27   | 26   | 25   | 24   | 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   |

|---------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| SY      | 0x6D | 0x5B | 0x51 | 0x43 | 0xD8 | 0xB4 | 0xB2 | 0x93 | 0x68 | 0xCC | 0xB1 | 0x23 | 0x5D | 0x64 | 0xD2 | 0xC6 |

|         | I    | I    | I    | I    | I    | I    | I    |      | I    |      |      |      | I    | I    |      |      |

| D[150]  | 15   | 14   | 1x   | 12   | 11   | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| SY      | 0x4F | 0xAC | 0x2A | 0x9A | 0xE0 | 0x3D | 0x3B | 0x2F | 0xCA | 0xA6 | 0x25 | 0x1F | 0x16 | 0x54 | 0xC5 | 0xB8 |

|         | •    | •    | •    | •    | •    | •    | •    |      | •    |      |      |      | •    | •    |      |      |

| C[70]   | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |      |      |      |      |      |      |      |

| SY      | 0x80 | 0x40 | 0x20 | 0x10 | 0x08 | 0x04 | 0x02 | 0x01 |      |      |      |      |      |      |      |      |

#### 8.3. Double Bit-In-Error

When the Memory Data word (D [31..0] & C[7..0]) read has two bit-in-error, the 20C532E EDAC develops a syndrome different of 0x00. The syndrome value generated by a double bit-in-error never takes place of a syndrome value generated by a single bit-in-error. In this case, the syndrome decoder sets low the non correctable

error flag  $\overline{NCERR}$  and  $\overline{CERR}$  flag remains at high level.  $\underline{Example:}$

If data D [24] and D [3] are incorrect, syndrome bit SY [7, 2, 0] are set to one (SY= 0x85), NCERR flag is set low (CERR flag remains at high level).

### 8.4. Triple Bit-In-Error

When the Memory Data word (D [31..0] & C[7..0]) read has three bit-in-error, the 20C532E EDAC develops a syndrome different of 0x00. The syndrome value generated by a triple bit-in-error can have any value, even a syndrome value normally generated by a single bit-in-error.  $\overline{NCERR}$  flag or  $\overline{CERR}$  flag can be activated following the value of the generated syndrome.

### Example:

If data D [25], D [20] and D [6] are incorrect, syndrome

## bit SY [5, 4, 2, 1, 0] are set to one (SY= 0x37), $\overline{NCERR}$ flag is set low ( $\overline{CERR}$ flag remains at high level).

Fault example: If data D [30], D [15] and D [0] are incorrect, syndrome bits SY [7, 5, 3, 2] are set to one (SY=0xAC). The syndrome is decoded by the 29C532E EDAC has being a correctable error on D [14]. Then,  $\overline{CERR}$  flag is set low and  $\overline{NCERR}$  flag remains at high level. A correction would cause more errors.

### 8.5. Multi Bit-In-Error

When the Memory Data word (D [31..0] & C[7..0]) read has four or more bit-in-error, the 20C532E EDAC develops a non controlled syndrome. This syndrome can take any value, from 0x00 (No Error Detected) to specific syndrome value of single bit-in-error .

### Example:

If the data read = 0x00000000 instead of 0xFFFFFFFF, the generated syndrome is 0x00. Then, no error flag is actived.

### 8.6. 4-Bit Wide Memory Error

The 8 checkbit code can be used to provide error detection for up to four errors occuring in the following fields:

- D [31..28],

- D [27..24],

- D [23..20],

- D [19..16],

- D [15..12],

- D [11..8],D [7..4],

- D [7..4],D [3..0],

- C [7..4],

- C [3..0].

The 29C532E EDAC can flag any number of errors in 4-bit wide memory chip. If the one device returns from one to four bit-in error, the  $\overline{\text{CERR}}$  and  $\overline{\text{NCERR}}$  flags are generated following the error type and the generated syndrome takes a value which never overlaps the code of a single bit-in-error. This is a restriction to triple and multi bit-in-error.

### Example:

If the device controlling D [7..4] generates error, the 15 possible codes are different of 0x00 and of those describing a single bit-in-error.

| Bit in error | 7    | 6    | 5    | 4    | 7<br>6 | 7<br>5 | 7<br>4 | 6<br>5 | 6<br>4 | 5<br>4 | 7<br>6<br>5 | 7<br>6<br>4 | 7<br>5<br>4 | 6<br>5<br>4 | 7<br>6<br>5<br>4 |

|--------------|------|------|------|------|--------|--------|--------|--------|--------|--------|-------------|-------------|-------------|-------------|------------------|

| SY           | 0xCA | 0xA6 | 0x25 | 0x1F | 0x6C   | 0xEF   | 0xD5   | 0x83   | 0xB9   | 0x3A   | 0x49        | 0x73        | 0xF1        | 0x9C        | 0x56             |

| CERR         | Х    | х    | х    | X    | -      | -      | -      | -      | -      | -      | -           | -           | -           | -           | -                |

| NCERR        | -    | -    | -    | -    | X      | X      | X      | X      | X      | X      | X           | X           | X           | X           | X                |

### 8.7. 8-Bit Wide Memory Error

The 8 checkbit code can be used to provide error detection for up to eight errors occurring in the following fields:

- D [31..24],

- D [23..16],

- D [15..8],

- D [7..0],

- C [7..0].

The 29C532E EDAC can flag any number of errors in 8-bit wide memory chip. If the one device returns from one to eight bit-in error, the CERR and NCERR flags are generated following the error type and the generated syndrome takes a value which never overlaps the code of a single bit-in-error. This is a restriction to triple and multi bit-in-error.

### 9. Transactions

### 9.1. Control

The controller guides The data flow in the 29C532E EDAC. This data flow control defines the value of the output buses DO [31..0] & CO [7..0] and the checkbit bus RCB [7..0]:

- SYNCHK and CORRECT control flow on DO [31..0],

- OLE/CHK and DIAG [0] control flow on CO [7..0],

- DIAG [1] controls flow on RCB [7..0].

**Table 7: Data Flow Control**

|          | SYNCHK | CORRECT | Connected to                              |

|----------|--------|---------|-------------------------------------------|

|          | High   | High    | CDO [310]                                 |

| DO [310] | High   | Low     | DI [310]                                  |

|          | Low    | X       | DIA [70] // SY [70] // CI [70] // DIA[70] |

|         | OLE/CHK | DIAG [0] | Connected to |

|---------|---------|----------|--------------|

|         | Low     | Low      | GCB [70]     |

| CO [70] | High    | Low      | SY [70]      |

|         | X       | High     | DIA [70]     |

|            | DIAG [1] | Connected to |

|------------|----------|--------------|

| DCD [7, 0] | Low      | CI [70]      |

| RCB [70]   | High     | DIA [70]     |

Eight signals are used to supervise the transactions :

- $\bullet \;\; \overline{\text{DOE}}$  [3..0] control Data Output Buffers,

- $\bullet \;\; \overline{\text{COE}}$  control Checkbit Output Buffer.

- OLE/CHK controls Data Output Latch,

- ILE controls Checkbit and Data Input Latchs,

- DLE controls Diagnostic Input Latch.

### 9.2. Memory Write

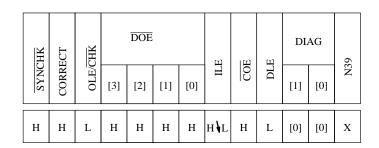

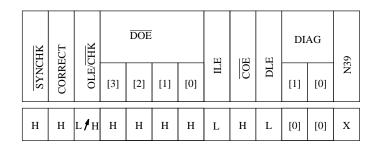

| SYNCHK | CORRECT | OLE/CHK | <del>DOE</del> [3] | ILE               | COE | DLE | DIAG [1] | DIAG [0] | N39    |

|--------|---------|---------|--------------------|-------------------|-----|-----|----------|----------|--------|

| High   | High    | Low     | High               | $H \Rightarrow L$ | Low | Low | Low      | Low      | H or L |

Rev. B – 26 February, 1997

16

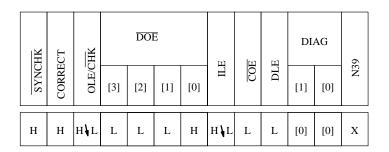

### 9.3. Memory Read

### ... Till Error Generation

| SYN | CHK | CORRECT | OLE/CHK | <del>DOE</del> [3] | ILE               | COE  | DLE | DIAG [1] | DIAG [0] | N39    |

|-----|-----|---------|---------|--------------------|-------------------|------|-----|----------|----------|--------|

| Hi  | gh  | High    | Low     | High               | $H \Rightarrow L$ | High | Low | Low      | Low      | H or L |

Rev. B-26 February, 1997

17

### **Preliminary Information**

### 9.4. Memory Read (continue)

### ... With Correction - Single Bit-in-error

| SYNCHK | CORRECT | OLE/ <del>CHK</del> | <del>DOE</del> [3] | ILE | COE | DLE | DIAG [1] | DIAG [0] | N39    |

|--------|---------|---------------------|--------------------|-----|-----|-----|----------|----------|--------|

| High   | High    | L⇒M <sup>(*)</sup>  | High               | Low | Low | Low | Low      | Low      | H or L |

(\*) when OLE/ $\overline{CHK}$  = H, then CO [7..0] = SY [7..0] (placed in schematic), when OLE/ $\overline{CHK}$  = I, then CO [7..0] = GCB [7..0]

18

Rev. B – 26 February, 1997

### 9.5. Byte Memory Write - Read Modify Write

### A) 32-bit Data Memory + Checkbit Read

Rev. B-26 February, 1997

19

## **Preliminary Information**

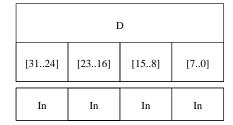

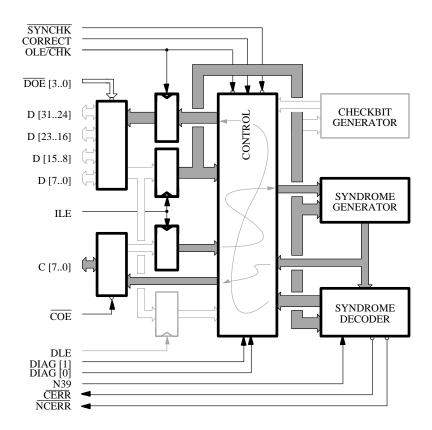

### B) Preparing of 32-bit Corrected Data

|        | D                        |    |    |  |  |  |  |  |  |  |  |

|--------|--------------------------|----|----|--|--|--|--|--|--|--|--|

| [3124] | [3124] [2316] [158] [70] |    |    |  |  |  |  |  |  |  |  |

| In     | In                       | In | In |  |  |  |  |  |  |  |  |

Rev. B – 26 February, 1997

20

### C) 8-bit Data Memory + Checkbit Write

|        | I                        | )      |    |  | С   |  |  |  |

|--------|--------------------------|--------|----|--|-----|--|--|--|

| [3124] | [3124] [2316] [158] [70] |        |    |  |     |  |  |  |

| In-Out | In-Out                   | In-Out | In |  | Out |  |  |  |

Rev. B-26 February, 1997

### 10. Signal Timing

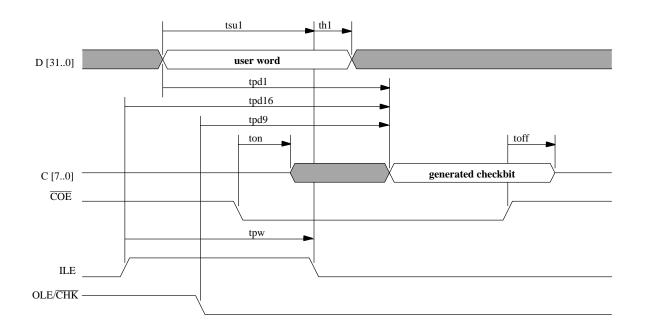

### 10.1. Memory Write

|          | tsu 1 | th 1 | tpd 1 | tpd 16 | tpd 9 | ton | toff | tpw |

|----------|-------|------|-------|--------|-------|-----|------|-----|

| Max (ns) |       |      | 30    | 38     | 20    | 14  | 14   |     |

| min (ns) | 6     | 5    |       |        |       |     |      | 5   |

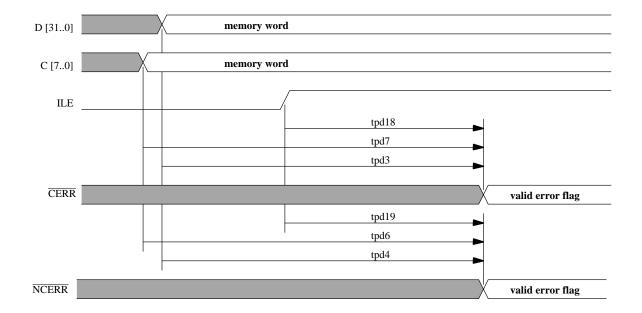

### 10.2. Memory Read

|          | tpd 18 | tpd 7 | tpd 3 | tpd 19 | tpd 8 | tpd 4 |

|----------|--------|-------|-------|--------|-------|-------|

| Max (ns) | 41     | 32    | 34    | 45     | 35    | 37    |

| min (ns) |        |       |       |        |       |       |

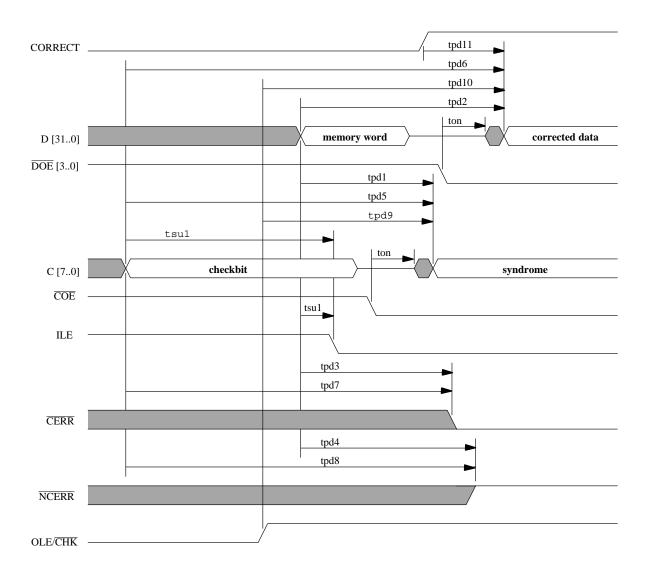

### 10.3. Memory Read With Correction

|          | tpd 11 | tpd 6 | tpd 10 | tpd 2 | ton | tpd 1 | tpd 5 | tpd 9 | tsu 1 | tpd 3 | tpd 7 | tpd 4 | tpd 8 |

|----------|--------|-------|--------|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| Max (ns) | 20     | 38    | 18     | 39    | 14  | 30    | 29    | 20    |       | 34    | 32    | 37    | 35    |

| min (ns) |        |       |        |       |     |       |       |       | 6     |       |       |       |       |

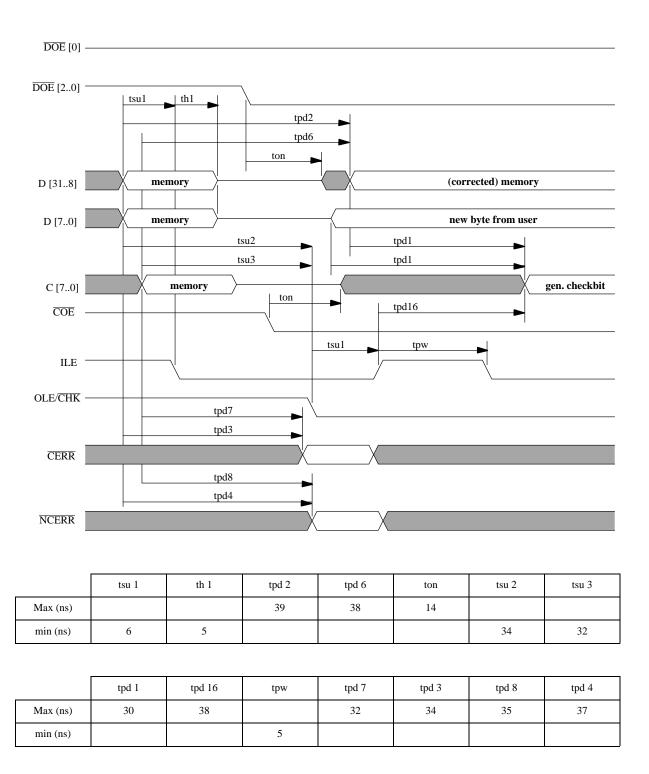

### 10.4. Memory Byte Write (Read Modify Write)

The information contained herein is subject to change without notice. No responsibility is assumed by Atmel Wireless & Microcontrollers for using this publication and/or circuits described herein: nor for any possible infringements of patents or other rights of third parties which may result from its use.

\_ .. . \_ .

Rev. B – 26 February, 1997