PMC-980474

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# PM6388/PM4388

# **EOCTL/TOCTL WITH FREEDM-8**

# REFERENCE DESIGN

# RELEASED ISSUE 2: JANUARY 1999

PMC-980474

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# **Blank Page**

#### EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# **CONTENTS**

| 1 | OVE | RVIEW                                | 1  |

|---|-----|--------------------------------------|----|

|   | 1.1 | APPLICATION PERSPECTIVE              | 1  |

|   | 1.2 | DESIGN CONSTRAINTS                   | 2  |

| 2 | FUN | ICTIONAL DESCRIPTION                 | 4  |

|   | 2.1 | BLOCK DIAGRAM DRAWING                | 4  |

|   | 2.2 | BLOCK DIAGRAM DESCRIPTION            | 5  |

|   | 2.3 | E1/DS-1 CONNECTOR INTERFACE          | 5  |

|   | 2.4 | TRANSFORMERS AND QDSX LINE INTERFACE | 8  |

|   |     | 2.4.1 RECEIVE PATH                   | 8  |

|   |     | 2.4.2 TRANSMIT PATH                  | 10 |

|   | 2.5 | CLOCK DISTRIBUTION                   | 13 |

|   |     | 2.5.1 E1/T1 TIMING                   | 14 |

|   |     | 2.5.2 MICROPROCESSOR CLOCKS          | 14 |

|   | 2.6 | LED INDICATORS                       | 14 |

|   |     | 2.6.1 POWER INDICATORS               | 14 |

|   |     | 2.6.2 RESET INDICATOR                | 15 |

|   | 2.7 | RESET CIRCUIT                        | 16 |

|   |     | 2.7.1 PCI BUS RESET                  | 16 |

|   |     | 2.7.2 MICROPROCESSOR RESET LINE RSTB | 17 |

| 3 | QDS | SX DEVICE DESCRIPTION                | 18 |

|   | 3.1 | QDSX BLOCK DIAGRAM                   | 18 |

|   | 3.2  | E1/DS-1 TRANSMIT BLOCK                           | . 19 |

|---|------|--------------------------------------------------|------|

|   |      | 3.2.1 TRANSMIT INTERFACE                         | .19  |

|   |      | 3.2.2 PROGRAMMING THE XPLS WAVEFORM TEMPLATE     | .21  |

|   | 3.3  | E1/DS-1 RECEIVE BLOCK                            | .27  |

|   | 3.4  | DROP SIDE INTERFACE                              | .28  |

|   | 3.5  | LOOPBACK OPTIONS                                 | .29  |

|   | 3.6  | TRANSMIT JITTER ATTENUATION                      | .31  |

|   | 3.7  | RECEIVER JITTER TOLERANCE AND JITTER ATTENUATION | 31   |

|   | 3.8  | MICROPROCESSOR INTERFACE TO QDSX                 | .32  |

| 4 | EOCT | TL DEVICE DESCRIPTION                            | .33  |

|   | 4.1  | BLOCK DIAGRAM                                    | .33  |

|   | 4.2  | EOCTL DEVICE - TRANSMIT DIRECTION                | . 35 |

|   |      | 4.2.1 BTIF - BACKPLANE EGRESS INTERFACE          | .35  |

|   |      | 4.2.2 TPSC – PER-CHANNEL CONTROLLER              | .37  |

|   |      | 4.2.3 TRAN – BASIC E1 TRANSMITTER                | .37  |

|   |      | 4.2.4 TJAT – DIGITAL JITTER ATTENUATION          | .38  |

|   |      | 4.2.5 PRGD – PATTERN GENERATOR                   | .39  |

|   | 4.3  | EOCTL DEVICE – RECEIVE DIRECTION                 | .39  |

|   |      | 4.3.1 RJAT – DIGITAL JITTER ATTENUATION          | .40  |

|   |      | 4.3.2 FRMR - E1 FRAMER                           | .40  |

|   |      | 4.3.3 SIGX – SIGNAL EXTRACTOR                    | .41  |

|   |      | 4.3.4 RPSC – PER-CHANNEL CONTROLLER              | .41  |

|   |      | 4.3.5 BRIF – BACKPLANE INGRESS INTERFACE         | .41  |

| 4.5 MICROPROCESSOR INTERFACE ON EOCTL  5 TOCTL DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                               |   | 4.4   | LOOPBACKS                               | .43 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|-----------------------------------------|-----|

| 6 FREEDM-8 DEVICE DESCRIPTION                                                                                                                                                                                                                                                                                                                                   |   | 4.5   | MICROPROCESSOR INTERFACE ON EOCTL       | .44 |

| 6.1 BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                               | 5 | TOCT  | L DEVICE DESCRIPTION                    | .45 |

| 6.2 PCI BUS INTERFACE TO THE HOST PROCESSOR AND PACE MEMORY 6.3 LINE LOOPBACK                                                                                                                                                                                                                                                                                   | 6 | FREE  | DM-8 DEVICE DESCRIPTION                 | .48 |

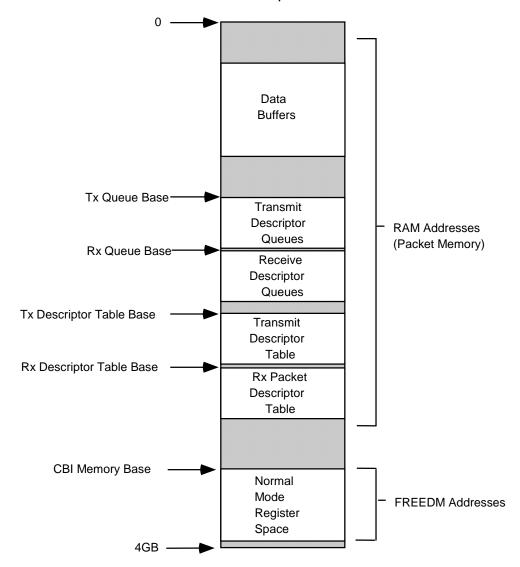

| MEMORY  6.3 LINE LOOPBACK  6.4 SOFTWARE DRIVER  7 ON-BOARD MICROPROCESSOR  8 SOFTWARE AND FIRMWARE  8.1 SYSTEM TESTBED DESCRIPTION  8.2 FIRMWARE DESCRIPTION  8.3 BOOT SEQUENCE  8.3.1 EOCTL/TOCTL DETECTION  8.3.2 FREEDM-8 POWER-UP  8.3.3 EOCTL BOOT  8.3.4 TOCTL BOOT  8.4 HOMOLOGATION SOFTWARE  8.4.1 STATE MATRIX.  8.4.2 BASIC FRAME AND CRC MULTIFRAME |   | 6.1   | BLOCK DIAGRAM                           | .48 |

| 6.4 SOFTWARE DRIVER                                                                                                                                                                                                                                                                                                                                             |   | 6.2   |                                         |     |

| 7 ON-BOARD MICROPROCESSOR                                                                                                                                                                                                                                                                                                                                       |   | 6.3   | LINE LOOPBACK                           | .51 |

| 8 SOFTWARE AND FIRMWARE                                                                                                                                                                                                                                                                                                                                         |   | 6.4   | SOFTWARE DRIVER                         | .51 |

| 8.1 SYSTEM TESTBED DESCRIPTION  8.2 FIRMWARE DESCRIPTION  8.3 BOOT SEQUENCE  8.3.1 EOCTL/TOCTL DETECTION  8.3.2 FREEDM-8 POWER-UP  8.3.3 EOCTL BOOT  8.3.4 TOCTL BOOT  8.4 HOMOLOGATION SOFTWARE  8.4.1 STATE MATRIX  8.4.2 BASIC FRAME AND CRC MULTIFRAME                                                                                                      | 7 | ON-B  | OARD MICROPROCESSOR                     | .52 |

| 8.2 FIRMWARE DESCRIPTION                                                                                                                                                                                                                                                                                                                                        | 8 | SOFT  | WARE AND FIRMWARE                       | .53 |

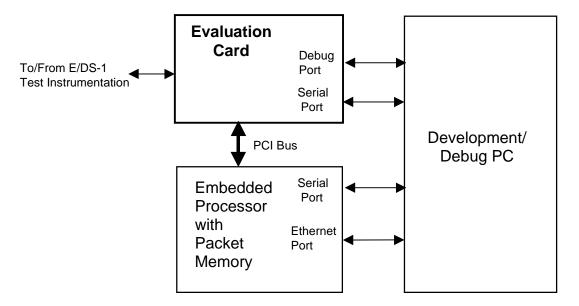

| 8.3 BOOT SEQUENCE                                                                                                                                                                                                                                                                                                                                               |   | 8.1   | SYSTEM TESTBED DESCRIPTION              | .53 |

| 8.3.1 EOCTL/TOCTL DETECTION                                                                                                                                                                                                                                                                                                                                     |   | 8.2   | FIRMWARE DESCRIPTION                    | .54 |

| 8.3.2 FREEDM-8 POWER-UP  8.3.3 EOCTL BOOT  8.3.4 TOCTL BOOT  8.4 HOMOLOGATION SOFTWARE  8.4.1 STATE MATRIX  8.4.2 BASIC FRAME AND CRC MULTIFRAME                                                                                                                                                                                                                |   | 8.3   | BOOT SEQUENCE                           | .54 |

| 8.3.3 EOCTL BOOT                                                                                                                                                                                                                                                                                                                                                |   |       | 8.3.1 EOCTL/TOCTL DETECTION             | .54 |

| 8.3.4 TOCTL BOOT                                                                                                                                                                                                                                                                                                                                                |   |       | 8.3.2 FREEDM-8 POWER-UP                 | .54 |

| 8.4.1 STATE MATRIX                                                                                                                                                                                                                                                                                                                                              |   |       | 8.3.3 EOCTL BOOT                        | .54 |

| 8.4.1 STATE MATRIX                                                                                                                                                                                                                                                                                                                                              |   |       | 8.3.4 TOCTL BOOT                        | .58 |

| 8.4.2 BASIC FRAME AND CRC MULTIFRAME                                                                                                                                                                                                                                                                                                                            |   | 8.4   | HOMOLOGATION SOFTWARE                   | .60 |

|                                                                                                                                                                                                                                                                                                                                                                 |   |       | 8.4.1 STATE MATRIX                      | .60 |

|                                                                                                                                                                                                                                                                                                                                                                 |   |       | 8.4.2 BASIC FRAME AND CRC MULTIFRAME    | .62 |

| 9 IMPLEMENTATION DESCRIPTION                                                                                                                                                                                                                                                                                                                                    | 9 | IMPLI | EMENTATION DESCRIPTION                  | .63 |

| 9.1 PRINTED CIRCUIT BOARD LAYOUT                                                                                                                                                                                                                                                                                                                                |   | 9.1   | PRINTED CIRCUIT BOARD LAYOUT            | .63 |

| 9.1.1 CARD SIZE AND COMPONENT PLACEMENT                                                                                                                                                                                                                                                                                                                         |   |       | 9.1.1 CARD SIZE AND COMPONENT PLACEMENT | .63 |

10

11

12

13

ISSUE 2

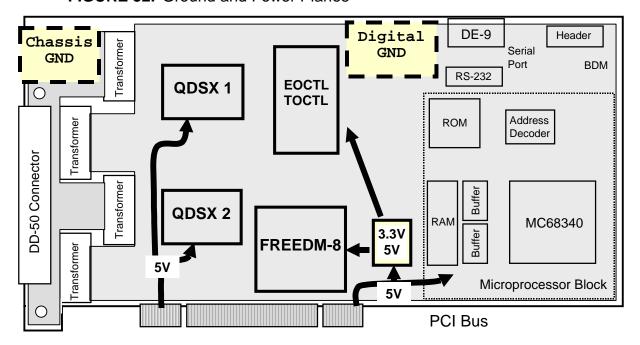

|      | 9.1.2  | GROUND AND POWER PLANES64                                |   |

|------|--------|----------------------------------------------------------|---|

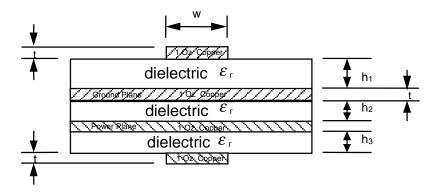

|      | 9.1.3  | LAYER STACKING AND TRANSMISSION LINE IMPEDANCE CONTROL65 | į |

|      | 9.1.4  | DECOUPLING, BYPASSING AND BULK CAPACITORS68              | , |

|      | 9.1.5  | CALCULATION OF DECOUPLING CAPACITOR VALUES70             | 1 |

|      | 9.1.6  | PCI INTERFACE71                                          |   |

| 9.2  | SCHE   | MATIC71                                                  |   |

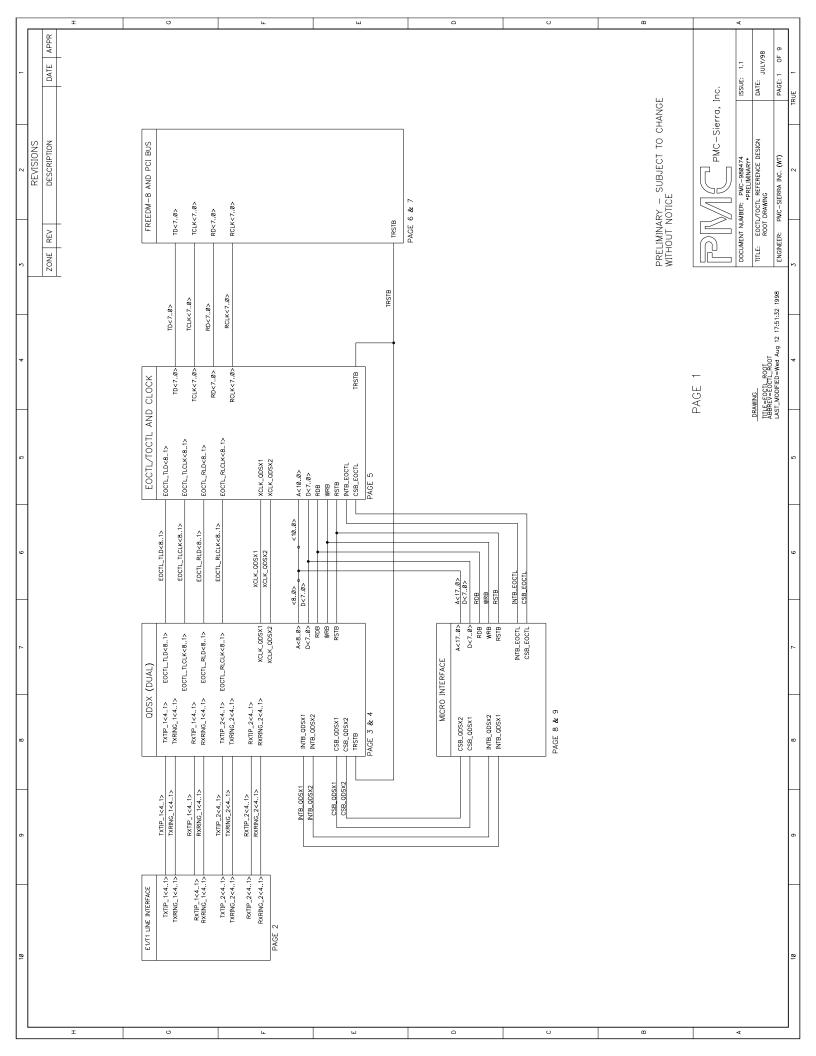

|      | 9.2.1  | PAGE 1: ROOT DRAWING71                                   |   |

|      | 9.2.2  | SHEET 2: E1/DS-1 LINE INTERFACE WITH DD-50 CONNECTOR     |   |

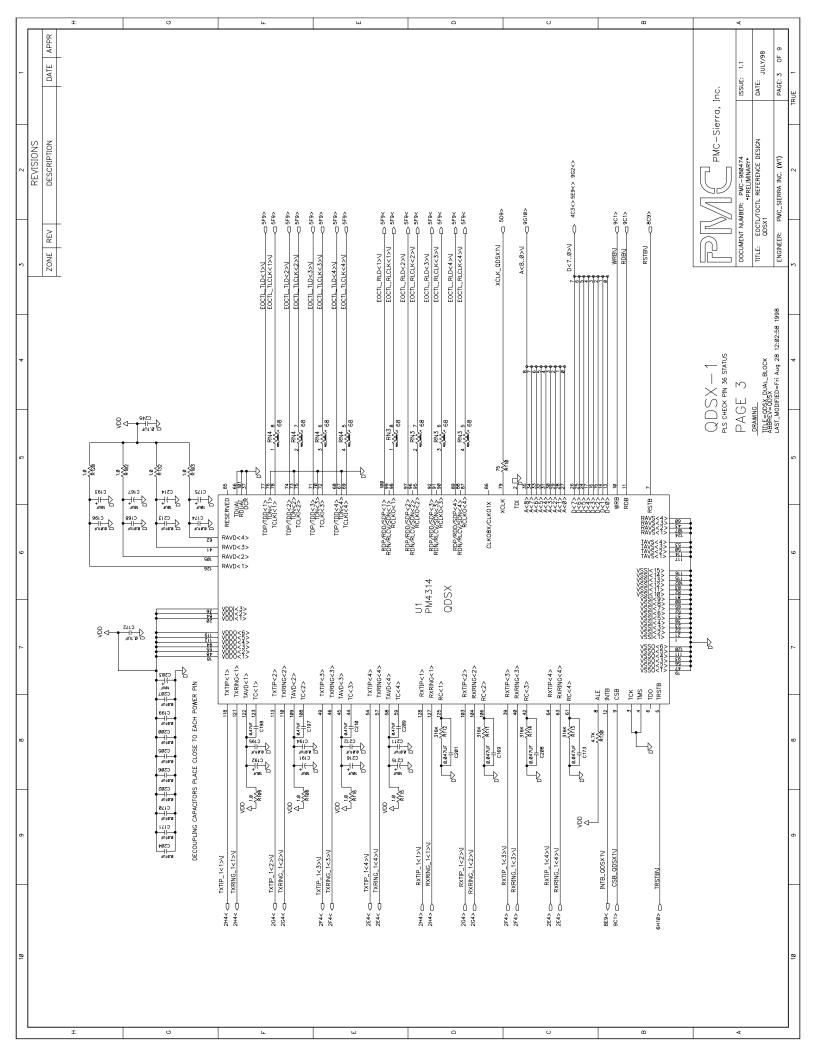

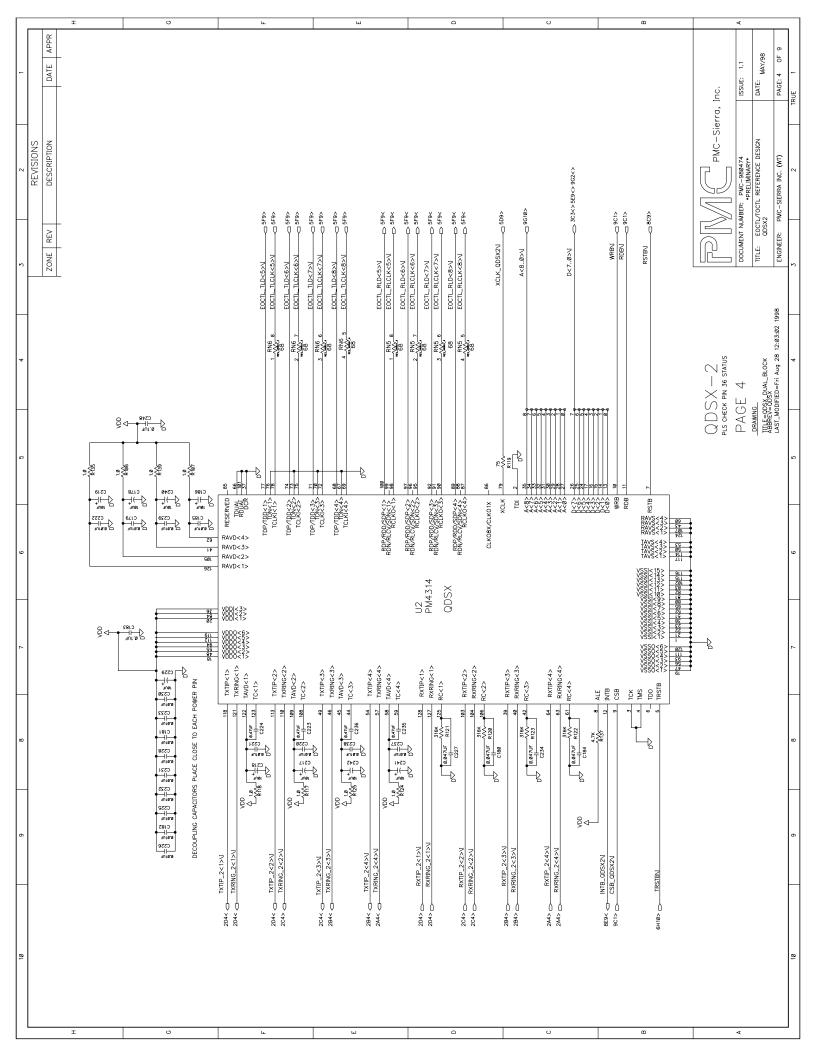

|      | 9.2.3  | SHEET 3 AND 4: QDSX - E1/DS-1 LINE INTERFACE DEVICE      |   |

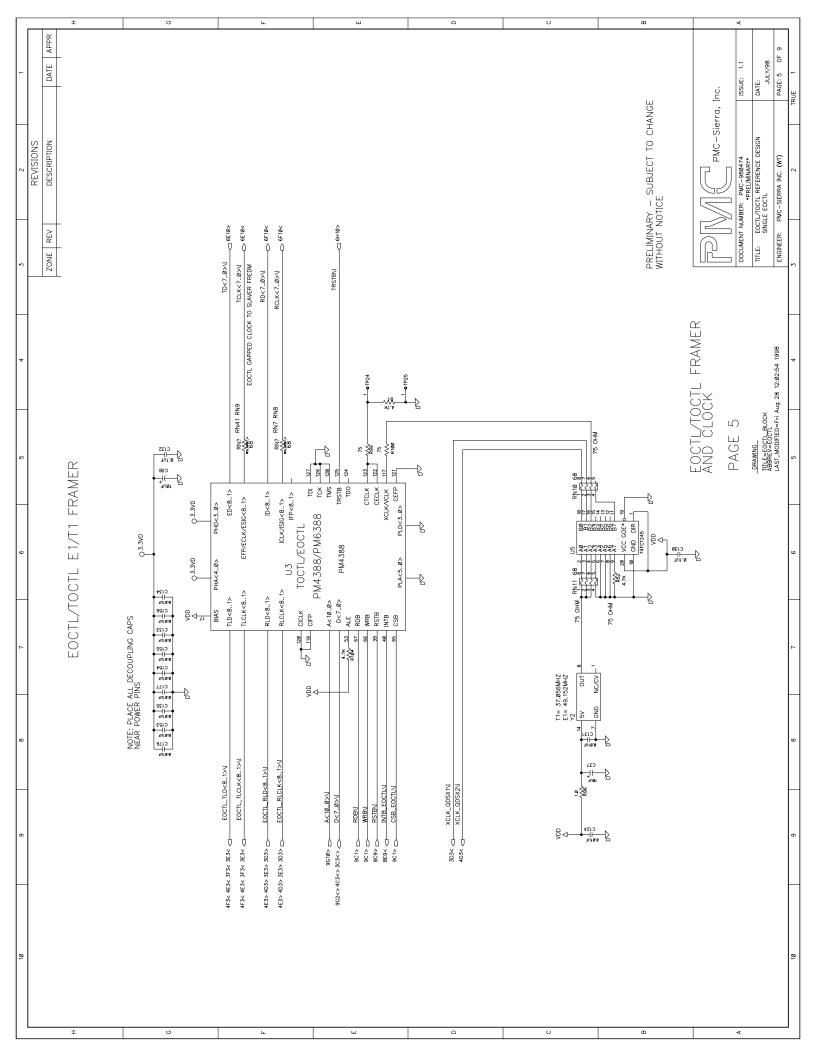

|      | 9.2.4  | SHEET 5: EOCTL/TOCTL AND CLOCK - E1/T1 FRAMER73          | 3 |

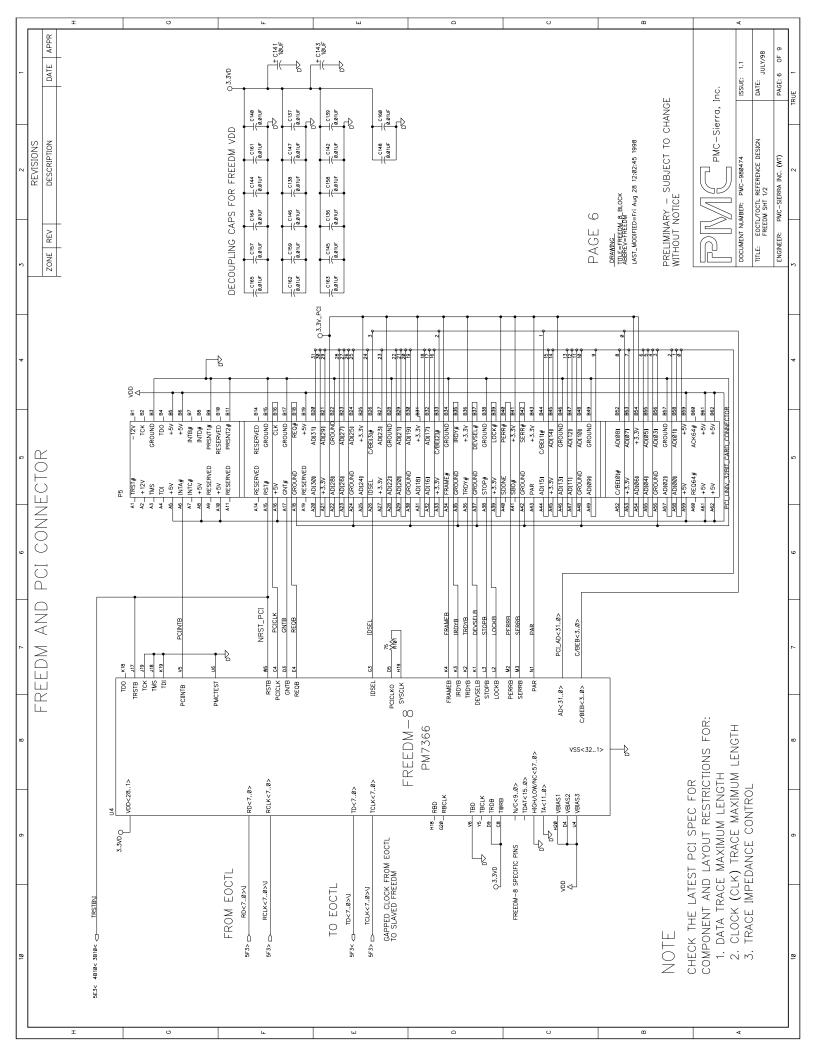

|      | 9.2.5  | PAGE 6: FREEDM-8 AND PCI BUS INTERFACE73                 |   |

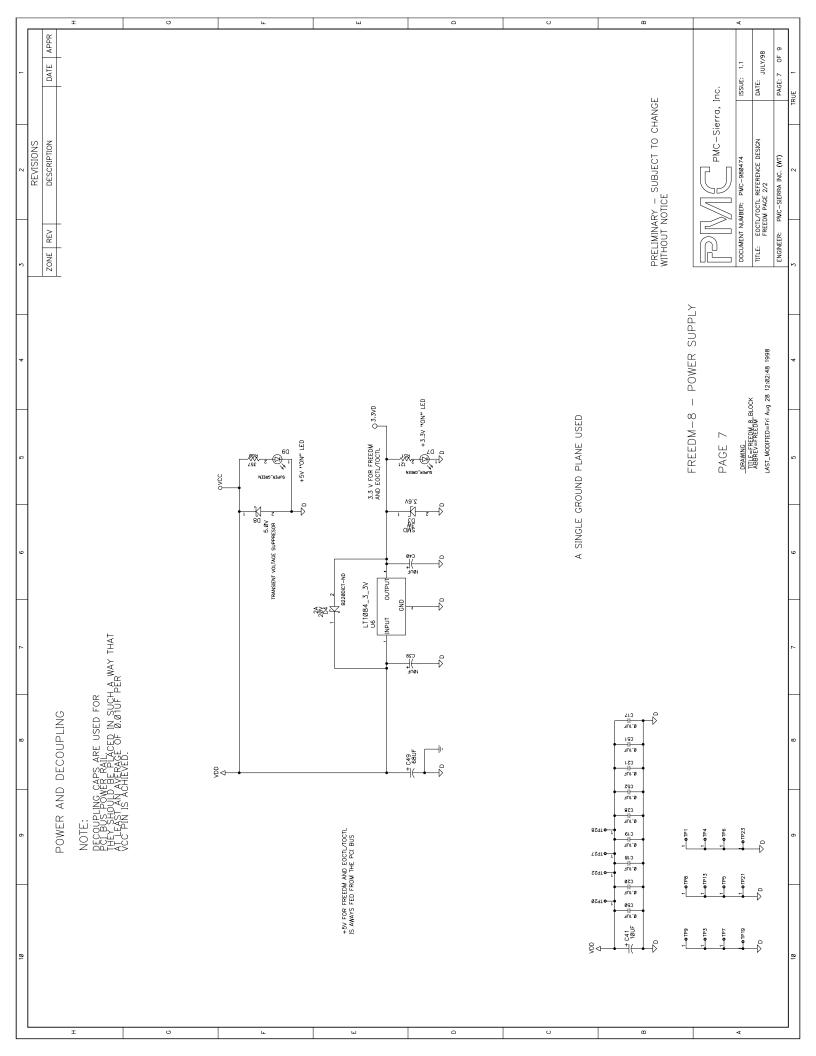

|      | 9.2.6  | PAGE 7: FREEDM-8 - POWER SUPPLY74                        |   |

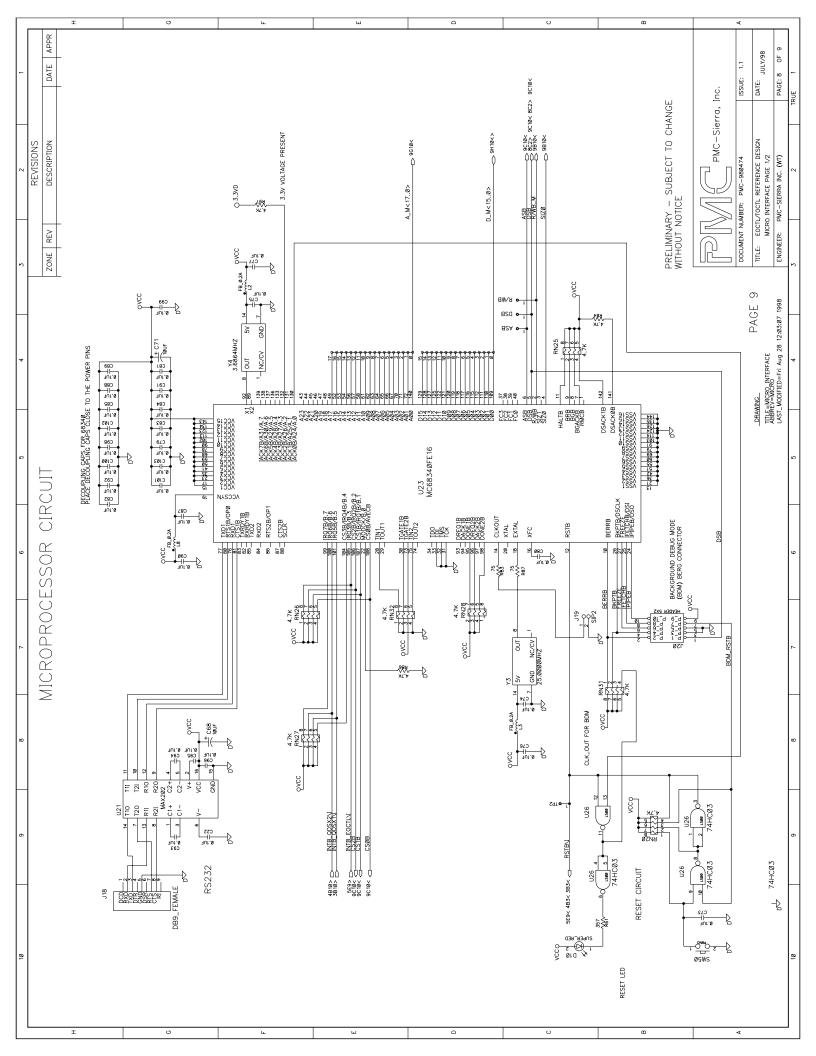

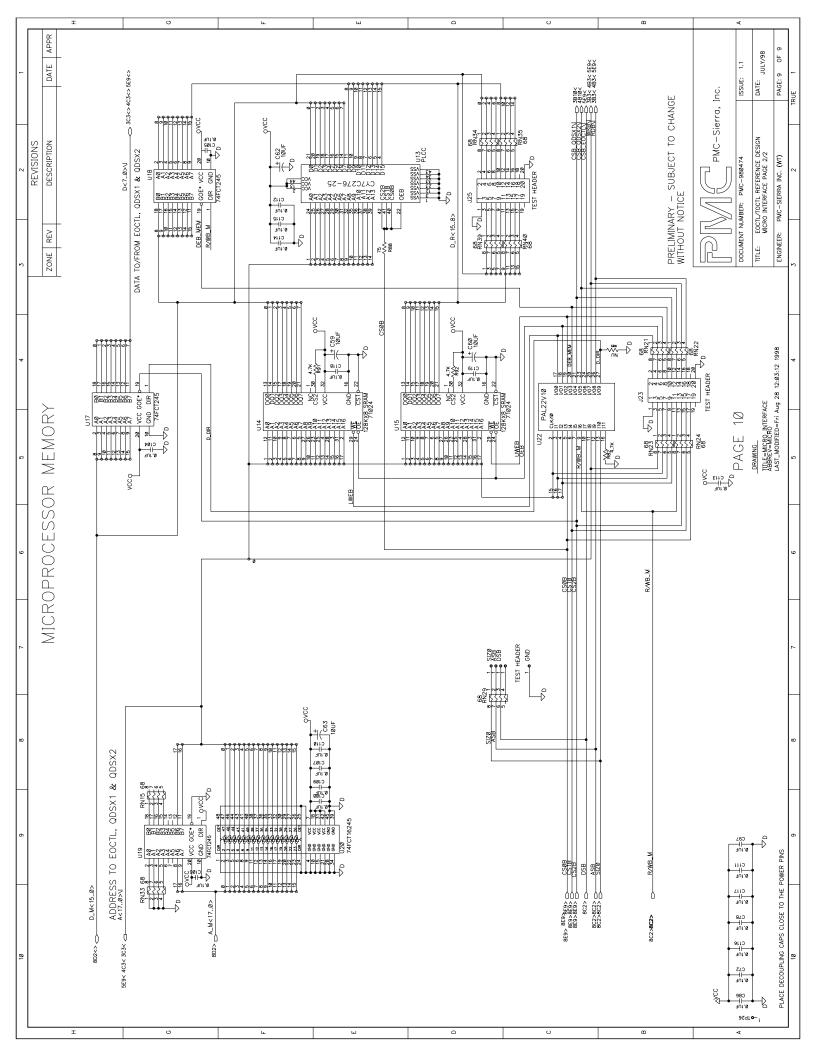

|      | 9.2.7  | SHEET 8: MICROPROCESSOR INTERFACE – ON-BOARD MC6834075   |   |

|      | 9.2.8  | SHEET 9: MICROPROCESSOR INTERFACE - DECODE LOGIC76       | , |

| 9.3  | PCB I  | MODIFICATION78                                           | , |

| GLOS | SARY   | 79                                                       |   |

| APPE | NDIX / | A. PAL VHDL TEXT FILE82                                  |   |

| 11.1 | ROM    | VERSION OF PAL82                                         |   |

| 11.2 | BDM '  | VERSION OF PAL84                                         |   |

| APPE | NDIX I | B. SCHEMATICS86                                          | ì |

| APPE | NDIX ( | C: BILL OF MATERIALS87                                   | , |

PMC-Sierra, Inc.

| REFERENCE DESIGN | ۷ |

|------------------|---|

| PMC-980474       |   |

| 100 | ,, | _ | 2 |  |

|-----|----|---|---|--|

| 133 | u  | _ | _ |  |

| 13.1 | BILL OF MATERIALS FOR E1 INTERFACE WITH EOCTL   | 87 |

|------|-------------------------------------------------|----|

| 13.2 | BILL OF MATERIALS FOR DS-1 INTERFACE WITH TOCTL | 91 |

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

## **REFERENCES**

- [1]. PMC-Sierra, Inc., PMC950857, "PM4314 QDSX Long Form Data Sheet", (PM4314) Data Sheet, Issue 4, October 1997.

- [2]. PMC-Sierra, Inc., PMC971019 "OCTAL E1 Framer Device Standard Data Sheet" (PM6388), Issue 2, January 1998.

- [3]. PMC-Sierra, Inc., PMC960840 "OCTAL T1 Framer Standard Data Sheet" (PM4388), Issue 4, December 1997.

- [4]. PMC-Sierra, Inc., PMC-970930, "FREEDM-8 Data Sheet" (PM7366), Issue 1, November 1996.

- [5]. PMC-Sierra, Inc., PMC-970935, "FREEDM-8 Bus Utilization and Latency Test"

- [6]. PMC-Sierra, Inc., PMC-970281, "FREEDM-32 Programmer's Guide" Application Note, March 1997, Issue 1.

- [7]. PMC-Sierra, Inc., PMC-971017, "FREEDM-8 and FREEDM-32 Software Differences"

- [8]. PMC-Sierra, Inc., PMC-971178, "Answers to Frequently-Asked Questions Regarding the FREEDM-8",

- [9]. PMC-Sierra, Inc., PMC-tbd, "MC68340 Software for the EOCTL/TOCTL Reference Design.

- [10]. PCI SIG, PCI Local Bus Specification, June 1, 1995, Version 2.1

- [11]. Motorola, "MC68340 Integrated Processor with DMA, User manual" 1992

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# 1 OVERVIEW

# 1.1 Application Perspective

The focus of the Reference Design is to show implementation of the E1/DS-1 line interface Card with PM6388 Octal E1 Framer (EOCTL) and PM4388 Octal T1 Framer (TOCTL). The FREEDM-8 (PM7366), the QDSX (PM4314) and the physical E1/DS-1 line interface are also key components of this Reference Design.

This Reference Design provides an application example of a circuit that supports a total of eight E1/T1 data links. At the system side, the PCI Bus transfers the data for upper level processing interface. The eight E1/DS-1 line interfaces are implemented using two PMC-Sierra's QDSXs. The QDSX is a physical layer device. On the system side the FREEDM-8 device interfaces to a 5/3.3Volt, 32bit, PCI connector compliant with the PCI SIG Specification Rev. 2.1. Software drivers are provided to interface the FREEDM-8 and the PC host. The EOCTL device sits between those two interfaces and provides data extraction and framing.

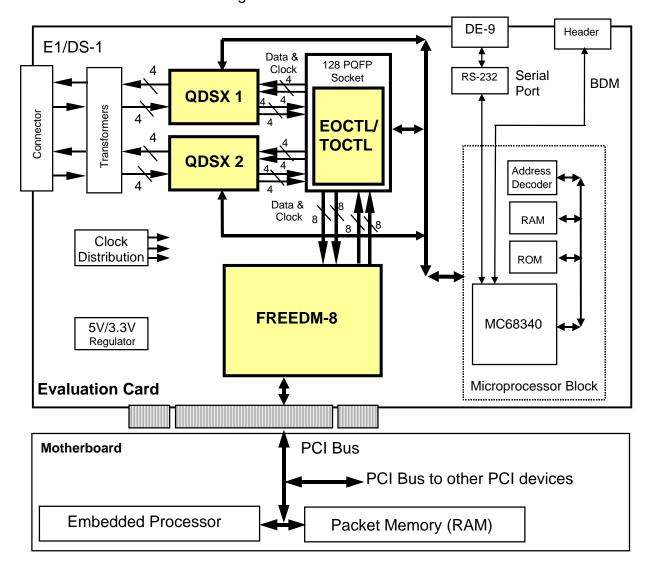

Example of high-level system architecture is shown in FIGURE 1.

ISP INTERNET Dial-up Access Frame Relay FRI Server Server Frame Relay IP Router IP Router Switch Frame Relay Frame Relay Switch ×<sub>FUNI</sub> FUNI ATM Frame Relay Implementation **FUNI Implementation** Packet IP Routing Memory PCI Bus PCI Bus PM7375 LASAR-155 PM7364 FREEDM PM7364 FREEDM PM7364 PM7364 PM7364 PM7364 FREEDM FREEDM FREEDM PM7345 S/UNI-PDH FREEDM PM4388 PM4388 PM6388 PM4388 PM4388 PM6388 TOCTL TOCTL TOCTL TOCTL EOCTL PM8313 PM8313 D3MX Δтм PM4314 PM4314 D3MX QDSX QDSX Switch Fabric T3, E3 DS3 LIU DS3 LIU FT3, T3 FT3, T3 EOCTL/TOCTL EOCTL/TOCTL EOCTL/TOCTL EOCTL/TOCTL

**FIGURE 1.** Frame Relay Inter-Networking Overview

This Reference Design fits well into the Frame Relay network shown in figure above.

REFERENCE DESIGN PMC-980474

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

The QDSX device is software configurable and supports both the E1 and DS-1 line interface.

The FREEDM-8 standard product is primarily designed for the frame relay application. Frame relay is a multiplexed data networking technology supporting connectivity between user equipment (routers, nodal processors/fast packet switches) and between user equipment and the public frame relay network. The frame relay protocol supports data transmission over a connection-oriented path and enables the transmission of variable-length data units over an assigned virtual connection.

User equipment such as routers, E1/T1 multiplexers, front end processors (FEPs), and packet assemblers/dissemblers (PADS) need to support the frame relay interface in order for them to be connected to a private or a public frame relay network.

# 1.2 Design Constraints

The purpose of the "EOCTL/TOCTL With FREEDM-8" Reference Design is to serve as an example to assist designers of data routers and frame relay switches to design their products using PMC-Sierra's FREEDM-8, EOCTL/TOCTL and QDSX standard products, as shown in FIGURE 1.

This design illustrates the frame relay application with interfaces to channelized and unchannelized E1/T1 data streams. The hardware which implements these interfaces is built, tested and debugged thereby assisting designers to more quickly bring their designs to market.

The following hardware constraints have been included in this design:

- Support the PCI local bus revision 2.1, which allows up to four PCI devices per PCI bus segment to be connected to a host processor and packet memory. This constraint allows the reference design to be implemented as an add-in card to any readily available processor board with a revision 2.1 compliant PCI bus. Up to four reference design cards can be interfaced to the processor board.

- Mechanical and electrical constraints for interfacing an add-in card to the processor board, as specified in revision 2.1 of the PCI local bus specification.

REFERENCE DESIGN PMC-980474

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

The software interfaces to the FREEDM-8 via a host processor on the PCI bus and enables support of network protocol layers necessary to transmit and receive data packets of PVC. Software procedures are provided to illustrate the following:

- PCI device location and memory resource assignment

- Reset of the hardware via software

ISSUE 2

- Initialization of the hardware, software and the packet memory

- Activation/deactivation of the hardware

- Provisioning/unprovisioning of PVCs

- Transmit and receive packet processing

- Error handling

- Performance counters

- Diagnostics

The following software constraints have been included in this design:

- The FREEDM-8 data interfaces are the only interfaces the software has access to. The content of the user data field of the HDLC frame is not processed. Other upper layer functions such as congestion management, LMI protocol and multi-cast capability are not implemented.

- Source code is written in the C language. Executable code can run on i960 or Pentium based processor boards.

This Reference Design and Evaluation Card supports E1 and T1 data format that is hardware and/or software configurable within the same basic printed circuit board assembly.

# **2 FUNCTIONAL DESCRIPTION**

The following sections provide a functional description of the components mounted on the Board.

# 2.1 Block Diagram Drawing

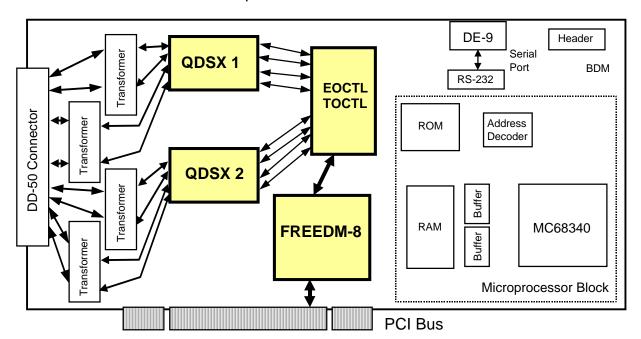

FIGURE 2. Block Diagram

ISSUE 2

# 2.2 Block Diagram Description

The Reference Design consists of the following blocks:

**ISSUE 2**

- **EOCTL** E1 OCTaL Framer; single device containing eight E1 Framers;

- TOCTL T1 OCTaL Framer; single device containing eight T1 Framers;

- QDSX Quad DSX-1/E1 Line Interface; two devices each containing four E1/DS-1 line interfaces;

- FREEDM FRame EnginE and Data Link Manager; single device interface to PCI Bus:

- Transformers and connectors four dual bi-directional magnetics and connector supporting total of eight (8) bi-directional ports;

- Microprocessor block contains Motorola's MC68340 processor, RAM, ROM, address decoder and supporting digital buffers and logic;

- Serial Ports RS-232 and BDM; the RS-232 port allows control of the QDSX, EOCTL and Microprocessor during test. The BDM port allows faster software/firmware development;

- +5V to +3.3V linear voltage regulators.

The major devices such as EOCTL, TOCTL, QDSX and FREEDM-8 are described in more detail further in this document.

#### 2.3 E1/DS-1 Connector Interface

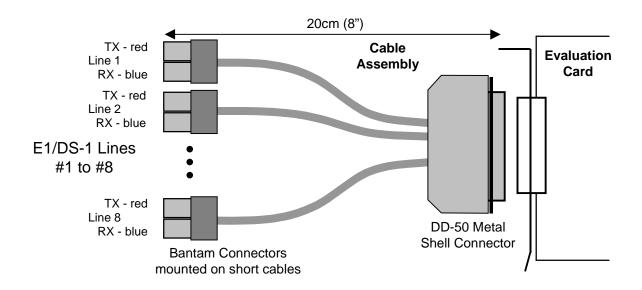

One of the limitations imposed on the EOCTL/TOCTL Evaluation Card is a physical height dimension. The printed circuit board (PCB) is required to fit into a PC with a closed cover. This requirement in return limits the E1/DS-1 connector placement. A standard E1/DS-1 connector consists of two bantam concentric connectors. For this Reference Design a total of sixteen such connectors are required on the front-end of the card, and this is physically impossible. In this case an industry accepted solution is implemented. This consists of a multiple pin E1/DS-1 non-standard connector with attached short pieces of cables and bantam connectors. This connectorization is shown in FIGURE 3 below.

Bantam connectors (and cables) are paired for transmitter and receiver cables corresponding to the same E1/DS-1 line. A standard, DD-50 metal shell connector penetrates through the metal bracket attached to the Evaluation Card. The connector fits into a standard PC Card slot opening at the back of any PC. The mating cable/connector assembly is an integral part of the Evaluation Card.

A full metal body connector helps to keep EMI below FCC Cat B levels.

FIGURE 3. Cable Assembly for Eight E1/DS-1 Lines

ISSUE 2

Bantam connectors are individually wrapped with a colored (red/blue) heat-shrink tubing and then another piece of a heat-shrink tubing packages corresponding pair of transmitter and receiver lines.

The red color depicts transmitter and the blue one depicts receiver.

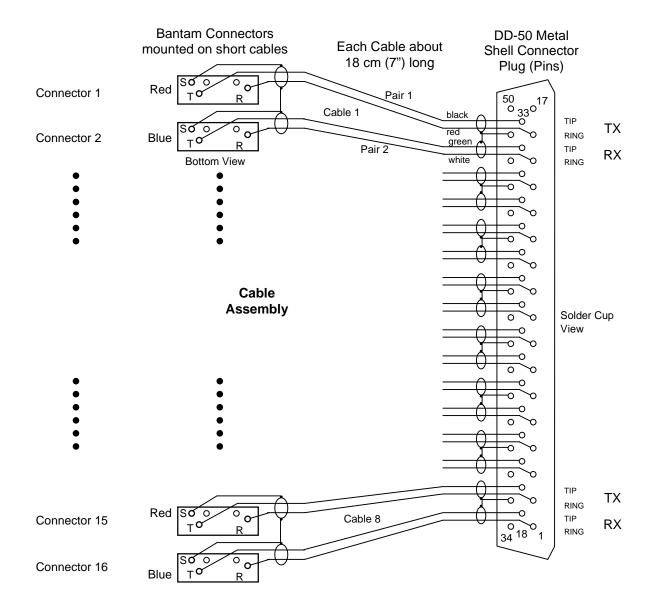

Electrical connections are shown in FIGURE 4 below.

FIGURE 4. Electrical Connection of the DD-50 Connector Harness.

#### 2.4 Transformers and QDSX Line Interface

**ISSUE 2**

#### 2.4.1 Receive Path

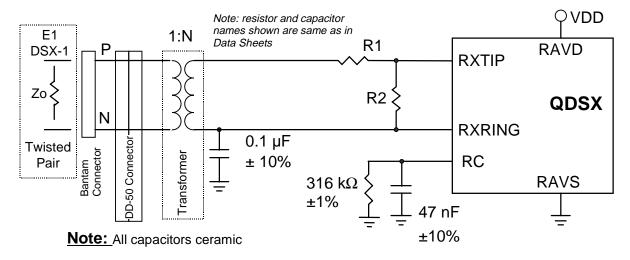

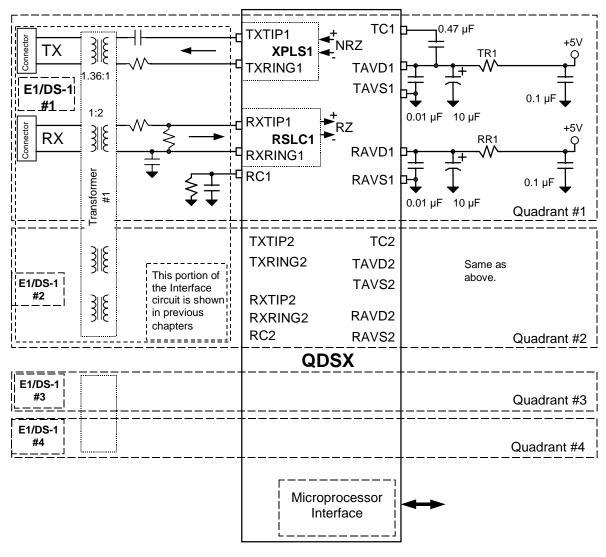

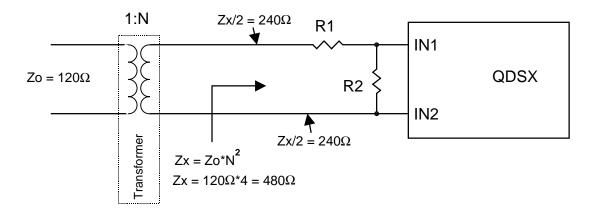

The E1/DS-1 receiver lines are interfaced to the QDSX (line transceivers) via transformers and resistive voltage divider pads. The interface is shown in FIGURE 5 below. To save on costs and board real estate multiple transformer packages are used. A total of four dual, bi-directional magnetics are assembled on the evaluation card.

Signals from transformers are fed into the first stage of the QDSX device, the Analog E1 Pulse Slicer, that is a part of the Receive Data Slicer (RSLC) block. The RSLC block provides the first stage of signal conditioning for the G.703 2048 kbit/s E1 (or 1544kbit/s DSX-1serial data stream by converting bipolar line signals to dual rail RZ pulses. The E1 signal is sliced at 50% (DSX-1 at 67%) of a peak amplitude.

The RSLC block relies on an external network for compliance to the E1 (DSX-1) input port specifications. The RSLC block needs an off-chip attenuator pad to operate in one of four modes: DSX-1 normal mode, DSX-1 bridging mode, E1  $120\Omega$  twisted pair mode and  $75\Omega$  coax mode.

Further details of the signal levels is discussed in section 3.3 "E1/DS-1 Receive Block" below.

The off-chip attenuator pad network is shown in FIGURE 5 below. The network values shown in the table are recommended for the specified applications:

**TABLE 1.** Receive Path Component Values.

|                                         | Format            | Zo   | R1<br>(Ω± 1%) | R2<br>(Ω± 1%) | Squelch Level<br>at Primary<br>(mV Typical) |

|-----------------------------------------|-------------------|------|---------------|---------------|---------------------------------------------|

|                                         | E1                | 120Ω | 357           | 121           | 276                                         |

| Not supported by Reference Design       | E1                | 75Ω  | 205           | 95.3          | 220                                         |

|                                         | DSX-1<br>Normal   | 100Ω | 309           | 93.1          | 227                                         |

| Not supported<br>by Reference<br>Design | DSX-1<br>Bridging |      | 0             | 402           | 50                                          |

ISSUE 2

Tight tolerances are required on the resistors and turns ratio to meet the return loss specification.

**FIGURE 5.** External Analog Receive Interface Circuit.

The Evaluation Card can support E1 or DSX-1 interface. The PCB Card has to have parts assembled to support only one of the standards at the time. No switches/headers are present on the board.

The transformer is designed for use in T1/CEPT/ISDN-PRI applications. Many manufacturers have standard products for these applications. Typical characteristics of a suitable transformer are given in the following table.

TABLE 2. E1/DS-1 Receive Transformer Characteristics

| Turns | •    |    | L <sub>L</sub> | DCR pri. (Ω | DCR sec. |

|-------|------|----|----------------|-------------|----------|

| Ratio |      |    | (µH max.)      | max.)       | (Ω max.) |

| 1:2   | 1.20 | 35 | 0.80           | 0.80        | 1.2      |

OCL is the open-circuit inductance, where

> $C_{w/w}$ is the inter-winding capacitance, is the leakage inductance, and Lı

is the DC resistance.

PMC-Sierra has verified the operation of the RSLC functional block with the following transformers:

- Pulse Engineering PE64931 (1:1:1) and PE64952 (1:2CT)

- BH Electronics 500-1775 (1:1:1) and 500-1777 (1:2CT)

Many manufacturers produce dual transformers containing the 1:2 and 1:1.36 turn ratio necessary for the receiver and transmitter circuits. PMC-Sierra has verified the operation of XPLS and RSLC with the following dual parts:

Pulse Engineering PE64952

ISSUE 2

- Pulse Engineering PE65774 (for extended temperature range)

- BH Electronics500-1777

A quad transformer package T1008 is used in this reference design in order to provide efficient layout.

# 2.4.2 Transmit Path

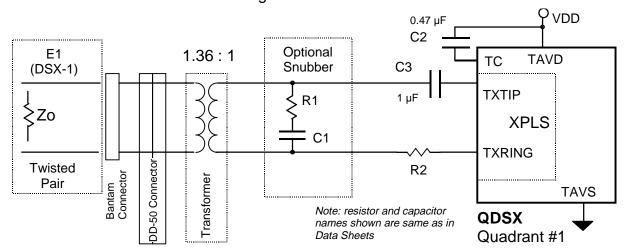

The transmitter interface is shown in FIGURE 6 below. Transmit lines are interfaced from the QDSX to the E1/DS-1 lines via transformers. The serial capacitor prevents DC bias current flow through transformer windings.

The QDSX's internal line driver stage is the Transmit Pulse Generator (XPLS) block. This block outputs pulses specified by Recommendation G.703 at 2048 kbit/s (and 1544 kbit/s). The output pulse shape is synthesized digitally from user-programmed template settings with an internal Digital to Analog (D/A) converter. The signal is presented on the TXTIP[1:4] and TXRING[1:4] outputs.

FIGURE 6. External Analog Transmit Interface Circuit

The step-up transformer "amplifies" the output pulses to their final line interface levels.

A high-frequency negative-going spike may be observed on the falling edge of the transmit pulse. The optional "snubbing" network shown in FIGURE 6 can be used

to filter out this spike. Test performed on the evaluation card shows a need for a snubber circuit for all length of the twisted pair.

**TABLE 3.** E1 Transmitter Interface Component Values

ISSUE 2

|                                   | Format | Zo   | R1<br>(optional<br>snubber) | R2                   | C1              | C2             | С3                  |

|-----------------------------------|--------|------|-----------------------------|----------------------|-----------------|----------------|---------------------|

|                                   | E1     | 120Ω | 47Ω<br>±10%                 | 18Ω<br>±5%,<br>1/8W  | 1000pF<br>±10%  | 0.47uF<br>±10% | 1uF<br>±10%,<br>50V |

| Not supported by Reference Design | E1     | 75Ω  | 47Ω<br>±10%                 | 6.2Ω<br>±5%,<br>1/8W | 1000pF<br>±10%  | 0.47uF<br>±10% | 1uF<br>±10%,<br>50V |

|                                   | DSX-1  | 100Ω | 22Ω<br>±10%                 | Ω0                   | 10000pF<br>±10% | 0.47uF<br>±10% | 1uF<br>±10%,<br>50V |

The R2 resistor value, shown in table above, differs from the standard data sheet value. That may be related to a new type of transformer (T008) and a specific cable interface (DD-50 connector) used for this reference design.

Resistor R2 in conjunction with snubber R1/C1 can control overshoot. This reference design requires a permanent snubber as specified in the table above and R2 at  $18\Omega$  on the E1 board. DSX1 interfaces use R2 at  $0\Omega$  Designers should verify compliance of the E1/DSX-1 waveform with appropriate templates by adjusting values of the R2 resistor and use of a snubber.

The evaluation card supports both E1 and DSX-1 interfaces, and the PCB Card has to be configured at assembly to support the desired mode of operation. No switches/headers are present on the board to reconfigure the line interface.

The line interface transformer should be designed for use in T1/CEPT/ISDN-PRI applications. Many manufacturers have standard products for these applications. Typical characteristics of a suitable transformer are given in the following table.

REFERENCE DESIGN PMC-980474

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

**TABLE 4.** E1 Transmit Transformer Characteristics

| Turns<br>Ratio | OCL C <sub>W/v</sub><br>(mH min.) (pF ma |    | LL<br>(µH max.) | DCR pri. (Ω<br>max.) | DCR sec. (Ω max.) |

|----------------|------------------------------------------|----|-----------------|----------------------|-------------------|

| 1:1.36         | 1.20                                     | 35 | 0.80            | 0.80                 | 1.2               |

Where OCL is the open-circuit inductance,

$C_{w/w}$  is the inter-winding capacitance,

L<sub>L</sub> is the leakage inductance, and

DCR is the DC resistance.

PMC-Sierra has verified the operation of the XPLS functional block with the following 1:1.36 transformers:

- Pulse Engineering PE64937 (1:1.36)

- Pulse Engineering PE65340 (1:1.36) (for extended temperature range)

- BH Electronics 500-1776 (1:1.36)

There are many manufacturers making dual transformers on the market. Hybrid packages contain 1:2 and 1:1.36 transformers necessary for the receiver and transmitter circuits. PMC-Sierra has verified the operation of XPLS and RSLC with the following dual parts:

- Pulse Engineering PE64952

- Pulse Engineering PE65774 (for extended temperature range)

- BH Electronics500-1777.

To save on cost and board real estate a multiple transformer package is used. A total of four dual, bi-directional magnetics are assembled on the card.

# 2.5 Clock Distribution

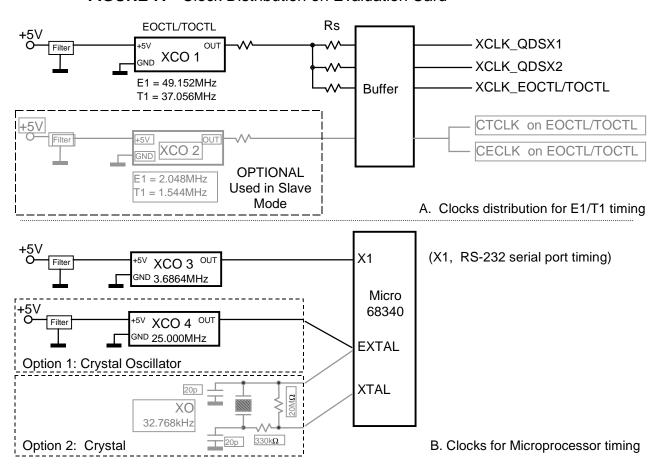

The Reference Design employs crystal oscillators to provide stable clock timing for transmitted E1/T1 data. The clock distribution block diagram is presented in FIGURE 7 below.

FIGURE 7. Clock Distribution on Evaluation Card

ISSUE 2

# 2.5.1 E1/T1 Timing

The crystal oscillator XCO1, shown in FIGURE 7 above, provides timing for EOCTL/TOCTL and QDSX devices. The EOCTL/TOCTL device on this reference design is set to a Master Clock Mode and requires only a single clock at the XCLK input. The line clock is derived from the XCLK by dividing it down by 24. A 50 ppm frequency tolerance is required to meet Recommendation G.703. Therefore, the following oscillators are used:

E1 – 49.152MHz ±50 ppm (parts per million);

ISSUE 2

T1 – 37.056MHz ±50 ppm (parts per million).

In a Slave Clock Mode the EOCTL/TOCTL requires line rate clock input on its CTCLK/CECLK inputs. This is shown with shaded lanes in the above diagram.

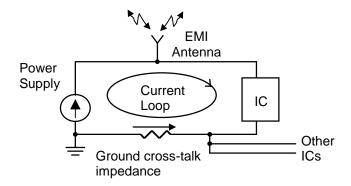

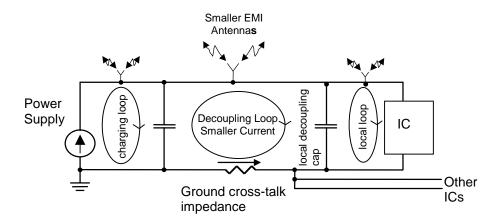

Each crystal oscillator is powered through a low pass filter to minimize EMI radiation and/or interference to other blocks on the Reference Design circuitry. More on power supply filtering can be found in section 9.1.4 below.

# 2.5.2 Microprocessor Clocks

The microprocessor requires two clock signals to operate as shown in FIGURE 7 above.

The main clock can be fed from an external crystal oscillator or it can be synthesized using a low-cost crystal and internal PLL. This reference design has the 25MHz clock supplied from an external crystal HCMOS oscillator (XCO4). The crystal option (and internal PLL) is desired for a cost-sensitive design.

The second clock signal is used for the RS-232 serial port timing. That signal is fed from a crystal oscillator XCO3 at 3.6864 ±100ppm.

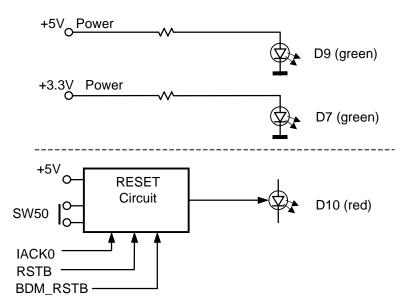

#### 2.6 LED Indicators

The Reference Design employs green and red LEDs for a visual indication of some parameters. A simplified block diagram shown in FIGURE 8 below depicts the LED's functions.

#### 2.6.1 Power Indicators

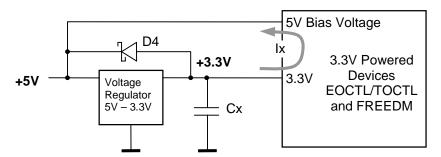

The green LEDs are used to signal the presence of +5V and +3.3V. The LED D3 is dedicated to +5V. It turns on if "+5V" line exceeds +2.2V. The LED D5 turns on

if the "+3.3V" line exceeds +2.5V. Those LEDs are used to show that power is being supplied to the board.

#### 2.6.2 Reset Indicator

The red LED D10 is associated with the RESET circuit. D10 signals logic low on RSTB line. This line resets the Microprocessor, QDSX and EOCTL/TOCTL devices.

The Reset indicator is activated on five conditions:

ISSUE 2

- on power up while capacitor C1 is charged

- when push-button switch SW50 is activated

- if microprocessor sets IACK0 line "low" ("0")

- if microprocessor activates RSTB by pulling it "low"

- on reset from an external BDM interface.

#### FIGURE 8. Led Indicators.

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

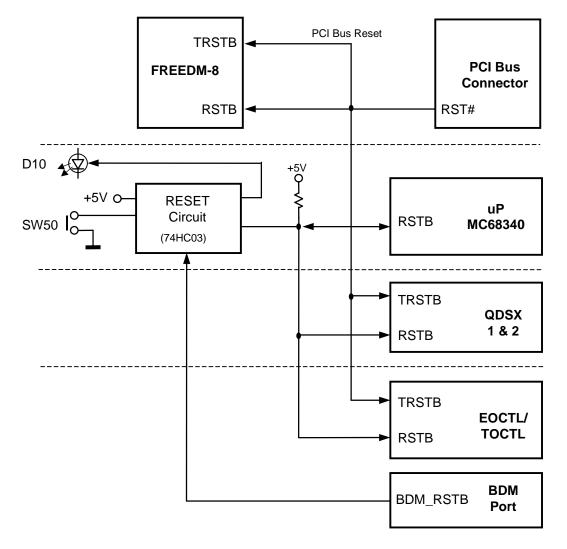

## 2.7 Reset Circuit

The reset circuit block diagram, used for this Reference Design, is shown in FIGURE 9 below. Each block is described in subsequent sections.

FIGURE 9. Reset Circuit.

#### 2.7.1 PCI Bus Reset

The PCI Bus connector provides an active low RST# reset line. This line is used as a main reset for the FREEDM-8 device and as a boundary scan reset for FREEDM-8, QDSX and EOCTL/TOCTL devices (TRSTB). The Microprocessor can not be reset with this line.

PMC-Sierra, Inc.

REFERENCE DESIGN PMC-980474

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

An option for a manual reset is not available on the Evaluation Card.

The RST# reset line is active on system power-up and/or per PCI Bus interface requirement.

## 2.7.2 Microprocessor Reset Line RSTB

The microprocessor reset RSTB is active low. This interface is an input/output on the MC68340. The RSTB signal can be generated with the reset circuit or by the microprocessor itself (software reset). The reset circuit employs an open drain 47HC03 device and that allows connecting two active outputs together. A pull-up resistor is required.

A push-button switch SW50 is used for manual reset of all devices connected to the RSTB\I net (Microprocessor, QDSXs, and EOCTL/TOCTL). The BDM port, connected through a NAND gate, can also generate reset.

When the RSTB line is asserted by software or hardware means (active low), a red LED D10 turns on to display the reset status present on the board.

# 3 QDSX DEVICE DESCRIPTION

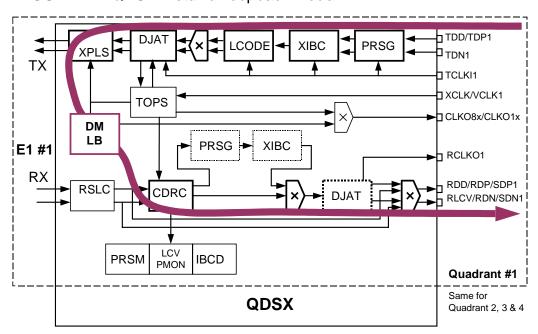

The PM4314 QDSX Quad T1/E1 Line Interface Device is a monolithic integrated circuit supporting G.704-compatible transmit and receive interfaces for four 2048 kbit/s E1 data streams or four 1544kb/s T1 data streams. Two QDSX devices are assembled on the Evaluation Board.

# 3.1 QDSX Block Diagram

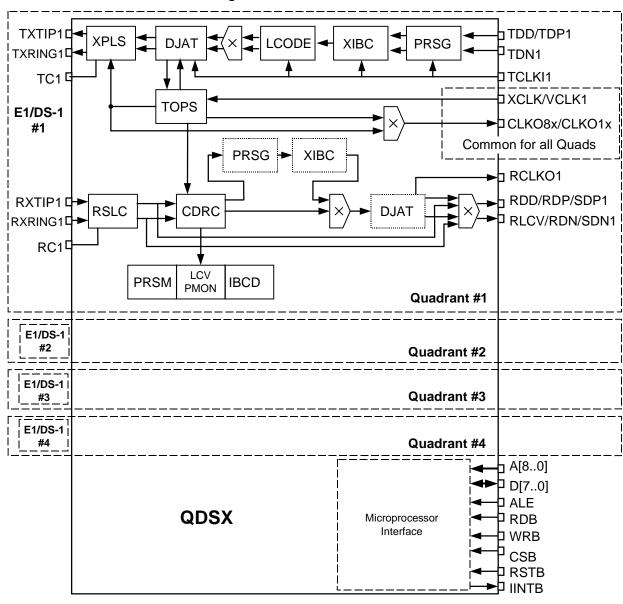

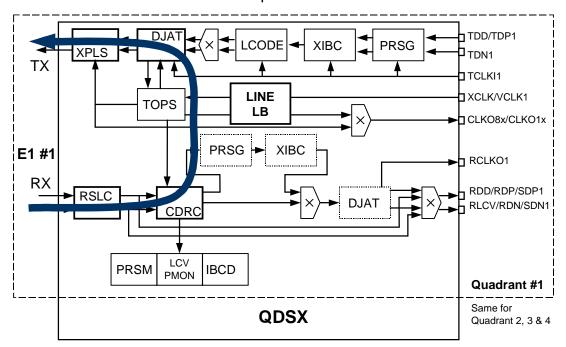

FIGURE 10. Block Diagram

ISSUE 2

REFERENCE DESIGN PMC-980474

**ISSUE 2**

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

#### 3.2 E1/DS-1 Transmit Block

#### 3.2.1 Transmit Interface

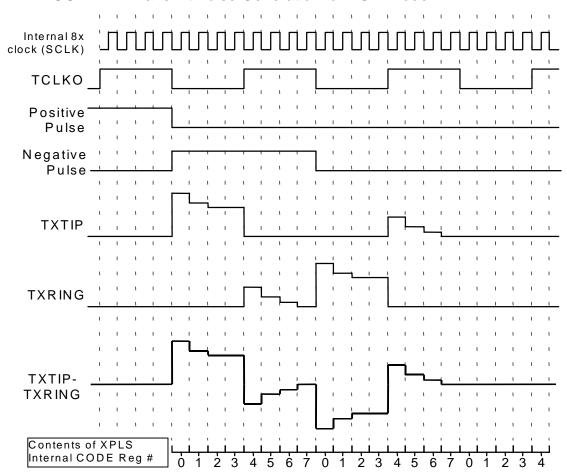

The TXTIP and TXRING are the output pins for the Transmit Pulse Generator (XPLS) block. This block functions as the Analog Pulse Generator converting NRZ signals into line signals suitable for use in a G.703 intra-office environment.

A logical "1" on the positive NRZ input to XPLS causes a positive pulse to be transmitted on an E1/DS-1 line. A logical "1" signal on the negative NRZ input to XPLS causes a negative pulse to be transmitted on a E1/DS-1 line. If both positive and negative NRZ inputs to XPLS are logical "0" or "1," no output pulse is transmitted.

The output wave shape is synthesized digitally from a user programmed template with an internal digital-to-analog (D/A) converter. A 4-bit (16 levels) D/A converter is updated eight times per period with programmed words. These words define the output pulse shape. Recommended codes for CEPT E1 120  $\Omega$  and DS-1 110  $\Omega$  symmetrical lines are given in the Operations section of the Data Sheet [1]. If an external circuit differs from the recommended one, the pulse generator permits creation of custom pulse shapes. Again refer to the Data Sheet [1] operations section for details. An example of a pulse generation is shown in FIGURE 12 below.

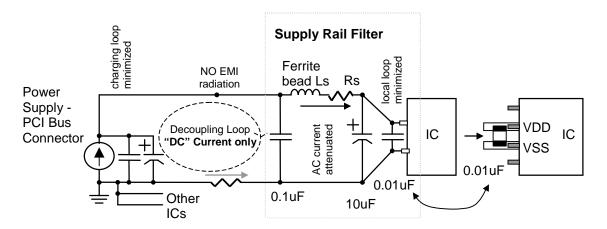

Each quadrant Transmitter has dedicated power supply pins as shown in FIGURE 11 below. The TAVD[1:4] are +5V lines fed via dedicated filters. Care must be taken to avoid coupling noise between quadrants and from transmitter to receiver on the same quadrant. Therefore RC elements are used to prevent power rail noise propagatiion to/from different circuitry on the Evaluation Card. The 0.01 uF capacitors must be placed as close as possible to the corresponding TAVD[1:4] and TAVS[1:4] pins. The 0.47uF capacitor is used to decouple the internal reference generator and must be connected from the TC[1:4] pin to the 0.01 uF filtering capacitor and corresponding TAVD[4:1]. A serial inductor and a resistor provide attenuation of supply current noise. Resistor RR1/TR1 and the 0.01/10 uF capacitors provide interference attenuation. Resistor value for TR1 can be calculated to have voltage drop of no more than 50 mV to prevent supply voltage mismatch.

The tantalum capacitor and the serial resistor help to meet the requirements stated in the data sheet [1]: "Analog power supplies must be applied after both VDDI[3:1] and VDDO[6:1] have been applied or they must be current limited to less than the maximum latchup current specification (100 mA). In normal operation the differential voltage measured between the TAVD[4:1] and RAVD[4:1]

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

supplies and the VDDI[3:1] and VDDO[6:1] supplies must be less than 0.5 volt. The relative power sequencing of TAVD[4:1] and RAVD[4:1] power supplies is not important."

Ground pins TAVS[1:4] must be connected immediately to the ground plane with traces as short as possible in order to keep inductive effects low.

FIGURE 11. E1/DS-1 Interface of QDSX Device

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# 3.2.2 Programming the XPLS Waveform Template

An example of a DS-1 output waveform is presented in FIGURE 12 below.

FIGURE 12. Transmit Pulse Generation for DS-1 Mode

The highlighted curve above shows that the pulse-shape is not intuitive and is built with a complex algorithm. The final waveform produced depends on transformer and associated components, as shown in FIGURE 6 in the previous chapter.

The Data Sheet [1] in chapter "OPERATIONS" (page 100) show recommended values for the D/A converter (driver). Register 02CH (06CH, 0ACH and 0ECH) Bit7 RPT sets the default values. However, in some cases, transmitted wave-shape may not meet the ANSI template for DS1 and E1. In this instances the values specific to the layout, employed transformers, connectors and cable harness must be determined. For the reference design this has been verified through a test and is shown in the table below.

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

**TABLE 5.** Transmit XPLS Code (for meeting ANSI DS-1/E1 template).

|                                                          | Length<br>Setting                | <u> </u> |   |   |   |   |   |   | ues |

|----------------------------------------------------------|----------------------------------|----------|---|---|---|---|---|---|-----|

|                                                          | [ft]                             | 0        | 1 | 2 | 3 | 4 | 5 | 6 | 7   |

|                                                          | 0 – 110                          | 9        | 9 | 9 | 9 | 1 | 1 | 1 | 0   |

|                                                          | 110 – 220                        | А        | 9 | 9 | 9 | 2 | 3 | 1 | 1   |

| DS-1                                                     | 220 – 330                        | С        | Α | Α | А | 3 | 3 | 1 | 1   |

| With the                                                 | 330 – 440                        | D        | В | Α | Α | 4 | 3 | 2 | 1   |

| serial resistor at $0\Omega$ and                         | 440 – 550                        | Е        | В | В | Α | 6 | 3 | 3 | 1   |

| snubber                                                  | 550 – 660                        | F        | С | В | В | 7 | 4 | 3 | 1   |

| E-1 With the serial resistor at 18Ω and snubber in place | All length<br>G.703<br>2048 kb/s | В        | В | В | В | 0 | 0 | 0 | 0   |

NOTE: on the TOCTL version of the evaluation card the QDSX devices have default setting on power-up at 0 – 110 feet cable length. Other cable length can be programmed through a serial port.

It was confirmed through a test that the DS-1 transmit circuit requires snubber circuit to be assembled to meet ANSI T1.102 (and ANSI T1.403 (1989)) DSX-1 template.

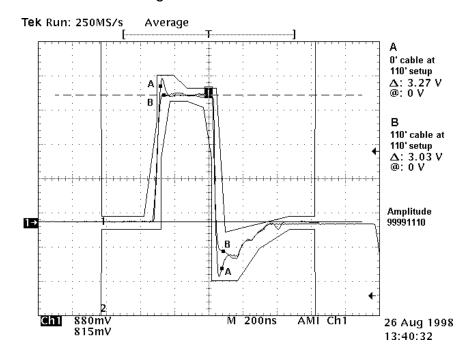

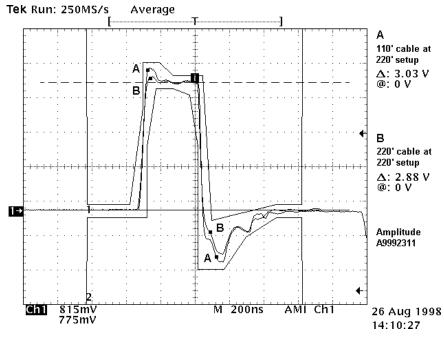

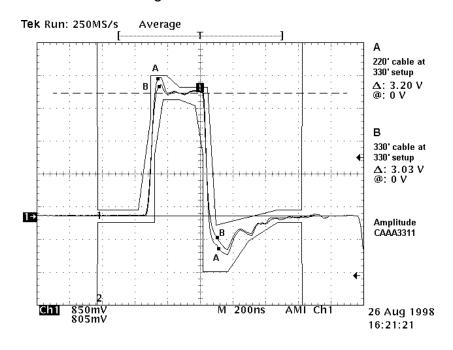

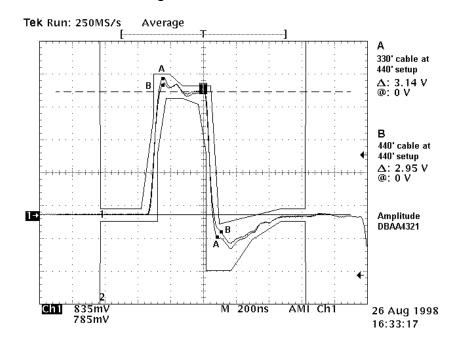

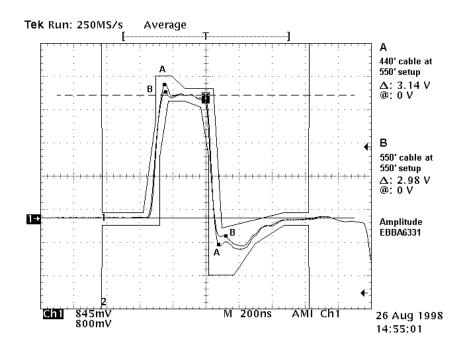

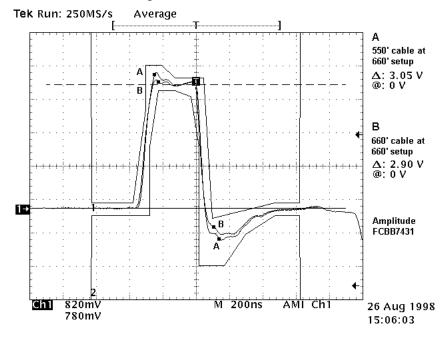

The waveforms corresponding to each cable length settings, shown in TABLE 5 above, are presented below in FIGURE 13, FIGURE 14, FIGURE 15, FIGURE 16, FIGURE 17 and FIGURE 18. Each figure has two waves superimposed to show waveform at the minimum and maximum length (DSX-1) of a cable for each cable setting.

**FIGURE 13.** DSX-1 Waveforms at 0 Feet (A) and 110 Feet (B) with XPLS setting at 0-110 feet.

**FIGURE 14.** DSX-1 Waveforms at 110 Feet (A) and 220 Feet (B) with XPLS setting at 110-220 feet.

**FIGURE 15.** DSX-1 Waveforms at 220 Feet (A) and 330 Feet (B) with XPLS setting at 220-330 feet.

**FIGURE 16.** DSX-1 Waveforms at 330 Feet (A) and 440 Feet (B) with XPLS setting at 330-440 feet.

**FIGURE 17.** DSX-1 Waveforms at 440 Feet (A) and 550 Feet (B) with XPLS setting at 440-550 feet.

**FIGURE 18.** DSX-1 Waveforms at 550 Feet (A) and 660 Feet (B) with XPLS setting at 550-660 feet.

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

FIGURE 19. E1 Waveforms.

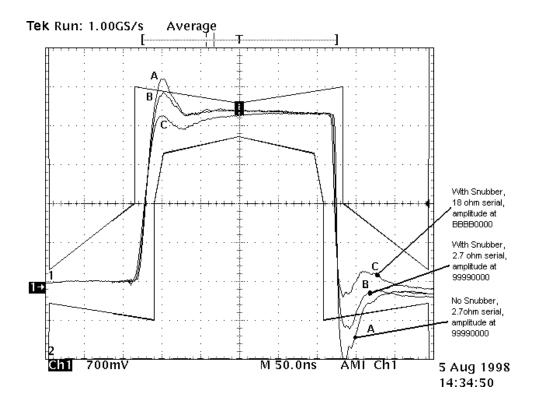

Three waveforms for E1 transmitter are superimposed and are shown in FIGURE 19 below. Waveform A shows an E1 signal without a snubber and the serial resistor at 2.7 ohm (as recommended in [1]). Waveform B shows signal with the snubber in place and a serial resistor of 2.7 ohm. Waveform C shows a transmitted signal with the snubber in place and the serial resistor of 18 ohm. The amplitude of the C waveform was set to BBBB0000 to compensate for signal loss associated with a higher value of the serial resistor.

It is clearly visible that curves A and B do not fit into the E1 template. Waveform C meets the requirement. The waveform C passed the CTR-4 Layer1 test at TUV Telcom Services, Inc.

REFERENCE DESIGN PMC-980474

**ISSUE 2**

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

#### 3.3 E1/DS-1 Receive Block

The RXTIP and RXRING are the inputs to the Analog Pulse Slicer (RSCL) block. This is the first stage of the QDSX signal conditioning. A bipolar G.703 serial data stream is converted to dual rail RZ pulses.

In  $120\Omega$ E1 mode, the amplitude of a received pulse at the 1:2 line-coupling transformer's primary can be in the range from 3.3V to 1.4V (depending on the length of the cable from the signal source). In this mode, the QDSX can receive signal levels down to a typical squelching level of 276mV, which means that there is 14.1 dB margin between the minimum expected signal level and the typical minimum receivable signal level.

In  $75\Omega E1$  mode, the amplitude of a received pulse at the 1:2 line-coupling transformer's primary can be in the range from 2.6V to 1.1V (depending on the length of the cable from the signal source). In this mode, the QDSX can receive signal levels down to a squelching level of 220mV which means that there is a 14.0 dB margin between the minimum expected signal level and the minimum receivable signal level in the worst case.

The RSLC block provides a squelching circuit, which indicates an alarm when input pulses are below the squelching level threshold. In this state, data is not sliced, which prevents the detection of noise on an idle transmission line. The "low level" signal condition or "signal squelch" may be enabled to generate interrupts. Clock and data are recovered from the dual rail RZ digital pulses using a digital phase-locked loop that provides excellent high frequency jitter tolerance. The recovered data is decoded using B8ZS line code rules. Loss of signal and line code violations are detected as well as excessive zeros, and B8ZS signatures. These various events or changes in status may be enabled to generate interrupts. Additionally, loss of signal and line code violations is also indicated on outputs. The SQ status bit in the RSLC Interrupt Enable/Status registers (031H, 071H, 0B1H, and 0F1H) goes high whenever the RSLC block is squelching the input signal. The RSLC can be configured to generate an interrupt whenever the SQ status bit changes state.

Each quadrant Receiver has dedicated power supply pins. The RAVD[1:4] are the +5V lines fed via dedicated filters. Care must be taken to avoid coupling noise between quadrants and from transmitter to receiver on the same quadrant. Therefore RC elements are used to prevent power rail noise propagation to/from different circuitry on the Evaluation Card. The 0.01 uF capacitors must be placed as close as possible to the RAVD[1:4] and RAVS[1:4] pins. A serial inductor and a resistor provide attenuation of supply current noise. Resistor TR1 and 10uF (SMD tantalum) capacitor provide attenuation at low frequency. The RL1 inductor and

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

0.01/10 uF capacitors provide attenuation at high frequency. Resistor value for RR1 can be calculated to have a voltage drop of no more than 50 mV to prevent supply voltage mismatch.

The tantalum capacitor and the serial resistor help to meet requirement stated in data sheet [1]: "Analog power supplies must be applied after both VDDI[1:3] and VDDO[1:6] have been applied or they must be current limited to less than the maximum latchup current specification, (100 mA). In normal operation the differential voltage measured between TAVD[1:4] and RAVD[1:5] supplies and VDDI[1:3] and VDDO[6:1] must be less than 0.5 volt. The relative power sequencing of TAVD[1:4] and RAVD[1:4] power supplies is not important."

Ground pins RAVS[1:4] must be connected immediately to the ground plane with traces as short as possible.

# 3.4 Drop Side Interface

The drop side interface (backplane) provides data and clock for both directions of the E1/T1 interface. In the transmit direction three data lines are interfaced:

- TDD/TDP Transmit Data in a single rail mode or Positive Transmit Data in dual-rail mode.

- TDN Negative Transmit Data in a dual-rail mode.

- TCLKI Transmit Clock Input, 2.048 MHz for E1 (1.544 MHz for T1).

In the receive direction data is output on three lines:

- RDD/RDP Receive Data in a single rail mode or positive receive data in dual-rail mode.

- RDN Negative Transmit Rail in a dual-rail mode.

- RCLKO Receive Clock Output, 2.048 MHz for E1 (1.544 MHz for T1).

There are two additional clock line interfaces:

High-speed XCLK clock is the timing reference required by many portions of the QDSX. XCLK is nominally a 24 x 2.048 MHz = 49.152 MHz for E1 or 37.056 MHz for T1. When jitter attenuation is not required, an 8x clock can drive XCLK at 16.384 MHz for E1 or 12.352 MHz for T1.

The other clock interface is the CLKO8x/CLKO1x. This output has two modes of operation. The first one provides a divide by three the 24x clock. In the second mode, when an 8x clock is input to XCLK, this pin outputs a divide by eight clock. This baseband E1 clock can be used to drive all four quadrants in synchronous mode by feeding this signal parallel to all TCLK[1:4].

# 3.5 Loopback Options

The QDSX provides three modes of loopbacks. Loopback paths are shown in FIGURE 20, FIGURE 21and FIGURE 22 below. Only the first quadrant of the QDSX is shown for simplicity.

FIGURE 20. QDSX Line Loopback Mode

ISSUE 2

The Line Loopback provides diagnostic capabilities for the E1 line interface side. In this case the signal is sliced (RSLC), reclocked (CDRC) and run through a jitter attenuator (DJAT) before being looped back (XPLS). Detecting loopback code in an incoming E1 data stream can activate this loopback also.

FIGURE 21. QDSX Diagnostic Loopback Mode.

ISSUE 2

DIALB is a diagnostic digital line loopback used to verify integrity of the data path at the system side of the QDSX device.

FIGURE 22. QDSX Metallic Loopback Mode.

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

The DMLB is a diagnostic metalic loopback mode, where the digital RZ version of the TX signals are internally connected to the receive input at CDRC.

### 3.6 Transmit Jitter Attenuation

The QDSX device provides jitter attenuation in the transmit direction of E1/DS-1 interface using the Digital Jitter Attenuator (DJAT) block (with FIFO). The DJAT input jitter tolerance is 35 Unit Intervals peak-to-peak (Ulpp) for an E1 interface with the worst case frequency offset of 308 Hz. The input jitter tolerance is 29 Ulpp for a DS-1 interface with the worst case frequency offset of 354 Hz. It is 48 Ulpp with no frequency offset. The frequency offset is the difference between the frequency of XCLK divided by 24 and that of the input data clock.

The DJAT generates a "jitter-free" 2.048/1.544 MHz clock by adaptively dividing the 24x XCLK input. Adaptation is done according to the phase difference between the generated "jitter-free" clock and the input data clock to DJAT (TCLKI[X] when DJAT is in the default transmit path, or the recovered clock RCLKO[X] if in line loopback mode or when DJAT is configured to be on the receive path). Phase variations in the input clock with a jitter frequency above 8.8 Hz (for the E1 format) or 6.6 Hz (for the T1 formats) are attenuated by 6 dB per octave of jitter frequency. The "jitter-free" clock tracks phase variations below these jitter frequencies.

For further details please refer to the QDSX Data Sheet [1].

### 3.7 Receiver Jitter Tolerance and Jitter Attenuation

The E1 line receiver provides jitter tolerance that complies with ITU-T Recommendation G.823. Jitter tolerance is determined by performance of the Clock and Data Recovery unit (CDRC). The tolerance is measured with a PRBS20 (with 14 zero restriction) sequence. The QDSX provides two options for the jitter tolerance characteristics. The first option provides better tolerance at low jitter frequencies and the second one provides better jitter tolerance at high jitter frequencies. The DSX-1 interface complies with Bellcore TA-TSY-000170 and AT&T TR62411 specifications.

The jitter attenuation (DJAT) function can optionally be moved to the receive side. The recovered clock and data is passed through the jitter attenuator before being presented at the digital receiver block outputs.

For further details please refer to the QDSX Data Sheet [1].

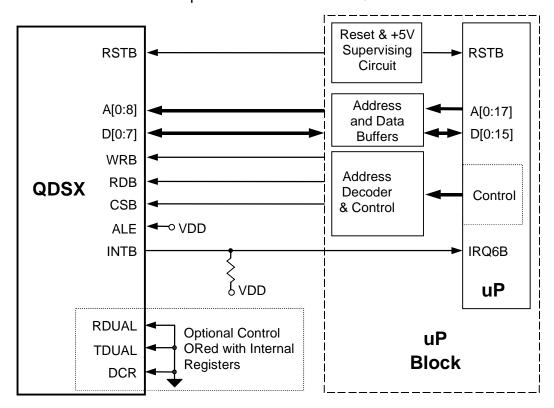

# 3.8 Microprocessor Interface to QDSX

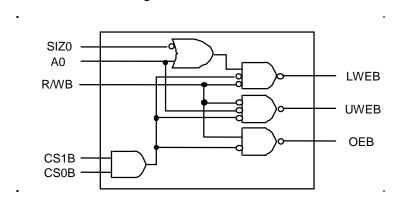

The QDSX device provides a generic microprocessor interface. This is shown in FIGURE 23.

FIGURE 23. Microprocessor Interface on QDSX

ISSUE 2

Optional control lines (RDUAL, TDUAL and DCR) are connected to GND and are not used for QDSX control. The same functions are executed via writing to registers through uP port. The interrupt signal INTB is an open-drain output that can be wire ORed with other device. INTB needs a +5V pull-up resistor.

The QDSX device is fully configurable for normal and test modes through the microprocessor interface. The normal mode register access allows the QDSX to be to configured and monitored. The test mode option allows the execution of production test, board test and troubleshooting.

For more on microprocessor interface timing see to references [1], [9] and [11].

### 4 EOCTL DEVICE DESCRIPTION

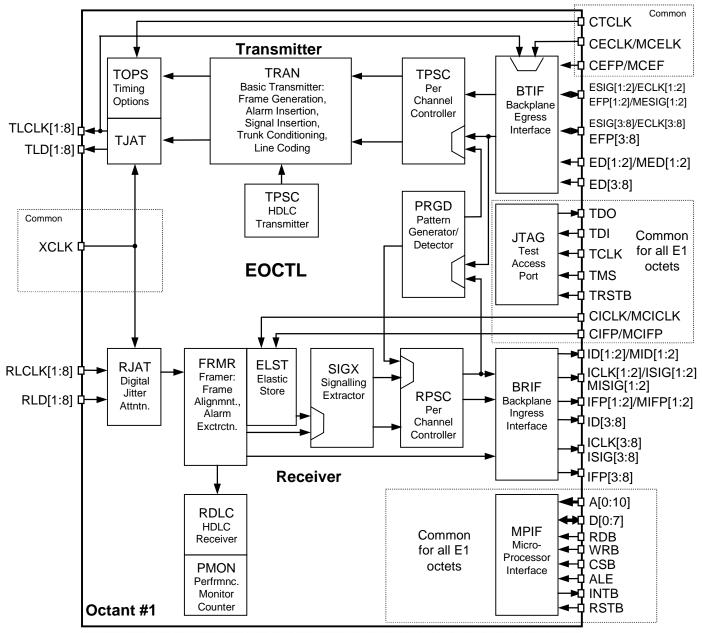

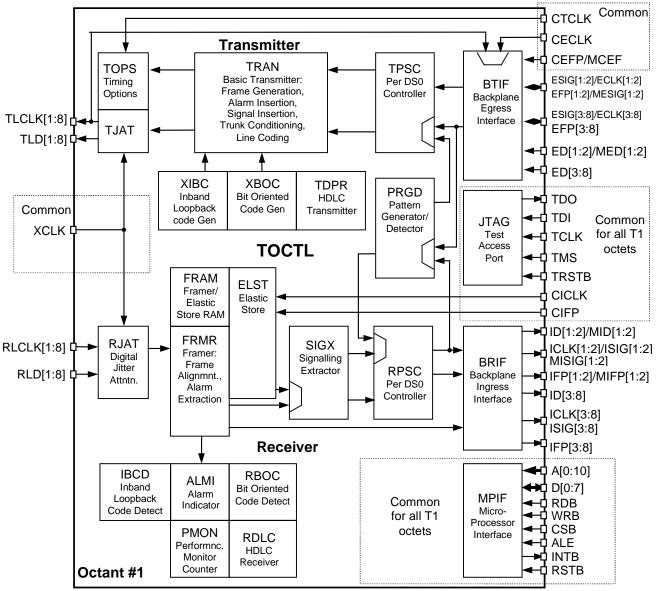

# 4.1 Block Diagram

FIGURE 24. EOCTL Block Diagram (Octant #1)

ISSUE 2

NOTE: Octant #1 shown only. Blocks common to all octets are framed with dashed line. Power supply and ground pins not shown.

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

The block diagram shows one of the eight octants inside the EOCTL device. All common blocks are framed with dashed line. Other octants are not shown due to complexity of the circuit.

The PM6388 E1 OCTaL Framer (EOCTL) is a feature-rich device for use in systems carrying data (frame relay, Point to Point Protocol, and other protocols) or voice over E1 facilities. Each of the framers and transmitters are independently software configurable, allowing feature selection without changes to external wiring.

On the receive line interface side, each of the eight independent framers can be configured to frame a basic G.704 2048 kbit/s signal as well as finding the signaling multiframe alignment signal and the CRC multiframe alignment. Framing can also be bypassed (unframed mode). The EOCTL detects and indicates the presence of various alarm conditions such as loss of frame-alignment, loss of signaling multiframe alignment, loss of CRC multiframe alignment, reception of remote alarm indication signals, remote multiframe alarm signals, alarm indication signal (AIS) and timeslot 16 alarm indication signal. The EOCTL integrates red and AIS alarms as per industry specifications. Performance monitoring with accumulation of CRC-4 errors, far-end block errors, framing bit errors, and out-of-frame events is also provided.

The EOCTL also detects and terminates HDLC messages on TS16, the Sa National bits, and/or on any arbitrary timeslot. Each HDLC link is terminated in a 128 byte FIFO.

Each of eight independent framers can be configured to frame to either of the common E1 signal formats: CRC-4 MF or to be bypassed (unframed mode). The EOCTL detects and indicates the presence of YELLOW and AIS patterns and also integrates YELLOW, RED, and AIS alarms.

Performance monitoring with accumulation of CRC-4 errors, framing bit errors, out-of-frame events, and changes of frame alignment is provided. The HDLC messages are terminated in a 128-byte FIFO. An elastic store that optionally supports slip buffering and adaptation to back plane timing is provided, as is a signaling extractor that supports signaling de-bounce, signaling freezing and interrupt on signaling state change on a per-DS0 basis. The EOCTL also supports idle code substitution and detection, digital milliwatt code insertion, data extraction, trunk conditioning, data sign and magnitude inversion, and pattern generation or detection on a per-DS0 basis.

On the transmit side, the EOCTL generates framing for CRC-4 MF E1 formats, or framing can be optionally disabled. The EOCTL supports signaling insertion, idle

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

code substitution, data insertion, line loopback, data inversion, zero-code suppression, and pattern generation or detection on a per-E0 basis.

The EOCTL can generate a low jitter transmit clock, and also provides jitter attenuation in the receive path.

It should be noted that the EOCTL operates on unipolar data only. The E1 HDB3 and DS-1 B8ZS substitution and line code violation monitoring, if required, must be processed by the E1/DS-1 LIU, in this case the QDSX.

The system side of the EOCTL supports clock, data and framing interfaces. On the Evaluation Card the EOCTL device connects to FREEDM-8. The EOCTL also supports an alternative backplane interface where up to 4 links can be bytemultiplexed onto one of two 8.192Mbps buses.

Further information on the EOCTL can be found in the long form data sheet [2].

#### 4.2 **EOCTL Device – Transmit Direction**

The "Transmit Direction" is referred to a direction, where gapped data from the system side (egress) is input to the EOCTL, processed by the EOCTL and output on the line interface side (of the EOCTL) as a continuous NRZ data and clock.

# 4.2.1 BTIF - Backplane Egress Interface

This interface receives payload serial data and clock from the FREEDM device. **NOTE:** This reference design has the default power-up state set to: Master Clock, NxTS Mode, Gapped Clock, 2.048mbit/s Receive/Transmit rates modes. Other operation modes are not discussed in this document.

The EOCTL internal system timing clock is fed from an on board crystal oscillator.

Functions and connections of each BITF interface are as follows:

• Egress Data ED[1:8] - the egress data streams are input on these pins. ED[x] lines are shown on the Block Diagram in two subsections ED[1:2]/MED[1:2] and ED[3:8]. The MED[1:2] supports multiplexed data, and is not used on this Reference Design. Therefore, only the ED[1:8] inputs are used. The Clock Master *NxTS* mode is active on the Evaluation Card. ED[x] is sampled on the rising edge of ECLK[x].

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

- Egress Clock (ECLK[1:8]) clock for the ED[1:8] data. The Gapped Mode is used. The instantaneous clock speed is 2.048MHz. The gap is used by FREEDM-8 to determine the beginning and the end of the data stream as there are no framing pulses available. The gap coincides partially with the framing signal. The gapped clock is fed from EOCTL to FREEDM device.

- On this reference design default is to gap all DS0 timeslots, while time slots DS1 through DS31 are clocked in. The timeslot DS0 is used by EOCTL to insert framing bits. ECLK[x] is a version of a TLCLK[x] clock. The TLCLK[x] is by default derived from the XCLK by divide by 8. ED[x] is sampled on the rising edge of the associated ECLK[x].

- Common Transmit Clock (CTCLK). A Slave Clock Mode is not supported on this reference design and therefore CTCLK is terminated to ground. A provision for an external clock is laid out on the PCB. A 1x2 header TP24/TP25 allows an external clock to be fed to the EOCTL/TOCTL device for a test and demonstration purposes only. The CTCLK has to be at 2.048MHz for E1 and 1.544MHz for DS-1.

- Common Egress Clock (CECLK) / Multiplexed Common Egress Clock (MCECLK). This reference design does not support this clock interface. A provision for an external clock is laid out on the PCB and is connected in parallel to CTCLK see above. The CECLK must be 2.048MHz for E1 or 1.544MHz for DS-1. For more on clock options see reference [2].

- Common Egress Frame Pulse (CEFP) / Multiplexed Common Egress

Frame Pulse (MCEFP) this framing bit input is not used on this

Reference Design and is connected to GND.

The egress interface has two modes of operation: Non-Multiplexed Bus Egress Mode and Multiplexed Bus Egress Mode. The Non-Multiplexed mode is used on this Reference Design.

<u>The Non-Multiplexed Bus Egress Modes</u>. In this mode the egress Interface allows egress data to be inserted into the transmit line using one of four possible modes. These modes are selected by the ECLKSLV and ESIG\_EN bits in the Transmit Backplane Configuration and Egress Interface Options Registers.

For more on bus modes see reference [2].

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

#### 4.2.2 TPSC – Per-Channel Controller

The Transmit Per-DS0 Serial Controller allows data and signaling trunk conditioning or idle code to be applied on the transmit E1 stream on a per-channel basis. It also allows per-channel control of zero code suppression, data inversion, per-channel loopback (from the ingress stream), channel insertion, and the detection or generation of pseudo-random or repetitive patterns.

The TPSC interfaces directly to the TRAN block and provides serial streams for signaling control, idle code data, digital milliwatt insertion, and egress data control.

#### 4.2.3 TRAN – Basic E1 Transmitter

The E1 Transmitter (TRAN) generates a 2048 kbit/s data stream according to ITU-T recommendations, providing individual enables for frame generation, CRC-4 Multi-frame generation, and channel associated signaling (CAS) multi-frame generation.

In concert with Transmit Per-Channel Serial Controller (TPSC), the TRAN block provides per-timeslot control of idle code substitution, data inversion, digital milliwatt substitution, selection of the signaling source and CAS data. All timeslots can be forced into a trunk conditioning state (idle code substitution and signaling substitution) by use of the master trunk conditioning bit in the Configuration Register.

Common Channel Signaling (CCS) is supported in timeslot 16 through the internal HDLC Transmitter (TDPR). Support is provided for the transmission of AIS and TS16 AIS, and the transmission of remote alarm (RAI) and remote multiframe alarm signals.

The E1-TRAN supports insertion of 4-bit code words into the National Bits Sa4 to Sa8 as specified in ETS 300-233. Alternatively, the National bits may individually carry data links derived from the internal HDLC controllers, or may be passed transparently from the ED[x] input.

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# 4.2.4 TJAT – Digital Jitter Attenuation

ISSUE 2

The TJAT block provides the Digital Jitter Attenuation function in the transmit data path. This block is positioned between the egress interface and the transmit line data. TJAT block receives jittered data and stores the stream in a FIFO timed to the associated clock (CECLK). The jitter-attenuated data emerges from the FIFO timed to the jitter-attenuated clock. In the TJAT, the jitter-attenuated clock TLCLK[x] may be referenced to either CTCLK, CECLK, or RLCLK[1:8].

Jitter attenuator generates its output clock (TLCLK[1:8] by adaptively dividing the 49.152 MHz XCLK signal according to the phase difference between the jitter attenuated clock and the reference clock. Jitter fluctuations in the phase of the reference clock are attenuated by the phase-locked loop within TJAT so that the frequency of the jitter-attenuated clock is equal to the average frequency of the reference. Phase fluctuations with a jitter frequency above 8.8 Hz are attenuated by 6 dB per octave of jitter frequency. The jitter-attenuated clock tracks wandering phase fluctuations with frequencies below 8.8 Hz. The jitter attenuated clock (ICLK[x] for the RJAT and TLCLK[x] for the TJAT) is used to read data out of the FIFO.

If the FIFO read pointer comes within one bit of the write pointer, the TJAT will track the jitter of the input clock. This permits the phase jitter to pass through unattenuated, inhibiting the loss of data.

Jitter Characteristics. The TJAT Block provides excellent jitter tolerance and jitter attenuation while generating minimal residual jitter. It can accommodate up to 35 Ulpp of input jitter at jitter frequencies above 9 Hz. For jitter frequencies below 9 Hz, more correctly called wander, the tolerance increases 20 dB per decade. In most applications the TJAT Block will limit jitter tolerance at lower jitter frequencies only. For high frequency jitter, above 10 kHz for example, other factors such as clock and data recovery circuitry may limit jitter tolerance and must be considered. For low frequency wander, below 10 Hz for example, other factors such as slip buffer hysteresis may limit wander tolerance and must be considered. The TJAT blocks meet the low frequency jitter tolerance requirements ITU-T Recommendation G.823.

TJAT exhibits negligible jitter gain for jitter frequencies below 8.8 Hz, and attenuates jitter at frequencies above 8.8 Hz by 20 dB per decade. In most applications the TJAT Blocks will determine jitter attenuation for higher jitter frequencies only. Wander, below 10 Hz for example, will essentially be passed unattenuated through TJAT. Jitter, above 10 Hz for example, will be attenuated as specified, however, outgoing jitter may be dominated by the generated residual jitter in cases where incoming jitter is insignificant. This generated residual jitter is

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

directly related to the use of 24X (49.152 MHz) digital phase locked loop for transmit clock generation. TJAT meets the jitter transfer requirements of ITU-T Recommendations G.737, G.738, G.739, and G.742.

**Jitter Tolerance.** Jitter tolerance is the maximum input phase jitter at a given jitter frequency that a device can accept without exceeding its linear operating range, or corrupting data. For TJAT, the input jitter tolerance is 35 Unit Intervals peak-to-peak (Ulpp) with a worst case frequency offset of 308 Hz. It is 48 Ulpp with no frequency offset. The frequency offset is the difference between the frequency of XCLK divided by 24 and that of the input data clock.

#### 4.2.5 PRGD – Pattern Generator

The Pattern Generator/Detector (PRGD) block is a software programmable test pattern generator, receiver, and analyzer. Patterns may be generated in either transmit or receive directions, and detected in the opposite direction. Two types of ITU-T 0.151 compliant test patterns are provided: pseudo-random and repetitive.

The PRGD can be programmed to generate any pseudo-random pattern with length up to  $2^{32}$ -1 bits or any user programmable bit pattern from 1 to 32 bits in length. In addition, the PRGD can insert single bit errors or a bit error rates between  $10^{-1}$  to  $10^{-7}$ .

The PRGD can be programmed to check for the presence of the generated pseudo-random pattern.

The PRGD may also be programmed to check for repetitive sequences. When configured to detect a pattern of length N bits, the PRGD will load N bits from the detected stream, and determine whether the received pattern repeats itself every N subsequent bits. All the features (error counting, auto-synchronization, etc.) available for pseudo-random sequences are also available for repetitive sequences.

### 4.3 EOCTL Device – Receive Direction

The Receiver section of the EOCTL device in general receives an E1 data stream from a line interface device and outputs at the ingress interface into a backplane type of destination. On this reference design the data is input on the RLD[1:8] pin(s) from the QDSX device, processed by the EOCTL and then fed into the FREEDM device by the BRIF output ID[1:8].

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# 4.3.1 RJAT – Digital Jitter Attenuation

ISSUE 2

The very first block in receiver path is the Receive Digital Jitter Attenuator (RJAT). The function of this block is very similar to TJAT described in section *4.2.4* above. For more on RJAT refer to that section and to document [2].

### 4.3.2 FRMR - E1 Framer

De-jittered data from RJAT is fed to the E1 Framer (FRMR), which searches for frame alignment, CRC multiframe alignment, and Channel Associated Signaling (CAS) multiframe alignment in the incoming recovered PCM stream.

An elastic store ELST (part of the E1 Framer) synchronizes the ingress frames to the common ingress clock and frame pulse (CICLK and CIFP or MCICLK and MCIFP) in the Clock Slave ingress modes. The frame data is buffered in a two-frame circular data buffer. Input data is written to the buffer using a write pointer and output data is read from the buffer using a read pointer.

The elastic store can optionally be bypassed to eliminate the two-frame delay. In this configuration (the Clock Master ingress modes), the elastic store is used to synchronize the ingress frames to the transmit line clock (TLCLK[x]) so that perchannel loopbacks may be enabled. Per-channel loopbacks are only available when the elastic store is bypassed, or when CECLK and CICLK clocks and CEFP and CIFP frame pulses are tied together, and the CICLKRISE and CECLKFALL register bits are either both logic 1 or both logic 0. CICLKRISE and CECLKFALL are found in registers 3 and 4 of each octant, respectively. The elastic store cannot be bypassed if the Multiplexed bus is enabled.

When the elastic store is being used, if the average frequency of the incoming data is greater than the average frequency of the backplane clock, the write pointer will catch up to the read pointer and the buffer will be filled. Under this condition a controlled slip will occur when the read pointer crosses the next frame boundary. The subsequent ingress frame is deleted.

If the average frequency of the incoming data is less than the average frequency of the backplane clock, the read pointer will catch up to the write pointer and the buffer will be empty. Under this condition a controlled slip will occur when the read pointer crosses the next frame boundary. The previous ingress frame is repeated.

A slip operation is always performed on a frame boundary.

For payload conditioning, the ELST can be configured to insert a programmable idle code into all channels when the FRMR is out of frame alignment.

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

# 4.3.3 SIGX – Signal Extractor

The Signaling Extraction (SIGX) block provides signaling bit extraction from timeslot 16 of the ingress. When the external signaling interface is enabled, the SIGX serializes the bits into a serial stream (ISIG[x] or MISIG[x]) aligned to the synchronized outgoing data stream (ID[x] or MID[x]).

The SIGX also provides user control over signaling freezing and provides control over signaling bit fixing and signaling debounce on a per-channel basis. The block contains three multiframes worth of signal buffering to ensure that there is a greater than 95% probability that the signaling bits are frozen in the correct state for a 50% ones density out-of-frame condition. With signaling debounce enabled, the per-channel signaling state must be in the same state for 2 multiframes before appearing on the serial output stream. The SIGX indicates the occurrence of a change of signaling state for each channel via an interrupt and by a change of signaling state bit for each channel.

#### 4.3.4 RPSC – Per-Channel Controller

The RPSC allows data and signaling trunk conditioning to be applied to the receive E1 stream on a per-channel basis. It also allows per-channel control of data inversion, the extraction of clock and data on ICLK[x] and ID[x] (when the Clock Master: NxTS mode is active), and the detection or generation of pseudorandom or repetitive patterns. The RPSC operates on the data after its passage through ELST, so that data and signaling conditioning may overwrite the ELST trouble code.

# 4.3.5 BRIF – Backplane Ingress Interface

In general terms this interface transmits serial data, signal data, frame pulses and clock(s) to a system (a backplane) destination. The Reference Design uses only data and clock signals that are fed to the FREEDM-8 device. Output data is in E1 format with a gap at the DS0 time slot.

Functions and connections of each BRIF interface pins are as follows:

• Ingress Data ID[1:8] - presented to the system HDLC (packet) data. Default settings on the reference design sets the data gap at the DS0 time slot. Time slots DS1 through DS31 are clocked out. Each ID[x] signal contains the recovered payload data stream. ID[x] is aligned to the receive line timing and is updated on the active edge of the associated ICLK[x].

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

- Ingress Clock (ICLK[1:8]) clock output for the ID[1:8] data. The Ingress Clocks are active when the external signaling interface is disabled. Each ingress clock is a smoothed (jitter attenuated) version of the associated receive line clock (RLCLK[x]). The Clock Master: NxTS mode is active on this reference design. Default on the Evaluation Card sets clock gap at the DS0 time slot. ICLK[x] is a gapped version of the smoothed RLCLK[x]. ID[x] is updated on the active edge of ICLK[x].

- Common Ingress Clock (CICLK) / Multiplexed Common Ingress Clock (MCICLK) – this output is not used on this reference design. For more on clock modes refer to [2].

- Common Ingress Frame Pulse (CIFP) / Multiplexed Common Ingress

Frame Pulse (MCIFP) this output is not used on this reference design.

- Ingress Frame Pulse (IFP[1:8]) this output is not this reference design.

The ingress interface has two modes of operation: Non-Multiplexed Bus Ingress Mode and Multiplexed Bus Ingress Mode. The Non-Multiplexed mode is used on this Reference Design.

<u>The Non-Multiplexed Bus Ingress Modes</u>. In this mode the Ingress Interface allows ingress data to be presented to a system using one of four possible modes as selected by the ICLKSLV and ISIG\_EN bits in the Receive Backplane and Ingress Interface Options Registers.

For more on Ingress Bus modes refer to EOCTL Data Sheet [2].

# 4.4 Loopbacks

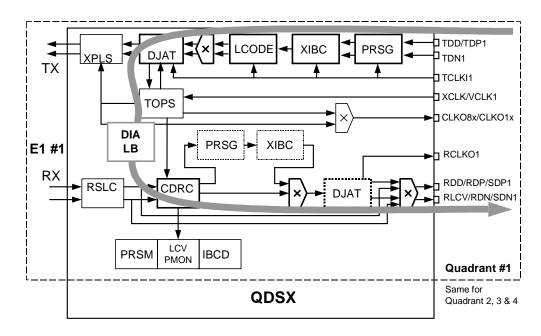

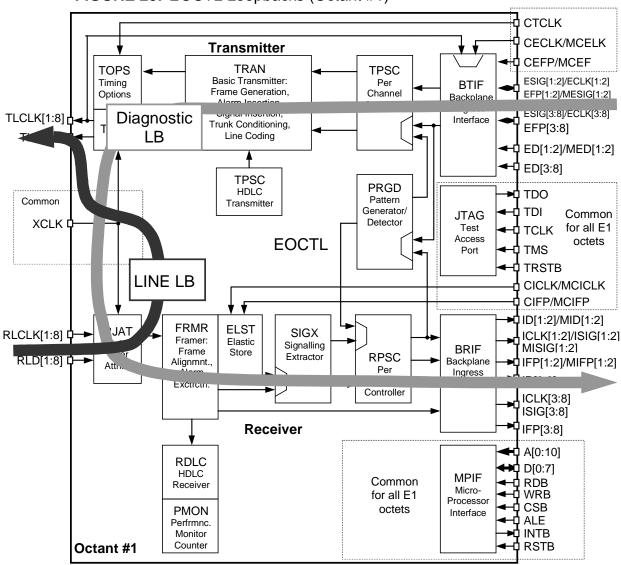

FIGURE 25. EOCTL Loopbacks (Octant #1)

ISSUE 2

The figure above shows the Diagnostic Loopback, which includes most of the EOCTL/TOCTL circuitry. Loopback is executed at the line interface side including TJAT and RJAT.

# 4.5 Microprocessor Interface on EOCTL

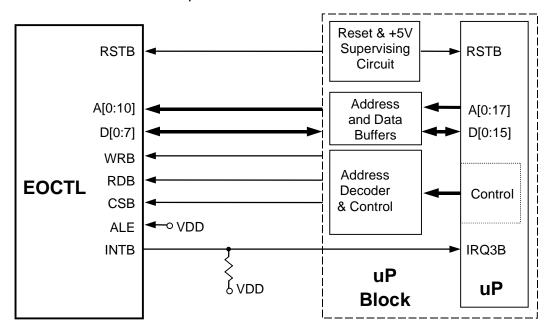

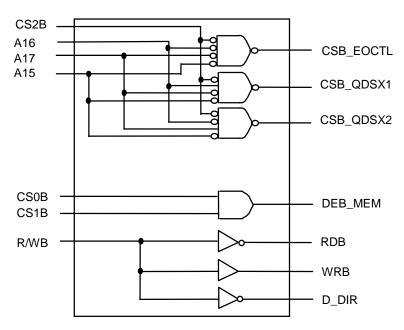

The EOCTL device provides a generic microprocessor interface. This is shown in FIGURE 26.

FIGURE 26. Microprocessor Interface on EOCTL

ISSUE 2

The Motorola 68340 microprocessor is used to monitor and control the EOCTL device. Address decoder and control lines are generated with PAL devices.

The interrupt signal INTB is an open-drain output that can be wire ORed with other devices. INTB needs a +5V pull-up resistor.

For more on microprocessor interface timing refer to EOCTL Data Sheet [2] and MC68340 Software [9].

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

### 5 TOCTL DEVICE DESCRIPTION

FIGURE 27. TOCTL Block Diagram (Octant #1)

NOTE: Octant #1 shown only. Blocks common to all octets are framed with dashed line. Power supply and ground pins not shown.

ISSUE 2

EOCTL/TOCTL WITH FREEDM-8 REFERENCE DESIGN

The noticeable differences between EOCTL and TOCTL devices (on the TOCTL block diagram above and EOCTL on FIGURE 24) are related mostly to framing procedures, which are different for each data interface. The external interface ports (pins) are exactly the same as for EOCTL and are not elaborated in this chapter.

The PM4388 Octal T1 Framer (TOCTL) is a feature-rich device for use primarily in systems carrying data (frame relay, Point to Point Protocol, or other protocols) over DS-1 facilities. Each of the framers and transmitters is independently software configurable, allowing feature selection without changes to external wiring.

On the receive side, each of eight independent framers can be configured to frame to either of the common DS-1 signal formats: (SF, ESF) or to be bypassed (unframed mode). The TOCTL detects and indicates the presence of Yellow and AIS patterns and also integrates Yellow, Red, and AIS alarms.