# PM6341 E1XC

# MEETING ETS 300 011 REQUIREMENTS WITH THE E1XC

# **CONTENTS**

| CONTENTS                                                                                                                     | I        |

|------------------------------------------------------------------------------------------------------------------------------|----------|

| LIST OF FIGURES                                                                                                              | 1        |

| LIST OF TABLES                                                                                                               | 2        |

| 1 REFERENCES                                                                                                                 | 3        |

| 2 DEFINITIONS AND TERM GLOSSARY                                                                                              | 4        |

| 3 BACKGROUND AND OVERVIEW                                                                                                    | 10       |

| 4 SOFTWARE RECOMMENDATIONS                                                                                                   | 11       |

| 4.1 Initialization                                                                                                           | 14<br>15 |

| 5 HARDWARE RECOMMENDATIONS                                                                                                   | 28       |

| 5.1 Timing Connections                                                                                                       | 29       |

| 6 TEST DETAILS                                                                                                               | 31       |

| 6.C.2 Electrical Characteristics 6.C.3 Functional Characteristics Tests 6.C.4 Interface Procedures Tests 6.C.5 Power Feeding | 47<br>48 |

| APPENDIX A RECOMMENDED FRAMING SOFTWARE                                                                                      | 52       |

| A.1 Implementation Assumptions                                                                                               | 54       |

| APPENDIX B SOFTWARE RESPONSE TO C.4.3 (TBR 004 B.5.2)                                                                        |          |

| APPENDIX C SOFTWARE RESPONSE TO C.4.4 (TBR 004 B.5.3)                                                                        | 86       |

| APPENDIX D SOFTWARE RESPONSE TO C.4.5 (TBR 004 B.4.2)                                                                        | 101      |

# APPLICATION NOTE

PMC-951128 ISSUE 3 E1 FRAMER/TRANSCEIVER

# **LIST OF FIGURES**

| igure 1. Event Decision Tree                                | 23 |

|-------------------------------------------------------------|----|

| igure 2 Recommended Timing Connections                      | 28 |

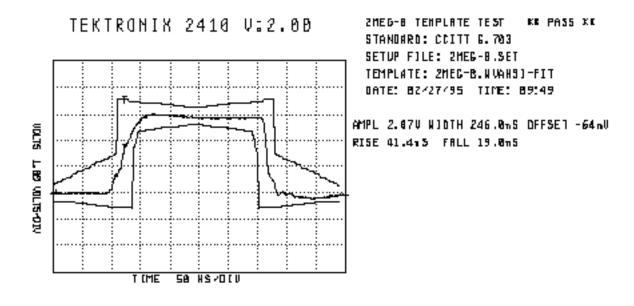

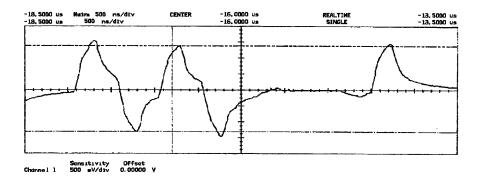

| igure 3 Typical Results of 120 $\Omega$ Positive Pulse Test | 32 |

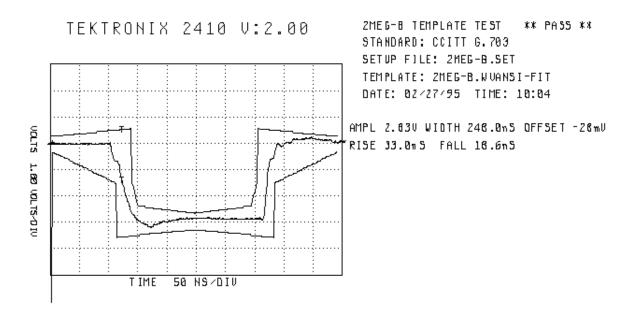

| igure 4 Typical Results of 120 $\Omega$ Negative Pulse Test | 33 |

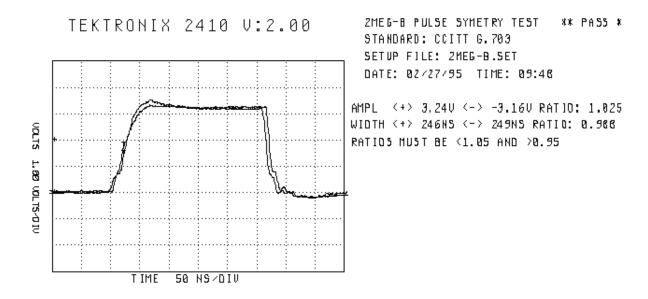

| igure 5 Typical Results of Pulse Symmetry Test              | 34 |

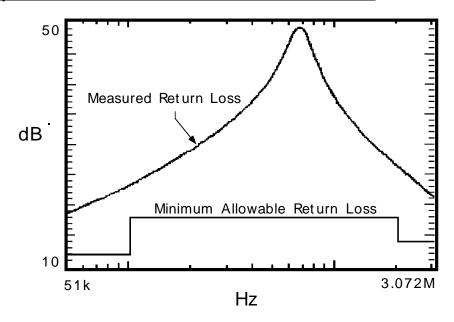

| igure 6 Typical Return Loss of E1XC Receive Line Interface  | 36 |

| igure 7 Typical C.2.4.2.b Test Signal                       | 37 |

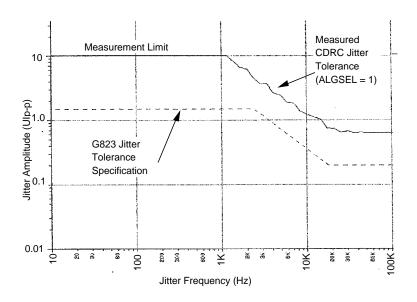

| igure 8 Typical Jitter Tolerance of E1XC                    | 41 |

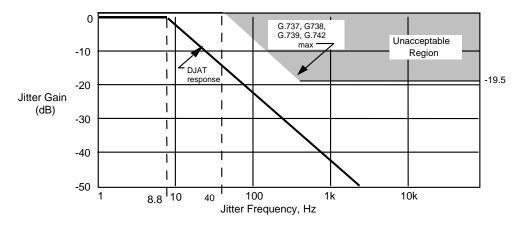

| igure 9 E1XC Jitter Transfer                                | 42 |

#### APPLICATION NOTE

PMC-951128 ISSUE 3 E1 FRAMER/TRANSCEIVER

# **LIST OF TABLES**

| Table 1. | Recommended Register Initialization            | 12 |

|----------|------------------------------------------------|----|

| Table 2. | States Matrix at User Side                     | 18 |

| Table 3. | States Matrix at Network Side                  | 19 |

| Table 4. | Transient States Matrix                        | 27 |

| Table 5  | Output Jitter with Jittered Input Timing       | 44 |

| Table 6. | Correspondence Between States Table and C Code | 71 |

#### 1 REFERENCES

- ETSI, ETS 300 011 (April 1992), "ISDN; Primary Rate User-Network Interface Layer 1 Specification and Test Principles"

- ETSI, ETS 300 011 Amendment 1 (December 1994), "ISDN; Primary Rate User-Network Interface Layer 1 Specification and Test Principles"

- ETSI, TBR 004 (November 1995); "ISDN; Attachment requirements for terminal equipment to connect to an ISDN using ISDN primary rate access"

- ITU-T Recommendation G.703, Study Group XVIII, Resolution No. 2 (April 1991), "Physical/Electrical Characteristics of Hierarchical Digital Interfaces"

- ITU-T Recommendation G.704, Study Group XVIII, Resolution No. 2 (April 1991), "Synchronous Frame Structures Used at Primary and Secondary Hierarchical Levels"

- ITU-T Recommendation G.706, Study Group XVIII, Resolution No. 2 (April 1991), "Frame Alignment and Cyclic Redundancy Check (CRC) Procedures Relating to Basic Frame Structures Defined in Recommendation G.704"

- ITU-T Recommendation I.431 (03/93), "Primary Rate User-Network Interface Layer 1 Specification"

- PMC-Sierra, Inc., "EQUAD With QDSX Reference Design", PMC-960911, Issue 1

# 2 DEFINITIONS AND TERM GLOSSARY

|           | TIONS AND TERM SECONARY                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AIS       | Alarm Indication Signal. This is a standardized (ITU-T G.704) signal consisting of an un-framed all-ones signal. It is transmitted when the data source for the transmit data is unavailable. The E1XC provides the ability to transmit and detect AIS.       |

| B-Channel | The B-Channel is the "building block" of the ISDN user channel. Different numbers of B-Channels are grouped with a D-Channel to produce H0, H11 and H12 ISDN channels.                                                                                        |

| BER       | Bit Error Ratio. This is the ratio of bits received in error to the total bits received.                                                                                                                                                                      |

| CAS       | Channel-Associated Signaling. This is a standardized (ITU-T G.704) use of TS16 of the E1 frame. CAS consists of sending a 16-frame signaling multiframe in TS16. CAS is not used for ISDN.                                                                    |

| CCS       | Common Channel Signaling. This is a standardized (ITU-T G.704) use of TS16 of the E1 frame. CCS consists of sending a HDLC formatted packets over TS16. CCS is the same as the D-Channel for ISDN primary rate applications.                                  |

| CDRC      | Clock and Data Recovery Unit. Used by PMC-Sierra to denote the functional block within the E1XC which contains the circuitry for recovering the timing from the received E1 signal to which the received data is re-timed. It is implemented with a DPLL.     |

| CMF       | CRC-4 Multiframe. This is a standardized (ITU-T G.704) use of the International Use Bits, Si, in Timeslot 0 of the E1 frame. The Si bits are used to provide a MFAS, a CRC-4 check calculated over the E1 payload, and a far end error indication via E-bits. |

| CRC       | Cyclic Redundancy Check. A type of parity check used to detect bit errors across a transmission link.                                                                                                                                                         |

| D-Channel | The D-Channel is the ISDN datalink channel associated with some number of ISDN user channels. The D-Channel carries LAPD formatted messages. It is carried in TS16 of the E1 frame for ISDN primary rate applications.                                        |

| DPLL      | Digital Phase-Locked Loop. This term is used for phase-locked loops                                                                                                                                                                                           |

which make phase corrections in discrete (quantized) corrections.

| PMC-951128 | ISSUE 3                                                                                                                                                                                         | E1 FRAMER/TRANSCEIVER                                                |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| DJAT       | Digital Jitter Attenuator. This term is u functional block within the E1XC which the phase jitter on the transmit timing rDPLL.                                                                 | contains the circuitry to attenuate                                  |

| E1         | European First Order transmission form<br>T G.704) base format of the European<br>Hierarchy. It operates at 2048 kbit/s.                                                                        | `                                                                    |

|            | The E1 format consists of frames cons<br>(numbered 0 to 31). Timeslot 0 alterna<br>and containing the National Use bits (S<br>Timeslot 0s contain an International Use<br>provide a CMF format. | ates between containing an FAS<br>Sn[8:4]) and an A-bit for RAI. All |

| E1XC       | E1 Framer with Line interface unit. Th Sierra gives to its PM6341 device.                                                                                                                       | is is the mnemonic label PMC-                                        |

| ETSI       | European Telecommunication Standar<br>body that has the primary objective of<br>European telecommunications connec                                                                              | end-to-end compatibility for pan-                                    |

| F0         | State zero in the I.431 states table for is "Loss of Power on User Side". In the transmit nor receive signals.                                                                                  |                                                                      |

| F1         | State one in the I.431 states table for t is the "Operational State". In this state service is available, CRC multiframing                                                                      | e, network timing and Layer 1                                        |

| F2         | State two in the I.431 states table for the state is the "Fault Condition No. 1". This state received. The differences between the I.604 option used in the network.                            | ate is the same as F1 except RAI is                                  |

| F3         | State three in the I.431 states table for state is the "Fault Condition No. 2". In available, the user side detects loss of frame alignment), and the user side tra                             | this state, network timing is not signal (and corresponding loss of  |

| F4         | State four in the I.431 states table for the state is the "Fault Condition No. 3". In this state available, the user side detects AIS (and alignment), and the user side transmits              | state, network timing is not<br>nd corresponding loss of frame       |

| PMC-951128 | ISSUE 3                                                                                                                        | E1 FRAMER/TRANSCEIVER                                                                                                                                                                                                         |

|------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F5         | is the "Fault Condition No. 4".                                                                                                | able for the user side of the UNI. This state This state is the same as F1 except RAI is ween this state and State F2 depend on the ork.                                                                                      |

| F6         | is the "Power On State". This                                                                                                  | ble for the user side of the UNI. This state is the only transient state for the user side e may change to another state after                                                                                                |

| FAS        | •                                                                                                                              | s term is used both for the frame alignment n) and for E1 frames that contain the frame.                                                                                                                                      |

| FEBE       | structure. Two E-Bits are pro                                                                                                  | is term refers to the E-Bits in the CMF vided, one for each sub-multiframe. They put signal when the input signal contains a                                                                                                  |

| FIFO       | First In, First Out. This term rethe data serially in the same of                                                              | efers to a kind of digital buffer which outputs order in which it was input.                                                                                                                                                  |

| FRMR       | E1XC which contains the fran                                                                                                   | to denote the functional block within the ning circuitry required to find and maintain he received E1 signal. It also contains AI and AIS.                                                                                    |

| FTP        | procedures used by the PMC-<br>the functionality of a PMC-Sie<br>performed on an evaluation P<br>industry standard test equipm | used by PMC-Sierra to describe the Sierra Product Verification group to verify rra product. Generally, the FTP is CB designed for that purpose, using ent. By PMC-Sierra's ISO-9001 passed successfully before releasing a e. |

| G0         |                                                                                                                                | table for the network side of the UNI. This NT1". In this state, the NT1 can neither                                                                                                                                          |

| G1         | state is the "Operational State                                                                                                | able for the network side of the UNI. This ". In this state, network timing and Layer 1 iframing is transmitted and received.                                                                                                 |

| PMC-951128     | ISSUE3                           | E1 FRAMER/TRANSCEIVER                                                                                                                  |

|----------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| G2             | state is the "Fault Condition No | ole for the network side of the UNI. This of 1". This state is the same as G1 except es between this state and State G5 dependentwork. |

| G3             | state is the "Fault Condition No | able for the network side of the UNI. This b. 2". In this state, network timing is not the network side transmits NOFs.                |

| G4             | state is the "Fault Condition No | ble for the network side of the UNI. This a. 3". In this state, network timing is not etwork side transmits AIS, and the ut with RAI.  |

| <b>G</b> 5     |                                  | ole for the network side of the UNI. This o. 4". The network side detects LOS or asmits NOF with RAI.                                  |

| G6             | state is the "Power On State".   | le for the network side of the UNI. This This is the only transient state for the The network side may change to another ed signal.    |

| H0             |                                  | r channel consisting of six B-Channels. A cannel for ISDN 2048 kbit/s primary rate                                                     |

| H11            |                                  | er channel consisting of 23 B-Channels. with a single D-Channel for ISDN 1544                                                          |

| H12            |                                  | er channel consisting of 30 B-Channels. with a single D-Channel for ISDN 2048                                                          |

| HDB3           | , ,                              | of order 3. This is a standardized (ITU-T ed for zero suppression, while maintaining sed for E1 transmission.                          |

| HDLC           | •                                | This protocol is commonly specified for ubset of HDLC, LAPD, is used over the                                                          |

| l <sub>a</sub> | Interface A. This refers to the  | user side of the UNI.                                                                                                                  |

| PMC-951128     | ISSUE 3                                                                                                                                              |                                                                                      | E1 FRAMER/TRANSCEIVER                                     |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------|

| I <sub>b</sub> | Interface B. This refers to th                                                                                                                       | e network side of the UNI                                                            |                                                           |

| IPATS          | This is a test system from He test for ETS 300 011 complia                                                                                           |                                                                                      | any test houses to                                        |

| ISDN           | Integrated Services Digital N telecommunications network and paths supporting a broad                                                                | that implemented as a se                                                             | •                                                         |

| ISO            | International Organization fo voluntary, non-treaty organiz standards bodies from partic                                                             | ation whose members are                                                              |                                                           |

| ITU-T          | International Telecommunical within a United Nations treatissue recommendations on the relating to telegraphy and telecompatibility of international | ty organization. The char<br>echnical, operating, and t<br>ephony." Its primary obje | ter is "to study and ariff questions ective is end-to-end |

| IUT            | Implementation Under Test. test stimulus is being applied responses.                                                                                 |                                                                                      |                                                           |

| LAPD           | Link Access Procedure for D based on HDLC. It is used for channels.                                                                                  |                                                                                      | 0 0.                                                      |

| Layer 1        | Layer 1 of the ISDN protocol Physical Layer. It is standar                                                                                           |                                                                                      |                                                           |

| LOS            | Loss of Signal. This is the si<br>it is impossible to recover the<br>number of consecutive zeros                                                     | e line timing. For E1, LOS                                                           | ,                                                         |

| MFAS           | Multiframe Alignment Signal.<br>International Use Bits of six of<br>CMF format.                                                                      |                                                                                      | ,                                                         |

| NFAS           | No Frame Alignment Signal. contain the frame alignment National Use Bits and the RA                                                                  | signal in TS0. Instead TS                                                            |                                                           |

| NOF            | Normal Operating Frames. and MFAS are correct, the lippresent (the A-bit in TS0 of t                                                                 | ne coding (HDB3) is corre                                                            | ect, and no RAI is                                        |

| PMC-951128 | ISSUE 3                                                          | E1 FRAMER/TRANSCEIVER                                                                                                                                          |

|------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NT         | Network Termination. Equipment network connection.               | ent on user premises which terminates the                                                                                                                      |

| OOCMF      | <u> </u>                                                         | the state an E1 framer is in if it cannot ational Use bits of TS0. An E1 framer is                                                                             |

| OOF        | Out-Of-Frame alignment. This find the FAS within the received    | is the state an E1 framer is in if it cannot discriptions serial 2048 kbit/s data.                                                                             |

| PMON       | functional block within the E1X accumulate performance statis    | m is used by PMC-Sierra to denote the C which contains counters which tics such as framing bit errors, FEBEs, plations. The accumulation interval is rocessor. |

| RAI        |                                                                  | A-bit in TS0 of NFAS frames is used to that a receiver alarm condition (such as                                                                                |

| RED        | OOF conditions. The E1XC au                                      | ate which is entered due to a persistent tomatically integrates OOF and signals a ED bits in Registers 25H and 27H                                             |

| Т3         | this document. It is used to imp                                 | in the transient states matrix defined in plement the recommendations in G.706 puts in the search for MFAS alignment.                                          |

| TE         | Terminal Equipment. Subscrib premises.                           | er interface equipment on the user                                                                                                                             |

| TS0        | alternates between the FAS an                                    | first timeslot (octet) in the E1 frame. TS0 d NFAS frames. The International Use NFAS frames may carry the MFAS. The e A-Bit used for RAI.                     |

| TS16       |                                                                  | e seventeenth timeslot (octet) in the E1 erally for either CAS or CCS. For ISDN, ed the D-Channel.                                                             |

| UI         | Unit Interval. This is a unit use time deviation of phase normal | d to measure phase jitter. The unit is the zed to the bit period.                                                                                              |

| UNI        | User-Network Interface.                                          |                                                                                                                                                                |

#### 3 BACKGROUND AND OVERVIEW

PMC-Sierra's PM6341 E1XC E1 Framer is a full-featured device which is fully compatible with European Primary Rate ISDN requirements. In relation to the ISDN protocol stack, the E1 transceiver functionality is part of Layer 1. The primary source of European ISDN specifications is ETSI. For Layer 1, the primary ETSI specifications are ETS 300 011 and TBR 004.

ETS 300 011 and TBR 004 are based on the ITU-T suite of requirements for interfaces operating at 2048 kbit/s. However, ETSI expands on the ITU-T standards by specifying the test principles. Annex C of ETS 300 011 is devoted to "Conformance test principles for the user and the network side of the interface."

The PM6341 E1XC has a parallel microprocessor port which provides access to the E1XC'S internal register set. Via these registers, all relevant Layer 1 status conditions can be monitored, and all maintenance responses can be controlled such that the E1 interface complies with ETS 300 011. However, it is left to the software to appropriately control the E1XC's responses to various status conditions.

This document makes general recommendations for software and hardware development, then describes each test in ETS 300 011 Annex C. It explains how following PMC-Sierra's recommendations for designing with the PM6341 E1XC will allow the implementation to meet the ETS 300 011 requirements.

Note: It is assumed that the reader is familiar with the documents cited in the References section. They should be read in conjunction with this document.

#### 4 SOFTWARE RECOMMENDATIONS

The E1XC has a full-featured register set which provides access to all the status monitoring and control functions necessary to pass the ETS 300 011 tests. However, it is up to the software to use the E1XC registers properly. This section details the considerations that must be taken while developing software for an E1XC design.

The software has four main functions:

- initializing,

- performance monitoring,

- implementing of the I.431 states matrix for static states,

- handling transient states.

This section explains how the software development should be approached for each of these four functions.

Interrupt-driven routines are recommended because they are much more efficient than polling routines when responding to low frequency events such as Layer 1 defects. In general, changes in Layer 1 status can be enabled to generate an interrupt indication on the E1XC'S INTB output pin.

#### 4.1 Initialization

After E1XC power up, a software reset should be performed on the E1XC to put it in a default state. The software reset is performed by setting the RESET bit (register 0DH) then clearing it. The recommended initial configuration is given in Table 1. Registers which are not included in Table 1 should be left in their default state. Also, bits which are not included in Table 1 should be left in their default state.

Table 1. Recommended Register Initialization

| Register<br>Address<br>(hex) |            | Recommended Configuration                                                                                                                                                                                                        |

|------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00                           | TRKEN=1    | This allows E1XC to automatically propagate an AIS to the receive backplane while in OOF condition.                                                                                                                              |

| 02                           | TXSA4=1    | Default value.                                                                                                                                                                                                                   |

| 07                           | PLLREF1=1  | This chooses the possible transmit timing reference to be either RCLKO or TCLKI                                                                                                                                                  |

|                              | RLLREF0=X  | This bis should be set according to the desired transmit timing mode. (See the Timing Connections section)                                                                                                                       |

| 09                           | RXSA4EN=0  | This allows TS16 to be extracted for D-Channel processing.                                                                                                                                                                       |

| 19                           | N1[7:0]=FF | The value in this register must be the same as in Register 1AH when the transmit timing reference is at the line rate.                                                                                                           |

| 1A                           | N2[7:0]=FF | This sets the DJAT transfer function for maximum jitter attenuation.                                                                                                                                                             |

| 1B                           | CENT=1     | This allows the DJAT FIFO to center itself thereby providing maximum room to absorb phase differences between the input and output transmit clocks.                                                                              |

|                              | SYNC=0     | This bit should be cleared whenever Register 1AH does not contain its default value (2FH).                                                                                                                                       |

|                              | LIMIT=0    | This function should be disabled so that the DJAT FIFO does not disrupt the DJAT PLL operation. With the hardware connections recommended in this document, the FIFO should never reach a condition where LIMIT would be useful. |

| 20                           | CRCEN=1    | This enables the MFAS alignment circuitry in the FRMR.                                                                                                                                                                           |

|                              | CASDIS=1   | This disables the CAS multiframe alignment circuitry in the FRMR.                                                                                                                                                                |

|                              | REFCRCE=1  | This enables the CRC error monitor to force a reframe if an excessive CRC error condition is detected.                                                                                                                           |

| 21                           | BIT2C=1    | This enables the E1XC to declare OOF if Bit 2 of TS0 of NFAS frames is received incorrectly for three consecutive frames.                                                                                                        |

| Register<br>Address<br>(hex) |          | Recommended Configuration                                                                                                                                                         |

|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22                           | OOFE=1   | This enables changes in the status of the FAS alignment circuit to generate interrupt indications on the E1XC'S INTB output pin.                                                  |

|                              | OOCMFE=1 | This enables changes in the status of the MFAS alignment circuit to generate interrupt indications on the E1XC'S INTB output pin.                                                 |

| 23                           | RRAE=1   | This enables changes in the status of the RAI detection circuit to generate interrupt indications on the E1XC'S INTB output pin.                                                  |

|                              | REDE=1   | This enables changes in the status of the RED detection circuit to generate interrupt indications on the E1XC'S INTB output pin.                                                  |

|                              | AISE=1   | This enables changes in the status of the AIS circuit to generate interrupt indications on the E1XC'S INTB output pin.                                                            |

| 30                           | IND=1    | This enables indirect accessing of the Transmit Per-<br>Channel Serial Controller (TPSC) registers within the<br>E1XC.                                                            |

|                              |          | The indirect registers within the TPSC should be initialized as explained below.                                                                                                  |

| 44                           | SIGEN=0  | This disables the transmission of Channel-Associated Signaling in TS16.                                                                                                           |

|                              | DLEN=0   | This disables the transmission of Channel-Associated Signaling in TS16.                                                                                                           |

|                              | GENCRC=1 | This enables the generation of the CRC multiframe.                                                                                                                                |

| 5C                           | THS=1    | This sets the 'slicing' threshold of the receive pulse slicer (RSLC) in the E1XC to 50%. This setting ensures maximum immunity to interference and reflections at the input port. |

Idle timeslots within the E1 frame must contain at least three binary ones. To implement insertion of compliant Idle codes, the Transmit Per-Channel Serial Controller (TPSC) in the E1XC must be properly initialized.

The TPSC contains a number of indirect registers which are used to control the transmitted timeslots on a per-channel basis. Accessing these registers is described in the section of the E1XC data book entitled "Using the Per-Channel Serial Controllers".

The indirect registers in the TPSC should be initialized so that each timeslot's IDLE code byte contains a value with at least three binary ONEs. Additionally, each timeslot's Data Control byte should be programmed so that the DS[1:0] bits are both cleared to logic zero, and the SUBS bit is set according to whether that timeslot is idle or not. Refer to the E1XC data book for further information on the use of these bits.

Once the TPSC is initialized, the PCCE bit in Register 30H should be set to logic one, enabling the per-channel functions as programmed in the TPSC indirect registers.

The variables and timers for implementing the I.431 states matrix and the transient states matrix (see section 4.4.4) should all be reset. Note that the most robust implementation would be to initialize the variables with a "best guess" of the current state.

#### 4.2 Performance Monitoring

In I.431, performance monitoring of the 2048 kbit/s primary rate interface is optional.

The PMON functional block of the E1XC provides counters for accumulating performance monitoring statistics, with the accumulation interval under microprocessor control. Refer to the description of Registers 49H to 4FH in the E1XC data book for an explanation of the operation of these registers.

The PMON counters are large enough such that the probability of saturating them during a one second interval is less than 0.001% under a BER of 1:10<sup>3</sup>. The values in these counters can be used to extrapolate the actual BER (see the section entitled "Using the Performance Monitor Counter Values" in the E1XC data book).

Whether or not the performance monitoring statistics are collected by the system, the FEBE count must be monitored to detect the I.431 F5 state. The F5 state is distinguished from the F2 state by the continuous reception of FEBEs.

Continuous reception of FEBEs corresponds to FEBEs received at a rate of 1000 per second. Therefore, the PMON FEBE counter (Registers 4AH and 4BH) must be polled to check the rate of FEBE reception.

I.431 says that the reception of continuous FEBEs should cause transitions within the states matrix. It is suggested that the PMON FEBE counters be polled every 10 ms and the value returned compared with a threshold to determine if continuous FEBEs have been received over the last 10 ms interval.

Therefore, if 10 FEBEs are received in 10 ms, continuous FEBEs are being received. However, the tolerance of the timer as well as robustness against bit errors should also be taken into account. Therefore, the threshold corresponding to continuous FEBEs received is given by:

threshold =

$$FEBE_rate_{max} \times T \times \left(1 - BER_{max} - \frac{tolerance}{10^6}\right)$$

(1)

where *threshold* is the minimum number of FEBEs which corresponds to continuous FEBEs being received during the polling interval, *FEBE\_rate<sub>max</sub>* is the maximum rate that FEBEs can be indicated (two per multiframe), *T* is the polling time interval, *BER<sub>max</sub>* is the maximum BER under which continuous received FEBEs is to be detected, and *tolerance* is the sum of the tolerances of the polling timer and the incoming line rate (in ppm).

Note: threshold should be rounded down to the nearest integer.

For example, using the recommended values of T=10ms and  $BER_{max}=10^{-3}$ , and assuming *tolerance*=1000ppm, the *threshold* value would be:

threshold =

$$1000$$

bps× $0.010$ s× $\left(1-10^{-3} - \frac{1000$ ppm}{ $10^{6}$ }\right)

=  $9.98 \approx 9$

Note: The time it takes for a microprocessor to service the timer interrupts will be variable. This variability should be included in the *tolerance* term.

#### 4.3 Implementing the I.431 States Matrix

ITU-T I.431 defines a states matrix for each side of the ISDN primary rate UNI. The purpose of those matrices is to standardize the way in which each side of the interface informs the other of the Layer 1 status related to the different defects which may be present.

States F0 to F6 (defined in the Glossary and Term Definitions section) are states at the user side, while states G0 to G6 (also defined in the Glossary and Term Definitions section) are the states at the network side of the UNI.

Corresponding to each state, each side of the interface must exchange information on the Layer 1 status, as well as passing primitives between Layer 1 and Layer 2, and between Layer 1 and the management entity.

The microprocessor monitoring and controlling the PM6341 E1XC, must be able to correctly implement the I.431 states matrix. Typically, this requires detecting a change in Layer 1 status and responding appropriately. The response usually requires a steady-state signal transmitted toward the interface as well as the passing of primitives to the Layer 2 and management entities.

Since the frequency of the state transitions is generally low, it is best to handle them using interrupt-driven routines. In the E1XC, many different conditions can be enabled to generate interrupt indications on the INTB output.

In order to implement the states matrix, it is sufficient to enable the interrupts due to RAI detection, RED alarm assertion, and AIS detection. The detection circuits for all three of these defects are contained in the FRMR functional block of the E1XC. To enable these interrupts, the following bits should be set to logic one (as specified in the Initialization section):

- RRAE bit in Register 23H

- REDE in Register 23H

- AISE in Register 23H

When an interrupt is indicated on the INTB output of the E1XC, the microprocessor should first read Register 08H. Register 08H indicates which functional blocks within the E1XC are asserting the INTB signal. If the FRMR bit is set to logic one, then one of the above interrupts may have occurred (note that other FRMR interrupt sources will likely be enabled for purposes other than the states matrix — see section entitled "Transient States").

Once it is determined that a FRMR interrupt has occurred, the microprocessor should read Register 25H. For each interrupt source, there is a corresponding interrupt indication bit whose mnemonic label ends with an "I". These bits are set when the corresponding status bit changes state. Therefore, in Register 25H, the RRAI, REDI, and AISI bits should be examined.

Note: The interrupt indication bits are cleared upon read. This also clears the assertion of the INTB signal (unless other interrupts are pending). Therefore, it is important to save the value of the interrupt indication bits until they are fully processed.

If any of these bits is logic one, then the corresponding state has changed since the last time that register was read, generating the interrupt. If one or more of the RRAI, REDI, and AISI bits are set to logic one, then the microprocessor should read Register 27H. In that register, the RRA, RED, and AIS bits should be examined to determine the current state of the FRMR. Depending on these values, the appropriate state transition should be performed, as explained below.

ITU-T I.431 defines the states matrices for the user and network side of the UNI. It contains two tables which show how new events should move the equipment through the state matrix, including what signal to transmit towards the interface and what primitives to pass to the Layer 2 and management entities.

#### **APPLICATION NOTE**

PMC-951128 ISSUE 3 E1 FRAMER/TRANSCEIVER

The difficulty with implementing the matrices in I.431 is that they do not explicitly explain which events are mutually exclusive, and which events take precedence over others. For example, when AIS is received a framer will declare RED Alarm; however, AIS and RED Alarm are considered different events which move the equipment into different states. Therefore, a decision has to be made as to the precedence of these events.

In the following two tables, Tables 2 and 3, the I.431 states matrices are re-written for actual interrupt events within the E1XC. These tables looks different than those in I.431 because interrupt events in the E1XC do not have a one-to-one correspondence with the events defined in I.431.

In Tables 2 and 3, the following acronyms and symbols are used:

| /          | Impossible event.                                                                                                                                                                                                       |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _          | No response required.                                                                                                                                                                                                   |

| AIS        | There are two bits in the E1XC with this name: Bit 2 in Register 27H, and Bit 0 in Register 45H. Respectively, these bits indicate the current status of the AIS detection circuit and control the transmission of AIS. |

| AISI       | Bit 2 in Register 25H of the E1XC. This bit indicates that a change of status of the AIS detection circuit has caused an interrupt.                                                                                     |

| FEBE       | This variable contains the number of FEBEs received over the last performance monitoring polling interval. This value is read from the PMON FEBE counter (Registers 4AH and 4BH) in the E1XC.                           |

| F <i>z</i> | Go to State Fz.                                                                                                                                                                                                         |

| G <i>z</i> | Go to State Gz.                                                                                                                                                                                                         |

| MPH-y      | Issue management primitive <i>y</i> as defined in I.431.                                                                                                                                                                |

| RCLKO      | The clock recovered from the received signal. It is available on the E1XC's RCLKO output pin as well as internally as the transmit timing reference. For more information, refer to the Timing Connections section.     |

| RED        | Bit 3 in Register 27H of the E1XC. This bit indicates the current state of the RED alarm integration circuit. RED Alarm is an integrated version of OOF.                                                                |

| REDI       | Bit 3 in Register 25H of the E1XC. This bit indicates that a change of status of the RED alarm integration circuit has caused an interrupt.                                                                             |

| REMAIS     | Bit 3 in Register 45H of the E1XC. This bit controls the transmission of the RAI in outgoing signal.                                                                                                                    |

| PH-x       | Issue primitive x as defined in I.431.                                                                                                                                                                                  |

E1 FRAMER/TRANSCEIVER

PMC-951128

ISSUE 3

| RRAI  | Bit 7 in Register 25H of the E1XC. This bit indicates that a change of status of the RAI detection circuit has caused an interrupt. |

|-------|-------------------------------------------------------------------------------------------------------------------------------------|

| RRA   | Bit 7 in Register 27H of the E1XC. This bit indicates the current status of the RAI detection circuit.                              |

| TCLKI | An independent timing signal applied to the TCLKI input of the E1XC. For more                                                       |

information, refer to the Timing Connections section.

Table 2. States Matrix at User Side

| Initial State                 |                                       |       | F1                     | F2                    | F3                    | F4                    | F5                    |

|-------------------------------|---------------------------------------|-------|------------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Remote Alarm<br>Transmission  |                                       |       | REMAIS=0               | REMAIS=0              | REMAIS=1              | REMAIS=1              | REMAIS=0              |

| Transmit                      | Transmit Timing Reference             |       | RCLKO                  | RCLKO                 | TCLKI                 | RCLKO                 | RCLKO                 |

|                               | RRAI=1                                | RRA=0 | /                      | PH-AI<br>MPH-AI<br>F1 | /                     | /                     | PH-AI<br>MPH-AI<br>F1 |

|                               |                                       | RRA=1 | PH-DI<br>MPH-E11<br>F2 | /                     | /                     | /                     | /                     |

|                               | REDI=1                                | RED=0 | /                      | /                     | PH-AI<br>MPH-AI<br>F1 | PH-AI<br>MPH-AI<br>F1 | /                     |

| New<br>Event                  |                                       | RED=1 | PH-DI<br>MPH-E12<br>F3 | MPH-E12<br>F3         | /                     | _                     | MPH-E12<br>F3         |

|                               | AISI=1                                | AIS=0 | _                      | /                     | _                     | MPH-E12<br>F3         | /                     |

|                               |                                       | AIS=1 | PH-DI<br>MPH-E13<br>F4 | MPH-E13<br>F4         | MPH-E13<br>F4         | /                     | MPH-E13<br>F4         |

|                               | FEBE <threshold<sup>1</threshold<sup> |       | _                      | _                     | _                     | _                     | MPH-E11<br>F2         |

| FEBE>= threshold <sup>1</sup> |                                       | _     | MPH-E14<br>F5          | _                     | _                     | _                     |                       |

The threshold for continuous FEBE detection is calculated using Equation (1) in the Performance Monitoring section.

Table 2 does not contain information on States F0 and F6 since the events related to these states (loss and return of power) cannot be detected within the E1XC. These events must be detected externally as part of the power supply design.

**Table 3. States Matrix at Network Side**

| Initial State             |        |       | G1                     | G3                    | G5                    |

|---------------------------|--------|-------|------------------------|-----------------------|-----------------------|

| Transmitter Configuration |        |       | REMAIS=0<br>AIS=0      | REMAIS=0<br>AIS=0     | REMAIS=1<br>AIS=0     |

| RRAI=                     |        | RRA=0 | /                      | PH-AI<br>MPH-AI<br>G1 | /                     |

| New<br>Event              |        | RRA=1 | PH-DI<br>MPH-E12<br>G3 | /                     | /                     |

|                           | REDI=1 | RED=0 | /                      | /                     | PH-AI<br>MPH-AI<br>G1 |

|                           |        | RED=1 | PH-DI<br>MPH-E14<br>G5 | MPH-E14<br>G5         | /                     |

Table 3 does not contain information on States G0, G2, G4 and G6 since the events related to these states (loss of power, FC1, FC3, and power on) cannot be detected within the E1XC.

#### 4.4 Transient States

In addition to the static states defined in the I.431 states matrices, there are transient states which must be handled by the E1XC.

Some important transient states which must be handled properly are those related to framing. This section explains how the microprocessor should use the status and control bits within the E1XC to properly handle transient states related to framing procedures.

Tests C.4.3 (Frame Alignment), C.4.4 (CRC Multiframe Alignment) and C.4.5 (CRC Processing) in ETS 300 011 stress the IUT's response to transient framing conditions. Because the stimulus for C.4.4 was poorly specified in the 1992 issue of the specification, Amendment 1 (A1) to ETS 300 011 was issued (in 1994) containing a new C.4.4 stimulus which supersedes the previous specification. Equipment based on the E1XC should be tested to Amendment 1 for C.4.4.

The E1XC can interrupt the microprocessor in response to transient states via its INTB output. It is recommended that interrupts be used for all the maintenance functions since these events usually have a low frequency of occurrence, but require a quick response.

#### 4.4.1 Frame Alignment

The ETS 300 011 C.4.3 test stresses the terminal equipment's ability to properly assert RAI in response to loss of FAS alignment.

The correct response is described in ITU-T G.706 Section 4.1. This standard specifies several options. However, inspection of the expected response in ETS 300 011 C.4.3 implies that:

- Frame alignment is considered found if the FAS is found followed in the next frame with Bit 2 set to logic one, followed by a FAS in the next frame.

- Frame alignment is considered lost if three consecutive incorrect FASs have been received. Additionally, frame alignment is considered lost if Bit 2 in TS0 in NFAS frames has been received in error on three consecutive occasions.

The E1XC provides configuration bits to support all the framing options given in G.706. If the registers are programmed as indicated in the Initialization section, the E1XC will conform with the ETS 300 011 expectations.

The E1XC provides the OOF bit in Register 26H to indicate the state of its FAS alignment circuit. Additionally, changes of state of the OOF bit are indicated in the OOFI bit in Register 24H. The OOFI bit can be enabled to indicate interrupts on the INTB signal by setting the OOFE bit in Register 22H to logic one.

Generally, the equipment should send an RAI in response to loss of FAS alignment. This is accomplished by setting the REMAIS bit to logic one when the E1XC interrupts indicating OOFI=1 and OOF=1. The REMAIS bit should be cleared to logic zero when the E1XC interrupts indicating OOFI=1 and OOF=0.

However, as explained in the next subsection, the E1XC can be forced out of FAS alignment by the circuit searching for MFAS alignment. Therefore, the OOFI interrupt should be handled as part of a more comprehensive FRMR interrupt-handling routine. A transient states matrix to handle this is detailed in Section 4.4.4. An explanation of how that matrix responds to the C.4.3 test stimulus is given in Appendix B.

### 4.4.2 CRC Multiframe Alignment

The ETS 300 011 (A1) C.4.4 test stresses the terminal equipment's ability to properly assert RAI in response to a loss of MFAS alignment.

The correct response is described in ITU-T G.706 Section 4.2 which specifies three main requirements concerning responses to MFAS alignment status:

- MFAS alignment is considered found if at least two valid MFASs are located within 8 ms (64 basic frames), with the time separating the two MFASs being 2 ms or a multiple of 2 ms.

- If MFAS alignment cannot be achieved in 8 ms, a re-search for FAS alignment should be initiated.

- If MFAS alignment cannot be achieved within a time limit in the range of 100 ms to 500 ms, consequent actions should be taken equivalent to those specified for loss of frame alignment.

It is important to understand the intent of this specification. If the terminal equipment is configured to expect a CRC-4 multiframe formatted signal, then it searches for MFAS alignment after finding FAS alignment. If it cannot find the MFAS alignment in a reasonable time, then the equipment should "assume" that it has framed to a mimic basic FAS. It therefore forces a re-search for the FAS alignment. After doing this a number of times without ever finding MFAS alignment, then the equipment makes another "assumption" — it assumes that the far end equipment is not sending a CMF formatted signal and gives up disrupting the FAS alignment. However, if the equipment does find MFAS alignment at least once before giving up then it assumes that the far end is sending a CMF-formatted signal but there is another problem (e.g. high BER).

The ETS 300 011 (A1) C.4.4 test expects RAIs to be transmitted to indicate the conformance to the specification. An RAI may be sent every time a reframe is forced by the MFAS alignment circuitry. Additionally, if the equipment decides that the far end is not sending a CMF-formatted signal, it should continuously assert RAI. If the equipment decides that the far end is sending a CMF-formatted signal but that another problem is present, then it stops asserting RAI.

The E1XC provides a number of register bits to indicate the state of the FRMR functional block:

- the OOF and OOCMF bits in Register 26H. These bits indicate the current status

of the basic and CMF frame find circuits.

- the OOFI and OOCMFI bits in Register 24H. These bits indicate that a change of state has occurred in the OOF and OOCMF bits, respectively, at least once since the last time Register 24H was read.

- the OOFE and OOCMFE bits in Register 22H. These bits enable the OOFI and OOCMFI bits to generate interrupt indications on the INTB output pin.

- the CMFACT bit in Register 21H. This bit indicates that a re-search for FAS alignment has been forced at least once since the last time Register 21H was read.

It is expected that the MFAS alignment transient states will be processed using interrupts.

A comprehensive interrupt-handling routine expects interrupts from a variety of sources within the PM6341 E1XC. Therefore, it should first determine which quadrant interrupted then whether the FRMR was the source of the interrupt before processing the OOF and OOCMF status bits. To do this, the microprocessor should read Register 08H to check if the FRMR bit is set to logic one. If so, the software should call a routine which implements the transient framing states matrix detailed in the next section.

Once a FRMR interrupt is detected, a software routine which implements the transient states matrix in Section 4.4.4 should be called. The operation of that routine in response to the C.4.4 (A1) test stimulus is explained in Appendix C.

#### 4.4.3 CRC Processing

The ETS 300 011 C.4.5 test stresses the terminal equipment's ability to properly send FEBE's and assert RAI in response to received CRC-4 errors.

The correct response is described in ITU-T G.706 Section 4.3.2. That standard says:

To achieve the probability bounds for detection of false frame alignment, a

preferred threshold count is 915 errored CRC blocks out of 1000, with the

understanding that a count of ≥ 915 errored CRC blocks indicates false

frame alignment.

The E1XC provides configuration bits to support various framing options. If the registers are programmed as indicated in the Initialization section, the E1XC will will respond to stimulus as expected by the ETS 300 011 tests.

The E1XC provides the REFCRCE bit in Register 20H to enable reframing due to excessive CRC-4 errors. Also, It provides the OOF bit in Register 26H to indicate the state of its FAS alignment circuit. Additionally, changes of state of the OOF bit are indicated in the OOFI bit in Register 24H. The OOFI bit can be enabled to indicate interrupts on the INTB signal by setting the OOFE bit in Register 22H to logic one.

Generally, the equipment should send an RAI in response to loss of FAS alignment. This is accomplished by setting the REMAIS bit to logic one when the E1XC interrupts indicating OOFI=1 and OOF=1. The REMAIS bit should be cleared to logic zero when the E1XC interrupts indicating OOFI=1 and OOF=0. An explanation of how the matrix in Section 4.4.4 responds to the C.4.5 test stimulus is given in Appendix D.

## 4.4.4 Transient Framing States Matrix

Figure 1 shows a decision tree to determine which event has occurred based on status bits and software variables.

Figure 1. Event Decision Tree OOFI OOCMF OOF EVENT ( EVENT 2 CMFAC OOCMF EVENT 1 OOCMFI GNORE EVENT 7 CMF **FALSE** EVENT 7 TRUE EVENT 8 EVENT 3 **EVENT 6 T3 EXP FALSE** TRUE EVENT EVENT 4

Table 4 depicts a transient state matrix for framing events. The table associates interrupt events with movement about the matrix. The following acronyms and symbols are used:

| /      | Impossible event. No response is required.                                                                                                                                                                                                                                                                                             |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _      | No response required.                                                                                                                                                                                                                                                                                                                  |

| CMF    | This Boolean software variable indicates whether the MFAS alignment circuit has found MFAS alignment at least once since the list time the FAS alignment circuit was out-of-frame alignment due to FAS errors. CMF will be cleared to FALSE when the IUT moves from S1 to S2 and CMF will be set to TRUE whenever the IUT moves to S3. |

| CMFACT | Bit 1 in Register 21H of the E1XC. This bit indicates that the current OOF=1 state was caused by the MFAS alignment circuitry which forced a reframe because it could not find MFAS alignment within 8 ms.                                                                                                                             |

| CRCEN  | Bit 7 of Register 20H. When set, this bit enables the MFAS find circuitry.                                                                                                                                                                                                                                                             |

| E0     | Event 0. Non transient event. This is indicated by OOFI=0 and OOCMFI-0, or OOFI,=0 OOCMFI=1 and OOCMF=1.                                                                                                                                                                                                                               |

| E1     | Event 1. FAS alignment lost due to FAS errors. This is indicated by OOFI=1, OOF=1, and CMFACT=0.                                                                                                                                                                                                                                       |

| E2     | Event 2. FAS alignment found. This is indicated by OOFI=1 and OOF=0.                                                                                                                                                                                                                                                                   |

| E3     | Event 3. MFAS alignment found. This is indicated by OOFI=0, OOCMFI=1, OOCMF=0, and IGNORE=0.                                                                                                                                                                                                                                           |

| E4     | Event 4. FAS reframe forced and T3 is expired and no MFAS alignment was found before T3 expired. This is indicated by OOFI=1, OOF=1, CMFACT=1, OOCMFI=0, CMF=FALSE, and T3>300 ms.                                                                                                                                                     |

| E5     | Event 5. FAS reframe forced while timer, T3, is not yet expired and MFAS alignment has not been found. This is indicated by OOFI=1, OOF=1, CMFACT=1, OOCMFI=0, CMF=FALSE and T3<300 ms.                                                                                                                                                |

| E6     | Event 6. FAS reframe forced and MFAS alignment has been found at least once. This is indicated by OOFI=1, OOF=1, CMFACT=1, OOCMFI=0, and CMF=TRUE.                                                                                                                                                                                     |

| E7     | Event 7. MFAS alignment lost. This is indicated by OOFI=1, OOF=1, CMFACT=1, and OOCMFI=1.                                                                                                                                                                                                                                              |

| E8     | Event 8. Spurious MFAS alignment found. This is indicated by OOFI=0, OOCMFI=1, OOCMF=0, and IGNORE=1.                                                                                                                                                                                                                                  |

| FALSE  | This is the Boolean value FALSE.                                                                                                                                                                                                                                                                                                       |

| IGNORE | This Boolean software variable indicates whether the first occurrence of MFAS alignment is spurious and should therefore be ignored.                                                                                                                                                                                                   |

|        |                                                                                                                                                                                                                                                                                                                                        |

#### APPLICATION NOTE

| PMC-951128 | ISSUE3                                                                   | E1 FRAMER/TRANSCEIVER                                                                                                                               |

|------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| NOF        |                                                                          | d, clears the RAI indication (A-Bit in TS0) in the lished by clearing the REMAIS bit in Register 45H of                                             |

| OOCMF      | Bit 4 in Register 26H of the E1XC. alignment circuit.                    | This bit indicates the current state of the MFAS                                                                                                    |

| OOCMFI     | Bit 4 in Register 24H of the E1XC. alignment circuit has caused an int   | This bit indicates that a change of status of the MFAS errupt.                                                                                      |

| OOF        | Bit 6 in Register 26H of the E1XC. alignment circuit.                    | This bit indicates the current state of the FAS                                                                                                     |

| OOFI       | Bit 6 in Register 24H of the E1XC. alignment circuit has caused an int   | This bit indicates that a change of status of the FAS errupt.                                                                                       |

| RAI        |                                                                          | d, sets the RAI indication (A-Bit in TS0) in the lished by setting the REMAIS bit in Register 45H of the                                            |

| REFR       | Bit 2 in Register 20H. This bit shot alignment.                          | uld be cleared then set to force a reframe of basic frame                                                                                           |

| REFRDIS    | Bit 0 in Register 20H. When set, th                                      | is bit suppresses the basic frame find circuit.                                                                                                     |

| RESET_T3   | This is a reference to reset timer T                                     | 3.                                                                                                                                                  |

| S1         | Transient State 1. In this state, the lost due to FAS errors. RAI should | e IUT is searching for FAS alignment because it was I be transmitted during this state.                                                             |

| S2         | Transient State 2. In this state, the MFAS alignment. RAI should not be  | e IUT has acquired FAS alignment and is searching for pe transmitted during this state.                                                             |

| S3         |                                                                          | e IUT has acquired both FAS alignment and MFAS ational state. RAI should not be transmitted during this                                             |

| S4         |                                                                          | e IUT has acquired FAS alignment, but not MFAS expired and CMF=FALSE. RAI should be transmitted in                                                  |

| S5         | MFAS alignment circuit forced the                                        | e IUT is searching for FAS alignment because the FAS alignment circuit to reframe while the timer, T3, RAI should be transmitted during this state. |

| S6         |                                                                          | e IUT is searching for FAS alignment because the FAS alignment circuit to reframe while CMF=TRUE. ng this state.                                    |

| Sz         | Go to State Sz.                                                          |                                                                                                                                                     |

| PMC-951128 | ISSUE 3                                                                                                                                                | E1 FRAMER/TRANSCEIVER |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Т3         | Timer 3. This is a resettable timer which implements the G.706 Section 4.2. A 300 ms expiry limit is recommend 100 to 500 ms range specified in G.706. |                       |

| TRUE       | This is the Boolean value TRUE.                                                                                                                        |                       |

The transient states matrix in Table 4 assumes that the E1XC has been initialized as recommended in the Initialization section.

Also, the bits in Register 24H and the CMFACT bit in Register 21H are cleared upon read. Therefore, whenever these registers are read all the bits must be fully processed or else stored for future processing.

Table 4 should be interpreted as follows:

- a) The interrupt event should be determined based on Figure 1.

- b) The entry in Table 4 should be located, the one which corresponds to the current state and the interrupt event.

- c) If the table entry has a " / " or " " then no action need be taken. Else the following actions need to be taken:

- i) The next state (indicated in the entry) should be entered.

- ii) The software variables should be updated as indicated.

- iii) The Timer T3 should be controlled as indicated.

- iv) The transmitted RAI should be controlled as indicated.

# **Table 4. Transient States Matrix**

| Event      | Initial State                                            |                                 |                          |                                  |            |           |  |

|------------|----------------------------------------------------------|---------------------------------|--------------------------|----------------------------------|------------|-----------|--|

|            | S1                                                       | S2                              | <b>S</b> 3               | S4                               | <b>S</b> 5 | S6        |  |

| E1         | /                                                        | R.<br>CRCI                      | S1<br>AI<br>EN=1<br>RE=0 | _                                | ,          | /         |  |

| E2         | S2<br>RESET_T3<br>CMF=FALSE<br>NOF<br>REFR=0<br>IGNORE=0 | ,                               | /                        | _                                | S2<br>NOF  | S2<br>NOF |  |

| <b>E</b> 3 | /                                                        | S3 CMF=TRUE / NOF NOF REFRDIS=0 |                          | ,                                | ,          |           |  |

| E4         | S4<br>RAI<br>REFRDIS=1<br>IGNORE=1                       |                                 | 1                        | _                                | ,          | 1         |  |

| E5         | / S5<br>RAI                                              |                                 |                          | ,                                | ,          |           |  |

| E6         | / S6<br>NOF                                              |                                 |                          | ,                                | ,          |           |  |

| E7         | ,                                                        | 1                               | S2<br>NOF<br>CRCEN=0     |                                  | 1          |           |  |

| E8         |                                                          | /                               |                          | S4<br>IGNORE=0<br>TOGGLE<br>REFR |            | /         |  |

#### 5 HARDWARE RECOMMENDATIONS

This section details some of the hardware considerations necessary for an E1XC-based design to comply with ETS 300 011. Only the requirements which relate directly to the E1XC and its operation are covered in this section.

# 5.1 Timing Connections

The E1XC is designed to have a variety of timing options for the transmit and receive data paths.

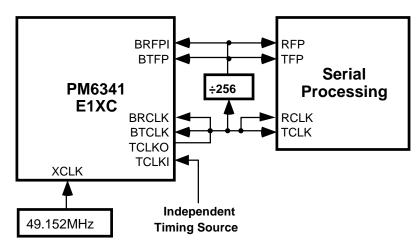

Figure 2 shows the recommended hardware connections for timing distribution.

Figure 2 Recommended Timing Connections

The timing connections shown in Figure 2 can support the different synchronization modes required for the Ia and Ib interface. The Ib interface always synchronizes its timing to the network clock (independently-timed mode), while the Ia interface times synchronizes its timing to the recovered line clock (loop-timed mode), unless the line signal is lost in which case the Ia must switch to a local independent timing reference (hold-over mode).

The connections shown in Figure 2 support all three synchronization modes. This connection scheme provides the required transmit timing options by using the PLLREF[1:0] bits in Register 07H of the E1XC.

#### 5.1.2 Loop-Timed Mode

In loop-timed mode, the transmit timing is synchronized to the timing recovered from the line. With the connections shown in Figure 2, this is accomplished by setting the PLLREF[1:0] bits in the E1XC to 10B. In that case the RCLKO signal is internally connected as the transmit timing reference.

#### 5.1.3 Independently-Timed Mode

In independently-timed mode, the transmit timing is sourced from an independent timing source. With the connections shown in Figure 2, this is accomplished by setting the PLLREF[1:0] bits in the E1XC to 11B. In that case the TCLKI input signal is used as the transmit timing reference.