ISSUE 8

PM5346 S/UNI-155-LITE

SATURN USER NETWORK INTERFACE

## PM5346

PMC PMC-Sierra, Inc.

# INTERFACING AND PC BOARD LAYOUT SUGGESTIONS FOR THE S/UNI-LITE

## **APPLICATION NOTE**

**ISSUE 8: SEPTEMBER 1997**

PMC-Sierra, Inc.

PM5346 S/UNI-155-LITE

ISSUE 8

SATURN USER NETWORK INTERFACE

ISSUE 8

### **CONTENTS**

| 1 | SUG  | GESTIONS FOR S/UNI-LITE BOARD LAYOUT 1                               |

|---|------|----------------------------------------------------------------------|

|   | 1.1  | DECOUPLING CAPACITORS ON ANALOG POWER 1                              |

|   | 1.2  | POWER AND GROUND CONNECTIONS 1                                       |

|   | 1.3  | FERRITE BEADS ON DIGITAL POWER SUPPLY 6                              |

|   | 1.4  | FERRITE BEADS ON ANALOG POWER SUPPLY7                                |

|   | 1.5  | REGULATING THE ANALOG POWER SUPPLY (OPTIONAL) 7                      |

|   | 1.6  | ANALOG TEST PINS                                                     |

|   | 1.7  | LOOP FILTER COMPONENTS7                                              |

|   | 1.8  | UNUSED INPUT PINS                                                    |

|   | 1.9  | DEALING WITH HIGH-SPEED RETURN CURRENTS7                             |

| 2 | SUGO | GESTIONS FOR S/UNI-LITE PECL TERMINATIONS                            |

|   | 2.1  | S/UNI-LITE TXD TO PMD 10                                             |

|   | 2.2  | DC COUPLED TXD+ VIA CMOS TO PECL CONVERTER 10                        |

|   | 2.3  | DIFFERENTIAL REFERENCE OSCILLATOR TERMINATIONS . 12                  |

|   | 2.4  | SINGLE TTL/CMOS REFERENCE OSCILLATOR DRIVING BOTH<br>RRCLK AND TRCLK |

| 3 | S/UN | I-LITE CLOCK RECOVERY LOOP FILTER COMPONENTS 14                      |

|   | 3.1  | POLARIZED TANTALUM CAPACITORS CONNECTED IN SERIES                    |

| 4 | REFE | RENCES 17                                                            |

ISSUE 8

SATURN USER NETWORK INTERFACE

#### **LIST OF FIGURES**

| FIGURE 1 - RECOMMENDED LAYOUT FOR VDD DECOUPLING<br>CONNECTION TO ANALOG POWER PINS | 1         |

|-------------------------------------------------------------------------------------|-----------|

| FIGURE 2                                                                            | 2         |

| FIGURE 3 - S/UNI-LITE TO PMD AND REFERENCE OSCILLATOR<br>TERMINATIONS               | 9         |

| FIGURE 4                                                                            | 10        |

| FIGURE 5 - CMOS TO PECL CONVERTER                                                   | 11        |

| FIGURE 6 - REFERENCE OSCILLATOR TERMINATIONS                                        | 12        |

| FIGURE 7                                                                            | 13        |

| FIGURE 8 - LOOP FILTER USING CERAMIC NON-POLARIZED CAP                              | ACITORS15 |

| FIGURE 9 - LOOP FILTER USING TANTALUM POLARIZED CAPACITO                            | ORS 16    |

PMC-Sierra, Inc.

APPLICATION NOTE PMC-941031

ISSUE 8

SATURN USER NETWORK INTERFACE

## LIST OF TABLES

|     | - S/UNI-LITE POWER/GROUND PINS | TABLE 1 |

|-----|--------------------------------|---------|

| 514 | - RECOMMENDED COMPONENT VALUE  | TABLE 2 |

|     |                                | TABLE 3 |

ISSUE 8

APPLICATION NOTE PMC-941031

SATURN USER NETWORK INTERFACE

iv

SATURN USER NETWORK INTERFACE

#### 1 SUGGESTIONS FOR S/UNI-LITE BOARD LAYOUT

ISSUE 8

#### 1.1 Decoupling Capacitors on Analog Power

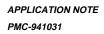

Decoupling capacitors (0.1 µF Ceramic X7R) are recommended for each analog power pin (TAVD1, TAVD2, TAVD3, TXVDD, RAVD1, RAVD2, RAVD3, RAVD4) placed as close to the package pin as possible according to the layout recommendation in figure 1 below. In particular, separate decoupling capacitors are strongly recommended for the TAVD1, TAVD2, RAVD1 and RAVD2 pins.

Separate decoupling is recommended to prevent transmit from coupling transient noise into the receiver. TAVD1 and RAVD1 are power supplies for voltage reference circuitry for the transmit and receive PLLs respectively. There must be separate decoupling of TAVD2 from TAVD1; RAVD2 must be separately decoupled from RAVD1. This prohibits transients from coupling into the references (i.e., RAVD1 and TAVD1).

## Figure 1 - Recommended Layout for VDD Decoupling Connection to Analog Power Pins

#### 1.2 Power and Ground Connections

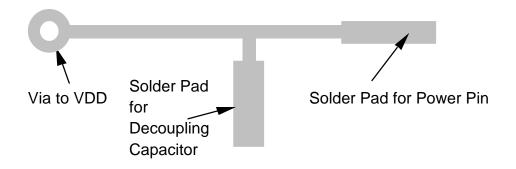

It is advisable to separate the S/UNI-LITE transmit power/ground pins from the receive power/ground pins by splitting the power and ground planes in the area surrounding these pins as shown in figure 2.

PM5346 S/UNI-155-LITE

APPLICATION NOTE PMC-941031

ISSUE 8

SATURN USER NETWORK INTERFACE

Figure 2

Power and Ground requirements are a function of the noise environment on a board and the performance target of the board. Ground and power supply noise will degrade the bit error performance of the S/UNI-LITE and introduce intrinsic jitter on the transmitted data. Table 1 is a summary of all power and ground connections for the S/UNI-LITE. The "Supply Noise Sensitivity" column highlights pins that are sensitive to perturbations on the supply rails. The "Current" column identifies the current consumption for a particular pin as either dynamic (fluctuating over time) or static (constant over time). The "Layout Consideration" column provides further detail regarding the layout requirements for each pin.

ISSUE 8

SATURN USER NETWORK INTERFACE

## Table 1 - S/UNI-LITE Power/Ground Pins

| Pin Name | Туре   | Supply Noise<br>Sensitivity | Current | Pin No. | Layout<br>Consideration                                                    |

|----------|--------|-----------------------------|---------|---------|----------------------------------------------------------------------------|

| RAVS1    | Ground | High                        | Static  | 31      | The ground<br>(RAVS1) pin for<br>analog voltage<br>reference<br>circuitry  |

| RAVS2    | Ground | High                        | Dynamic | 37      | The ground<br>(RAVS2) pin for<br>receive loop filter<br>and VCO.           |

| RAVS3    | Ground | High                        | Dynamic | 29      | The ground<br>(RAVS3) pin for<br>the RXD+/- &<br>ALOS+/- PECL<br>inputs.   |

| RAVS4    | Ground | High                        | Dynamic | 35      | The ground<br>(RAVS4) pin for<br>the RRCLK+/-<br>PECL inputs.              |

| TAVS1    | Ground | High                        | Static  | 5       | The ground<br>(TAVS1) pin for<br>analog voltage<br>reference<br>circuitry  |

| TAVS2    | Ground | High                        | Dynamic | 7       | The ground<br>(TAVS2) pin for<br>the transmit<br>clock synthesizer<br>VCO. |

| TAVS3    | Ground | High                        | Dynamic | 11      | The ground<br>(TAVS3) pin for<br>the transmit<br>PECL inputs.              |

PM5346 S/UNI-155-LITE

APPLICATION NOTE PMC-941031

ISSUE 8

SATURN USER NETWORK INTERFACE

| Pin Name                                                                                                    | Туре              | Supply Noise<br>Sensitivity | Current | Pin No.                                                                     | Layout<br>Consideration                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------|-------------------|-----------------------------|---------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXVSS                                                                                                       | Ground            | High                        | Dynamic | 17                                                                          | The transmit pad<br>ground (TXVSS)<br>is the return path<br>for the TXC+/-<br>and TXD+/-<br>outputs. TXVSS<br>is physically<br>isolated from the<br>other device<br>ground pins and<br>should be noise<br>free for good<br>performance.                                           |

| VSSI1H<br>VSSI2<br>VSSI3                                                                                    | Ground            | Low                         | Dynamic | 19<br>62<br>106                                                             | The core ground<br>(VSSI1 - VSSI3)<br>pins should be<br>connected to<br>GND in common<br>with VSSO.                                                                                                                                                                               |

| VSSO1<br>VSSO2<br>VSSO3<br>VSSO4<br>VSSO5                                                                   | Ground            | Low                         | Dynamic | 21<br>56<br>72<br>80<br>113                                                 | The pad ring<br>ground (VSSO1 -<br>VSSO5) pins<br>should be<br>connected to<br>GND in common<br>with VSSI.                                                                                                                                                                        |

| VSS1,<br>VSS2,<br>VSS3,<br>VSS4,<br>VSS5,<br>VSS6,<br>VSS7,<br>VSS8,<br>VSS9,<br>VSS10,<br>VSS11,<br>VSS12, | Thermal<br>Ground | Low                         | Dynamic | 1<br>38<br>39<br>64<br>65<br>102<br>103<br>128,<br>45,<br>46,<br>47,<br>48, | The thermal<br>grounds (VSS1 -<br>VSS13) provide<br>a low thermal<br>resistance for the<br>dissipated heat.<br>These pins must<br>be connected to<br>DIGITAL GND<br>only for correct<br>operation.<br>Note: these pins<br>are electrically<br>connected<br>together<br>internally |

PM5346 S/UNI-155-LITE

APPLICATION NOTE PMC-941031

ISSUE 8

SATURN USER NETWORK INTERFACE

| Pin Name | Туре  | Supply Noise<br>Sensitivity | Current | Pin No. | Layout<br>Consideration                                                   |

|----------|-------|-----------------------------|---------|---------|---------------------------------------------------------------------------|

| RAVD1    | Power | High                        | Static  | 30      | The power<br>(RAVD1) pin for<br>analog voltage<br>reference<br>circuitry. |

| RAVD2    | Power | High                        | Dynamic | 36      | The power<br>(RAVD2) pin for<br>receive loop filter<br>and VCO.           |

| RAVD3    | Power | High                        | Dynamic | 24      | The power<br>(RAVD3) pin for<br>the RXD+/- and<br>ALOS+/- PECL<br>inputs. |

| RAVD4    | Power | High                        | Dynamic | 32      | The power<br>(RAVD4) pin for<br>the RRCLK+/-<br>PECL inputs.              |

| TAVD1    | Power | High                        | Static  | 4       | The power<br>(TAVD1) pin for<br>analog voltage<br>reference<br>circuitry. |

| TAVD2    | Power | High                        | Dynamic | 6       | The power<br>(TAVD2) pin for<br>the transmit<br>clock synthesizer<br>VCO. |

| TAVD3    | Power | High                        | Dynamic | 8       | The power<br>(TAVD3) pin for<br>the transmit<br>PECL inputs.              |

ISSUE 8

SATURN USER NETWORK INTERFACE

| Pin Name                                  | Туре  | Supply Noise<br>Sensitivity | Current | Pin No.                     | Layout<br>Consideration                                                                                                                                                                                                                                    |

|-------------------------------------------|-------|-----------------------------|---------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXVDD                                     | Power | High                        | Dynamic | 12                          | The transmit pad<br>power (TXVDD)<br>supplies the<br>TXC+/- and<br>TXD+/- outputs.<br>TXVDD is<br>physically<br>isolated from the<br>other device<br>power pins and<br>should be a well<br>regulated +5 V<br>DC and noise<br>free for good<br>performance. |

| VDDI1<br>VDDI2<br>VDDI3                   | Power | Low                         | Dynamic | 20<br>61<br>107             | The core power<br>(VDDI1 - VDDI3)<br>pins should be<br>connected to a<br>well decoupled<br>+5 V DC in<br>common with<br>VDDO.                                                                                                                              |

| VDDO1<br>VDDO2<br>VDDO3<br>VDDO4<br>VDDO5 | Power | Low                         | Dynamic | 18<br>55<br>73<br>81<br>114 | The pad ring<br>power (VDDO1 -<br>VDDO5) pins<br>should be<br>connected to a<br>well decoupled<br>+5 V DC in<br>common with<br>VDDI.                                                                                                                       |

#### 1.3 Ferrite Beads on Digital Power Supply

Power supply isolation using Ferrite beads is not advisable in digital switching circuits as di/dt noise is introduced into the power rail. Sufficient capacitive decoupling on all digital power pins is recommended.

SATURN USER NETWORK INTERFACE

#### 1.4 Ferrite Beads on Analog Power Supply

Ferrite beads for power supply isolation can be used in analog (and ECL) circuitry where there is no di/dt noise due to single ended switching currents. If this not the case, or it is uncertain that the circuitry is operating in a balanced fashion, then using RC filtering or local bulk decoupling to filter local di/dt noise is recommended.

#### 1.5 Regulating the Analog Power Supply (Optional)

In applications that provide a +12V supply, a 5V regulator can be used to supply a low-noise analog power supply. The regulator should supply all analog power pins (TAVD1-4 and RAVD1-4); the total power draw of the analog circuitry in the S/UNI-LITE is less than 30mW. At a minimum, the regulator should power RAVD1, RAVD2, TAVD1, and TAVD2.

#### 1.6 Analog Test Pins

The Analog test pins must be grounded. ATP1 should be connected to the Receive analog ground plane. ATP2 should be connected to the Transmit analog ground plane.

#### 1.7 Loop Filter Components

The loop filter components should be placed such that they sit over the Receive analog ground plane.

#### 1.8 Unused Input Pins

All unused input pins should be tied to their appropriate inactive level.

#### 1.9 Dealing with high-speed return currents

At low speeds, return current follows the path of least resistance back to the driver. At high speeds, however, the return current follows the path of least inductance which lies on the plane directly under the signal trace, as the total loop area between the outgoing and returning paths is minimized. In other words, the high-speed return current follows a path that is almost the "mirror image" of the signal trace on the plane underneath the trace. This tight coupling provides good flux cancellation so that common-mode current is reduced. High speed traces should not cross cuts or heavily perforated areas (where tight spacing through-hole components reside) on the power and ground planes, as

ISSUE 8

SATURN USER NETWORK INTERFACE

any cuts on these planes may interrupt the return currents, causing them to seek alternative paths back to the driver. The different routes taken by the outgoing and return currents will both induce common-mode noise on other nearby signal traces. In addition, by routing high speed signals over continuous power planes, the return current paths of these signals are known and other signals will not cross over these return currents, reducing the possibility of noise coupling. Detailed discussions on high-speed design are provided by the references.

#### 2 SUGGESTIONS FOR S/UNI-LITE PECL TERMINATIONS

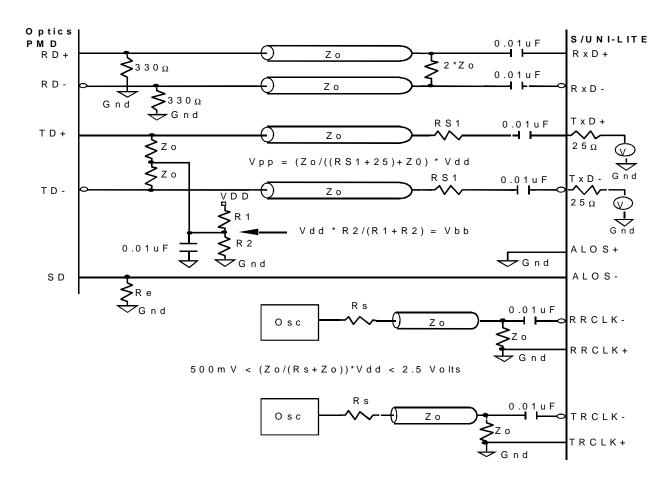

Figure 3 - S/UNI-LITE to PMD and Reference Oscillator Terminations

#### Notes for Figure 3:

- Vpp is minimum input swing required by the optical PMD device.

- Vbb is the switching threshold of the PMD device (typically Vdd 1.3 Volts).

- Vpp is Voh Vol (typically 800 mVolts).

- The value of Re is dependent on the signal trace characteristic impedance and the ECL or PECL supply voltage (-4.5 V, +5 V).

- Values in the range of 200-300  $\Omega$  are recommended.

• A single oscillator can be used to drive both RRCLK and TRCLK.

#### 2.1 S/UNI-LITE TxD to PMD

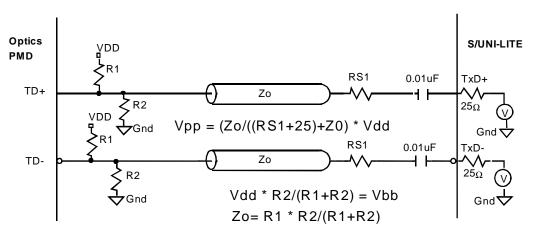

The TxD outputs from the S/UNI-LITE may also use Thévenin termination resistors that provide the Vbb bias voltage rather than the resistor-divider shown above. While this circuit uses one less component (0.01  $\mu$ F decoupling capacitor), it is more susceptible to common mode noise.

#### Figure 4

Notes: Vpp is minimum input swing required by the optical PMD device. Vbb is the switching threshold of the PMD device (typically Vdd - 1.3 volts) Vpp is Voh - Vol (typically 800 mVolts) For Zo = 50  $\Omega$ , R1=67  $\Omega$ , R2 = 192.3  $\Omega$ , RS1=237 $\Omega$

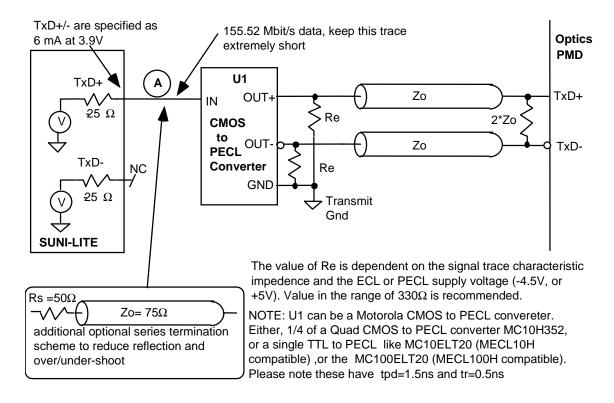

#### 2.2 DC coupled TxD+ via CMOS to PECL converter

Schemes (1) and (2) above use AC-coupling capacitors on the TXD+/- S/UNI-LITE outputs. A disadvantage of this scheme is that Diagnostic LOS (DLOS register bit) can no longer be used because the AC-coupled all zero transmit data will cause the PMD inputs to float to the Vbb threshold. This can result in the PMD transmitting pulses due to board noise. A way to eliminate this is to use a CMOS to PECL converter, between the S/UNI-LITE TXD+/- outputs and the ODL. Due to the high data rate, and this single ended CMOS I/F, make sure the converter is located right at the S/UNI-LITE TXD output.

Care must be taken to maintain signal integrity for low jitter. Connection 'A' below, must be an extremely short signal trace (less than 1") with no termination. Optionally, for slightly longer trace, a series termination and a controlled

|                  | PMC     | PMC-Sierra, Inc. | PM5346 S/UNI-155-LITE         |

|------------------|---------|------------------|-------------------------------|

| APPLICATION NOTE |         |                  |                               |

| РМС-941031       | ISSUE 8 |                  | SATURN USER NETWORK INTERFACE |

transmission trace is required. The length limit of such a terminated CMOS trace depends on factors such as system ground noise, Zo and Rs. The value of Rs depends on the SUNI-LITE source driver impedance (about  $25\Omega$ ) and the Zo of the controlled signal PCB trace (Zo= $25\Omega$ +Rs).

### Figure 5 - CMOS to PECL Converter

APPLICATION NOTE

PMC-941031

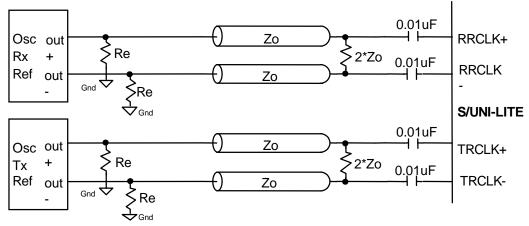

#### 2.3 **Differential Reference Oscillator Terminations**

For optimum jitter performance on the transmit side and noise immunity on the receive side the reference clocks should be connected differentially.

Figure 6 - Reference Oscillator Terminations

The value of Re is dependent on the signal trace characteristic impedence and the ECL or PECL supply voltage (-4.5 V, + 5 V). Values in the range of 200-330  $\Omega$  are recommended

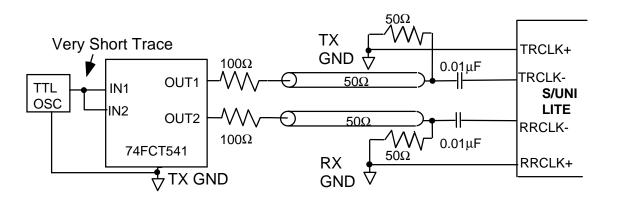

#### 2.4 Single TTL/CMOS Reference Oscillator Driving Both RRCLK and TRCLK

If a single TTL or CMOS oscillator is used to drive these inputs, the RRCLK- and TRCLK- inputs can be used while RRCLK+ and TRCLK+ signals are connected to their respective grounds. The single clock signal must be properly terminated, however, it is not a good idea to connect the clock trace to either RRCLK- or TRCLK- and then run the trace to the other input and terminate at the far end. The transmit and receive grounds are isolated by channels cut into the ground plane, so potential differences between transmit and receive grounds will affect one of the reference clock inputs. For example, if the reference clock signal is run to the TRCLK input and then is terminated to the receive ground near the RRCLK input, the TRCLK input (which is referenced to the transmit ground) will require the clock swing to be large enough to accommodate the difference between grounds. Otherwise, the TRCLK input will be more sensitive to noise than the RRCLK input. A second problem may arise if the clock signal trace crosses the cuts in the ground plane (i.e. from transmit ground island to receive ground island). In that case the ground return current from the receive side cannot follow the signal trace back to the driver. Instead, it will seek an

alternative path of least inductance. Consequently, this ground current will induce common-mode noise on signals nearby.

The solution is to run two separate reference clock signals and terminate them at each input<sup>1</sup>. The following diagram illustrates how to use a single TTL level oscillator to drive the RRCLK- & TRCLK- signals via a 74FCT541 buffer. The TRCLK+ and RRCLK+ signals are connected to their respective grounds.

### Figure 7

The TTL oscillator should be placed as close to the buffer as possible as it is unterminated. The TTL oscillator is used to match the 74FCT541's TTL input level in order to avoid duty cycle distortion caused by differences in output levels and input switching thresholds.

<sup>&</sup>lt;sup>1</sup> A layout alternative could be to run a 50 ohm clock trace to the vicinity of the RRCLK- & TRCLK- inputs and then split into two 100 ohm traces. Each one of these two traces could then be connected to the RRCLK- or TRCLK- input and each terminated with 100 ohm to the receive or transmit analog ground respectively. However, this is not recommended because the resulting the width of a 100 Ohm trace is very narrow (less than 3 mil). This width will be difficult for board manufacturers to fabricate accurately and reliably. Inaccuracy in the trace impedance will cause the signals to be improperly terminated.

SATURN USER NETWORK INTERFACE

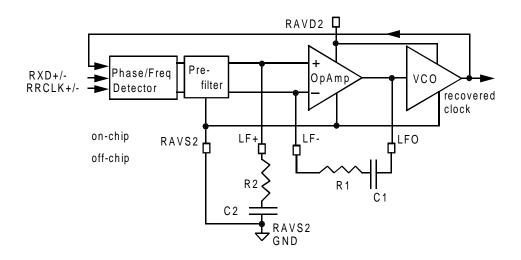

#### 3 S/UNI-LITE CLOCK RECOVERY LOOP FILTER COMPONENTS

**ISSUE 8**

The asymmetrical loop filter values were chosen to achieve maximum performance in the LAN environment. As well, to eliminate the power drain of the above mentioned emitter-follower and to achieve maximum jitter tolerance, the jitter transfer 20 db/decade, 130 kHz -3dB point can be sacrificed. Since the S/UNI-LITE is a terminating device and will not be used as a regenerator, the jitter transfer -3 dB point is not relevant.

All resistors are 1% metal film (1/8 or 1/10 watt) resistors and all capacitors should be  $\pm 10\%$  and non-polarized since under some cases the capacitors may be reversed biased by up to 2 Volts DC. A non-polarized ceramic capacitor or series connected polarized Tantalum capacitors may be used as shown below. Type X7R or X5R dielectric monolithic ceramic capacitors are recommended as these have the most desirable temperature coefficient, are non-polarized and the 0.47µF devices are readily available from several vendors, including AVX, Philips, TDK, Vitramon, and Prestidio.

#### Table 2 - Recommended Component Values

| Line Rate<br>(Mbit/s) | R1 (Ω) | R2 (Ω) | C1, C2 (µF) min | Transfer Function<br>BW |

|-----------------------|--------|--------|-----------------|-------------------------|

| 155.52 & 51.84        | 200    | 412    | 0.47 µF         | 450 kHz                 |

| 25.92 & 12.96         | 200    | 412    | 2.2 µF          | 75 kHz                  |

Recommended capacitor values will maintain jitter transfer peaking below the required 0.1 dB level. The capacitor values are the minimum recommended values; larger values of capacitance can be used on any of the line rates.

#### Figure 8 - Loop Filter Using Ceramic Non-Polarized Capacitors

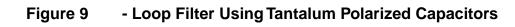

#### 3.1 **Polarized Tantalum Capacitors Connected in Series**

For lower line rates, a 2.2 µF capacitor is required. Due to footprint requirements, or sourcing constraints, two polarized Tantalum capacitors connected in series may be a more desirable option. Either back to back (-'ve to -'ve) or anode to anode (+'ve to +'ve) may be used to form one non-polar capacitor. Since the effective capacitance will be halved, two 4.7 µF capacitors must be used to form a 2.35 µF non-polar capacitor. Since the LF+ pin will always have a positive DC bias (about +1 Vdc when in lock), C2 may be a single polarized capacitor with the positive terminal connected to the LF+ pin. However, C1 is made up of a series combination of C1a and C1b as shown in the schematic below. AVX corporation publishes several articles on back to back tantalums.

PMC-941031

| Line Rate<br>(Mbit/s) | R1 (Ω) | R2 (Ω) | C2 (µF) min. | C1a (µF) min. | C1b (µF) min. | Transfer<br>Function BW |

|-----------------------|--------|--------|--------------|---------------|---------------|-------------------------|

| 25.92 & 12.96         | 200    | 412    | 2.2          | 4.7           | 4.7           | 75 kHz                  |

SATURN USER NETWORK INTERFACE

ISSUE 8

SATURN USER NETWORK INTERFACE

#### 4 REFERENCES

- 1. PMC-Sierra, Inc., PM5346 S/UNI-LITE Data Sheet, Issue 4, November, 1994.

- 2. Ott, Henry W., "Noise Reduction Techniques in Electronic Systems", Second Edition, John Wiley & Sons.

- 3. Montrose, Mark I., "Printed Circuit Board Design Techniques for EMC Compliance", IEEE Press, 1995.

- 4. Graham, Martin and Johnson, Howard W., "High-Speed Digital Design: A Handbook of Black Magic", PRT Prentice-Hall Inc, 1993.

PM5346 S/UNI-155-LITE

ISSUE 8

SATURN USER NETWORK INTERFACE

**NOTES**

PM5346 S/UNI-155-LITE

ISSUE 8

SATURN USER NETWORK INTERFACE

**NOTES**

ISSUE 8

SATURN USER NETWORK INTERFACE

#### **CONTACTING PMC-SIERRA, INC.**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

**Document Information:** Corporate Information: Application Information: Web Site:

document@pmc-sierra.com info@pmc-sierra.com apps@pmc-sierra.com http://www.pmc-sierra.com

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra. Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1997 PMC-Sierra, Inc.

PM-941031 (R8) Issue date: September 1997

PMC-Sierra, Inc.