## **FUJITSU SEMICONDUCTOR**

**CONTROLLER MANUAL**

# F<sup>2</sup>MC-16LX FAMILY 16-BIT MICROCONTROLLER MB90590 SERIES HARDWARE MANUAL

# F<sup>2</sup>MC-16LX FAMILY 16-BIT MICROCONTROLLER MB90590 SERIES HARDWARE MANUAL

## **PREFACE**

## ■ Objectives and Intended Reader

Thank you very much for your continued patronage of Fujitsu semiconductor products.

The MB90590 series has been developed as a general-purpose version of the  $F^2MC^{@}$ -16LX series, which is an original 16-bit single-chip microcontroller compatible with the Application Specific IC (ASIC).

This manual explains the functions and operation of the MB90590 series for designers who actually use the MB90590 series to design products. Read this manual first.

#### ■ Trademarks

F<sup>2</sup>MC stands for FUJITSU Flexible Microcontroller and is a registered trademark of Fujitsu Limited.

## ■ Structure of This Manual

## **Chapter 1 Overview**

Chapter 1 explains the advantages and basic specifications of the MB90590 series.

### Chapter 2 CPU

Chapter 2 explains the memory layout of the MB90590 series.

### Chapter 3 Interrupts

Chapter 3 explains the interrupt functions of the MB90590 series and also explains the functions and operation of the extended intelligent I/O service (EI<sup>2</sup>OS).

#### **Chapter 4 Delayed Interrupts**

Chapter 4 explains the delayed interrupt functions and operation.

## Chapter 5 Clock and Reset

Chapter 5 explains the clock and reset functions and operation.

#### **Chapter 6 Low-Power Control Circuit**

Chapter 6 explains the functions and operation of the low-power control circuit.

#### **Chapter 7 Memory Access Modes**

Chapter 7 explains the functions and operation of the memory access modes.

## Chapter 8 I/O Ports

Chapter 8 explains the I/O port functions and operation.

#### **Chapter 9 Time Base Timer**

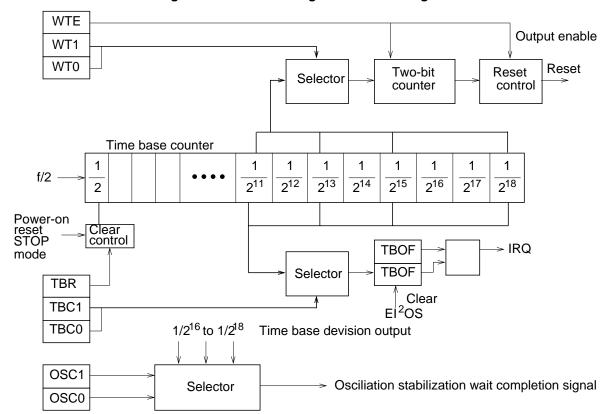

This chapter explains the time base timer functions and operation.

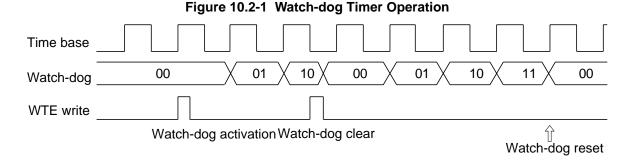

#### **Chapter 10 Watchdog Timer**

Chapter 10 explains the watchdog timer functions and operation.

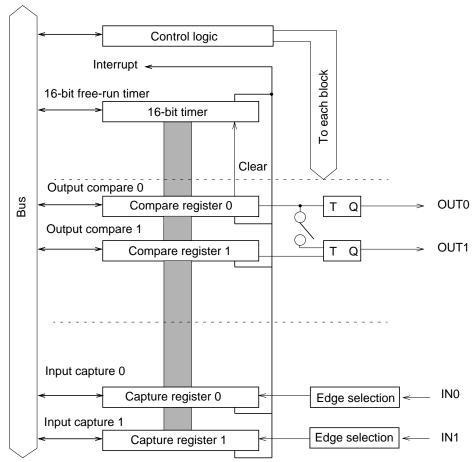

#### Chapter 11 16-bit I/O Timer

Chapter 11 explains the 16-bit I/O timer functions and operation.

## Chapter 12 16-bit Reload Timer (with Event Count Function)

Chapter 12 explains functions and operation of the 16-bit reload timer (with the event count function).

#### **Chapter 13 Time Base Timer**

Chapter 13 explains the time base timer functions and operation.

## Chapter 14 8/16-bit PPG

Chapter 14 explains the 8/16-bit PPG functions and operation.

#### **Chapter 15 DTP/External Interrupts**

Chapter 15 explains the DTP/external interrupt functions and operation.

## Chapter 16 A/D Converter

Chapter 16 explains the A/D converter functions and operation.

## Chapter 17 UART0

Chapter 17 explains the UART0 functions and operation.

#### Chapter 18 Serial I/O

Chapter 18 explains the serial I/O functions and operation.

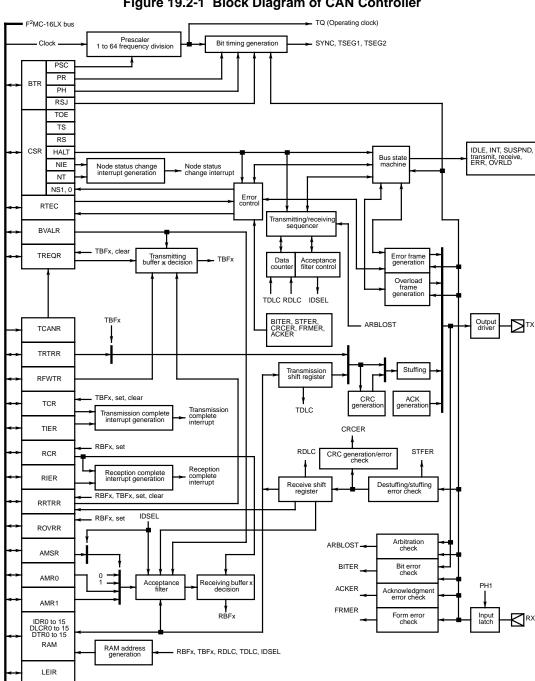

## **Chapter 19 CAN Controller**

Chapter 19 explains the CAN controller functions and operation.

## **Chapter 20 Stepping Motor Controller**

Chapter 20 explains the functions and operation of the stepping motor controller.

#### **Chapter 21 Sound Generator**

Chapter 21 explains sound generator functions and operation.

## **Chapter 22 ROM Correction**

Chapter 22 explains the ROM correction functions and operation.

#### **Chapter 23 ROM Mirroring Function Selection Module**

Chapter 23 explains the functions and operation of the ROM mirroring function selection module.

#### Chapter 24 Two-megabit Flash Memory

Chapter 24 explains the functions and operation of the 2-megabit flash memory.

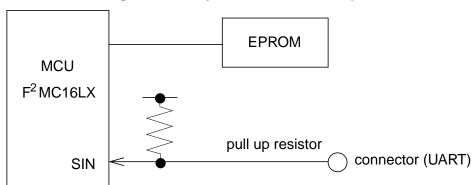

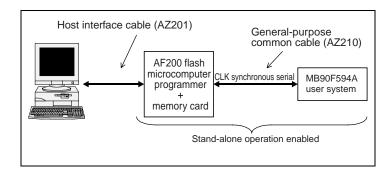

#### Chapter 25 Example of Connection F<sup>2</sup>MC-16LX MB90F594A for Serial Writing

Chapter 25 explains the connection of F<sup>2</sup>MC-16LX MB90F594A for serial writing, using an example.

## **Appendix**

Appendix explains instructions, provides I/O maps and timing diagrams in flash memory mode, and lists MB90590 interrupt vectors.

- 1. The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

- 2. The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

- 3. The contents of this document may not be reproduced or copied without the permission of FUJITSU LIMITED.

- 4. FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipments, industrial, communications, and measurement equipments, personal or household devices, etc.).

## **CAUTION:**

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

- 5. Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- 6. If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.

## **READING THIS MANUAL**

## ■ Page organization

Each section in this document contains a summary of the section. Reading only the summaries will give you an overview of the product.

In addition, the title of the section is also appears in subsections so that you always know which section you are reading.

# **CONTENT**

| CHAP | TER 1 OVERVIEW                                                                                      | 1  |

|------|-----------------------------------------------------------------------------------------------------|----|

| 1.1  | Product Overview                                                                                    | 2  |

| 1.2  | Features                                                                                            | 3  |

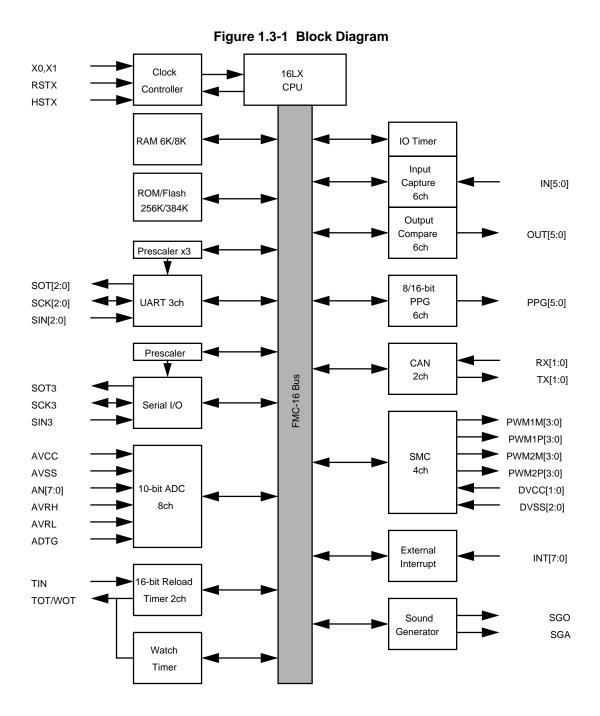

| 1.3  | Block Diagram                                                                                       | 5  |

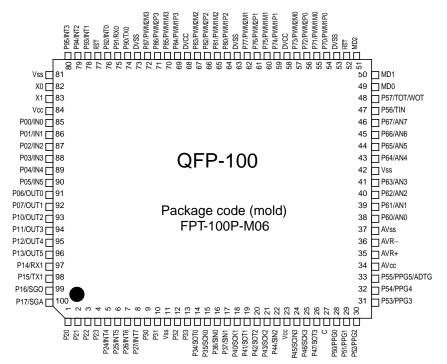

| 1.4  | Pin Assignment                                                                                      | 6  |

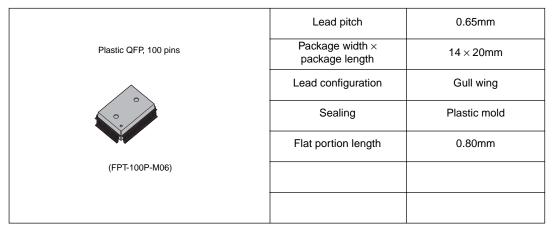

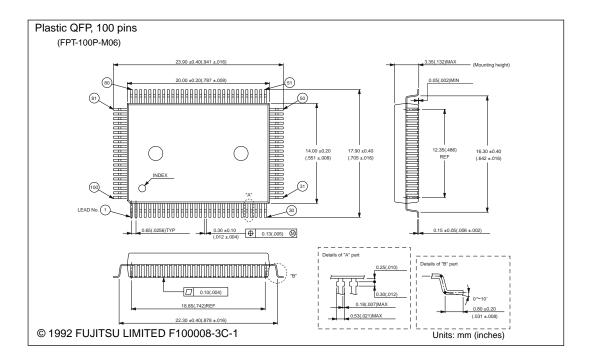

| 1.5  | Package Dimensions                                                                                  |    |

| 1.6  | Pin Functions                                                                                       | 8  |

| 1.7  | Input-Output Circuits                                                                               | 12 |

| 1.8  | Handling the Device                                                                                 | 15 |

| CHAP | TER 2 CPU                                                                                           | 17 |

| 2.1  | Outline of CPU                                                                                      | 18 |

| 2.2  | Memory Space                                                                                        | 19 |

| 2.3  | Memory Space Map                                                                                    | 20 |

| 2.4  | Linear Addressing                                                                                   | 21 |

| 2.5  | Bank Addressing Types                                                                               | 22 |

| 2.6  | Multi-byte Data in Memory Space                                                                     | 24 |

| 2.7  | Registers                                                                                           | 25 |

| 2.7  | .1 Accumulator (A)                                                                                  | 27 |

| 2.7  | .2 User Stack Pointer (USP) and System Stack Pointer (SSP)                                          | 28 |

| 2.7  | ,                                                                                                   |    |

| 2.7  | .4 Program Counter (PC)                                                                             | 32 |

| 2.8  | Register Bank                                                                                       | 33 |

| 2.9  | Prefix Codes                                                                                        | 35 |

| 2.10 | Interrupt Disable Instructions                                                                      | 37 |

| CHAP | TER 3 INTERRUPTS                                                                                    | 39 |

| 3.1  | Outline of Interrupts                                                                               | 40 |

| 3.2  | Interrupt Vector                                                                                    | 43 |

| 3.3  | Interrupt Control Registers (ICR)                                                                   | 44 |

| 3.4  | Interrupt Flow                                                                                      | 47 |

| 3.5  | Hardware Interrupts                                                                                 | 49 |

| 3.5  | .1 Hardware Interrupt Operation                                                                     | 50 |

| 3.5  | .2 Occurrence and Release of Hardware Interrupt                                                     | 51 |

| 3.5  | .3 Multiple interrupts                                                                              | 53 |

| 3.6  | Software Interrupts                                                                                 | 54 |

| 3.7  | Extended Intelligent I/O Service (EI <sup>2</sup> OS)                                               | 56 |

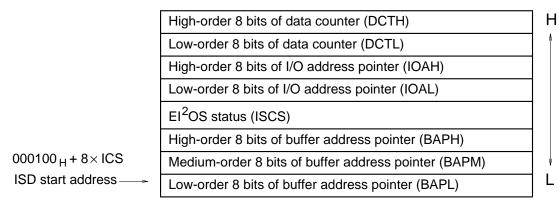

| 3.7  | .1 Extended Intelligent I/O Service Descriptor (ISD)                                                | 58 |

| 3.7  | .2 EI <sup>2</sup> OS Status Register (ISCS)                                                        | 60 |

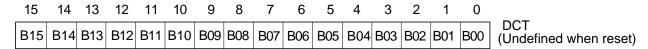

| 3.8  | Operation Flow of and Procedure for Using the Extended Intelligent I/O Service (EI <sup>2</sup> OS) | 61 |

| 3.9  | Exceptions                                                                                          | 64 |

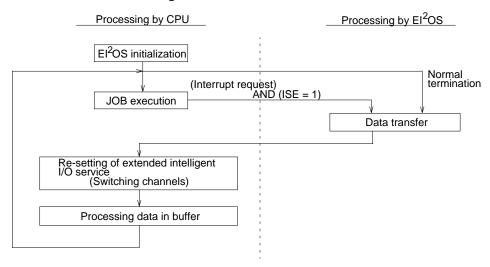

| CHAP | TER 4 DELAYD INTERRUPT                                                                              | 65 |

| _    | Outline of Delayed Interrupt Module                                                                 | 66 |

| 4.2  | Delayed Interrupt Register                  | 67  |

|------|---------------------------------------------|-----|

| 4.3  | Delayed Interrupt Operation                 | 68  |

| СНАЕ | PTER 5 CLOCK AND RESET                      | 69  |

| 5.1  | Clock Generator                             |     |

| 5.2  |                                             |     |

| 5.2  |                                             |     |

| 5.5  | Reset Gauses                                | 73  |

| CHAF | PTER 6 LOW-POWER CONTORL CIRCUIT            | 75  |

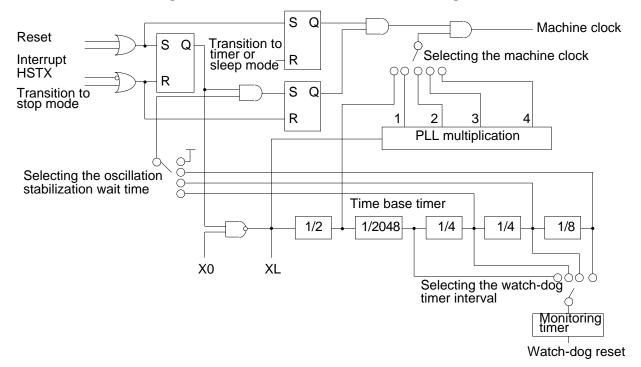

| 6.1  | Outline of Low-Power Control Circuit        | 76  |

| 6.2  | Registers                                   | 78  |

| 6.2  | 2.1 Low Power Mode Control Register (LPMCR) | 79  |

| 6.2  | 2.2 Clock Selection Register (CKSCR)        |     |

| 6.3  | Low-Power Mode Operation                    | 83  |

| 6.3  | 3.1 Sleep Mode                              | 85  |

| 6.3  | 3.2 Timer Mode                              |     |

| 6.3  | 3.3 Stop Mode                               |     |

|      | 3.4 Hardware Standby Mode                   |     |

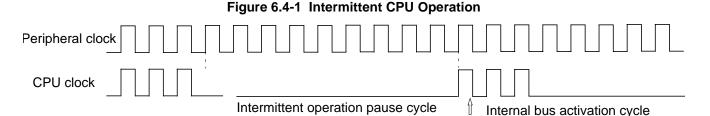

| 6.4  | •                                           |     |

| 6.5  | •                                           |     |

| 6.6  | -                                           |     |

| 0.0  | Status Transition of Glock Gelection        |     |

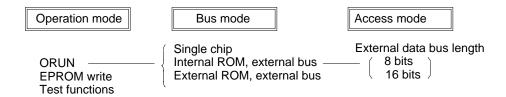

| CHAF | PTER 7 MEMORY ACCESS MODES                  | 93  |

| 7.1  | Outline of Memory Access Modes              | 94  |

| 7.2  | Mode Pins                                   | 95  |

| 7.3  | Mode Data                                   | 96  |

| СНАЕ | PTER 8                                      | aa  |

| 8.1  | I/O Ports                                   |     |

| 8.2  |                                             |     |

| _    |                                             |     |

|      | 2.1 Port Data Register                      |     |

| -    | 2.2 Port Direction Register                 |     |

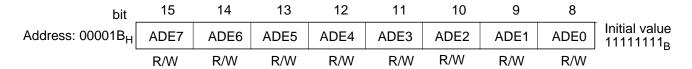

| 8.2  | 2.3 Analog Input Enable Register            | 104 |

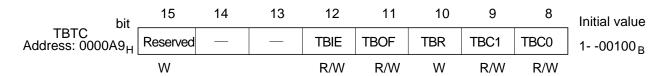

| CHAF | PTER 9 TIME BASE TIMER                      | 105 |

| 9.1  | Outline of Time Base Timer                  | 106 |

| 9.2  |                                             |     |

| 9.3  | -                                           |     |

| 0.0  |                                             |     |

| CHAF | PTER 10 WATCH-DOG TIMER                     | 111 |

| 10.1 |                                             |     |

| 10.2 | 2 Watch-dog Timer Operation                 | 115 |

| СНАБ | PTER 11 16-BIT I/O TIMER                    | 117 |

| 11.1 |                                             |     |

|      |                                             |     |

| 11.2 | - · · · · · · · · · · · · · · · · · · ·     |     |

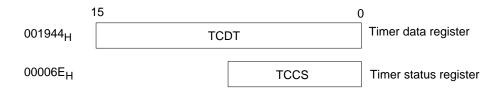

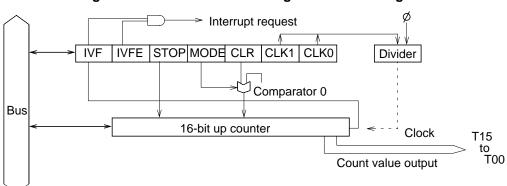

|      | 3 16-bit Free-running Timer                 | 400 |

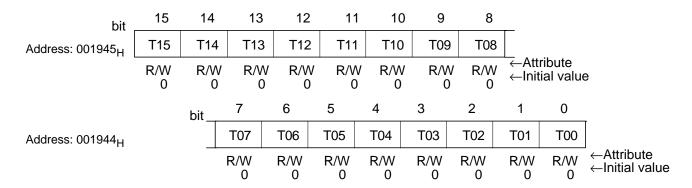

| 1.1  | 1.3.1 Data Register                         | 177 |

| 11.3.2 Control Status Register                                                       | 123 |

|--------------------------------------------------------------------------------------|-----|

| 11.3.3 16-bit Free-running TimerOperation                                            | 125 |

| 11.4 Output Compare                                                                  |     |

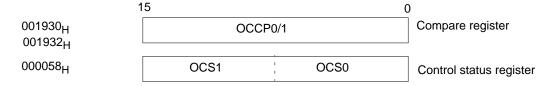

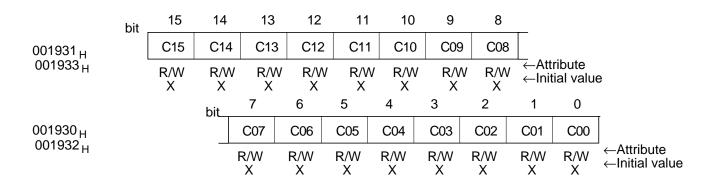

| 11.4.1 Output Compare Register                                                       |     |

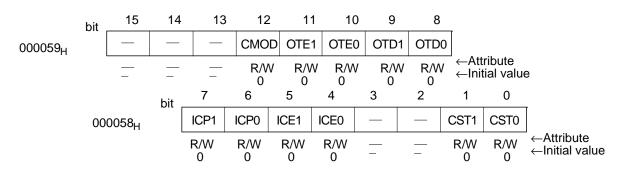

| 11.4.2 Control Status Register of Output Compare                                     |     |

| 11.4.3 16-bit Output Compare Operation                                               |     |

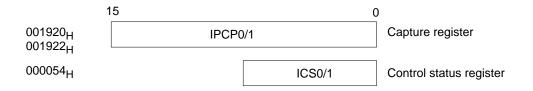

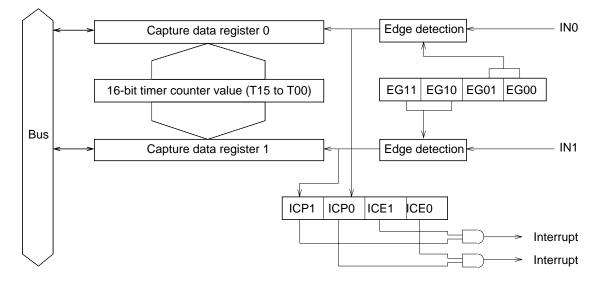

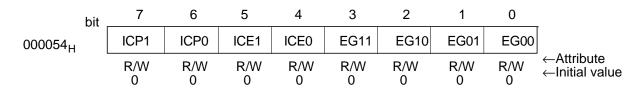

| 11.5 Input Capture                                                                   |     |

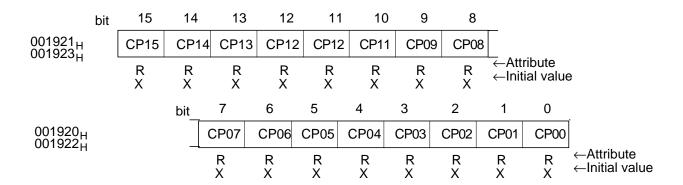

| 11.5.1 Input Capture Register Details                                                |     |

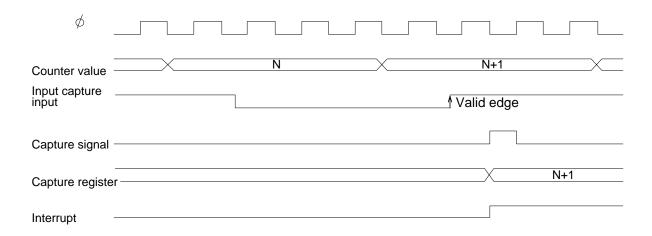

| 11.5.2 16-bit Input Capture Operation                                                |     |

| CHAPTER 12 16-BIT RELOAD TIMER (WITH EVENT COUNT FUNCTION)                           | 141 |

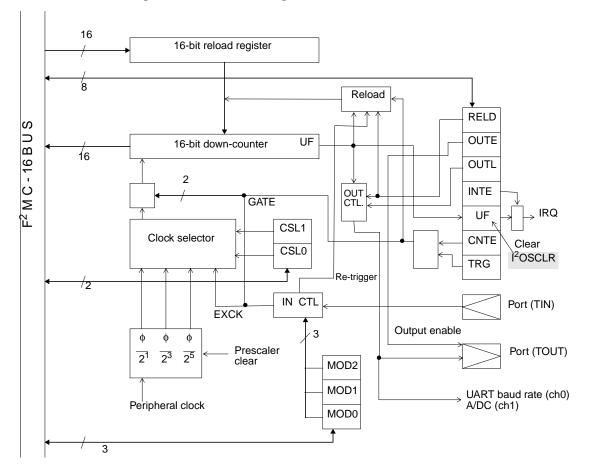

| 12.1 Outline of 16-Bit Reload Timer (with Event Count Function)                      | 142 |

| 12.2 16-Bit Reload Timer (with Event Count Function)                                 | 144 |

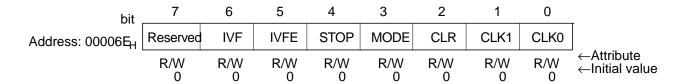

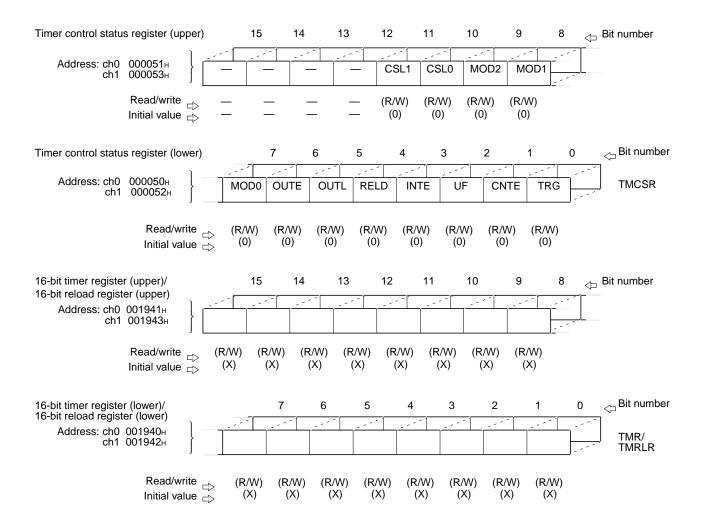

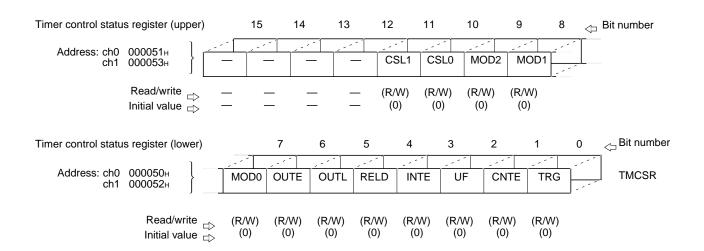

| 12.2.1 Timer Control Status Register (TMCSR)                                         | 145 |

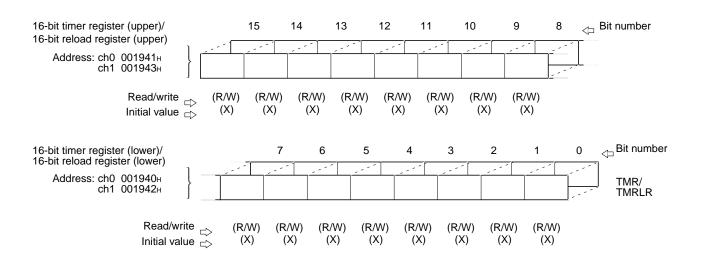

| 12.2.2 Register Layout of 16-bit Timer Register (TMR)/16-bit Reload Register (TMRLR) | 148 |

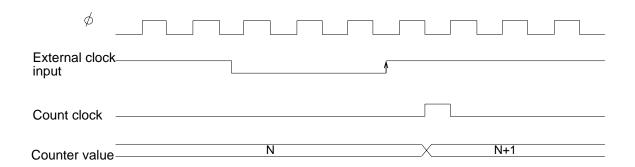

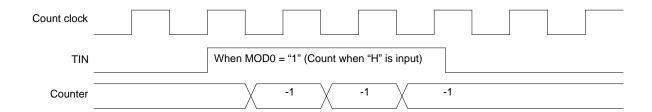

| 12.3 Internal Clock and External Clock Operations of 16-bit Reload Timer             | 149 |

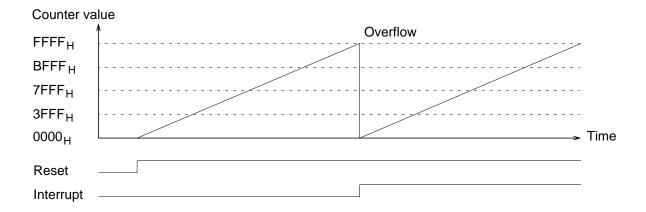

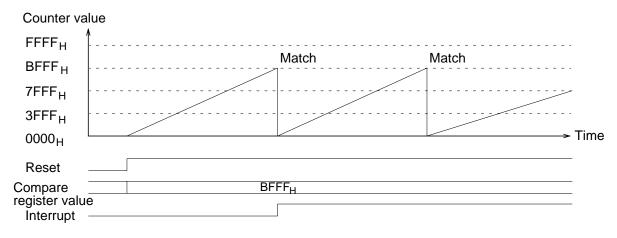

| 12.4 Underflow Operation of 16-bit Reload Timer                                      | 152 |

| 12.5 Output Pin Functions of 16-bit Reload Timer                                     | 153 |

| 12.6 Counter Operation State                                                         | 154 |

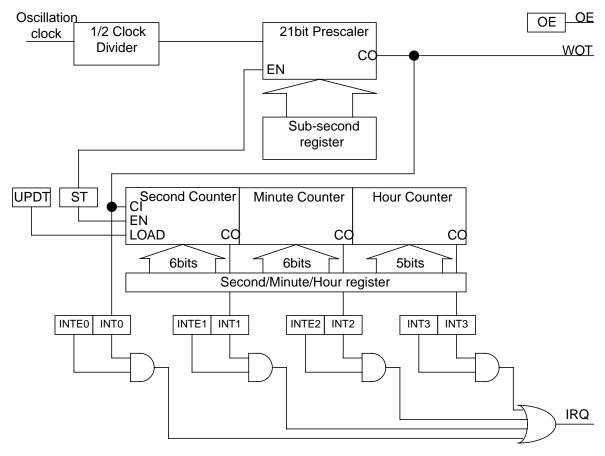

| CHAPTER 13 WATCH-DOG TIMER                                                           | 155 |

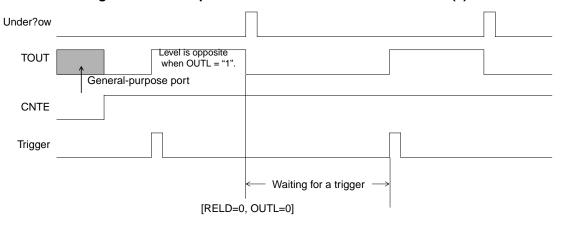

| 13.1 Outline of Watch Timer                                                          | 156 |

| 13.2 Watch-dog Timer Registers                                                       | 157 |

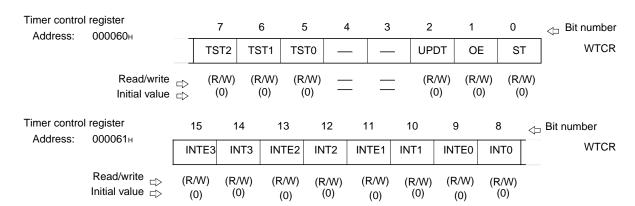

| 13.2.1 Timer Control Register                                                        | 158 |

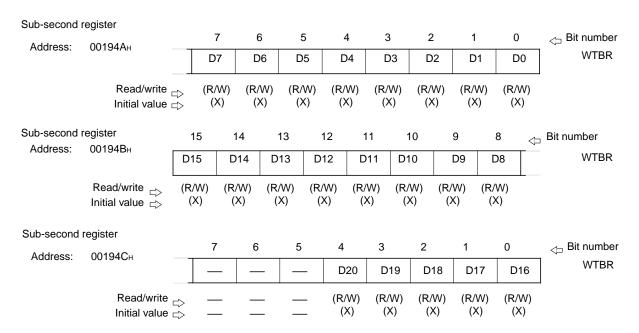

| 13.2.2 Sub-second Registers                                                          | 160 |

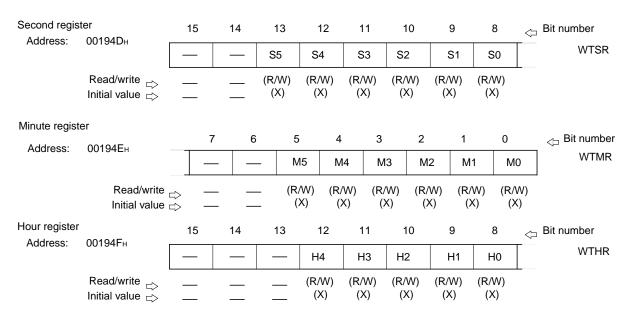

| 13.2.3 Second/Minute/Hour Registers                                                  | 161 |

| CHAPTER 14 8/16-BIT PPG                                                              | 163 |

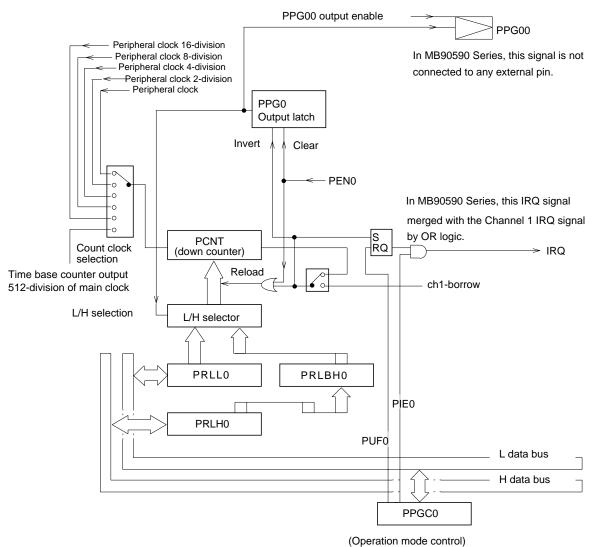

| 14.1 Outline of 8/16-bit PPG                                                         | 164 |

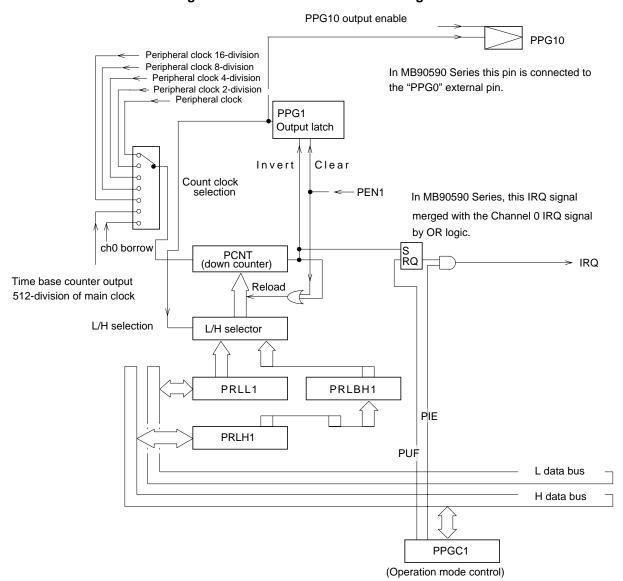

| 14.2 Block Diagram of 8/16-Bit PPG                                                   | 165 |

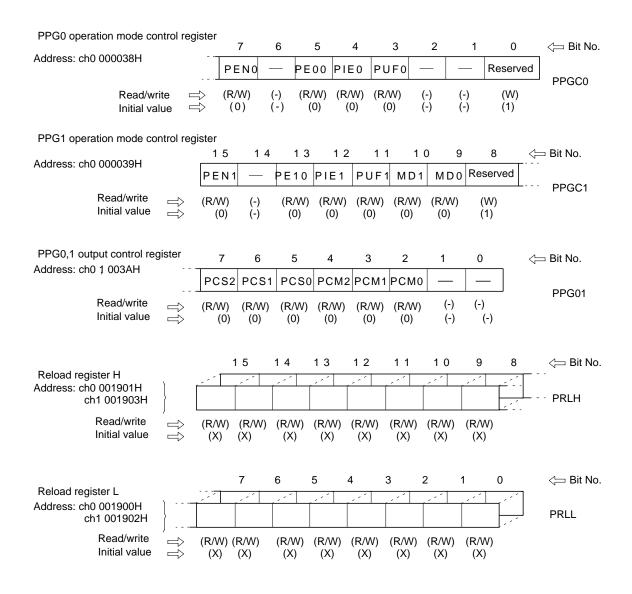

| 14.3 8/16-Bit PPG Registers                                                          | 167 |

| 14.3.1 PPG0 Operation Mode Control Register (PPGC0)                                  | 168 |

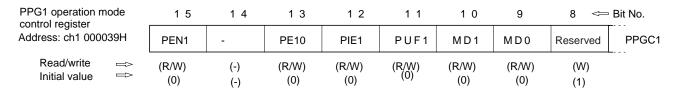

| 14.3.2 PPG1 Operation Mode Control Register (PPGC1)                                  | 170 |

| 14.3.3 PPG0, 1 Output Control Register (PPG01)                                       | 172 |

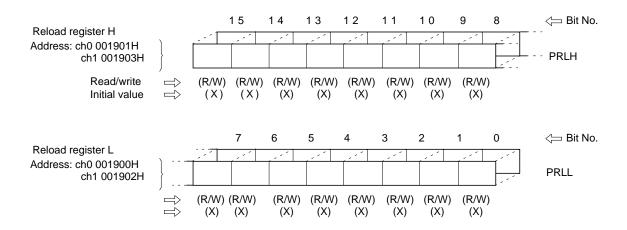

| 14.3.4 Reload Register (PRLL/PRLH)                                                   |     |

| 14.4 Operations of 8/16-bit PPG                                                      |     |

| 14.5 Selecting a Count Clock for 8/16-Bit PPG                                        | 177 |

| 14.6 Controlling Pin Output of 8/16-bit PPG Pulses                                   | 178 |

| 14.7 8/16-bit PPG Interrupts                                                         |     |

| 14.8 Initial Values of 8/16-bit PPG Hardware                                         | 180 |

| CHAPTER 15 DTP/EXTERNAL INTERRUPTS                                                   | 183 |

| 15.1 Outline of DTP/External Interrupts                                              | 184 |

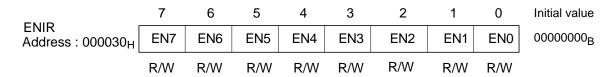

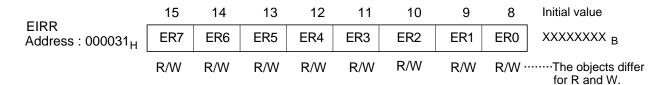

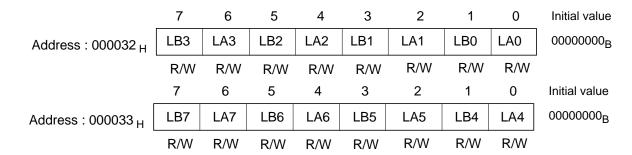

| 15.2 DTP/External Interrupt Registers                                                |     |

| 15.3 Operations of DTP/External Interrupts                                           |     |

| 15.4 Switching between External Interrupt and DTP Requests                           |     |

| 15.5 Notes on Using DTP/External Interrupts                                          |     |

| CHAPTER 16 A/D Converter 19                                          | 93  |

|----------------------------------------------------------------------|-----|

| 16.1 Features of A/D Converter 1                                     | 94  |

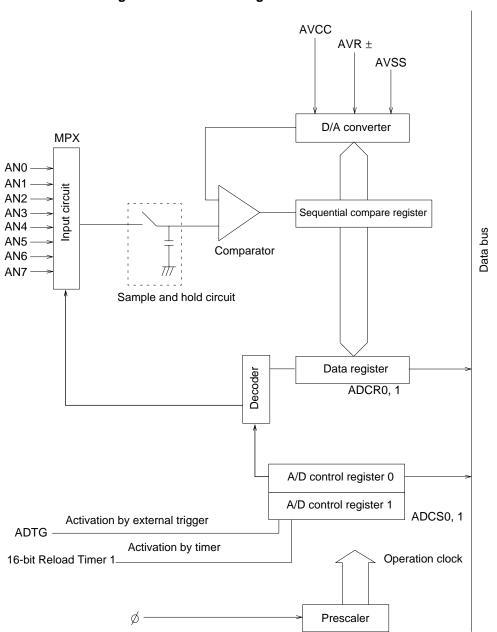

| 16.2 Block Diagram of A/D Converter                                  | 96  |

| 16.3 A/D Converter Registers                                         | 97  |

| 16.3.1 Control Status Registers (ADCS0)                              | 98  |

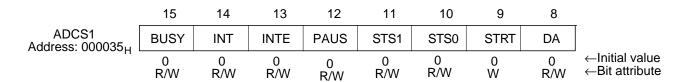

| 16.3.2 Control Status Register (ADCS1)                               | 201 |

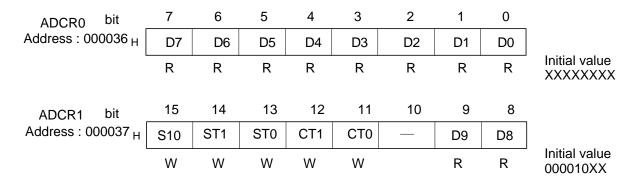

| 16.3.3 Data Registers (ADCR1 and ADCR0)                              | 204 |

| 16.4 Operations of A/D Converter                                     | 206 |

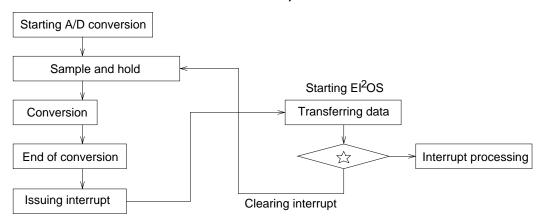

| 16.5 Conversion Using EI <sup>2</sup> OS                             | 208 |

| 16.5.1 Starting EI <sup>2</sup> OS in Single Mode                    | 209 |

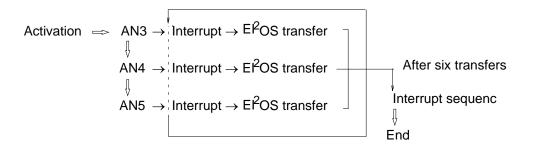

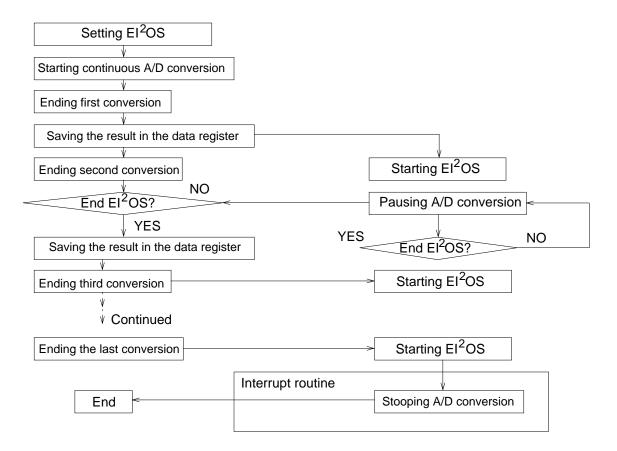

| 16.5.2 Starting EI <sup>2</sup> OS in Continuous Mode                | 211 |

| 16.5.3 Starting EI <sup>2</sup> OS in Stop Mode                      | 213 |

| 16.6 Conversion Data Protection                                      | 215 |

| CHAPTER 17 UART0                                                     | 17  |

| 17.1 Feature of UART0                                                | 218 |

| 17.2 UART Block Diagram                                              | 219 |

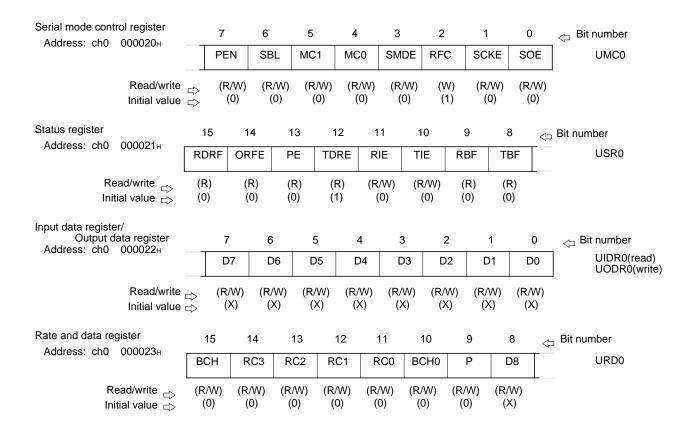

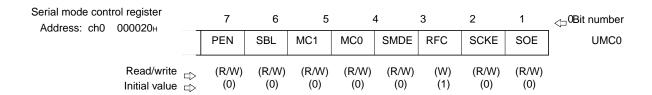

| 17.3 UART Registers                                                  |     |

| 17.3.1 Serial Mode Control Register (UMC)                            |     |

| 17.3.2 Status Register (USR)                                         |     |

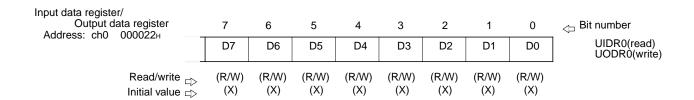

| 17.3.3 Input Data Register (UIDR) and Output Data Register (UODR)    |     |

| 17.3.4 Rate and Data Register (URD)                                  |     |

| 17.4 UARTO Operation                                                 |     |

| 17.5 Baud Rate                                                       |     |

| 17.6 Internal and External Clock                                     |     |

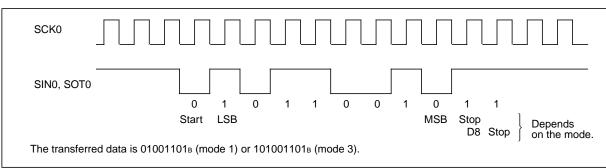

| 17.7 Transfer Data Format                                            |     |

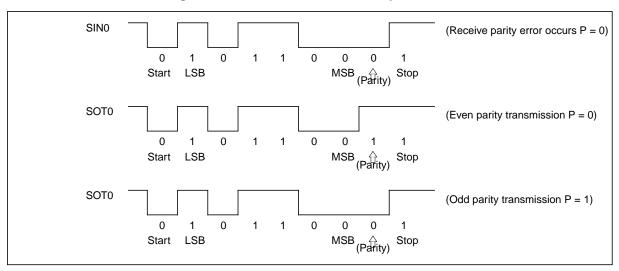

| 17.8 Parity Bit                                                      |     |

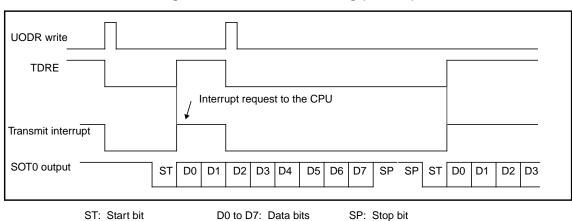

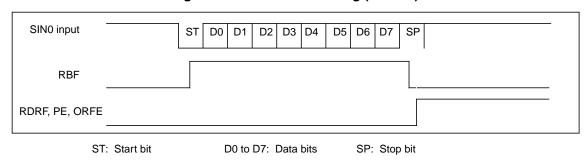

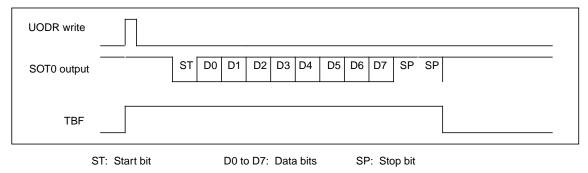

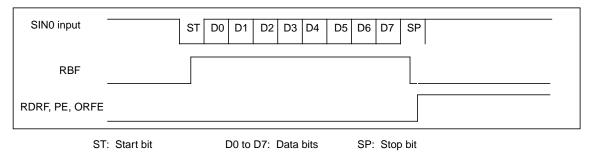

| 17.9 Interrupt Generation and Flag Set Timings                       |     |

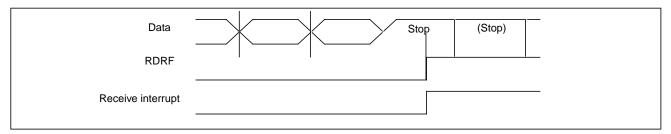

| 17.9.1 Flag Set Timings for a Receive Operation (in Mode 0, 1, or 3) |     |

| 17.9.2 Flag set timings for a receive operation (in mode 2)          |     |

| 17.9.3 Flag set Timings for a Transmit Operation                     |     |

| 17.9.4 Status Flag During Transmit and Receive Operation             |     |

| 17.10 UARTO Application Example                                      |     |

| CHAPTER 18 SERIAL I/O                                                | 43  |

| 18.1 Outline of Serial I/O                                           |     |

| 18.2 Serial I/O Registers                                            |     |

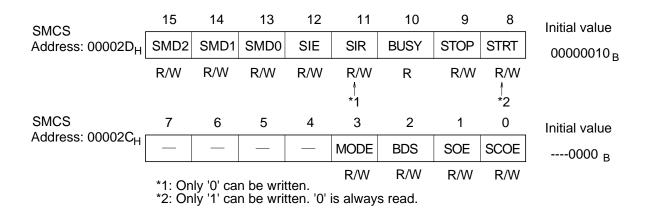

| 18.2.1 Serial Mode Control Status Register (SMCS)                    |     |

| 18.2.2 Serial Shift Data Register (SDR)                              |     |

| 18.3 Serial I/O Prescaler (CDCR)                                     |     |

| 18.4 Serial I/O Operation                                            |     |

| 18.4.1 Shift Clock2                                                  |     |

| 18.4.2 Serial I/O Operation                                          |     |

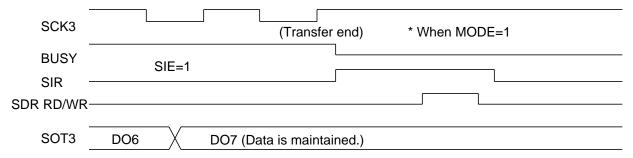

| 18.4.3 Shift Operation Start/Stop Timing                             |     |

| 18.4.4 Interrupt Function of the Extended Serial I/O Interface       |     |

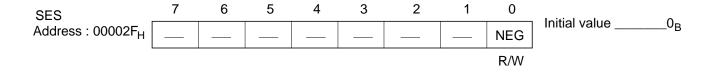

| 18.5 Negative Clock Operation                                        |     |

|                                                                      | 61  |

| 262        |

|------------|

| 263        |

| 264        |

| 266        |

| 269        |

| 273        |

| 274        |

| 277        |

| 278        |

| 280        |

| 281        |

| 283        |

| 284        |

| 285        |

| 286        |

| 287        |

| 288        |

| 289        |

| 290        |

| 291        |

| 292        |

| 293        |

| 294        |

| 295        |

| 297        |

| 299        |

| 300        |

| 302        |

| 303        |

| 305        |

| 307        |

| 310        |

| 311        |

| 313        |

| 315        |

| 317        |

| 319        |

| 320        |

| 320        |

| 321        |

| 322        |

| 323<br>324 |

| 324        |

| 327        |

| 328        |

| 329        |

| 330        |

|            |

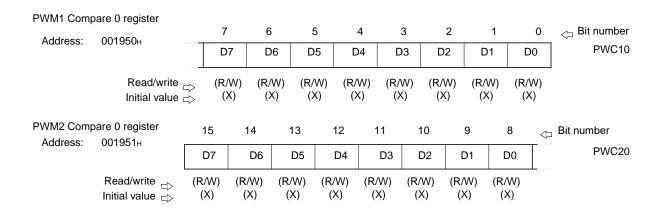

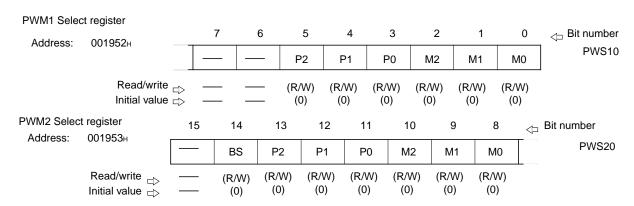

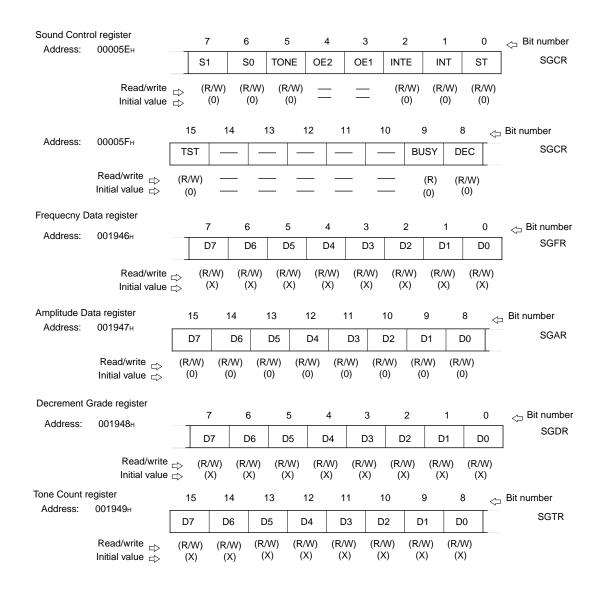

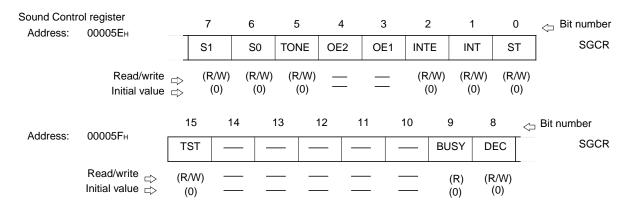

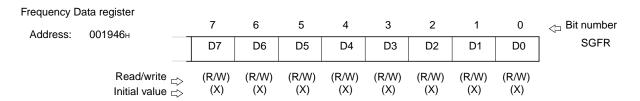

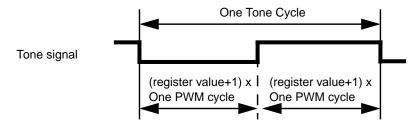

| 21.2.2 Frequency Data register                                              | 332                   |

|-----------------------------------------------------------------------------|-----------------------|

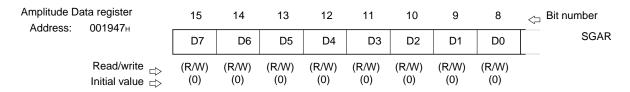

| 21.2.3 Amplitude Data Register                                              | 333                   |

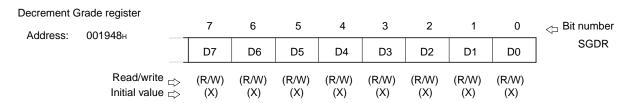

| 21.2.4 Decrement Grade Register                                             | 334                   |

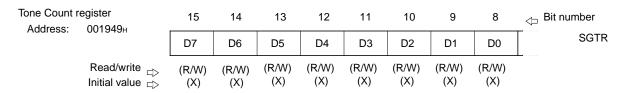

| 21.2.5 Tone Count Register                                                  | 335                   |

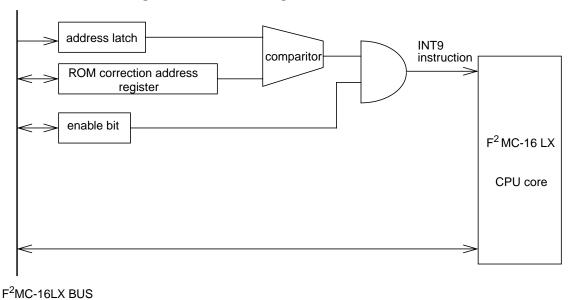

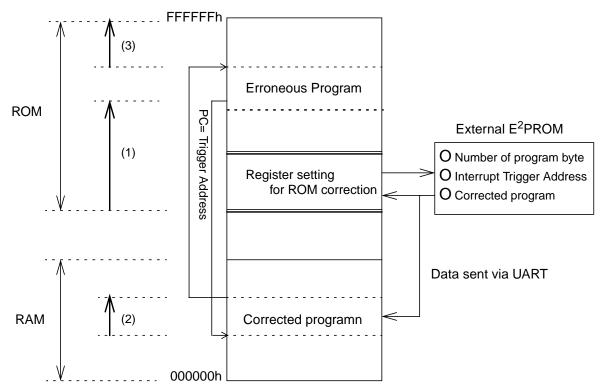

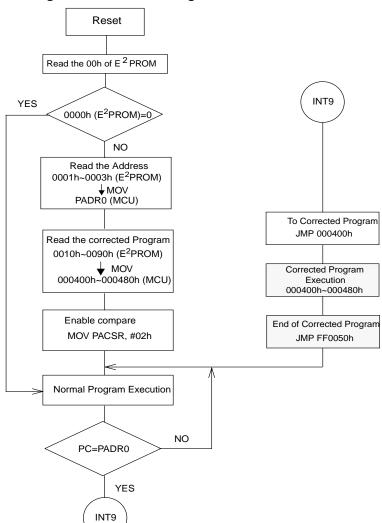

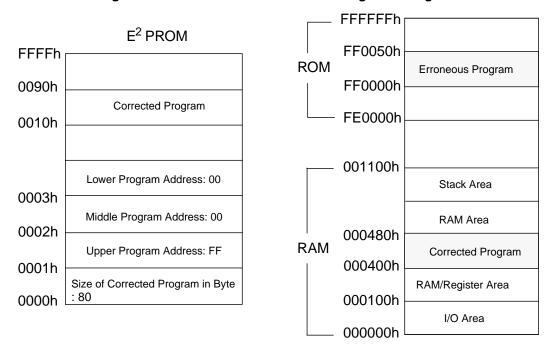

| CHAPTER 22 ROM CORRECTION                                                   | 337                   |

| 22.1 Outline of ROM Correction                                              | 338                   |

| 22.2 Application Example of ROM Correction                                  |                       |

| 22.2.1 Correction Example of Program Errors                                 | 341                   |

| 22.2.2 Example of Correction Processing                                     | 342                   |

| CHAPTER 23 ROM MIRRORING MODULE                                             | 345                   |

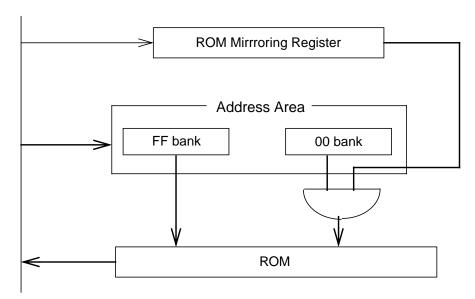

| 23.1 Outline of ROM Mirroring Module                                        | 346                   |

| 23.2 ROM Mirroring Register (ROMM)                                          | 347                   |

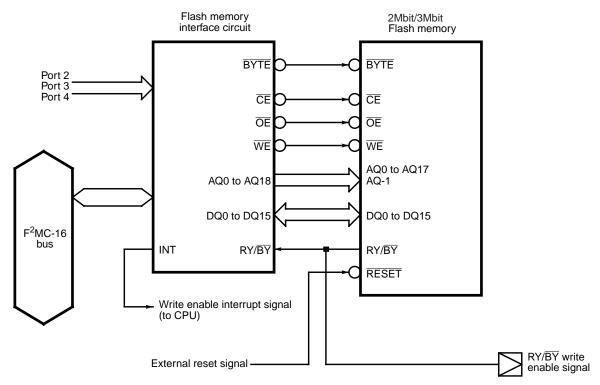

| CHAPTER 24 2M/3M-BIT FLASH MEMORY                                           | 349                   |

| 24.1 Outline of 2M/3M-Bit Flash Memory                                      | 350                   |

| 24.2 Block Diagram of the Entire Flash Memory and Sector Configuration of t |                       |

| 24.3 Write/Erase Modes                                                      | 353                   |

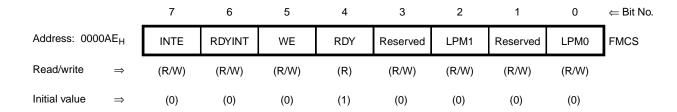

| 24.4 Flash Memory Control Status Register (FMCS)                            | 355                   |

| 24.5 Starting the Flash Memory Automatic Algorithm                          | 357                   |

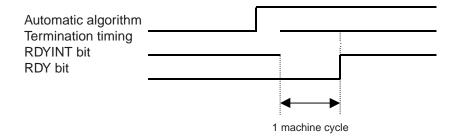

| 24.6 Confirming the Automatic Algorithm Execution State                     | 358                   |

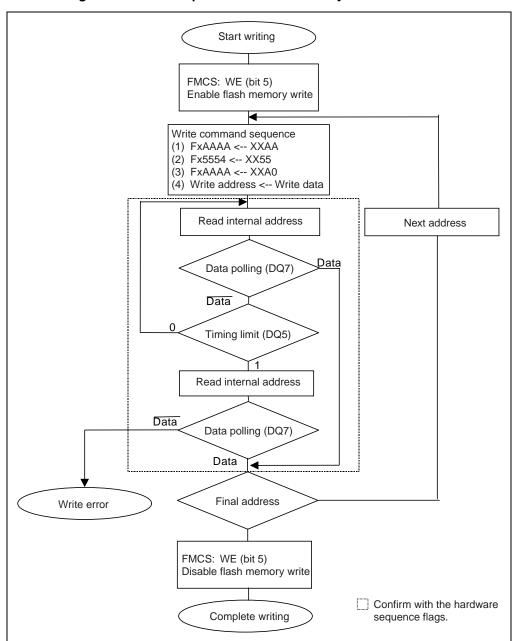

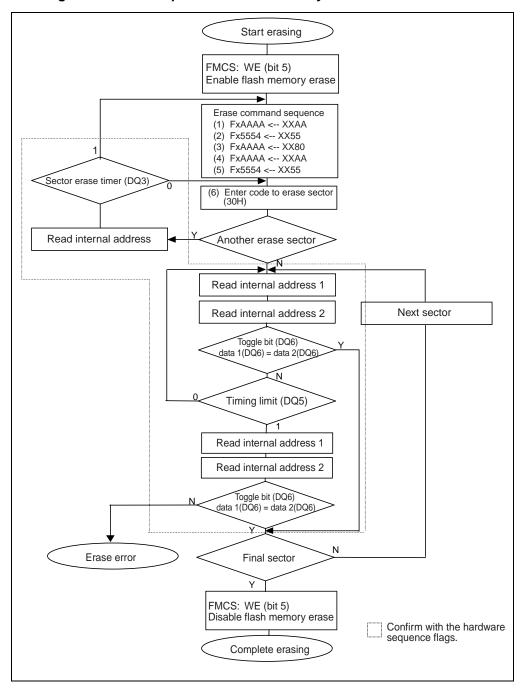

| 24.6.1 Data Polling Flag (DQ7)                                              | 360                   |

| 24.6.2 Toggle Bit Flag (DQ6)                                                | 362                   |

| 24.6.3 Timing Limit Exceeded Flag (DQ5)                                     | 363                   |

| 24.6.4 Sector Erase Timer Flag (DQ3)                                        | 364                   |

| 24.7 Detailed Explanation of Writing to and Erasing Flash Memory            |                       |

| 24.7.1 Setting The Read/Reset State                                         | 366                   |

| 24.7.2 Writing Data                                                         | 367                   |

| 24.7.3 Erasing All Data (Erasing Chips)                                     | 369                   |

| 24.7.4 Erasing Optional Data (Erasing Sectors)                              | 370                   |

| 24.7.5 Suspending Sector Erase                                              | 372                   |

| 24.7.6 Restarting Sector Erase                                              |                       |

| 24.8 Notes on using 2M-Bit Flash Memory                                     | 374                   |

| 24.9 Reset Vector Address in Flash Memory                                   | 376                   |

| 24.10 Example of Programming 2M/3M-Bit Flash Memory                         | 377                   |

| CHAPTER 25 EXAMPLES OF F2MC-16LX MB90F591/MB90F59                           | 4A SERIAL WRITE       |

| CONNECTION                                                                  | 381                   |

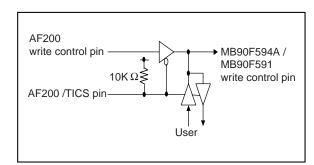

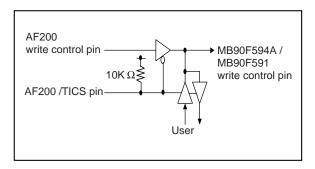

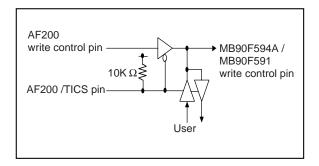

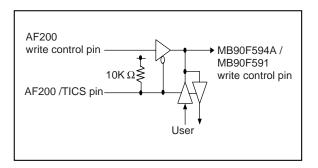

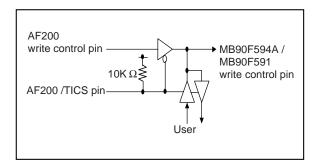

| 25.1 Basic Configuration of F2MC-16LX MB90F591/MB90F594A Serial Write       | Connection 382        |

| 25.2 Example of Serial Write Connection (User Power Supply Used)            | 385                   |

| 25.3 Example of Serial Write Connection (Power Supplied from the Writer)    | 387                   |

| 25.4 Example of Minimum Connection to the Flash Microcomputer Programm      | er (User Power Supply |

| Used)                                                                       | 389                   |

| 25.5 Example of Minimum Connection to the Flash Microcomputer Programm      |                       |

| Writer)                                                                     | 391                   |

| APPENI  | DIX                                         | 393 |

|---------|---------------------------------------------|-----|

| APPEN   | NDIX A I/O Maps                             | 394 |

| APPEN   | NDIX B INSTRUCTIONS                         | 404 |

| B.1     | Instruction Types                           | 405 |

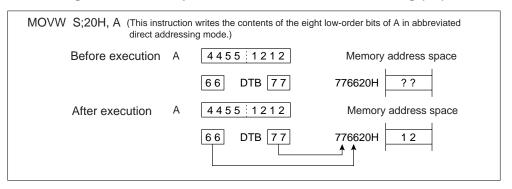

| B.2     | Addressing                                  | 406 |

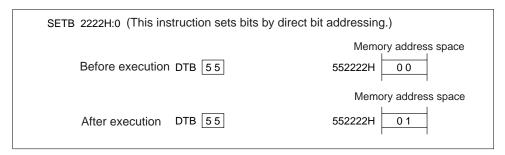

| B.3     | Direct Addressing                           | 408 |

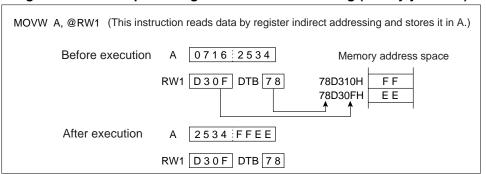

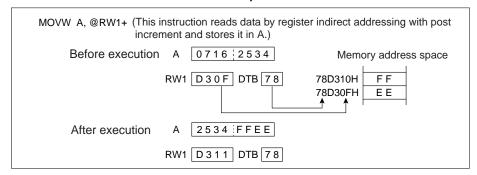

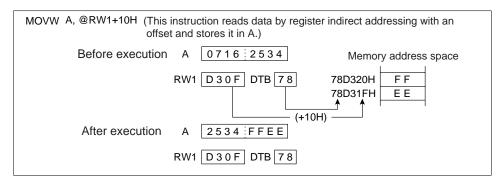

| B.4     | Indirect Addressing                         | 413 |

| B.5     | Execution Cycle Count                       |     |

| B.6     | Effective Address Field                     |     |

| B.7     | How to Read the Instruction List            |     |

| B.8     | F2MC-16LX Instruction List                  |     |

| B.9     | Instruction Map                             | 438 |

| APPEN   | NDIX C Timing Diagrams in Flash Memory Mode | 460 |

| APPEN   | NDIX D List of MB90590 Interrupt Vectors    | 465 |

| INDEX . |                                             | 469 |

# **FIGURES**

| Figure 1.3-1  | Block Diagram                                                         | 5  |

|---------------|-----------------------------------------------------------------------|----|

| Figure 1.4-1  | Pin Assignment                                                        | 6  |

| Figure 1.5-1  | Package Dimensions                                                    | 7  |

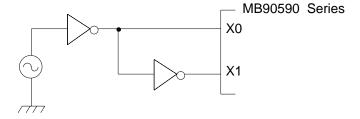

| Figure 1.8-1  | Using External Clock                                                  | 15 |

| Figure 1.8-2  | Power Supply Pins (Vcc/Vss)                                           | 16 |

| Figure 2.2-1  | Sample Relationship between F2MC-16LX System and Memory Map           | 19 |

| Figure 2.3-1  | Memory Space Map                                                      | 20 |

| Figure 2.4-1  | Example of Linear Method (24-bit Register Operand Specification)      | 21 |

| Figure 2.4-2  | Example of Linear Method (32-bit Register Indirect Specification)     | 21 |

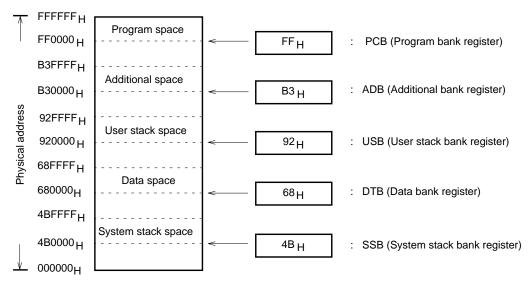

| Figure 2.5-1  | Physical Addresses of Each Space                                      | 23 |

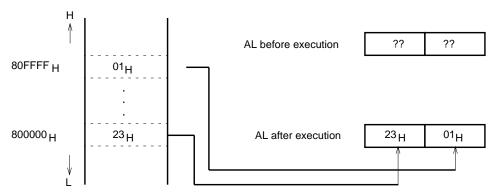

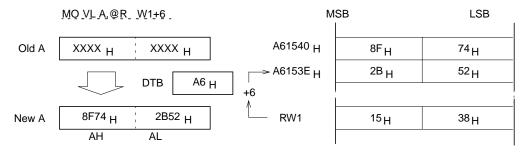

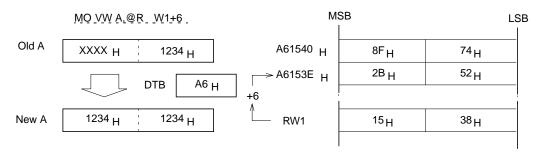

| Figure 2.6-1  | Sample Allocation of Multi-byte Data in Memory                        | 24 |

| Figure 2.6-2  | Execution of MOVW A, 080FFFFH                                         | 24 |

| Figure 2.7-1  | Special Registers                                                     | 26 |

| Figure 2.7-2  | General-purpose Registers                                             | 26 |

| Figure 2.7-3  | 32-bit Data Transfer                                                  | 27 |

| Figure 2.7-4  | AL-AH Transfer                                                        | 27 |

| Figure 2.7-5  | Stack Manipulation Instruction and Stack Pointer                      | 28 |

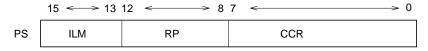

| Figure 2.7-6  | Processor Status (PS) Structure                                       | 29 |

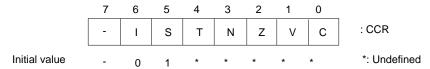

| Figure 2.7-7  | Condition Code Register (CCR) Configuration                           | 29 |

| Figure 2.7-8  | Register Bank Pointer (RP)                                            | 30 |

| Figure 2.7-9  | Interrupt Level Register (ILM)                                        | 30 |

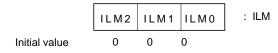

| Figure 2.7-10 | Program Counter                                                       | 32 |

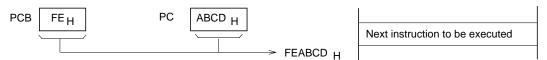

| Figure 2.8-1  | Generating a Physical address in Direct Addressing Mode               | 34 |

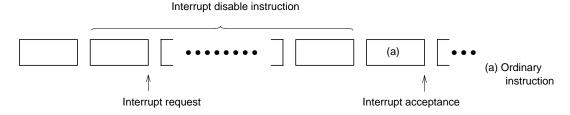

| Figure 2.10-1 | Interrupt Disable Instruction                                         | 37 |

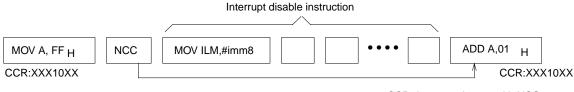

| Figure 2.10-2 | Interrupt Disable Instructions and Prefix Codes                       | 37 |

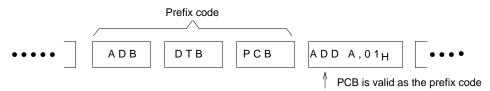

| Figure 2.10-3 | Consecutive Prefix Codes                                              | 37 |

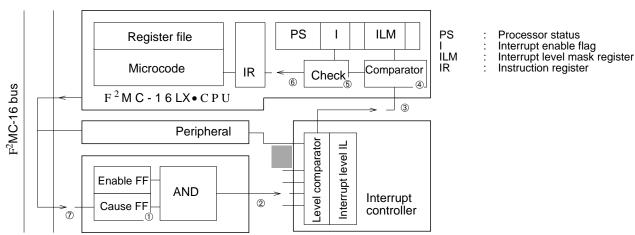

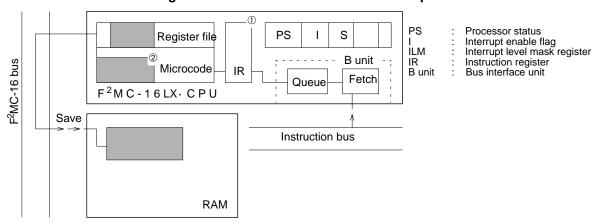

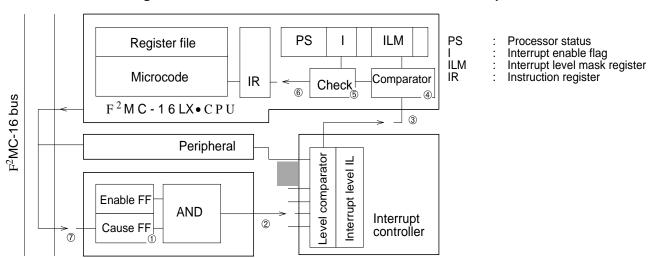

| Figure 3.1-1  | Overview of Hardware Interrupts                                       | 40 |

| Figure 3.1-2  | Overview of Software Interrupts                                       | 41 |

| Figure 3.1-3  | Overview of the Extended Intelligent I/O Service (EI <sup>2</sup> OS) | 42 |

| Figure 3.3-1  | Interrupt Control Register (ICR)                                      | 44 |

| Figure 3.4-1  | Interrupt Flow                                                        | 47 |

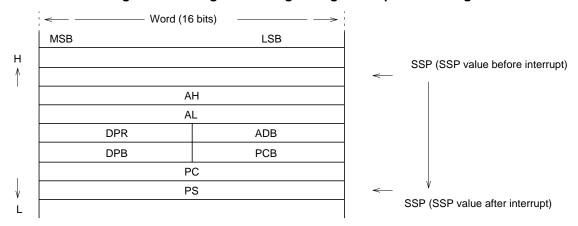

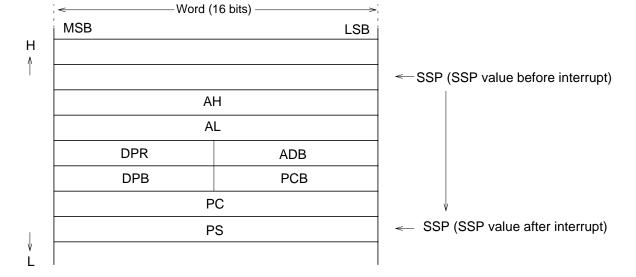

| Figure 3.4-2  | Register Saving during Interrupt Processing                           | 48 |

| Figure 3.5-1  | Occurrence and Release of Hardware Interrup                           | 51 |

| Figure 3.5-2  | Registers Saved in Stack                                              | 53 |

| Figure 3.6-1  | Occurrence and Release of Software Interrupt                          | 55 |

| Figure 3.7-1  | Outline of Extended Intelligent I/O Service                                              | 57  |

|---------------|------------------------------------------------------------------------------------------|-----|

| Figure 3.7-2  | Extended Intelligent I/O Service Descriptor Configuration                                | 58  |

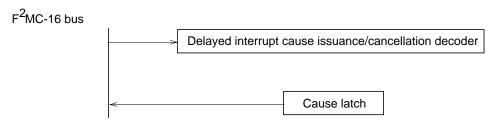

| Figure 3.7-3  | Data Counter Configuration                                                               | 58  |

| Figure 3.7-4  | I/O Register Address Pointer Configuration                                               | 59  |

| Figure 3.7-5  | ISCS Configuration                                                                       | 60  |

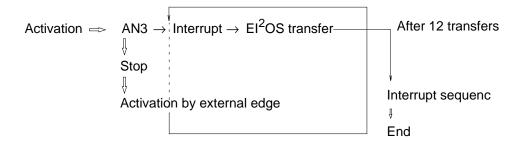

| Figure 3.8-1  | EI <sup>2</sup> OS Operation Flow                                                        | 61  |

| Figure 3.8-2  | El <sup>2</sup> OS Use Flow                                                              | 62  |

| Figure 4.1-1  | Block Diagram                                                                            | 66  |

| Figure 4.3-1  | Delayed Interrupt Issuance                                                               | 68  |

| Figure 5.1-1  | Clock Generator Circuit Block Diagram                                                    | 70  |

| Figure 5.2-1  | Source and Destination of Reset Vector and Mode Data                                     | 72  |

| Figure 5.3-1  | Reset Cause bit Block Diagram                                                            | 74  |

| Figure 5.3-2  | WDTC (Watch-Dog Timer Control) Register                                                  | 74  |

| Figure 6.1-1  | Low-power Control Circuit and Clock Generator                                            | 77  |

| Figure 6.4-1  | Intermittent CPU Operation                                                               | 90  |

| Figure 6.6-1  | Status Transition of Clock Selection                                                     | 92  |

| Figure 7.3-1  | Mode Data Structure                                                                      | 96  |

| Figure 7.3-2  | Access Areas and Physical Addresses in each Bus Mode                                     | 97  |

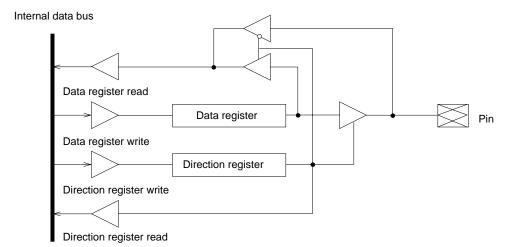

| Figure 8.1-1  | I/O Port Block Diagram                                                                   | 100 |

| Figure 8.2-1  | I/O Port Registers                                                                       | 101 |

| Figure 8.2-2  | Port Data Registers                                                                      | 102 |

| Figure 8.2-3  | Port Direction Registers                                                                 | 103 |

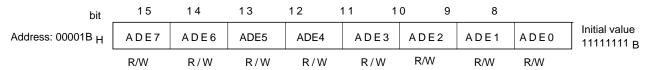

| Figure 8.2-4  | Analog Input Enable Register                                                             | 104 |

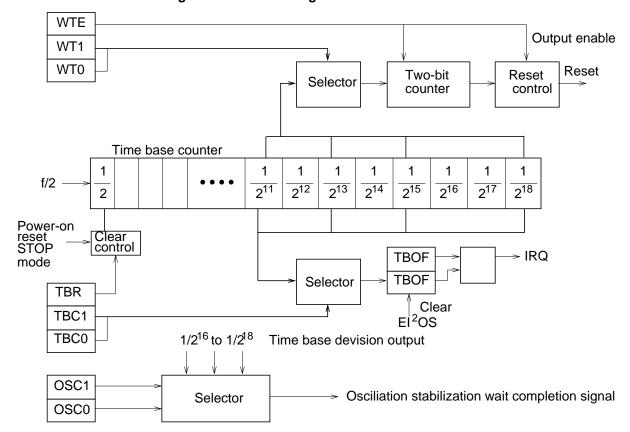

| Figure 9.1-1  | Block Diagram of Time Base Timer                                                         | 106 |

| Figure 10.1-1 | Watch-dog Timer Block Diagram                                                            | 112 |

| Figure 10.2-1 | Watch-dog Timer Operation                                                                | 115 |

| Figure 11.1-1 | Block Diagram of 16-bit I/O Timer                                                        | 119 |

| Figure 11.3-1 | 16-bit Free-running Timer Block Diagram                                                  | 121 |

| Figure 11.4-1 | Output Compare Block Diagram                                                             | 127 |

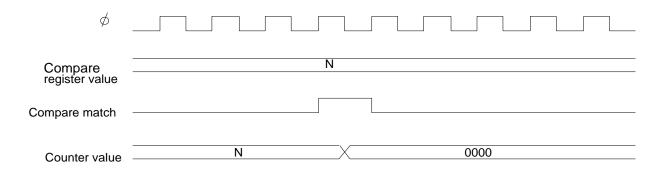

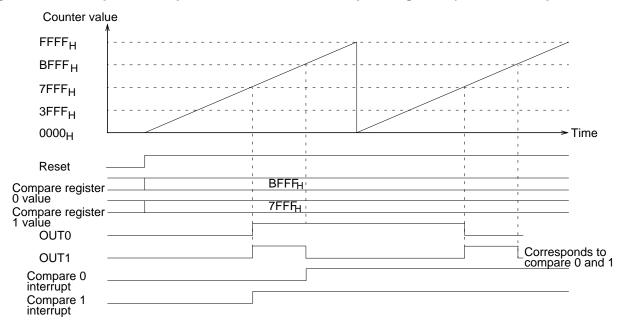

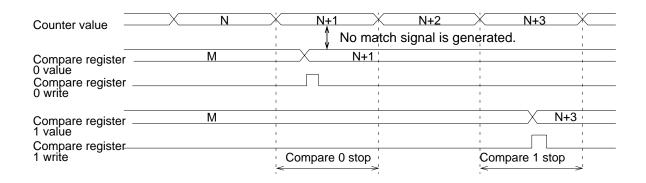

| Figure 11.4-2 | Sample of Output Waveform when Compare Registers 0 and 1 are Used                        | 132 |

| Figure 11.4-3 | Sample of a Output Waveform with Two Compare Registers (The Initial Output Value is '0') | 133 |

| Figure 11.5-1 | Input Capture Block Diagram                                                              | 135 |

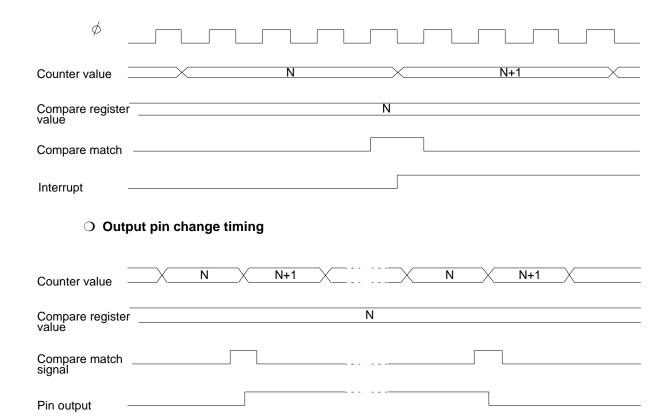

| Figure 11.5-2 | Sample of Input Capture Fetch Timing                                                     | 138 |

| Figure 12.1-1 | Block Diagram of 16-bit Reload Timer                                                     | 143 |

| Figure 12.3-1 | Activation and Operation of 16-bit Reload Timer Counter                                  | 149 |

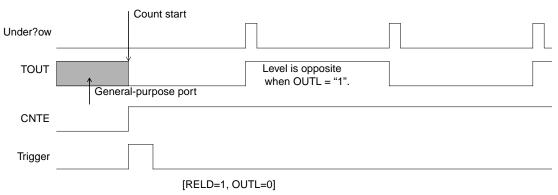

| Figure 12.3-2 | Trigger Input Operation of 16-bit Reload Timer                                           | 150 |

| Figure 12.3-3 | Gate Input Operation of 16-bit Reload Timer                                              | 150 |

| Figure 12.4-1 | Underflow Operation of 16-bit Reload Timer                                               | 152 |

| Figure 12.5-1  | Output Pin Function of 16-bit Reload Timer (1)                                                 | . 153 |

|----------------|------------------------------------------------------------------------------------------------|-------|

| Figure 12.5-2  | Output Pin Function of 16-bit Reload Timer (2)                                                 | . 153 |

| Figure 12.6-1  | Counter State Transitions                                                                      | . 154 |

| Figure 13.1-1  | Block Diagram of Watch-dog Timer                                                               | . 156 |

| Figure 14.2-1  | 8-bit PPG ch0 Block Diagram                                                                    | . 165 |

| Figure 14.2-2  | 8-bit PPG ch1 Block Diagram                                                                    | . 166 |

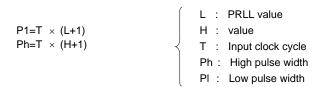

| Figure 14.4-1  | PPG Output Operation, Output Waveform                                                          | . 176 |

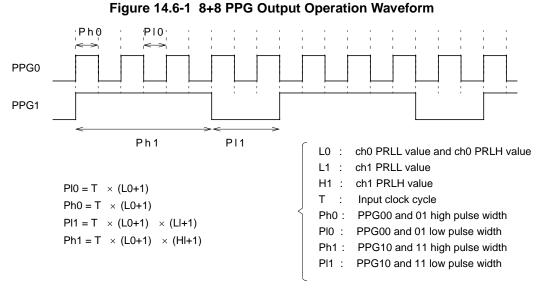

| Figure 14.6-1  | 8+8 PPG Output Operation Waveform                                                              | . 178 |

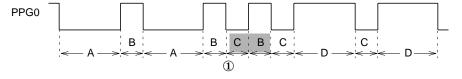

| Figure 14.8-1  | Write Timing for 8/16-bit PPG Reload Registers (PRLL and PRLH)                                 | . 180 |

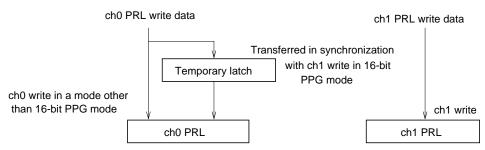

| Figure 14.8-2  | PRL Write Operation Block Diagram                                                              | . 181 |

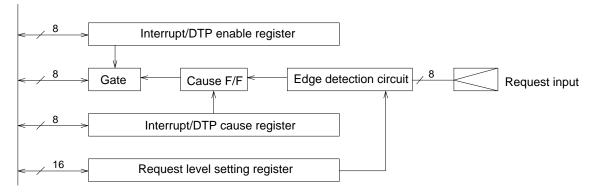

| Figure 15.1-1  | Block Diagram of DTP/External Interrupts                                                       | . 184 |

| Figure 15.3-1  | External Interrupt                                                                             | . 188 |

| Figure 15.3-2  | Timing to Cancel the External Interrupt at the End of DTP Operation                            | . 189 |

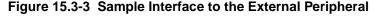

| Figure 15.3-3  | Sample Interface to the External Peripheral                                                    | . 189 |

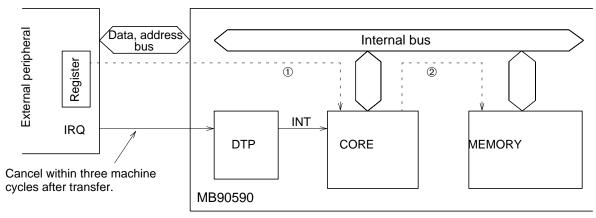

| Figure 15.4-1  | Switching Between External Interrupt and DTP Requests                                          | . 190 |

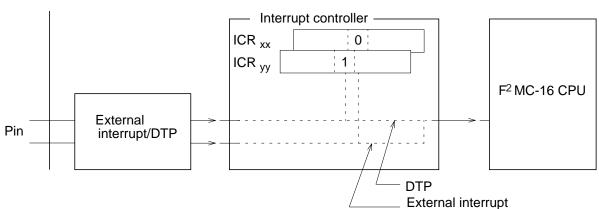

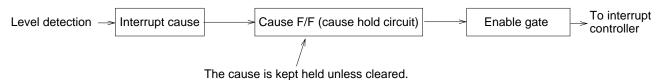

| Figure 15.5-1  | Clearing the Cause Hold Circuit Upon Level Set                                                 | . 192 |

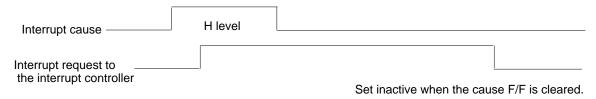

| Figure 15.5-2  | Interrupt Cause and Interrupt Request to the Interrupt Controller While Interrupts are Enabled | . 192 |

| Figure 16.2-1  | Block Diagram of A/D Converter                                                                 | . 196 |

| Figure 16.3-1  | A/D Converter Register Configuration                                                           | . 197 |

| Figure 16.5-1  | A/D conversion processing flow from the start to converted data transfer (in continuous mode)  | . 208 |

| Figure 17.2-1  | UART Block Diagram                                                                             | . 219 |

| Figure 17.7-1  | Transfer Data Format                                                                           | . 233 |

| Figure 17.8-1  | Serial Data with Parity Enabled                                                                | . 234 |

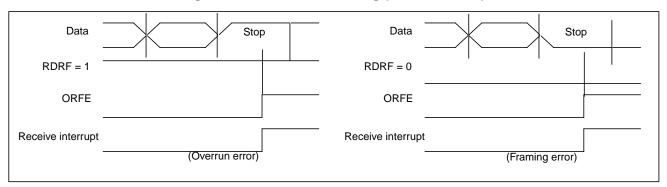

| Figure 17.9-1  | RDRF Set Timing (Mode 0, 1, or 3)                                                              | . 236 |

| Figure 17.9-2  | ORFE Set Timing (Mode 0, 1, or 3)                                                              | . 236 |

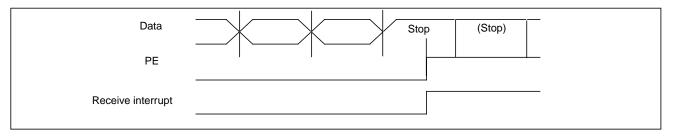

| Figure 17.9-3  | PE Set Timing (Mode 0, 1, or 3)                                                                | . 236 |

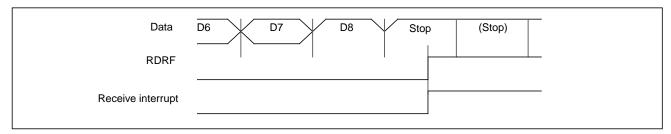

| Figure 17.9-4  | RDRF Set Timing (Mode 2)                                                                       | . 237 |

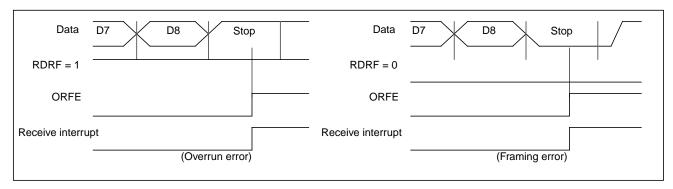

| Figure 17.9-5  | ORFE Set Timing (Mode 2)                                                                       | . 237 |

| Figure 17.9-6  | TDRE Set Timing (Mode 0)                                                                       | . 238 |

| Figure 17.9-7  | RBF Set Timing (Mode 0)                                                                        | . 239 |

| Figure 17.9-8  | TBF Set Timing (Mode 0)                                                                        | . 239 |

| Figure 17.10-1 | RBF Set Timing (mode 0)                                                                        | . 241 |

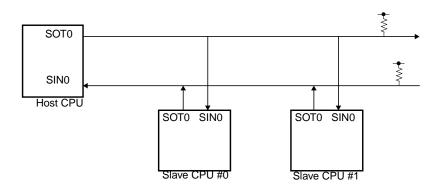

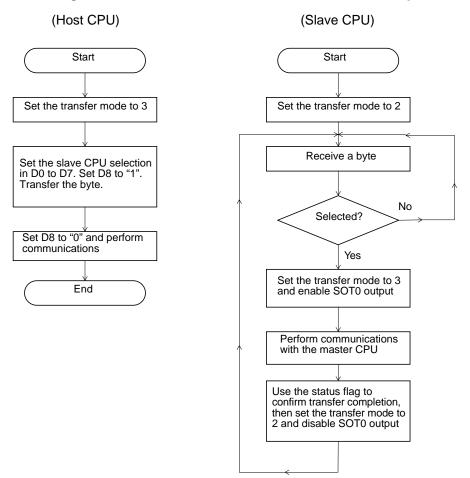

| Figure 17.10-2 | Example System Configuration Using Mode 2                                                      | . 241 |

| Figure 17.10-3 | Communication Flowchart for Mode 2 Operation                                                   | . 242 |

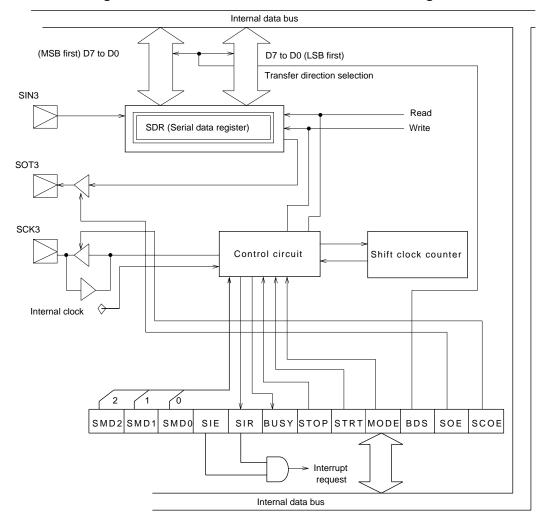

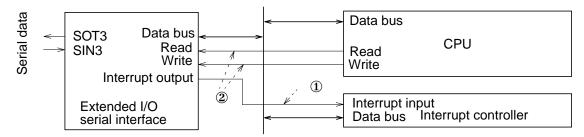

| Figure 18.1-1  | Extended Serial I/O Interface Block Diagram                                                    | . 244 |

| Figure 18.4-1  | Extended I/O Serial Interface Operation Transitions                                            | . 255 |

| Figure 18.4-2  | Serial Data Register Read/write                                                                | . 255 |

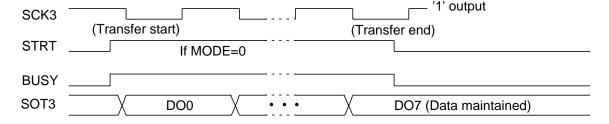

| Figure 18.4-3  | Shift Operation Start/Stop Timing (Internal Clock)                                                               |     |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------|-----|--|--|--|

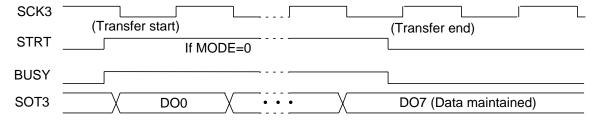

| Figure 18.4-4  | Shift Operation Start/Stop Timing (External Clock)                                                               |     |  |  |  |

| Figure 18.4-5  | Shift Operation Start/Stop Timing (External Shift Clock Mode with Instruction Shift)                             | 257 |  |  |  |

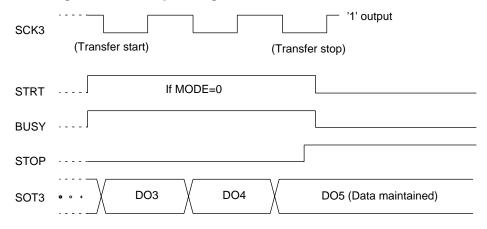

| Figure 18.4-6  | Stop Timing when '1' is Written to the STOP Bit                                                                  | 257 |  |  |  |

| Figure 18.4-7  | Serial Data I/O Shift Timing                                                                                     | 257 |  |  |  |

| Figure 18.4-8  | Interrupt Signal Output Timing of the Extended Serial I/O Interface                                              | 258 |  |  |  |

| Figure 19.2-1  | Block Diagram of CAN Controller                                                                                  | 263 |  |  |  |

| Figure 19.6-1  | Node Status Transition Diagram                                                                                   | 275 |  |  |  |

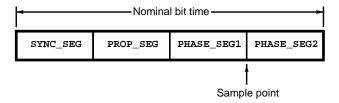

| Figure 19.6-2  | Bit Time Segment in CAN Specification                                                                            | 282 |  |  |  |

| Figure 19.6-3  | Bit Time Segment in CAN Controller                                                                               | 282 |  |  |  |

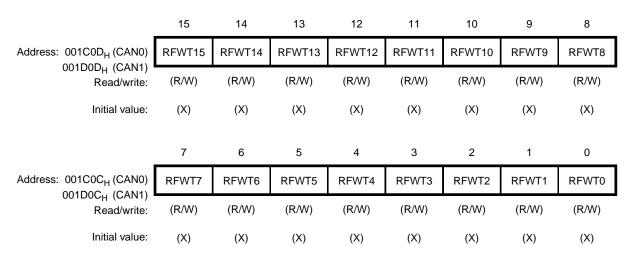

| Figure 19.7-1  | Transmission Flowchart of the CAN Controller                                                                     | 306 |  |  |  |

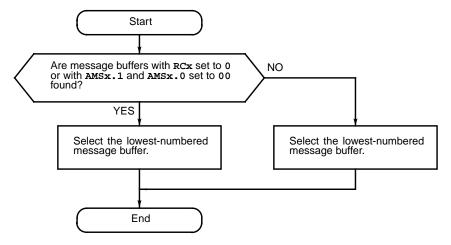

| Figure 19.8-1  | Flowchart Determining Message Buffer (x) where Received Messages Stored                                          | 308 |  |  |  |

| Figure 19.9-1  | Reception Flowchart of the CAN Controller                                                                        | 310 |  |  |  |

| Figure 19.12-1 | Example of Receive Interrupt Handling                                                                            | 316 |  |  |  |

| Figure 19.13-1 | Examples of Operation of Multi-level Message Buffer                                                              | 318 |  |  |  |

| Figure 20.1-1  | Block Diagram of Stepping Motor Controllerr                                                                      | 320 |  |  |  |

| Figure 21.1-1  | Block Diagram of Sound Generator                                                                                 | 328 |  |  |  |

| Figure 21.2-1  | Relationship between Tone Signal and Register Value                                                              | 332 |  |  |  |

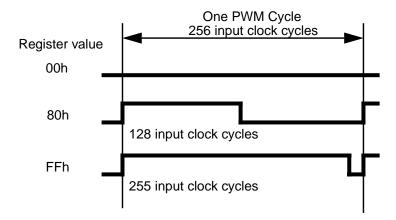

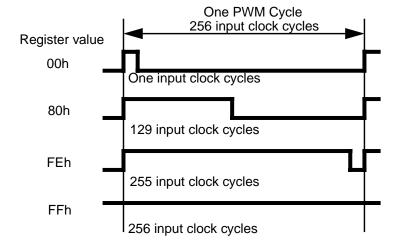

| Figure 21.2-2  | Relationship between Register Value and PWM Pulse                                                                | 333 |  |  |  |

| Figure 22.1-1  | Block Diagram of ROM Correction                                                                                  | 338 |  |  |  |

| Figure 22.2-1  | System Structure Example                                                                                         | 340 |  |  |  |

| Figure 22.2-2  | ROM Correction Processing Example                                                                                | 341 |  |  |  |

| Figure 22.2-3  | Processing Flow of ROM Correction                                                                                | 342 |  |  |  |

| Figure 22.2-4  | ROM Correction Processing Flow Diagram                                                                           | 343 |  |  |  |

| Figure 23.1-1  | Block Diagram of ROM Mirroring Module                                                                            | 346 |  |  |  |

| Figure 24.2-1  | Block Diagram of the Entire Flash Memory                                                                         | 351 |  |  |  |

| Figure 24.2-2  | Sector Configuration of the 2M/3M-Bit Flash Memory                                                               | 352 |  |  |  |

| Figure 24.7-1  | Example of the Flash Memory Write Procedure                                                                      | 368 |  |  |  |

| Figure 24.7-2  | Example of the Flash Memory Sector Erase Procedure                                                               | 371 |  |  |  |

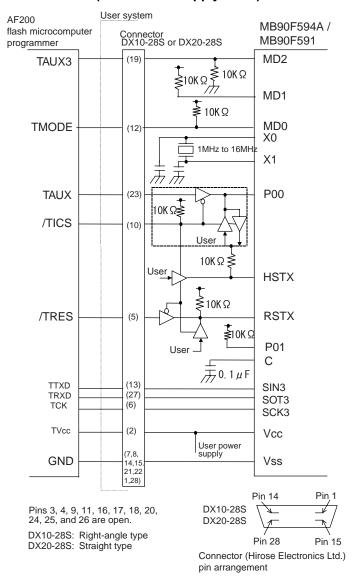

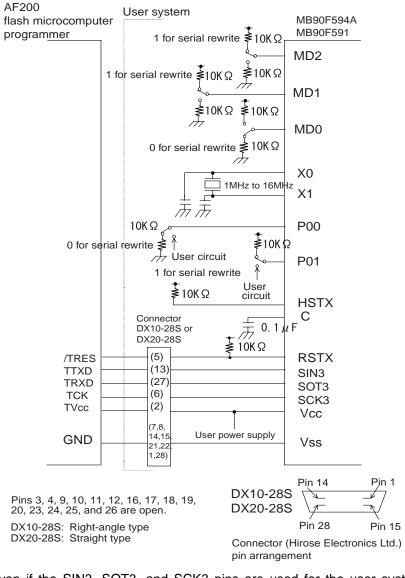

| Figure 25.2-1  | Example of Serial Write Connection for MB90F591/MB90F594A Internal Vector Modes (User Power Supply Used)         | 385 |  |  |  |

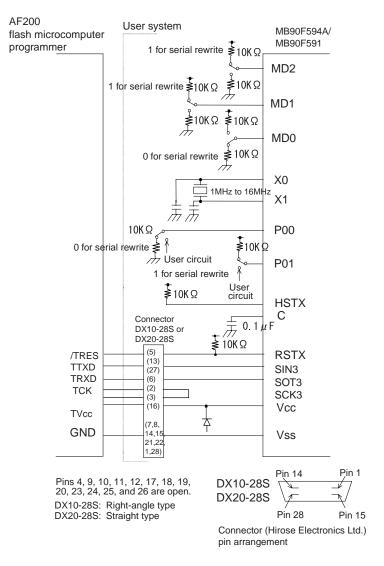

| Figure 25.3-1  | Example of Serial Write Connection for MB90F591/MB90F594A Internal Vector Modes (Power Supplied from the Writer) | 387 |  |  |  |

| Figure 25.4-1  | Example of Minimum Connection to the Flash Microcomputer Programmer (User Power Supply Used)                     | 389 |  |  |  |

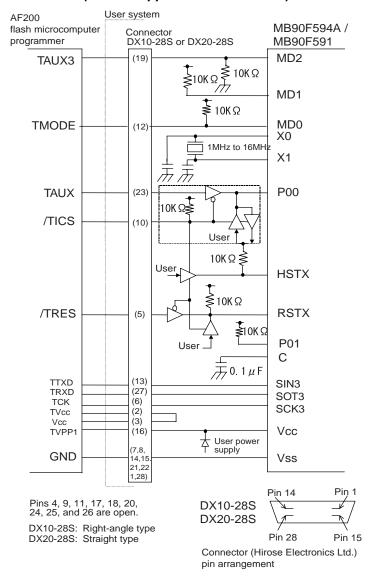

| Figure 25.5-1  | Example of Minimum Connection to the Flash Microcomputer Programmer (Power Supplied from the Writer)             | 391 |  |  |  |

| Figure B.3-1   | Example of immediate addressing (#imm)                                                                           |     |  |  |  |

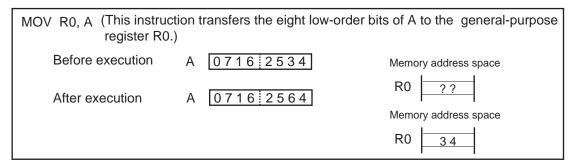

| Figure B.3-2   | Example of Register Direct Addressing                                                                            | 409 |  |  |  |

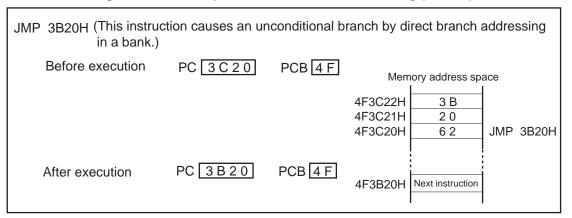

| Figure B.3-3  | Example of Direct Branch Addressing (addr16)                                                            |     |  |  |

|---------------|---------------------------------------------------------------------------------------------------------|-----|--|--|

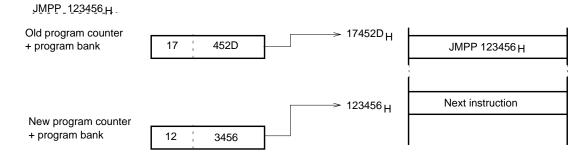

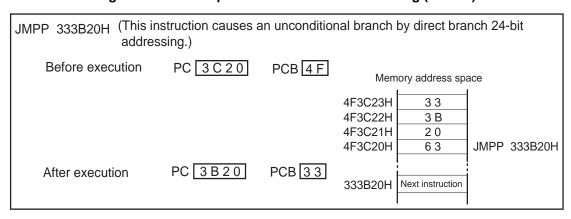

| Figure B.3-4  | Example of Direct Branch Addressing (addr24)                                                            |     |  |  |

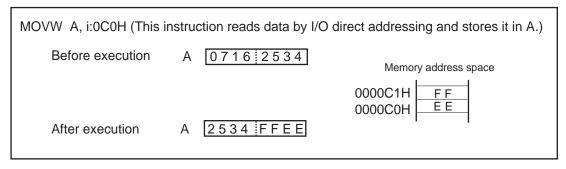

| Figure B.3-5  | Example of I/O Direct Addressing (io)                                                                   |     |  |  |

| Figure B.3-6  | Example of Abbreviated Direct Addressing (dir)                                                          |     |  |  |

| Figure B.3-7  | Example of Direct Addressing (addr16)                                                                   |     |  |  |

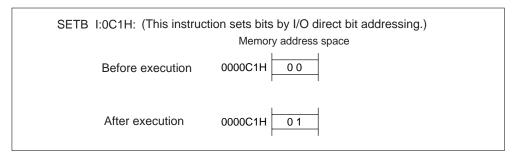

| Figure B.3-8  | Example of I/O Direct Bit Addressing (io:bp)4                                                           |     |  |  |

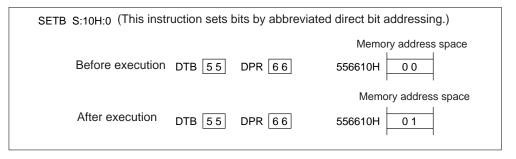

| Figure B.3-9  | Example of Abbreviated Direct Bit Addressing (dir:bp)                                                   | 411 |  |  |

| Figure B.3-10 | Example of Direct Bit addressing (addr16:bp)                                                            | 411 |  |  |

| Figure B.3-11 | Example of Vector Addressing (#vct)                                                                     | 412 |  |  |

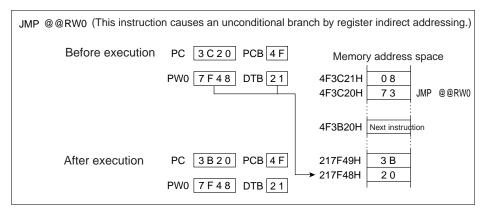

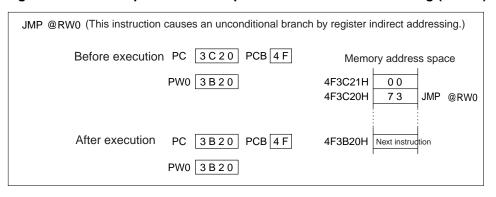

| Figure B.4-1  | Example of Register Indirect Addressing (@RWj j = 0 to 3)                                               | 413 |  |  |

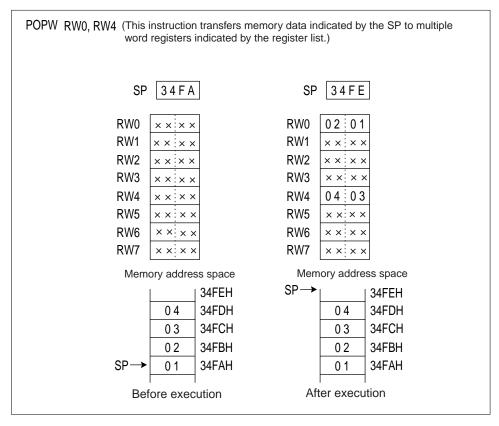

| Figure B.4-2  | Example of Register Indirect Addressing with Post Increment (@RWj + j = 0 to 3)                         | 413 |  |  |

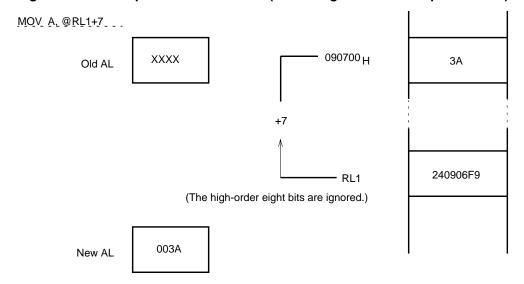

| Figure B.4-3  | Example of Register Indirect Addressing with Offset (@RWi + disp8 i = 0 to 7, @RWj + disp16 j = 0 to 3) | 414 |  |  |

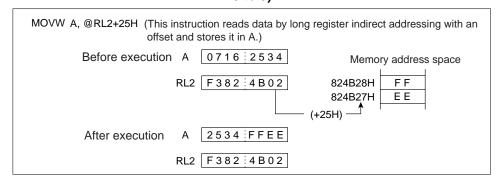

| Figure B.4-4  | Example of Long Register Indirect Addressing with Offset (@RLi + disp8 i = 0 to 3)                      | 414 |  |  |

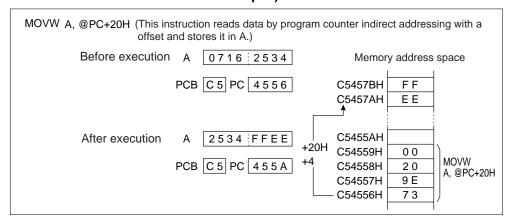

| Figure B.4-5  | Example of Program Counter Indirect Addressing with Offset (@PC + disp16)                               | 415 |  |  |

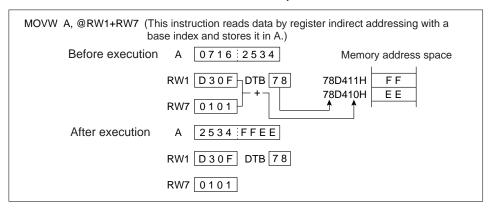

| Figure B.4-6  | Example of Register Indirect Addressing with Base Index (@RW0 + RW7, @RW1 + RW7)                        | 415 |  |  |

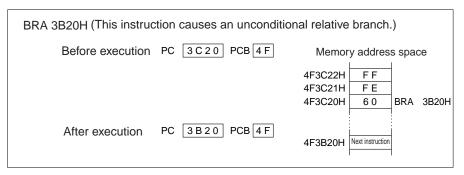

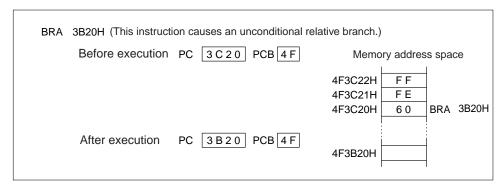

| Figure B.4-7  | Example of Program Counter Relative Branch Addressing (rel)                                             | 416 |  |  |

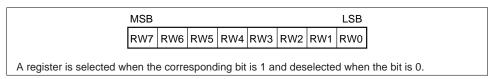

| Figure B.4-8  | Configuration of the Register List                                                                      | 416 |  |  |

| Figure B.4-9  | Example of Register List (rlist)                                                                        | 416 |  |  |

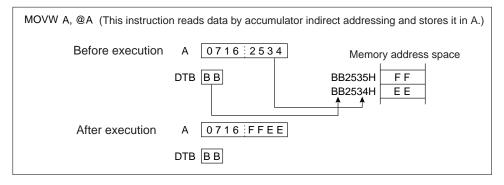

| Figure B.4-10 | Example of Accumulator Indirect Addressing (@A)                                                         | 417 |  |  |

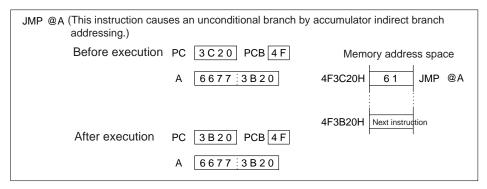

| Figure B.4-11 | Example of Accumulator Indirect Branch Addressing (@A)                                                  | 417 |  |  |

| Figure B.4-12 | Example of Indirect Specification Branch Addressing (@ear)                                              | 418 |  |  |

| Figure B.4-13 | Example of Indirect Specification Branch Addressing (@eam)                                              | 418 |  |  |

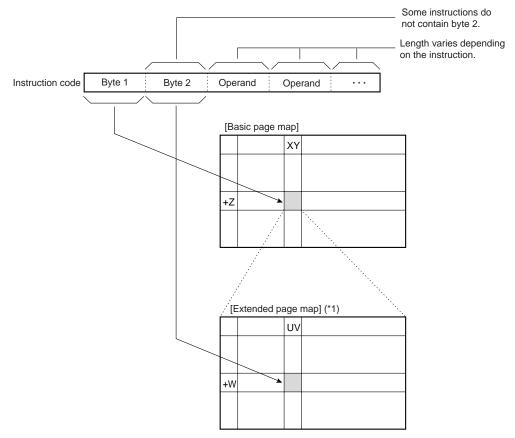

| Figure B.9-1  | Structure of Instruction Map                                                                            | 438 |  |  |

| Figure B.9-2  | Correspondence between Actual Instruction Code and Instruction Map                                      | 439 |  |  |

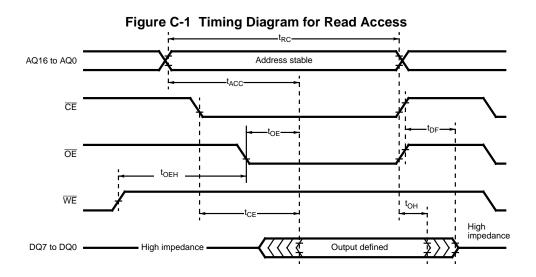

| Figure C-1    | Timing Diagram for Read Access                                                                          | 460 |  |  |

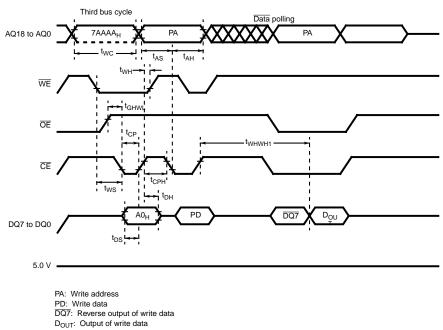

| Figure C-2    | Write Data polling Read (WE control)                                                                    | 460 |  |  |

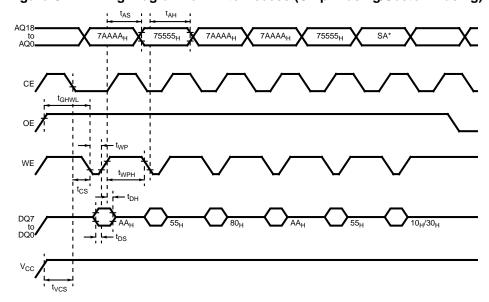

| Figure C-3    | Timing Diagram for Write Access (CE Control)                                                            |     |  |  |

| Figure C-4    | Timing Diagram for Write Access (Chip Erasing/Sector Erasing)                                           | 461 |  |  |

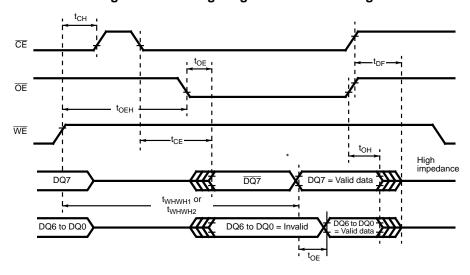

| Figure C-5    | Timing Diagram for Data Polling                                                                         | 462 |  |  |

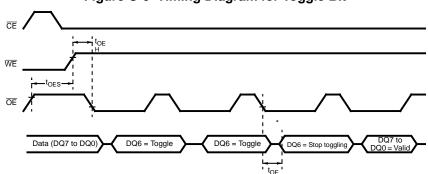

| Figure C-6    | Timing Diagram for Toggle Bit                                                                           |     |  |  |

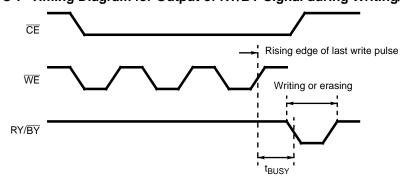

| Figure C-7    | Timing Diagram for Output of RY/BY Signal during Writing/Erasing                                        |     |  |  |

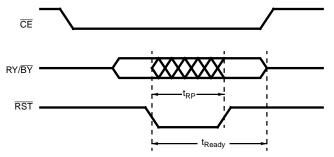

| Figure C-8    | Timing Diagram for Output of RY/BY Signal at Hardware Reset                                             | 463 |  |  |

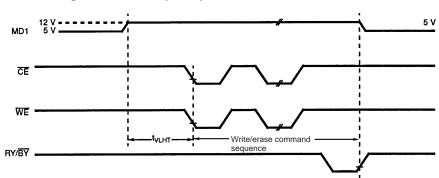

| Figure C-9    | Enable Sector Protect/Verify Sector Protect                                                             | 463 |  |  |

| Figure C-10   | Temporary Sector Protect Cancellation                                                                   | 464 |  |  |

# **TABLES**

| Table 1.1-1  | Product Overview                                                                 |     |  |  |

|--------------|----------------------------------------------------------------------------------|-----|--|--|

| Table 1.2-1  | MB90590 Features                                                                 | 3   |  |  |

| Table 1.6-1  | Pin Functions                                                                    | 8   |  |  |

| Table 1.7-1  | Input-output Circuits                                                            | 12  |  |  |

| Table 2.5-1  | Default Space                                                                    | 22  |  |  |

| Table 2.7-1  | Levels Indicated by the Interrupt Level Mask (ILM) Register                      | 30  |  |  |

| Table 2.8-1  | Register Functions                                                               | 33  |  |  |

| Table 2.8-2  | Relationship between Registers                                                   | 33  |  |  |

| Table 2.9-1  | Bank Select Prefix                                                               | 35  |  |  |

| Table 3.2-1  | Interrupt Vectors                                                                | 43  |  |  |

| Table 3.3-1  | Interrupt Level Setting Bits and Interrupt Levels                                | 44  |  |  |

| Table 3.3-2  | ICS bits, Channel Numbers, and Descriptor Addresses                              | 46  |  |  |

| Table 3.3-3  | S Bits and End Conditions                                                        | 46  |  |  |

| Table 3.5-1  | Compensation Values for Interrupt Processing Cycle Count                         | 52  |  |  |

| Table 3.8-1  | Execution Time when the Extended El <sup>2</sup> OS Continues                    | 62  |  |  |

| Table 3.8-2  | Data Transfer Compensation Values for Extended EI <sup>2</sup> OS Execution Time | 62  |  |  |

| Table 5.3-1  | Reset Causes                                                                     | 73  |  |  |

| Table 5.3-2  | Reset Cause Bits                                                                 | 74  |  |  |

| Table 6.2-1  | CG Bit Setting                                                                   | 80  |  |  |

| Table 6.2-2  | WS Bit Setting                                                                   | 81  |  |  |

| Table 6.2-3  | CS Bit Setting                                                                   | 82  |  |  |

| Table 6.3-1  | Low-power mode status                                                            | 83  |  |  |

| Table 6.3-2  | List of Instructions Used for Transition to Low-power Mode                       | 84  |  |  |

| Table 7.2-1  | Mode Pins and Modes                                                              | 95  |  |  |

| Table 7.3-1  | Mode Setting Bits and Functions                                                  | 96  |  |  |

| Table 7.3-2  | Bus Mode Setting Bits and Functions                                              | 96  |  |  |

| Table 7.3-3  | Sample Recommended Setting of Mode Pins and Mode Data                            | 97  |  |  |

| Table 9.2-1  | Selecting the Time Base Timer Interval                                           | 107 |  |  |

| Table 10.1-1 | Reset Cause Registers                                                            | 113 |  |  |

| Table 10.1-2 | Watch-dog Timer Interval Selection Bit                                           | 113 |  |  |

| Table 12.2-1 | Clock Sources for CSL Bit Settings                                               |     |  |  |

| Table 12.2-2 | MOD2, 1, 0 Bit Settings (1)                                                      |     |  |  |

| Table 12.2-3 | MOD2, 1, 0 Bit Settings (2)                                                      | 146 |  |  |

| Table 12.2-4 | OUTE, RELD, and OUTL Settings                                                    | 146 |  |  |

| Table 14.4-1 | Reload Operation and Pulse Output                                                | 175 |  |  |

| Table 15.2-1  | Interrupt Request Detection Factor for LBx and LAx Pins                                | . 187 |

|---------------|----------------------------------------------------------------------------------------|-------|

| Table 16.3-1  | Operation Mode Setting                                                                 | . 198 |

| Table 17.3-1  | UART Operation Modes                                                                   | 221   |

| Table 17.3-2  | UIDR State after Receive Completion                                                    | 223   |

| Table 17.3-3  | Clock Input Selection                                                                  | 226   |

| Table 17.3-4  | Clock Input Selection                                                                  | 226   |

| Table 17.4-1  | UART0 Operating Modes                                                                  | 228   |

| Table 17.5-1  | Baud Rate                                                                              | 230   |

| Table 17.6-1  | Baud Rate and Reload Value                                                             | 232   |

| Table 18.2-1  | Setting the Serial Mode Selection Bit                                                  | 246   |

| Table 18.2-2  | Setting the Transfer Direction Selection Bit                                           | 246   |

| Table 18.2-3  | Setting the Serial Output Enable Bit                                                   | 247   |

| Table 18.2-4  | Setting the Shift Clock Output Enable Bit                                              | 247   |

| Table 18.2-5  | Setting the Serial Shift Clock Mode                                                    | 247   |

| Table 18.2-6  | Setting the Interrupt Request Enable Bit                                               | 248   |

| Table 18.2-7  | Setting the Transfer Status Bit                                                        | 248   |

| Table 18.2-8  | Setting the Stop Bit                                                                   | 249   |

| Table 18.3-1  | Machine Clock Division Ratio                                                           | 251   |

| Table 18.5-1  | Setting the NEG Bit                                                                    | 259   |

| Table 19.3-1  | List of Overall Control Registers                                                      | . 264 |

| Table 19.4-1  | List of Message Buffers (ID Registers)                                                 | 266   |

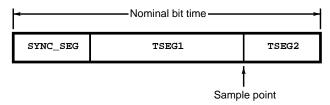

| Table 19.5-1  | List of Message Buffers (DLC Registers and Data Registers)                             | . 269 |

| Table 19.5-2  | List of Message Buffers (Data Registers)                                               | 271   |

| Table 19.6-1  | Correspondence between NS1 and NS0 and Node Status                                     | 275   |

| Table 19.6-2  | Selection of Acceptance Mask                                                           | 295   |

| Table 24.3-1  | Flash Memory Control Signals                                                           | 353   |

| Table 24.5-1  | Command Sequence Table                                                                 | 357   |

| Table 24.6-1  | Bit Assignments of Hardware Sequence Flags                                             | 358   |

| Table 24.6-2  | Hardware Sequence Flag Functions                                                       | 359   |

| Table 24.6-3  | Data Polling Flag State Transitions (State Change for Normal Operation)                | 360   |

| Table 24.6-4  | Data Polling Flag State Transitions (State Change for Abnormal Operation)              | 360   |

| Table 24.6-5  | Toggle Bit Flag State Transitions (State Change for Normal Operation)                  | 362   |

| Table 24.6-6  | Toggle Bit Flag State Transitions (State Change for Abnormal Operation)                | 362   |

| Table 24.6-7  | Timing Limit Exceeded Flag State Transitions (State Change for Normal Operation)       | 363   |

| Table 24.6-8  | Timing Limit Exceeded Bit Flag State Transitions (State Change for Abnormal Operation) | 363   |

| Table 24.6-9  | Sector Erase Timer Flag State Transitions (State Change for Normal Operation)          |       |

| Table 24.6-10 | Sector Erase Timer Flag State Transitions (State Change for Abnormal Operation)        | 364   |

| Table 25.1-1  | Pins Used for Fujitsu Standard Serial Onboard Writing                                  | 382   |

| Table 25.1-2 | AF200 Flash Microcomputer Programmer System Configuration (Manufactured by Yokogawa Digital Computer Ltd.) |     |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------|-----|--|--|--|

| Table A-1    | I/O Map                                                                                                    | 394 |  |  |  |

| Table A-2    | I/O Map (19XX Address)                                                                                     |     |  |  |  |

| Table B.2-1  | Effective Address Field                                                                                    |     |  |  |  |

| Table B.3-1  | Direct Addressing Registers                                                                                | 408 |  |  |  |

| Table B.3-2  | CALLV Vector List                                                                                          | 412 |  |  |  |

| Table B.5-1  | Execution Cycle Counts in Each Addressing Mode                                                             | 419 |  |  |  |

| Table B.5-2  | Cycle Count Correction Values for Counting Execution Cycles                                                | 420 |  |  |  |

| Table B.5-3  | Cycle Count Correction Values for Counting Instruction Fetch Cycles                                        | 420 |  |  |  |

| Table B.6-1  | Effective Address Field                                                                                    | 422 |  |  |  |

| Table B.7-1  | Description of Items in the Instruction List                                                               | 424 |  |  |  |

| Table B.7-2  | Explanation on Symbols in the Instruction List                                                             | 425 |  |  |  |

| Table B.8-1  | 41 Transfer Instructions (byte)                                                                            | 427 |  |  |  |

| Table B.8-2  | 38 Transfer Instructions (byte)                                                                            | 428 |  |  |  |

| Table B.8-3  | 42 Addition/subtraction Instructions (byte, word, long word)                                               | 429 |  |  |  |

| Table B.8-4  | 12 Increment/decrement Instructions (byte, word, long word)                                                | 429 |  |  |  |

| Table B.8-5  | 11 Compare Instructions (byte, word, long word)                                                            | 430 |  |  |  |

| Table B.8-6  | 11 unsigned multiplication/division instructions (word, long word)                                         | 430 |  |  |  |

| Table B.8-7  | 39 Logic 1 Instructions (byte, word)                                                                       |     |  |  |  |

| Table B.8-8  | Six Logic 2 Instructions (long word)                                                                       | 432 |  |  |  |

| Table B.8-9  | Six Sign Inversion Instructions (byte, word)                                                               | 432 |  |  |  |

| Table B.8-10 | One Normalization Instruction (long word)                                                                  | 432 |  |  |  |

| Table B.8-11 | 18 Shift Instructions (byte, word, long word)                                                              | 432 |  |  |  |

| Table B.8-12 | 31 Branch 1 Instructions                                                                                   | 433 |  |  |  |

| Table B.8-13 | 19 Branch 2 Instructions                                                                                   | 434 |  |  |  |

| Table B.8-14 | 31 28 Other Control Instructions (byte, word, long word)                                                   | 435 |  |  |  |

| Table B.8-15 | 21 Bit Operand Instructions                                                                                | 435 |  |  |  |

| Table B.8-16 | Six Accumulator Operation Instructions (byte, word)                                                        | 436 |  |  |  |

| Table B.8-17 | Ten String Instructions                                                                                    | 436 |  |  |  |

| Table B.9-1  | Example of an Instruction Code                                                                             | 439 |  |  |  |

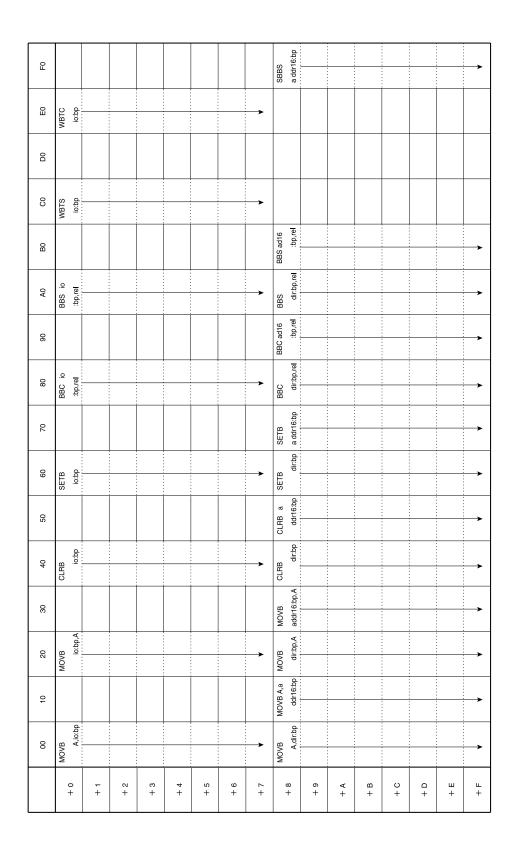

| Table B.9-2  | Basic Page Map                                                                                             | 440 |  |  |  |

| Table B.9-3  | Bit Operation Instruction Map (first byte = 6CH)                                                           | 441 |  |  |  |

| Table B.9-4  | Character String Operation Instruction Map (first byte = 6EH)                                              | 442 |  |  |  |

| Table B.9-5  | 2-byte Instruction Map (first byte = 6FH)                                                                  |     |  |  |  |

| Table B.9-6  | ea Instruction 1 (first byte = 70H)                                                                        | 444 |  |  |  |

| Table B.9-7  | ea Instruction 2 (first byte = 71H)                                                                        | 445 |  |  |  |

| Table B.9-8  | ea Instruction 3 (first byte = 72H)                                                                        |     |  |  |  |

|              |                                                                                                            |     |  |  |  |

| Table B.9-9  | ea Instruction 4 (first byte = 73H)                                  | 447 |

|--------------|----------------------------------------------------------------------|-----|

| Table B.9-10 | ea Instruction 5 (first byte = 74H)                                  | 448 |

| Table B.9-11 | ea Instruction 6 (first byte = 75H)                                  | 449 |

| Table B.9-12 | ea Instruction 7 (first byte = 76H)                                  | 450 |

| Table B.9-13 | ea Instruction 8 (first byte = 77H)                                  | 451 |

| Table B.9-14 | ea Instruction 9 (first byte = 78H)                                  | 452 |

| Table B.9-15 | MOVEA RWi, ea Instruction (first byte = 79H)                         | 453 |

| Table B.9-16 | MOV Ri, ea Instruction (first byte = 7AH)                            | 454 |

| Table B.9-17 | MOVW RWi, ea Instruction (first byte = 7BH)                          | 455 |

| Table B.9-18 | MOV ea, Ri Instruction (first byte = 7CH)                            | 456 |

| Table B.9-19 | MOVW ea, Rwi Instruction (first byte = 7DH)                          | 457 |

| Table B.9-20 | XCH Ri, ea Instruction (first byte = 7EH)                            | 458 |

| Table B.9-21 | XCHW RWi, ea Instruction (first byte = 7FH)                          | 459 |

| Table D-1    | MB90590 Interrupt Vectors                                            | 465 |

| Table D-2    | Interrupt Causes, Interrupt Vectors, and Interrupt Control Registers | 467 |

# **CHAPTER 1 OVERVIEW**

# The MB90590 Series is a family member of the F<sup>2</sup>MC-16LX micro controllers.

- 1.1 Product Overview

- 1.2 Features

- 1.3 Block Diagram

- 1.4 Pin Assignment

- 1.5 Package Dimensions

- 1.6 Pin Functions

- 1.7 Circuit

- 1.8 Handling the Device

# 1.1 Product Overview

## Table 1.1-1 provides a quick outlook of the MB90590 Series.

## **■** Product Overview

**Table 1.1-1 Product Overview**

| Features            | MB90V590A                                                                                                                        | MB90F594A/F591                                                                                                                                     | MB90594/591                                                          |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Product type        | Evaluation sample                                                                                                                | Flash version                                                                                                                                      | Mask ROM version                                                     |

| CPU                 |                                                                                                                                  | F <sup>2</sup> MC-16LX CPU                                                                                                                         |                                                                      |

| System clock        | On-chip PLL clock multiplier (x1, x2, x3, x4, 1/2 when PLL stop) Minimum instruction execution time: 62.5 ns (4 MHz osc. PLL x4) |                                                                                                                                                    |                                                                      |

| ROM/Flash<br>memory | External                                                                                                                         | Boot-block<br>Flash memory 256K/384K<br>bytes with Hard-wired reset<br>vector                                                                      | Mask ROM 256K/384K bytes                                             |

| RAM                 | 8Kbytes                                                                                                                          | 6K/8K bytes                                                                                                                                        |                                                                      |

| Technology          | 0.5 μm CMOS with on-chip voltage regulator for internal power supply                                                             | 0.5 µm CMOS + Flash<br>memory with on-chip voltage<br>regulator for internal power<br>supply and on-chip charge<br>pump for programming<br>voltage | 0.5 μm CMOS with on-chip voltage regulator for internal power supply |

| Package             | kage PGA-256 QFP100                                                                                                              |                                                                                                                                                    | P100                                                                 |

# 1.2 Features

## Table 1.2-1 lists the features of the MB90590 series.

## **■** Features

Table 1.2-1 MB90590 Features

| Function                                 | Feature                                                                                                                                                                                                                                                       |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UART<br>(3 channels)                     | Full duplex double buffer Supports asynchronous/synchronous(with start/stop bit) transfer Baud rate: 4808/5208/9615/10417/19230/38460/62500/500000bps (asynchronous) 500K/1M/2Mbps (synchronous) at System clock = 16MHz                                      |

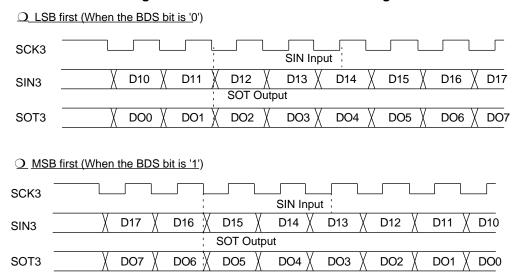

| Serial IO                                | Transfer can be started from MSB or LSB Supports internal clock synchronized transfer and external clock synchronized transfer Supports positive-edge and negative-edge clock synchronization Baud rate: 31.25K/62.5K/125K/500K/1Mbps at System clock = 16MHz |

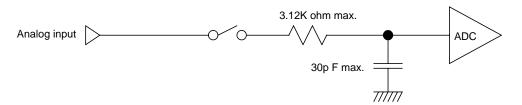

| A/D<br>Converter                         | 10 or 8-bit resolution<br>8 input channels<br>Conversion time : 26.3us (per one channel)                                                                                                                                                                      |

| 16-bit Reload Timer<br>(2 channels)      | Operation clock frequency: fsys/2 <sup>1</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>5</sup> (fsys = System clock frequency) Supports External Event Count function                                                                                             |

| Watch Timer                              | Directly operates with the oscillation clock Facility to correct oscillation deviation Read/Write accessible Second/Minute/Hour registers Signals interrupts                                                                                                  |

| 16-bit<br>IO Timer                       | Signals an interrupt when overflow Supports Timer Clear when a match with Output Compare(Channel 0) Operation clock frequency: fsys/2 <sup>2</sup> , fsys/2 <sup>4</sup> ,fsys/2 <sup>6</sup> , fsys/2 <sup>8</sup> (fsys = System clock frequency)           |

| 16-bit<br>Output Compare<br>(6 channels) | Signals an interrupt when a match with 16-bit IO Timer Six 16-bit compare registers A pair of compare registers can be used to generate an output signal                                                                                                      |

| 16-bit<br>Input Capture<br>(6 channels)  | Rising edge, falling edge or rising & falling edge sensitive Six 16-bit Capture registers Signals an interrupt upon external event                                                                                                                            |

## **CHAPTER 1 OVERVIEW**

Table 1.2-1 MB90590 Features (Continued)

| Function                                                    | Feature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 8/16-bit<br>Programmable Pulse<br>Generator<br>(6 channels) | Supports 8-bit and 16-bit operation modes Twelve 8-bit reload counters Twelve 8-bit reload registers for L pulse width Twelve 8-bit reload registers for H pulse width A pair of 8-bit reload counters can be configured as one 16-bit reload counter or as 8-bit prescaler plus 8-bit reload counter 6 output pins Operation clock frequency: fsys, fsys/2 <sup>1</sup> , fsys/2 <sup>2</sup> , fsys/2 <sup>3</sup> , fsys/2 <sup>4</sup> or 128us@fosc=4MHz (fsys = System clock frequency, fosc = Oscillation clock frequency) |  |  |

| CAN Interface<br>(2 channels)                               | Conforms to CAN Specification Version 2.0 Part A and B Automatic re-transmission in case of error Automatic transmission responding to Remote Frame Prioritized 16 message buffers for data and ID's Supports multiple messages Flexible configuration of acceptance filtering: Full bit compare / Full bit mask / Two partial bit masks Supports up to 1Mbps                                                                                                                                                                     |  |  |