# POSITIVE / PSEUDO ECL (PECL) CLOCK TERMINATION NETWORK

#### **Features**

- Stable resistor network

- Reduces power dissipation on the clock lines

- Ideal for high-speed clock termination

- Reduces board space by 70% vs. 1206 discretes and component count by more than 50%

# **Applications**

• PECL clock termination

## **Application Note**

High speed microprocessors line Intel's Pentium/P6®, Apple PowerPC®, SPARC® and other CISC and RISC based systems need well-controlled and precise clock signals to maintain a synchronous systems. The fast edge rated clock signals will exhibit transmission line effects on the clock lines resulting in undershoots and overshoots. The integrated PECL termination is designed to suppress the undershoots and overshoots on the clock lines. The PECL RC terminator dissipates very low power compared to the resistor termination network.

Why thin.film R networks? The PECL termination is an integrated R network fabricated on a silicon substrate using advanced thin film technology. This will have a fixed time constant and will not create additional skew on the clock lines. It has a low parasitic inductance compared to discrete and conventional thick film R terminators and provide effective termination at high frequencies.

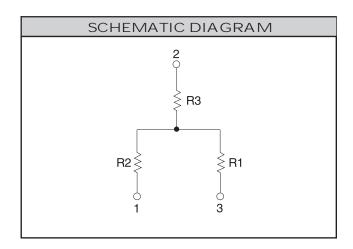

| STANDARD VALUES       |                       |                       |

|-----------------------|-----------------------|-----------------------|

| $R_1(\Omega) \pm 1\%$ | $R_2(\Omega) \pm 1\%$ | $R_3(\Omega) \pm 1\%$ |

| 50                    | 50                    | 46.4                  |

| STANDARD PART ORDERING INFORMATION |        |                      |

|------------------------------------|--------|----------------------|

| Pa                                 | ckage  | Ordering Part Number |

| Pins                               | Style  | Part Marking         |

| 3                                  | SOT-23 | PRN299               |

When placing an order please specify desired shipping: Tubes or Tape & Reel.

| ABSOLUTE MAXIMUM RATINGS                                     |                                |      |  |

|--------------------------------------------------------------|--------------------------------|------|--|

| Parameter                                                    | Rating                         | Unit |  |

| $V_{CC1}$ , $V_{CC2}$ , $V_{CC3}$ & $V_{CC4}$ supply voltage | GND-0.5, +6.0                  | V    |  |

| Diode D1 forward current                                     | 100                            | uA   |  |

| DC voltage at inputs:                                        |                                | V    |  |

| VIDEO_1, VIDEO_2, VIDEO_3                                    | GND-0.5, V <sub>CC1</sub> +0.5 | V    |  |

| TERM_1, TERM_2, TERM_3                                       | -6.0, +6.0                     | V    |  |

| DDC_IN1, DDC_IN2                                             | GND-0.5, V <sub>CC2</sub> +0.5 |      |  |

| DDC_OUT1, DDC_OUT2                                           | GND-0.5, V <sub>CC3</sub> +0.5 | V    |  |

| SYNC_IN1, SYNC_IN2                                           | GND-0.5, V <sub>CC4</sub> +0.5 | V    |  |

| Temperature:                                                 |                                |      |  |

| Storage                                                      | -40 to +150                    | ∘C   |  |

| Operating Ambient                                            | 0 to +70                       | ∘C   |  |

| Package power dissipation                                    | 1.0                            | W    |  |

| ELECTRICAL OPERATING CHARACTERISTICS (over operating conditions unless specified otherwise) |                                                    |                                                                                           |       |                       |       |      |

|---------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-----------------------|-------|------|

| Symbol                                                                                      | Parameter                                          | Conditions                                                                                | MIN   | TYP                   | MAX   | UNIT |

| I <sub>CC1</sub>                                                                            | V <sub>CC1</sub> supply current                    | $V_{CC1} = 5V$ ; VIDEO inputs at $V_{CC1}$ or GND                                         |       |                       | 10    | uA   |

| I <sub>CC2, 3</sub>                                                                         | V <sub>CC2</sub> , V <sub>CC3</sub> supply current | $V_{CC2} = V_{CC3} = 5V$                                                                  |       |                       | 10    | uA   |

| I <sub>CC4</sub>                                                                            | V <sub>CC4</sub> supply current                    | $V_{CC4} = 5V$ ; SYNC inputs at GND or $V_{CC4}$ ;                                        |       | 10                    |       | uA   |

|                                                                                             |                                                    | PWR_UP pin at V <sub>CC4</sub> ; SYNC outputs unloaded                                    |       |                       |       |      |

|                                                                                             |                                                    | $V_{CC4} = 5V$ ; SYNC inputs at 3.0V; PWR_UP                                              |       | 200                   |       | uA   |

|                                                                                             |                                                    | pin at V <sub>CC4</sub> ; SYNC outputs unloaded                                           |       |                       |       |      |

|                                                                                             |                                                    | $V_{CC4} = 5V$ ; PWR_UP input at GND; SYNC                                                |       |                       | 10    | uA   |

|                                                                                             |                                                    | outputs unloaded                                                                          |       |                       |       |      |

| $V_{BIAS}$                                                                                  | V <sub>BIAS</sub> open circuit voltage             | No external current drawn from V <sub>BIAS</sub> pin                                      |       | V <sub>CC4</sub> -0.8 |       | V    |

| R <sub>T</sub>                                                                              | VIDEO termination resistance                       |                                                                                           | 71.25 | 75                    | 78.75 | Ω    |

|                                                                                             | R <sub>T</sub> resistance matching                 |                                                                                           |       | 1                     | 2     | %    |

| $V_{IH}$                                                                                    | Logic High input voltage <sup>1</sup>              | $V_{CC4} = 5.0V$                                                                          | 2.0   |                       |       | V    |

| $V_{IL}$                                                                                    | Logic Low input voltage <sup>1</sup>               | $V_{CC4} = 5.0V$                                                                          |       |                       | 8.0   | V    |

| V <sub>OH</sub>                                                                             | Logic High output voltage <sup>1</sup>             | $I_{OH} = -4 \text{mA}, V_{CC4} = 5.0 \text{V}$                                           | 4.4   |                       |       | V    |

| V <sub>OL</sub>                                                                             | Logic Low output voltage <sup>1</sup>              | $I_{OL} = 4mA, V_{CC4} = 5.0V$                                                            |       |                       | 0.4   | V    |

| $R_{b'} R_{p}$                                                                              | Resistor value                                     | PWR_UP, $V_{CC3} = 5.0V$                                                                  | 0.5   | 1                     | 2     | MΩ   |

| R <sub>c</sub>                                                                              | V <sub>CC 2</sub> pull-down resistor               | $V_{CC2} = 3.0V$                                                                          | 0.5   | 1.5                   | 3     | MΩ   |

| I <sub>N</sub>                                                                              | Input current                                      |                                                                                           |       |                       |       |      |

|                                                                                             | VIDEO inputs                                       | $V_{CC1} = 5V$ ; $V_{IN} = V_{CC1}$ or GND                                                |       |                       | ±1    | μΑ   |

|                                                                                             | HSYNC, VSYNC inputs                                | $V_{CC4} = 5V$ ; $V_{IN} = V_{CC4}$ or GND                                                |       |                       | ±1    | μΑ   |

| I <sub>OFF</sub>                                                                            | OFF state leakage current, level                   | $(V_{CC2} - V_{DDC\_IN}) \le 0.4V; V_{DDC\_OUT} = V_{CC2}$                                |       |                       | 10    | μΑ   |

|                                                                                             | shifting NFET                                      | $(V_{CC2} - V_{DDC OUT}) \le 0.4V$ ; $V_{DDC_{IN}} = V_{CC2}$                             |       |                       | 10    | μА   |

| V <sub>ON</sub>                                                                             | Voltage drop across level                          | $V_{CC2} = 2.5V; V_S = GND, I_{DS} = 3mA$                                                 |       |                       | 0.15  | V    |

|                                                                                             | shifting NFET when turned ON                       |                                                                                           |       |                       |       |      |

| C <sub>IN</sub>                                                                             | Input capacitance 3                                |                                                                                           |       |                       |       |      |

|                                                                                             | VIDEO_1, VIDEO_2, VIDEO_3                          | $V_{CC1} = 5.0V$ ; $V_{IN} = 2.5V$ ; measured at 1MHz                                     |       | 4.0                   |       | рF   |

|                                                                                             |                                                    | $V_{CC1} = 2.5V$ ; $V_{IN} = 1.25V$ ; measured at 1MHz                                    |       | 4.5                   |       |      |

| t <sub>PLH</sub>                                                                            | SYNC drivers L-H propagation delay                 | $C_L = 50 \text{ pF}; V_{CC} = 5V; \text{ Input } t_r \text{ and } t_f \leq 5 \text{ ns}$ |       | 8                     | 12    | ns   |

| t <sub>PHL</sub>                                                                            | SYNC drivers H-L propagation delay                 | $C_L = 50 \text{ pF}; V_{CC} = 5V; \text{ Input } t_r \text{ and } t_f \leq 5 \text{ns}$  |       | 8                     | 12    | ns   |

| t <sub>r</sub> , t <sub>f</sub>                                                             | SYNC drivers output rise & fall times              | $C_L = 50 \text{ pF}; V_{CC} = 5V; \text{ Input } t_r \text{ and } t_f \leq 5 \text{ ns}$ |       | 7                     |       | ns   |

| V <sub>ESD</sub>                                                                            | ESD withstand voltage <sup>2, 3</sup>              | $V_{CC1} = V_{CC3} = V_{CC4} = 5V$                                                        | ±8    |                       |       | kV   |

Note 1: These parameter applies only to the HSYNC and VSYNC channels.

Note 2: Per the IEC-61000-4-2 International ESD Standard, Level 4 contact discharge method.  $V_{\rm CCI}$ ,  $V_{\rm CC3}$  and  $V_{\rm CC4}$  must be bypassed to GND via a low impedance ground plane with a 0.2uF, low inductance, chip ceramic capacitor at each supply pin. ESD pulse is applied between the applicable pins and GND. ESD pulse can be positive or negative with respect to GND. Applicable pins are: VIDEO\_1, VIDEO\_2, VIDEO\_3, SYNC\_OUT1, SD1, SYNC\_OUT2, SD2, DDC\_OUT1 and DDC\_OUT2. All other pins are ESD protected to the industry standard 2kV per the Human Body model (MIL-STD-883, Method 3015).

Note 3: This parameter is guaranteed by design and characterization.

©2000 California Micro Devices Corp. All rights reserved.

2

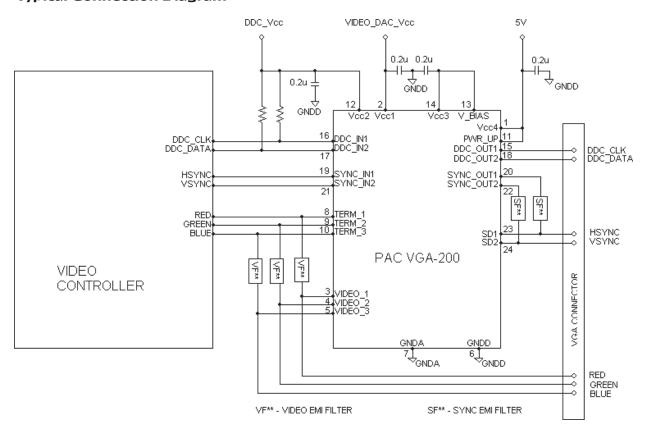

## **Typical Connection Diagram**

A resistor may be necessary between the  $V_{CC3}$  pin and ground if protection against a stream of ESD pulses is required while the PAC VGA200 is in the power-down state. The value of this resistor should be chosen such that the extra charge deposited into the  $V_{CC3}$  bypass capacitor by each ESD pulse will be discharged before the next ESD pulse occurs. The maximum ESD repetition rate specified by the IEC-61000-4-2 standard is one pulse per second. When the PAC VGA200 is in the power-up state, an internal discharge resistor is connected to ground via an FET switch for this purpose.

For the same reason,  $V_{cc1}$  and  $V_{cc4}$  may also require bypass capacitor discharging resistors to ground if there are no other components in the system to provide a discharge path to ground.

GNDA, the reference voltage for the 75R resistors is not connected internally to GNDD and should ideally be connected to the ground of the video DAC IC.

| STANDARD PART ORDERING INFORMATION |       |                      |

|------------------------------------|-------|----------------------|

| Package                            |       | Ordering Part Number |

| Pins                               | Style | Part Marking         |

| 24                                 | QSOP  | PACVGA200Q           |

When placing an order please specify desired shipping: Tubes or Tape & Reel.