Data Sheet

## May 1999 File Number 2785.5

# Digital Filter

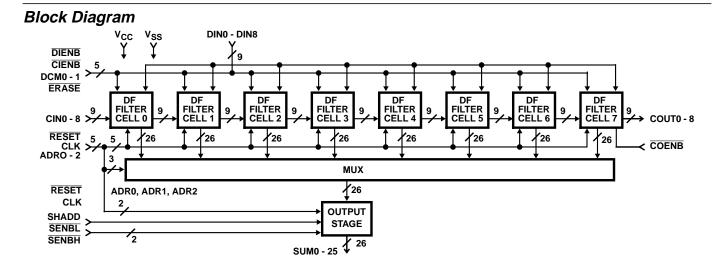

The HSP43891 is a video-speed Digital Filter (DF) designed to efficiently implement vector operations such as FIR digital filters. It is comprised of eight filter cells cascaded internally and a shift and add output stage, all in a single integrated circuit. Each filter cell contains a 9x9 two's complement multiplier, three decimation registers and a 26-bit accumulator. The output stage contains an additional 26-bit accumulator which can add the contents of any filter cell accumulator to the output stage accumulator shifted right by 8-bits. The HSP43891 has a maximum sample rate of 30MHz. The effective multiply-accumulate (mac) rate is 240MHz.

The HSP43891 DF can be configured to process expanded coefficient and word sizes. Multiple DFs can be cascaded for larger filter lengths without degrading the sample rate or a single DF can process larger filter lengths at less than 30MHz with multiple passes. The architecture permits processing filter lengths of over 1000 taps with the guarantee of no overflows. In practice, most filter coefficients are less than 1.0, making even larger filter lengths possible. The DF provides for 8-bit unsigned or 9-bit two's complement arithmetic, independently selectable for coefficients and signal data.

Each DF filter cell contains three resampling or decimation registers which permit output sample rate reduction at rates of  $1_{2}$ ,  $1_{3}$  or  $1_{4}$  the input sample rate. These registers also provide the capability to perform 2-D operations such as matrix multiplication and NxN spatial

correlations/convolutions for image processing applications.

## Features

- Eight Filter Cells

- 0MHz to 30MHz Sample Rate

- 9-Bit Coefficients and Signal Data

- 26-Bit Accumulator per Stage

- Filter Lengths Over 1000 Taps

- Expandable Coefficient Size, Data Size and Filter Length

- Decimation by 2, 3 or 4

## Applications

- 1-D and 2-D FIR Filters

- Radar/Sonar

- Digital Video

- Adaptive Filters

- Echo Cancellation

- Complex Multiply-Add

- Sample Rate Converters

## **Ordering Information**

| PART NUMBER   | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE       | PKG. NO.   |

|---------------|----------------------------------|---------------|------------|

| HSP43891VC-20 | 0 to 70                          | 100 Lead MQFP | Q100.14x20 |

| HSP43891VC-25 | 0 to 70                          | 100 Lead MQFP | Q100.14x20 |

| HSP43891VC-30 | 0 to 70                          | 100 Lead MQFP | Q100.14x20 |

| HSP43891JC-20 | 0 to 70                          | 84 Lead PLCC  | N84.1.15   |

| HSP43891JC-25 | 0 to 70                          | 84 Lead PLCC  | N84.1.15   |

| HSP43891JC-30 | 0 to 70                          | 84 Lead PLCC  | N84.1.15   |

| HSP43891GC-20 | 0 to 70                          | 85 Pin CPGA   | G85.A      |

| HSP43891GC-25 | 0 to 70                          | 85 Pin CPGA   | G85.A      |

| HSP43891GC-30 | 0 to 70                          | 85 Pin CPGA   | G85.A      |

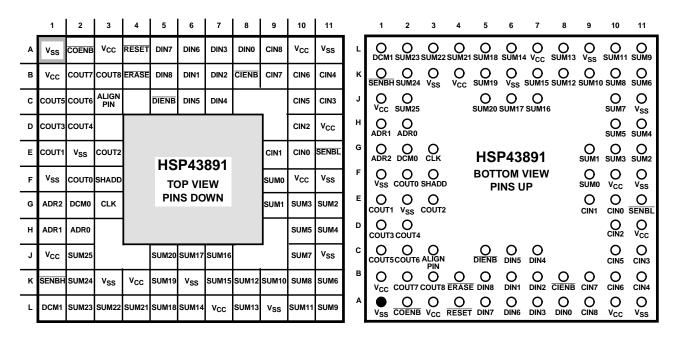

## Pinout

### 85 PIN GRID ARRAY (PGA)

84 LEAD PLASTIC LEADED CHIP CARRIER (PLCC)

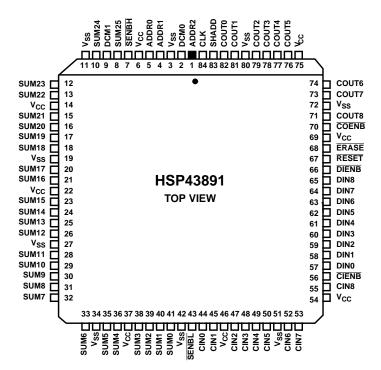

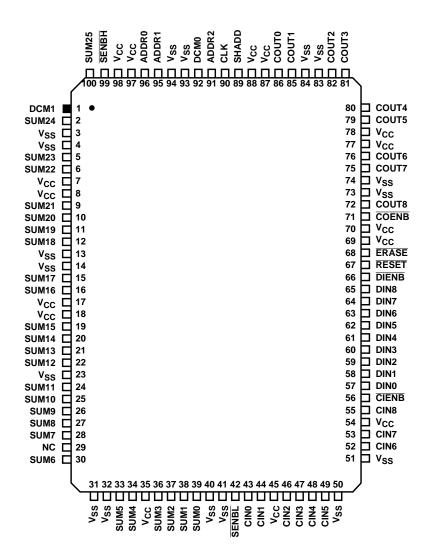

## **Pinout** (Continued)

100 LEAD MQFP TOP VIEW

# **Pin Description**

| SYMBOL          | PIN<br>NUMBER                               | TYPE |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                              |  |  |  |  |

|-----------------|---------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| V <sub>CC</sub> | B1, J1, A3, K4,<br>L7, A10, F10,<br>D11     |      | +5 power s                                                                                                                                                                                                                                                                                                                                                                             | +5 power supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

| V <sub>SS</sub> | A1, F1, E2, K3,<br>K6, L9, A11,<br>F11, J11 |      | Power supp                                                                                                                                                                                                                                                                                                                                                                             | Power supply ground input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

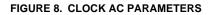

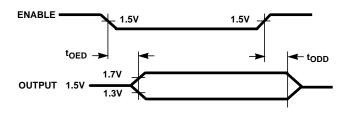

| CLK             | G3                                          | I    | The CLK in                                                                                                                                                                                                                                                                                                                                                                             | The CLK input provides the DF system sample clock. The maximum clock frequency is 30MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

| DIN0-8          | A5-8, B5-7, C6,<br>C7                       | I    | These nine inputs are the data sample input bus. Nine-bit data samples are synchronously loaded through these pins to the X register of each filter cell of the DF simultaneously. The DIENB signal enables loading, which is synchronous on the rising edge of the clock signal. The data samples can be either 9-bit two's complement or 8-bit unsigned values. For 9-bit two's com- |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      |                                                                                                                                                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | is the sign bit. For 8-bit unsigned values, DIN8                                                                                                                                                                                                                                                                                                                                          | •                                                                                                                                                                                            |  |  |  |  |

| DIENB           | C5                                          | I    | CLK signal<br>present on<br>CLK edge<br>latched insi<br>during the c                                                                                                                                                                                                                                                                                                                   | A low on this input enables the data sample input bus (DIN0-8) to all the filter cells. A rising edge of the CLK signal occurring while DIENB is low will load the X register of every filter cell with the 9-bit value present on DIN0-8. A high on this input forces all the bits of the data sample input bus to zero; a rising CLK edge when DIENB is high will load the X register of every filter cell with all zeros. This signal is latched inside the device, delaying its effect by one clock internal to the device. Therefore it must be low during the clock cycle immediately preceding presentation of the desired data on the DIN0-8 inputs. Detailed operation is shown in later timing diagrams. |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

| CIN0-8          | A9, B9-11, C10,<br>C11, D10, E9,<br>E10     | I    | These nine inputs are used to input the 9-bit coefficients. The coefficients are synchronously loaded into the C register of filter CELL0 if a rising edge of CLK occurs while CIENB is low. The CIENB signal is delayed by one clock as discussed below.<br>The coefficients can be either 9-bit two's complement or 8-bit unsigned values. For 9-bit two's comple-                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | he sign bit. For 8-bit unsigned values, CIN8 m                                                                                                                                                                                                                                                                                                                                            | -                                                                                                                                                                                            |  |  |  |  |

| ALIGN PIN       | C3                                          |      |                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | on socket or printed circuit board. This pin mus                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                              |  |  |  |  |

| CIENB           | B8                                          | I    | filter cell ac<br>CIENB is lo<br>their inputs<br>high on this<br>This signal<br>clock cycle                                                                                                                                                                                                                                                                                            | cording to<br>ow will load<br>This provi<br>is input free<br>is latched<br>immediate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ables the C register of every filter cell and the<br>the state of the DCM0-1 inputs. A rising edge<br>the C register and appropriate D registers w<br>des the mechanism for shifting coefficients fror<br>zes the contents of the C register and the D r<br>and delayed by one clock internal to the DF. The<br>preceding presentation of the desired coeffici-<br>later timing diagrams. | of the CLK signal occurring while<br>ith the coefficient data present at<br>n cell to cell through the device. A<br>egisters, ignoring the CLK signal.<br>herefore it must be low during the |  |  |  |  |

| COUT0-8         | B2, B3, C1, D1,<br>E1, C2, D2, F2,<br>E3    | 0    | are enabled                                                                                                                                                                                                                                                                                                                                                                            | the $\overline{CC}$ to coefficit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e outputs are used to output the 9-bit coefficient<br>DENB signal low. These outputs may be tied to<br>cients, or they may be tied to the CIN0-8 inputs                                                                                                                                                                                                                                   | the CIN0-8 inputs of the same DF                                                                                                                                                             |  |  |  |  |

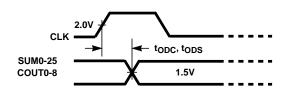

| COENB           | A2                                          | Ι    | A low on th in their high                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | input enables the COUT0-8 outputs. A high on<br>e state.                                                                                                                                                                                                                                                                                                                                  | this input places all these outputs                                                                                                                                                          |  |  |  |  |

| DCM0-1          | L1, G2                                      | I    | These two                                                                                                                                                                                                                                                                                                                                                                              | inputs dete                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | rmine the use of the internal decimation regist                                                                                                                                                                                                                                                                                                                                           | ers as follows:                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      | DCM1                                                                                                                                                                                                                                                                                                                                                                                   | DCM0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | DECIMATION FUNCTION                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      | 0                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Decimation registers not used                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      | 0 1 One decimation register is used                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      | 1                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Two decimation registers are used                                                                                                                                                                                                                                                                                                                                                         | -                                                                                                                                                                                            |  |  |  |  |

|                 |                                             |      | 1 1 Three decimation registers are used                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                              |  |  |  |  |

|                 |                                             |      | When no d decimation                                                                                                                                                                                                                                                                                                                                                                   | ecimation i register is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | from cell to cell at a rate determined by the nun<br>registers are used, coefficients move from cell<br>used, coefficients move from cell to cell on eve<br>ed by one clock internal to the device.                                                                                                                                                                                       | to cell on each clock. When one                                                                                                                                                              |  |  |  |  |

## Pin Description (Continued)

| SYMBOL  | PIN<br>NUMBER                                                                            | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUM0-25 | F9, G9-G11,<br>H10, H11, J2,<br>J5-J7, J10, K2,<br>K5, K7-K11,<br>L2-L6, L8, L10,<br>L11 | 0    | These 26 three-state outputs are used to output the results of the internal filter cell computations. Indi-<br>vidual filter cell results or the result of the shift and add output stage can be output. If an individual filter<br>cell result is to be output, the ADR0-2 signals select the filter cell result. The SHADD signal determines<br>whether the selected filter cell result or the output stage adder result is output. The signals <u>SENBH</u> and<br><u>SENBL</u> enable the most significant and least significant bits of the SUM0-25 result respectively. Both<br><u>SENBH</u> and <u>SENBL</u> may be enabled simultaneously if the system has a 26-bit or larger bus. However<br>individual enables are provided to facilitate use with a 16-bit bus.                                |

| SENBH   | K1                                                                                       | I    | A low on this input enables result bits SUM16-25. A high on this input places these bits in their high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SENBL   | E11                                                                                      | I    | A low on this input enables result bits SUM0-15. A high on this input places these bits in their high impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADR0-2  | G1, H1, H2                                                                               | I    | These three inputs select the one cell whose accumulator will be read through the output bus (SUM0-25) or added to the output stage accumulator. They also determine which accumulator will be cleared when ERASE is low. These inputs are latched in the DF and delayed by one clock internal to the device. If ADR0-2 remains at the same address for more than one clock, the output at SUM0-25 will not change to reflect any subsequent accumulator updates in the addressed cell. Only the result available during the first clock, when ADR0-2 selects the cell, will be output. This does not hinder normal operation since the ADR0-2 lines are changed sequentially. This feature facilitates the interface with slow memories where the output is required to be fixed for more than one clock. |

| SHADD   | F3                                                                                       | I    | The SHADD input controls the activation of the shift and add operation in the output stage. This signal is latched on chip and delayed by one clock internal to the device. Detailed explanation is given in the DF Output Stage section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RESET   | A4                                                                                       | I    | A low on this input synchronously clears all the internal registers, except the cell accumulators It can be used with ERASE to also clear all the accumulators simultaneously. This signal is latched in the DF and delayed by one clock internal to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ERASE   | B4                                                                                       | I    | A low on this input synchronously clears the cell accumulator selected by the ADR0-2 signals. If RESET is also low simultaneously, all cell accumulators are cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# **Functional Description**

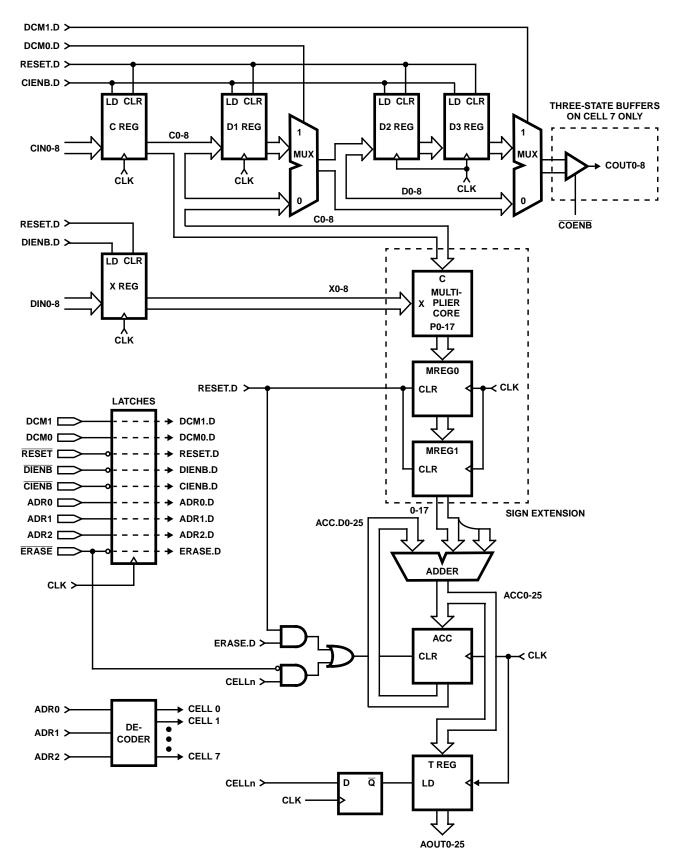

The Digital Filter Processor (DF) is composed of eight filter cells cascaded together and an output stage for combining or selecting filter cell outputs (See Block Diagram). Each filter cell contains a multiplier-accumulator and several registers (Figure 1). Each 9-bit coefficient is multiplied by a 9-bit data sample, with the result added to the 26-bit accumulator contents. The coefficient output of each cell is cascaded to the coefficient input of the next cell to its right.

# DF Filter Cell

A 9-bit coefficient (CIN0-8) enters each cell through the C register on the left and exits the cell on the right as signals COUT0-8. With no decimation, the coefficient moves directly from the C register to the output, and is valid on the clock following its entrance. When decimation is selected the coefficient exit is delayed by 1, 2 or 3 clocks by passing through one or more decimation registers (D1, D2 or D3).

The combination of D registers through which the coefficient passes is determined by the state of DCM0 and DCM1. The output signals (COUT0-8) are connected to the CIN0-8 inputs of the next cell to its right. The COENB input signal enables the COUT0-8 outputs of the right most cell to the COUT0-8 pins of the device.

The C and D registers are enabled for loading by CIENB. Loading is synchronous with CLK when CIENB is low. Note that CIENB is latched internally. It enables the register for loading after the next CLK following the onset of CIENB low. Actual loading occurs on the second CLK following the onset of CIENB low. Therefore CIENB must be low during the clock cycle immediately preceding presentation of the coefficient on the CINO-8 inputs. In most basic FIR operations, CIENB will be low throughout the process, so this latching and delay sequence is only important during the initialization phase. When CIENB is high, the coefficients are frozen.

The C and D registers are cleared synchronously under control of  $\overrightarrow{\text{RESET}}$ , which is latched and delayed exactly like  $\overrightarrow{\text{CIENB}}$ . The output of the C register (C0-8) is one input to 9 x 9 multiplier.

The other input to the 9 x 9 multiplier comes from the output of the X register. This register is loaded with a data sample from the device input signals DIN0-8 discussed above. The X register is enabled for loading by DIENB. Loading is synchronous with CLK when DIENB is low. Note that DIENB is latched internally. It enables the register for loading after the next CLK following the onset of DIENB low. Actual loading occurs on the second CLK following the onset of DIENB low; therefore, DIENB must be low during the clock cycle immediately preceding presentation of the data sample on the DIN0-8 inputs. In most basic FIR operations,  $\overline{\text{DIENB}}$ will be low throughout the process, so this latching and delay sequence is only important during the initialization phase. When  $\overline{\text{DIENB}}$  is high, the X register is loaded with all zeros.

The multiplier is pipelined and is modeled as a multiplier core followed by two pipeline registers, MREG0 and MREG1 (Figure 1). The multiplier output is sign extended and input as one operand of the 26-bit adder. The other adder operand is the output of the 26-bit accumulator. The adder output is loaded synchronously into both the accumulator and the TREG.

The TREG loading is disabled by the cell select signal, CELLn, where n is the cell number. The cell select is decoded from the ADR0-2 signals to generate the TREG load enable. The cell select is inverted and applied as the load enable to the TREG. Operation is such that the TREG is loaded whenever the cell is not selected. Therefore, TREG is loaded every clock except the clock following cell selection. The purpose of the TREG is to hold the result of a sum-ofproducts calculation during the clock when the accumulator is cleared to prepare for the next sum-of-products calculation. This allows continuous accumulation without wasting clocks.

The accumulator is loaded with the adder output every clock unless it is cleared. It is cleared synchronously in two ways. When  $\overrightarrow{\text{RESET}}$  and  $\overrightarrow{\text{ERASE}}$  are both low, the accumulator is cleared along with all other registers on the device. Since  $\overrightarrow{\text{ERASE}}$  and  $\overrightarrow{\text{RESET}}$  are latched and delayed one clock internally, clearing occurs on the second CLK following the onset of both  $\overrightarrow{\text{ERASE}}$  and  $\overrightarrow{\text{RESET}}$  low.

The second accumulator clearing mechanism clears a single accumulator in a selected cell. The cell select signal, CELLn, decoded from ADR0-2 and the  $\overline{\text{ERASE}}$  signal enable clearing of the accumulator on the next CLK.

The ERASE and RESET signals clear the DF internal registers and states as follows:

| ERASE | RESET | CLEARING EFFECT                                                                                                        |

|-------|-------|------------------------------------------------------------------------------------------------------------------------|

| 1     | 1     | No clearing occurs, internal state remains same.                                                                       |

| 1     | 0     | RESET only active, all registers except ac-<br>cumulators are cleared, including the inter-<br>nal pipeline registers. |

| 0     | 1     | ERASE only active, the accumulator whose address is given by the ADR0-2 inputs is cleared.                             |

| 0     | 0     | Both RESET and ERASE active, all accu-<br>mulators as well as all other registers are<br>cleared.                      |

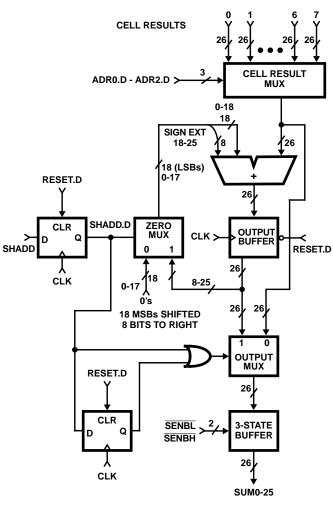

# The DF Output Stage

The output stage consists of a 26-bit adder, 26-bit register, feedback multiplexer from the register to the adder, an output multiplexer and a 26-bit three-state driver stage (Figure 2).

The 26-bit output adder can add any filter cell accumulator result to the 18 most significant bits of the output buffer. This result is stored back in the output buffer. This operation takes place in one clock period. The eight LSBs of the output buffer are lost. The filter cell accumulator is selected by the ADR0-2 inputs.

The 18 MSBs of the output buffer actually pass through the zero mux on their way to the output adder input. The zero mux is controlled by the SHADD input signal and selects either the output buffer 18 MSBs or all zeros for the adder input. A low on the SHADD input selects zero. A high on the SHADD input selects the output buffer MSBs, thus, activating the shift-and-add operation. The SHADD signal is latched and delayed by one clock internally.

FIGURE 1. HSP43891 DF FILTER CELL

FIGURE 2. HSP43891 DFP OUTPUT STAGE

The 26 least significant bits (LSBs) from either a cell accumulator or the output buffer are output on the SUM0-25 bus. The output mux determines whether the cell accumulator selected by ADR0-2 or the output buffer is output to the bus. This mux is controlled by the SHADD input signal. Control is based on the state of the SHADD during two successive clocks; in other words, the output mux selection contains memory. If SHADD is low during a clock cycle and was low during the previous clock, the output mux selects the contents of the filter cell accumulator addressed by ADR0-2. Otherwise the output mux selects the contents of the output buffer.

If the ADR0-2 lines remain at the same address for more than one clock, the output at SUM0-25 will not change to reflect any subsequent accumulator updates in the addressed cell. Only the result available during the first clock when ADR0-2 selects the cell will be output.

This does not hinder normal FIR operation since the ADR0-2 lines are changed sequentially. This feature facilitates the interface with slow memories where the output is required to be fixed for more than one clock.

The SUM0-25 output bus is controlled by the  $\overline{SENBH}$  and  $\overline{SENBL}$  signals. A low on  $\overline{SENBL}$  enables bits SUM0-15. A low on  $\overline{SENBH}$  enables bits SUM16-25. Thus, all 26 bits can be output simultaneously if the external system has a 26-bit or larger bus. If the external system bus is only 16 bits, the bits can be enabled in two groups of 16 and 10 bits (sign extended).

# DF Arithmetic

Both data samples and coefficients can be represented as either 8-bit unsigned or 9-bit two's complement numbers. The 9x9 bit multiplier in each cell expects 9-bit two's complement operands. The binary format of 8-bit two's complement is shown below. Note that if the most significant or sign bit is held at logical zero, the 9-bit two's complement multiplier can multiply 8-bit unsigned operands. Only the upper (positive) half of the two's complement binary range is used.

The multiplier output is 18 bits and the accumulator is 26 bits. The accumulator width determines the maximum possible number of terms in the sum of products without overflow. The maximum number of terms depends also on the number system and the distribution of the coefficient and data values. Then maximum numbers of terms in the sum products are:

|                                                              | MAXIMUM # | OF TERMS |

|--------------------------------------------------------------|-----------|----------|

| NUMBER SYSTEM                                                | 8-BIT     | 9-BIT    |

| Two Unsigned Vectors                                         | 1032      | N/A      |

| Two Two's Complement Vectors                                 |           |          |

| Two Positive Vectors                                         | 2080      | 1032     |

| Negative Vectors                                             | 2047      | 1024     |

| One Positive and One Negative     Vector                     | 2064      | 1028     |

| One Unsigned 8-Bit Vector and One<br>Two's Complement Vector |           |          |

| Positive Two's Complement Vector                             | 1036      | 1032     |

| Negative Two's Complement Vector                             | 1028      | 1028     |

For practical FIR filters, the coefficients are never all near maximum value, so even larger vectors are possible in practice.

# **Basic FIR Operation**

A simple, 30MHz 8-tap filter example serves to illustrate more clearly the operation of the DF. The sequence table (Table 1) shows the results of the multiply accumulate in each cell after each clock. The coefficient sequence,  $C_N$ , enters the DF on the left and moves from left to right through the cells. The data sample sequence,  $X_N$ , enters the DF from the top, with each cell receiving the same sample simultaneously. Each cell accumulates the sum of products for one output point. Eight sums of products are calculated simultaneously, but staggered in time so that a new output is available every system clock.

# HSP43891

|                                    | IABLE 1. H                                                                          | 1SP43891 30M                                                                                                                                                                                                                                                   | HZ, 8-TAP FIR                                                                                                                                                                              | FILTER SEQUE                                                                                                                                                                                                                                                                                               | INCE                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X <sub>15</sub> X <sub>9</sub> , X | x <sub>8</sub> , x <sub>7</sub> x <sub>1</sub> , x <sub>0</sub>                     |                                                                                                                                                                                                                                                                | <b>+</b>                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                              |

| С <sub>0</sub> С <sub>6</sub> , С  | C <sub>7</sub> , C <sub>0</sub> C <sub>6</sub> , C <sub>7</sub>                     |                                                                                                                                                                                                                                                                | HSP43891                                                                                                                                                                                   | <b>→</b> ·                                                                                                                                                                                                                                                                                                 | Υ <sub>15</sub> , Υ <sub>14</sub> Υ                                                                                                                                                                                                                                                                                                                                                      | ′ <sub>8</sub> , Y <sub>7</sub>                                                                                                                                                                                                                                                                                              |

| CELL 1                             | CELL 2                                                                              | CELL 3                                                                                                                                                                                                                                                         | CELL 4                                                                                                                                                                                     | CELL 5                                                                                                                                                                                                                                                                                                     | CELL 6                                                                                                                                                                                                                                                                                                                                                                                   | CELL 7                                                                                                                                                                                                                                                                                                                       |

| 0                                  | 0                                                                                   | 0                                                                                                                                                                                                                                                              | -                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                            |

| C <sub>7</sub> x X <sub>1</sub>    | 0                                                                                   | 0                                                                                                                                                                                                                                                              | -                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                            |

| +C <sub>6</sub> x X <sub>2</sub>   | C <sub>7</sub> x X <sub>2</sub>                                                     | 0                                                                                                                                                                                                                                                              | -                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                          | -                                                                                                                                                                                                                                                                                                                                                                                        | -                                                                                                                                                                                                                                                                                                                            |

|                                    | C <sub>0</sub> C <sub>6</sub> , C<br>CELL 1<br>0<br>C <sub>7</sub> x X <sub>1</sub> | $\begin{array}{c} x_{15} \dots x_{9}, x_{8}, x_{7} \dots x_{1}, x_{0} \\ c_{0} \dots c_{6}, c_{7}, c_{0} \dots c_{6}, c_{7} \\ \hline $ | $x_{15} \dots x_9, x_8, x_7 \dots x_1, x_0$ $C_0 \dots C_6, C_7, C_0 \dots C_6, C_7$ CELL 1       CELL 2       CELL 3         0       0       0       0 $C_7 \times X_1$ 0       0       0 | X <sub>15</sub> X <sub>9</sub> , X <sub>8</sub> , X <sub>7</sub> X <sub>1</sub> , X <sub>0</sub> C <sub>0</sub> C <sub>6</sub> , C <sub>7</sub> HSP43891         CELL 1       CELL 2       CELL 3       CELL 4         0       0       0       -         C <sub>7</sub> x X <sub>1</sub> 0       0       - | X <sub>15</sub> X <sub>9</sub> , X <sub>8</sub> , X <sub>7</sub> X <sub>1</sub> , X <sub>0</sub> C <sub>0</sub> C <sub>6</sub> , C <sub>7</sub> , C <sub>0</sub> C <sub>6</sub> , C <sub>7</sub> HSP43891         CELL 1       CELL 2       CELL 3       CELL 4       CELL 5         0       0       0       -       -         C <sub>7</sub> x X <sub>1</sub> 0       0       -       - | $C_0 \dots C_6, C_7, C_0 \dots C_6, C_7 \longrightarrow HSP43891 \longrightarrow \dots Y_{15}, Y_{14} \dots Y_{15}, Y_{14} \dots Y_{15}$ CELL 1       CELL 2       CELL 3       CELL 4       CELL 5       CELL 6         0       0       0       -       -       -         C_7 x X_1       0       0       -       -       - |

C<sub>7</sub> x X<sub>3</sub>

+C<sub>6</sub> x X<sub>3</sub>

+C<sub>5</sub> x X<sub>3</sub>

SUM/CLR -

-

-

-

CLK

0

1

2

3

+C<sub>4</sub> x X<sub>3</sub>

| 4  | +C <sub>3</sub> x X <sub>4</sub>  | +C <sub>4</sub> x X <sub>4</sub>  | +C <sub>5</sub> x X <sub>4</sub>  | +C <sub>6</sub> x X <sub>4</sub>  | C <sub>7</sub> x X <sub>4</sub>   | -                                 | -                                 | -                                 | -                         |

|----|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|-----------------------------------|---------------------------|

| 5  | +C <sub>2</sub> x X <sub>5</sub>  | +C <sub>3</sub> x X <sub>5</sub>  | +C <sub>4</sub> x X <sub>5</sub>  | +C <sub>5</sub> x X <sub>5</sub>  | +C <sub>6</sub> x X <sub>5</sub>  | C <sub>7</sub> x X <sub>5</sub>   | -                                 | -                                 | -                         |

| 6  | +C <sub>1</sub> x X <sub>6</sub>  | +C <sub>2</sub> x X <sub>6</sub>  | +C <sub>3</sub> x X <sub>6</sub>  | +C <sub>4</sub> x X <sub>6</sub>  | +C <sub>5</sub> x X <sub>6</sub>  | +C <sub>6</sub> x X <sub>6</sub>  | С <sub>7</sub> х Х <sub>6</sub>   | -                                 | -                         |

| 7  | +C <sub>0</sub> x X <sub>7</sub>  | +C <sub>1</sub> x X <sub>7</sub>  | +C <sub>2</sub> x X <sub>7</sub>  | +C <sub>3</sub> x X <sub>7</sub>  | +C <sub>4</sub> x X <sub>7</sub>  | +C <sub>5</sub> x X <sub>7</sub>  | +C <sub>6</sub> x X <sub>7</sub>  | C <sub>7</sub> x X <sub>7</sub>   | Cell 0 (Y <sub>7</sub> )  |

| 8  | C <sub>7</sub> x X <sub>8</sub>   | +C <sub>0</sub> x X <sub>8</sub>  | +C <sub>1</sub> x X <sub>8</sub>  | +C <sub>2</sub> x X <sub>8</sub>  | +C <sub>3</sub> x X <sub>8</sub>  | +C <sub>4</sub> x X <sub>8</sub>  | +C <sub>5</sub> x X <sub>8</sub>  | +C <sub>6</sub> x X <sub>8</sub>  | Cell 1 (Y <sub>8</sub> )  |

| 9  | +C <sub>6</sub> x X <sub>9</sub>  | С <sub>7</sub> х Х <sub>9</sub>   | +C <sub>0</sub> x X <sub>9</sub>  | +C <sub>1</sub> x X <sub>9</sub>  | +C <sub>2</sub> x X <sub>9</sub>  | +C <sub>3</sub> x X <sub>9</sub>  | +C <sub>4</sub> x X <sub>9</sub>  | +C <sub>5</sub> x X <sub>9</sub>  | Cell 2 (Y <sub>9</sub> )  |

| 10 | +C <sub>5</sub> x X <sub>10</sub> | +C <sub>6</sub> x X <sub>10</sub> | C <sub>7</sub> x X <sub>10</sub>  | +C <sub>0</sub> x X <sub>10</sub> | +C <sub>1</sub> x X <sub>10</sub> | +C <sub>2</sub> x X <sub>10</sub> | +C <sub>3</sub> x X <sub>10</sub> | +C <sub>4</sub> x X <sub>10</sub> | Cell 3 (Y <sub>10</sub> ) |

| 11 | +C <sub>4</sub> x X <sub>11</sub> | +C <sub>5</sub> x X <sub>11</sub> | +C <sub>6</sub> x X <sub>11</sub> | C <sub>7</sub> x X <sub>11</sub>  | +C <sub>0</sub> x X <sub>11</sub> | +C <sub>1</sub> x X <sub>11</sub> | +C <sub>2</sub> x X <sub>11</sub> | +C <sub>3</sub> x X <sub>11</sub> | Cell 4 (Y <sub>11</sub> ) |

| 12 | +C <sub>3</sub> x X <sub>12</sub> | +C <sub>4</sub> x X <sub>12</sub> | +C <sub>5</sub> x X <sub>12</sub> | +C <sub>6</sub> x X <sub>12</sub> | C <sub>7</sub> x X <sub>12</sub>  | +C <sub>0</sub> x X <sub>12</sub> | +C <sub>1</sub> x X <sub>12</sub> | +C <sub>2</sub> x X <sub>12</sub> | Cell 5 (Y <sub>12</sub> ) |

| 13 | +C <sub>2</sub> x X <sub>13</sub> | +C <sub>3</sub> x X <sub>13</sub> | +C <sub>4</sub> x X <sub>13</sub> | +C <sub>5</sub> x X <sub>13</sub> | +C <sub>6</sub> x X <sub>13</sub> | C <sub>7</sub> x X <sub>13</sub>  | +C <sub>0</sub> x X <sub>13</sub> | +C <sub>1</sub> x X <sub>13</sub> | Cell 6 (Y <sub>13</sub> ) |

| 14 | +C <sub>1</sub> x X <sub>14</sub> | +C <sub>2</sub> x X <sub>14</sub> | +C <sub>3</sub> x X <sub>14</sub> | +C <sub>4</sub> x X <sub>14</sub> | +C <sub>5</sub> x X <sub>14</sub> | +C <sub>6</sub> x X <sub>14</sub> | +C <sub>7</sub> x X <sub>14</sub> | +C <sub>0</sub> x X <sub>14</sub> | Cell 7 (Y <sub>14</sub> ) |

| 15 | +C <sub>0</sub> x X <sub>15</sub> | +C <sub>1</sub> x X <sub>15</sub> | +C <sub>2</sub> x X <sub>15</sub> | +C <sub>3</sub> x X <sub>15</sub> | +C <sub>4</sub> x X <sub>15</sub> | +C <sub>5</sub> x X <sub>15</sub> | +C <sub>6</sub> x X <sub>15</sub> | C <sub>7</sub> x X <sub>15</sub>  | Cell 0 (Y <sub>15</sub> ) |

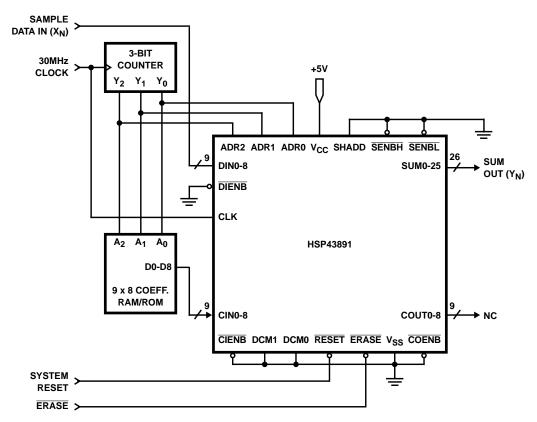

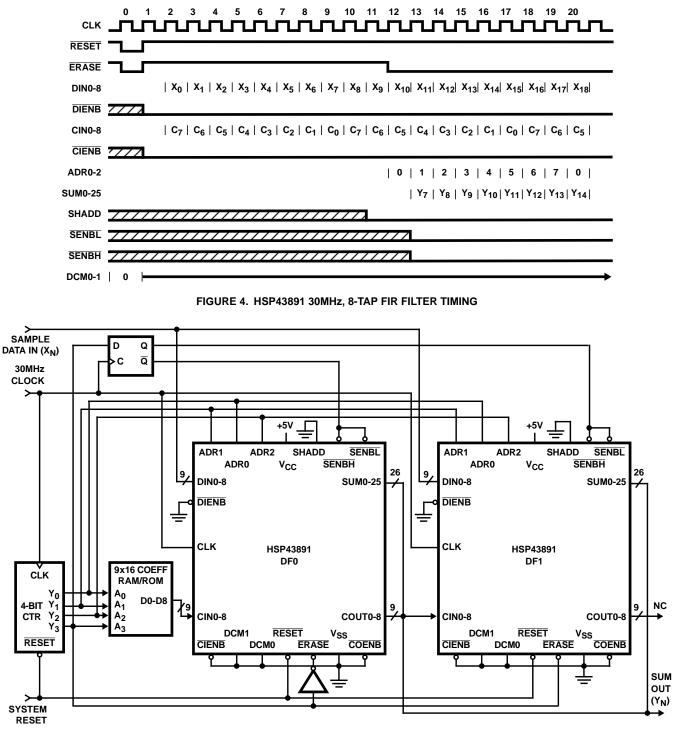

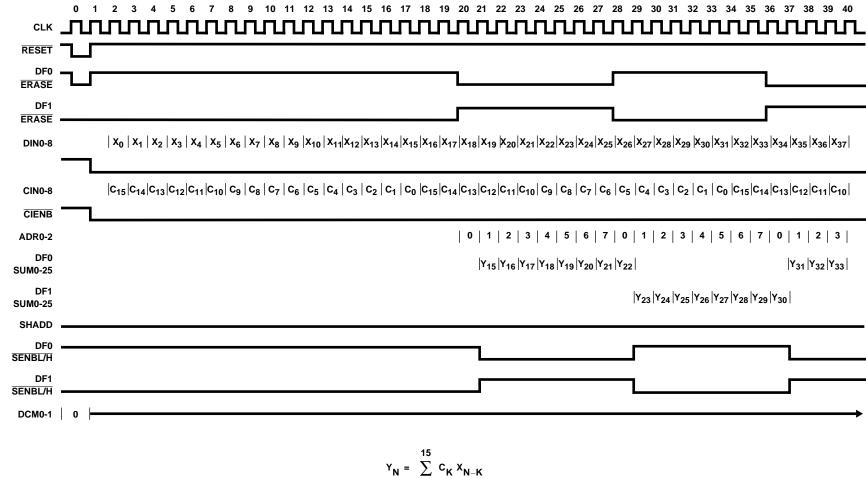

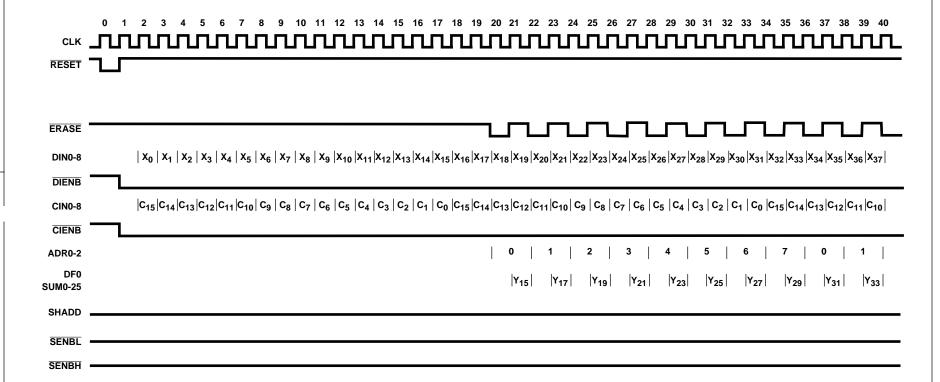

Detailed operation of the DF to perform a basic 8-tap, 9-bit coefficient, 9-bit data, 30MHz FIR filter is best understood by observing the schematic (Figure 3) and timing diagram (Figure 4). The internal pipeline length of the DF is four (4) clock cycles, corresponding to the register levels CREG (or XREG), MREG0, MREG1, and TREG (Figures 1 and 2). Therefore, the delay from presentation of data and coefficients at the DIN0-8 and CIN0-8 inputs to a sum appearing at the SUM0-25 output is: k + Td, where k = filter

length and Td = 4, the internal pipeline delay of the DF. After the pipeline has filled, a new output sample is available every clock. The delay to last sample output from last sample input is Td. The output sums,  $Y_N$ , shown in the timing diagram are derived from the sum-of-products equation.

$$Y_{N} = \sum_{K=0}^{7} C_{K} X_{N-K}$$

# Extended FIR Filter Length Filter

lengths greater that eight taps can be created by either cascading together multiple DF devices or "reusing" a single device. Using multiple devices, an FIR filter of over 1000 taps can be constructed to operate at a 30MHz sample rate. Using a single device clocked at 30MHz, an FIR filter of over 500 taps can be constructed to operate at less than a 30MHz sample rate. Combinations of these two techniques are also possible.

# Cascade Configuration

To design a filter length L>8, L/8 DFs are cascaded by connecting the COUT0-8 outputs of the (i)th DF to the CIN0-8 inputs of the (i+1)th DF. The DIN0-8fs inputs and SUM0-25 outputs of all the DFs are also tied together. A specific example of two cascaded DFs illustrates the technique (Figure 5). Timing (Figure 6) is similar to the simple 8-tap FIR, except the ERASE and SENBL/SENBH signals must be enabled independently for the two DFs in order to clear the correct accumulators and enable the SUM0-25 output signals at the proper times.

| CLK | CELL 0                             | CELL 1                            | CELL 2                             | CELL 3                             | CELL 4                             | CELL 5                             | CELL 6                             | CELL 7                             | SUM/CLR                 |