# **SP9685**

#### **ULTRA FAST COMPARATOR**

The SP9685 is an ultra-fast comparator manufactured with a high performance bipolar process which makes possible very short propagation delays (2.2ns typ.). The circuit has differential inputs and complementary outputs fully compatible with ECL logic levels. The output current capability is adequate for driving 50Ω terminated transmission lines. The high resolution available makes the device ideally suited to analog-to-digital signal processing applications.

A latch function is provided to allow the comparator to be used in a sample-hold mode. When the latch enable input is ECL high, the comparator functions normally. When the latch enable is driven low, the outputs are forced to an unambiguous ECL logic state dependent on the input conditions at the time of the latch input transition. If the latch function is not used, the latch enable may be connected to

The device is pin compatible with the AM685 but operates from conventional +5V and -5.2V rails. It is pin and voltage compatible with AD9685.

#### **FEATURES**

- Propagation Delay 2.2ns Typ.

- Latch Set-up Time 1ns Max.

- Complementary ECL Outputs

- Supply +5V, -5.2V (±0.25V)

- 50 ohm Line Driving Capability

- Excellent Common Mode Rejection

- Operating Temperature Range : SP9685 -30°C to +85°C SP9685AC -55°C to +125°C

- Pin Compatible with AD9685

- Pin Compatible with AM685 But Faster

### **APPLICATIONS**

- Ultra High Speed A/D Converter

- Ultra High Speed Line Receivers

- **Peak Detectors**

- Threshold Detectors

## **ORDERING INFORMATION**

SP9685CM (Industrial - Cylindrical Metal package) SP9685DG (Industrial - Ceramic DIL package) SP9685BB DG (Plessey High Reliability Ceramic DIL package)

SP9685MP (Industrial - Miniature Plastic package) SP9685AC DG (Military - Ceramic DIL package)

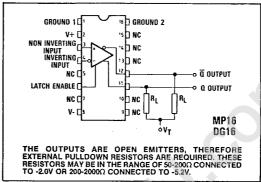

Fig.1 DIL pin connections (top view) and function diagram

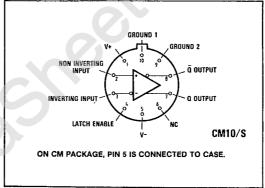

Fig.2 Metal package (CM10/S) pin connections (top veiw)

31 Sheethii. Com The AC version of this product conforms to MIL-STD-883C CLASS B screening and is covered by separate data which observes the change notification requirements of MIL-M-38510 and is published in the 'MIL-STD-883C CLASS B Integrated Circuit' Handbook. Please consult your nearest Plessey sales office.

### SP9685

T-73-53

### **ABSOLUTE MAXIMUM RATINGS**

| Postive supply voltage Negative supply voltage Output current Input voltage Differential input voltage Power dissipation | 6V<br>-6V<br>30mA<br>±3V<br>3.5V<br>350mW | Storage temperature range<br>Operating junction temperature<br>Lead temperature (soldering 60 sec)<br>Vibration<br>Shock 14700m/s <sup>2</sup> | -55° C to +150° C<br><175° C<br>300° C<br>196m/s²<br>peak 0.5ms duration |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated): Vcc = 5.00V;  $V\epsilon\epsilon = -5.2V$ ;  $R\iota = 50\Omega$ ;  $V\tau = 2.0V$  (see Fig.1)

| Characteristic                 |          | Value |        | Units | Conditions                                      |

|--------------------------------|----------|-------|--------|-------|-------------------------------------------------|

|                                | Min.     | Тур.  | Max.   | Uins  | Ochanions .                                     |

| Input offset voltage           | -5       |       | +5     | mV    | Rs < 100Ω 25 °C                                 |

| par amara sanaga               | -7       |       | +7     | mV    | Rs < 100Ω                                       |

| Input bias current             |          |       | 20     | μΑ    | 25°C                                            |

|                                |          |       | 30     | μΑ    |                                                 |

| Input offset current           |          |       | 5      | μΑ    | 25 °C                                           |

|                                |          |       | 8      | μΑ    |                                                 |

| Supply current les             |          |       | 34     | mA    | 25°C                                            |

|                                |          | j     | 36     | mA    |                                                 |

| Supply current Icc             |          |       | 23     | mA    | 25°C                                            |

|                                |          |       | 24     | mA    | 25°C                                            |

| Total power dissipation        | 210      |       | 350    | mW    | 25°C Note 3                                     |

| Common mode range              | -2.5     |       | +2.5   | V     |                                                 |

| Output logic levels            |          |       |        |       | ·                                               |

| Output high                    | -0.96    |       | -0.81  | V     | 25°C                                            |

|                                | -1.045   |       | -0.875 | V     | T <sub>amb</sub> = Min.                         |

|                                | -0.89    |       | -0.70  | V     | T <sub>amb</sub> = Max.                         |

| Output low                     | -1.85    |       | -1.65  | V     | 25°C                                            |

|                                | -1.89    | 1     | -1.65  | V     | T <sub>amb</sub> = Min. T <sub>amb</sub> = Max. |

|                                | -1.83    |       | -1.575 | V     |                                                 |

| Min. latch set up time         |          |       | 1      | ns    | Notes 1, 2, 3 25°C                              |

|                                |          |       | 2      | ns    |                                                 |

| Input to output delay          |          |       | 3      | ns    | Note 1, 3 (Q and Q) 25°C                        |

|                                |          |       | 4      | ns    | <del>.</del>                                    |

| Latch to output delay          |          |       | 3      | ns    | Notes 1, 2, 3 (Q and Q) 25°C                    |

|                                |          |       | 4.5    | ns    |                                                 |

| Minimum latch pulse width      |          | 1     | 3      | ns    | Note 3 25°C                                     |

| Minimum hold time              | ļ        |       | 1      | ns    | Note 3 25°C                                     |

| Max. input capacitance         |          | 3     | 1.0    | pF    | Note 3 25°C<br>Note 3 25°C                      |

| Input resistance               | 60<br>70 |       | kΩ     | dB    | Note 3 25°C                                     |

| Common mode rejection ratio    | 50       |       |        | dB    | Note 3 25 °C                                    |

| Supply voltage rejection ratio |          |       |        |       | 1.0000                                          |

NOTES

1. · 100mV pulse with - 10mV overdrive.

2. Switching measurements involving the latch are particularly difficult to perform and cannot be tested in production. Circuit analysis shows that at least 95% of devices will meet these specifications.

3. Guaranteed but not tested.

Thermal characteristics

| CM10 | $oldsymbol{	heta}$ JA | 220°C/W |

|------|-----------------------|---------|

|      | $\theta$ JC           | 65°C/W  |

| DG16 | $oldsymbol{	heta}$ JA | 120°C/W |

|      | $\theta$ JC           | 40°C/W  |

| LC20 | $oldsymbol{	heta}$ JA | 73°C/W  |

|      | $\theta$ JC           | 22°C/W  |

SP9685

Fig.3 Timing diagram

#### **OPERATING NOTES**

Timing diagram

The timing diagram, Fig. 3, shows in graphic form a sequence of events in the SP9685. It should not be interpreted as 'typical' in that several parameters are multivalued and the worst case conditions are illustrated. The top line shows two latch enable pulses, high for 'compare', and low for latch. The first pulse is used to highlight the 'compare' function, where part of the input action takes place in the compare mode. The leading edge of the input signal, here illustrated as a large amplitude, small overdrive pulse switches the comparator over after a time tpd. Output Q and Q transitions are essentially similar in timing. The input signal must occur at a time ts before the latch falling edge, and must be maintained for a time thafter the latch falling edge, in order

to be acquired. After  $t_h$ , the output ignores the input status until the latch is again strobed. A minimum latch pulse width  $t_{\text{PW}(E)}$  is required for the strobe operation, and the output transitions occur after a time  $t_{\text{pd}(E)}$ .

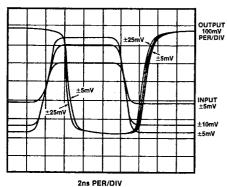

Measurement of propagation and latch delays

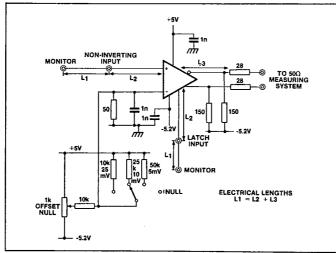

A simple test circuit is shown in Fig.4. The operating sequence is:

- Power up and apply input and latch signals. Input = 100mV square wave, latch ECL levels. Connect monitoring scope(s).

- Select 'offset null'.

- Adjust offset null potentiometer for an output which switches evenly between states on clock pulses.

- Measure input/output and latch/output delays at 5mV offset, 10mV offset and 25mV offset.

Fig.4 SP9685 test circuit

Fig.5 Open loop gain as a function of frequency

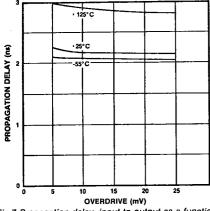

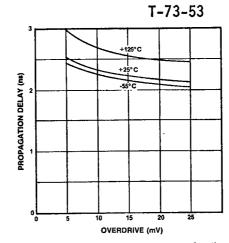

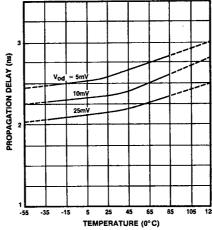

Fig.7 Propagation delay, input to output as a function of overdrive

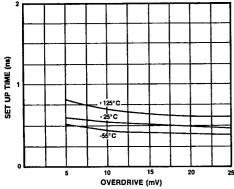

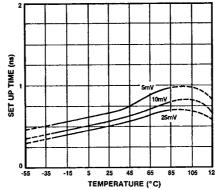

Fig.9 Set-up time as a function of input overdrive

Fig.6 Propagation delay, latch to output as a function of

Fig.8 Set-up time as a function of temperature

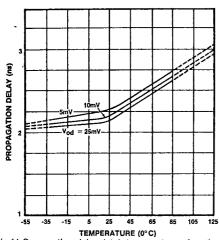

Fig.10 Propagation delay, input to output as a function of temperature

Fig.11 Propagation delay, latch to output as a function of temperature

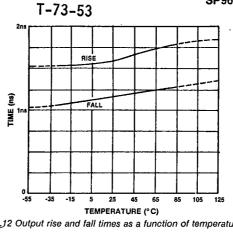

Fig. 12 Output rise and fall times as a function of temperature

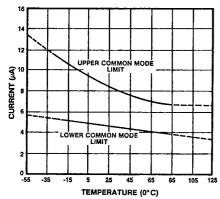

Fig.13 Input bias currents as a function of temperature

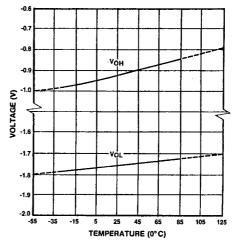

Fig.14 Output levels as a function of temperature

Fig.15 Response to various input signal levels