# 12 V High-Side Hot-Swap Hall Effect Based Current Monitor

#### **Features and Benefits**

- Hall-effect current monitor—no external sense resistor required

- Analog output voltage (factory trimmed for gain and offset) proportional to applied current

- External high-side FET gate drive

- 240V\*A Power Fault Protection with user-programmable delay

- User programmable Overcurrent Fault Protection with programmable delay

- 1.5 m $\Omega$  internal conductor resistance

- Short Circuit Protection isolates failed supply from output in < 2 μs</li>

- Active low Fault indicator output signal

- External FET failure detection with active low S1 Short failure indicator output signal

- User controlled soft start / hot-swap function

- Logic enable input pin

- 10.8 to 13.2 V, single-supply operation

- 2 kV ESD protection for all pins

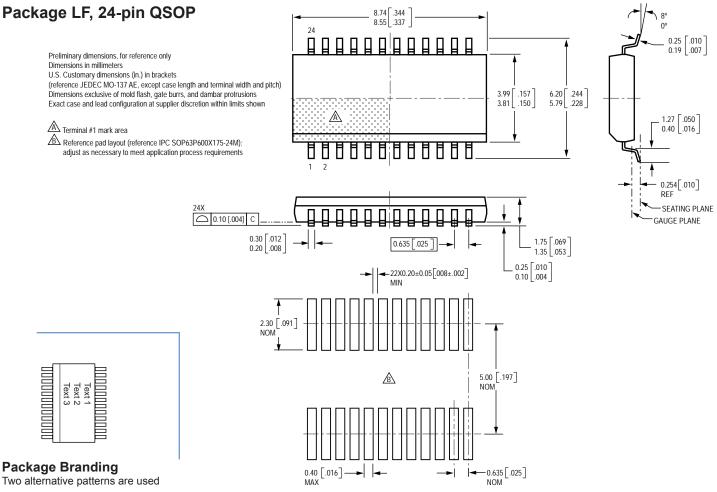

### Package: 24 pin QSOP (suffix LF)

Approximate Scale

#### **Description**

The ACS760 combines Allegro® Hall-effect current sense technology with a hot-swap controller resulting in a more efficient integrated controller for 12 V applications. By eliminating the need for a shunt resistor, the I²R losses in the power path are reduced.

When the ACS760 is externally enabled, and the voltage rail is above the internal UVLO threshold, the internal charge pump drives the gate of the external FET. When a fault is detected, the gate is disabled while simultaneously alerting the application that a fault has occurred.

The integrated protection in the ACS760 incorporates three levels of fault protection, which includes a Power Fault with user-programmable delay, a user-programmable Overcurrent Fault threshold with programmable delay, and Short Circuit protection, which disables the gate in less then 2 µs.

Additionally, in the event the external high-side FET fails short, the ACS760 detects the S1 Short failure and immediately disables the gate and alerts the host system. Unlike the three protection faults, cycling the EN pin does not reset the S1 Short failure. Power to the device must be cycled.

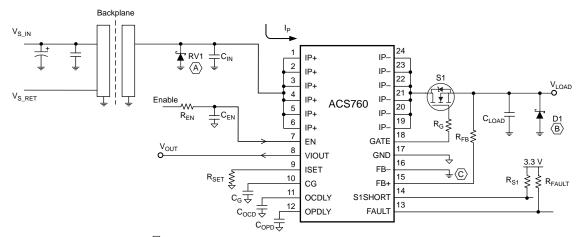

### **Typical Application**

- RV1 is required only for inductive loads.

- B D1 should be a Schottky for inductive loads, to eliminate over-stress of the ACS760.

- © FB- is tied to GND at the point of load.

#### **Selection Guide**

| Part Number       | Package              | Packing*         |

|-------------------|----------------------|------------------|

| ACS760ELF-20BTR-T | QSOP24 surface mount | 2500 pieces/reel |

<sup>\*</sup>Contact Allegro for additional packing options

#### **Absolute Maximum Ratings**

| inscription in statement in the statemen |                            |             |            |       |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------|------------|-------|--|

| Characteristic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Symbol                     | Notes       | Rating     | Units |  |

| Forward Voltage, IPx pins*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>CC</sub>            |             | 24         | V     |  |

| GATE Drive Output Voltage*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $V_{GATE}$                 |             | 32         | V     |  |

| FB+ Forward Voltage*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | V <sub>FB+</sub>           |             | 24         | V     |  |

| EN Forward Voltage*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>EN</sub>            |             | 32         | V     |  |

| All Other Pins Forward Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>IN</sub>            |             | 8          | V     |  |

| Reverse DC Voltage, All Pins*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V <sub>R</sub>             |             | -0.5       | V     |  |

| Reverse Transient DC Voltage, All Pins*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>r</sub>             | 10 µs pulse | -5         | V     |  |

| Current Sense Output Current Source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I <sub>VIOUT(Source)</sub> |             | 1          | mA    |  |

| Current Sense Output Current Sink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>VIOUT(Sink)</sub>   |             | 1          | mA    |  |

| Operating Ambient Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | T <sub>A</sub>             | Range E     | -40 to 85  | °C    |  |

| Maximum Junction Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | T <sub>J</sub> (max)       |             | 165        | °C    |  |

| Storage Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | T <sub>stg</sub>           |             | -65 to 170 | °C    |  |

<sup>\*</sup> With respect to GND.

## ACS760ELF-20B

# 12 V High-Side Hot-Swap Hall Effect Based Current Monitor

#### **Pin-out Diagram**

#### **Terminal List Table**

| Terminal List Table |         |                                                                                                                                                                                                                                                                                                                                   |  |  |  |

|---------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Number              | Name    | Function                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 1-6                 | IP+     | Primary sensed current conduction path input; power input pins: connected to V <sub>CC</sub>                                                                                                                                                                                                                                      |  |  |  |

| 7                   | EN      | Enable pin. Toggling this pin to the low state after a FAULT condition resets the ACS760.                                                                                                                                                                                                                                         |  |  |  |

| 8                   | VIOUT   | Analog current sense output. Output voltage on this pin is proportional to the current flowing from the IP+ pins to the IP- pins.                                                                                                                                                                                                 |  |  |  |

| 9                   | ISET    | Terminal for $R_{SET}$ resistor. Sets Fault Current Threshold, $I_{PF}$ , via external resistor, $R_{SET}$ , connected between this terminal and GND. Factory trimmed 100 $\mu$ A current source flows out of this pin.                                                                                                           |  |  |  |

| 10                  | CG      | Terminal for $C_G$ capacitor. May be used to adjust the turn-on time and soft start control of an external MOSFET, S1. Voltage on this pin limits inrush current through MOSFET S1. Set via external capacitance, $C_G$ , connected between this pin and GND. This capacitor is charged by an internal 20 $\mu$ A current source. |  |  |  |

| 11                  | OCDLY   | Terminal for external capacitor, $C_{\text{OCD}}$ , Used to adjust delay for overcurrent shutdown, set via the external capacitor, $C_{\text{OCD}}$ , connected between this pin and GND.                                                                                                                                         |  |  |  |

| 12                  | OPDLY   | Terminal for external capacitor, $C_{OPD}$ , Used to adjust delay for overpower shutdown, set via the external capacitor, $C_{OPD}$ , connected between this pin and GND.                                                                                                                                                         |  |  |  |

| 13                  | FAULT   | Active low; output signal for short circuit and 240 V*A overload faults; does not trip for S1 short circuit fault.                                                                                                                                                                                                                |  |  |  |

| 14                  | S1SHORT | Active low; output signal for MOSFET S1 failure.                                                                                                                                                                                                                                                                                  |  |  |  |

| 15                  | FB+     | Input of positive feedback on output voltage. Used to determine 240 V*A threshold by difference between FB+ and FB– pins.                                                                                                                                                                                                         |  |  |  |

| 16                  | FB-     | Input of negative feedback on output voltage. Used to determine 240 V*A threshold by difference between FB+ and FB- pins. Pulling the FB- pin to 3.3 V, and the OPDLY pin to GND, disables the 240 V*A power fault, which allows the ACS760 to operate purely in Current Mode.                                                    |  |  |  |

| 17                  | GND     | Terminal for ground connection.                                                                                                                                                                                                                                                                                                   |  |  |  |

| 18                  | GATE    | Terminal for external MOSFET, S1. Provides output voltage to drive S1. Current through S1 is controlled at start-up by external capacitance connected between the CG pin and GND.                                                                                                                                                 |  |  |  |

| 19-24               | IP-     | Primary sensed current conduction path output; power output pins.                                                                                                                                                                                                                                                                 |  |  |  |

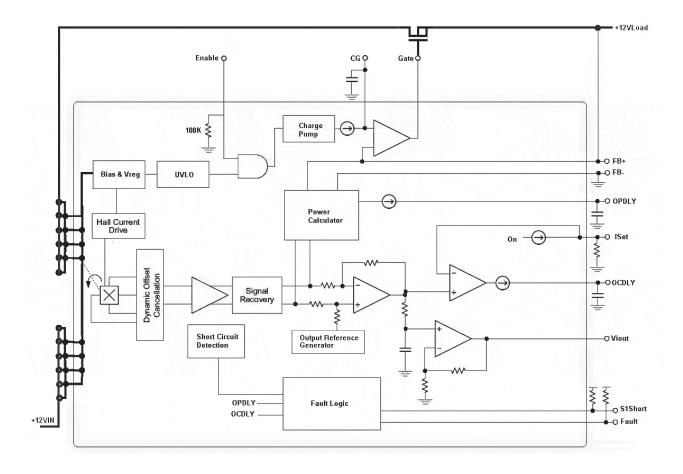

#### **Functional Block Diagram**

**OPERATING CHARACTERISTICS** valid at  $V_{CC} = 12 \text{ V}$ ,  $T_A = 0 ^{\circ}\text{C}$  to  $85 ^{\circ}\text{C}$ , unless otherwise noted

| Characteristic                                          | Symbol                 | 2 V, T <sub>A</sub> = 0°C to 85°C, unless otherwise noted  Test Conditions                                                                    | Min.  | Тур.  | Max.  | Units |

|---------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| GENERAL ELECTRICAL CHARACTER                            |                        |                                                                                                                                               |       |       | 1     | I     |

| Linear Sensing Range                                    | I <sub>P</sub>         | Current flows from IP+ to IP- pins                                                                                                            | 0     | _     | 55    | Α     |

| Primary Conductor Resistance                            | R <sub>PRIMARY</sub>   | T <sub>A</sub> = 25°C                                                                                                                         | _     | 1.5   | _     | mΩ    |

| Supply Voltage                                          | V <sub>CC</sub>        | Voltage applied to IP+ pins                                                                                                                   | _     | 12    | 13.2  | V     |

| Supply Current                                          | I <sub>CC</sub>        |                                                                                                                                               | _     | 10    | 12    | mA    |

|                                                         | V <sub>UVLOH</sub>     | V <sub>CC</sub> rising and CG pin current source turns on, EN pin = high                                                                      | _     | _     | 10.5  | V     |

| Undervoltage Lockout (UVLO)                             | V <sub>UVLOL</sub>     | V <sub>CC</sub> falling and CG pin current source turns off, EN pin = high                                                                    | 7.1   | _     | _     | V     |

| 10/10 D 1                                               | t <sub>UVLOE</sub>     | Enabling, measured from rising $V_{CC} > V_{UVLOH}$ to $V_{GATE} > 1 \text{ V}$                                                               | _     | 500   | 900   | μs    |

| UVLO Delay to Chip Enable/ Disable                      | t <sub>UVLOD</sub>     | Disabling, from falling V <sub>CC</sub> < V <sub>UVLOL</sub> to V <sub>GATE</sub> < 1 V                                                       | _     | _     | 2     | μs    |

| FB+ to FB– Input Resistance                             | R <sub>FB</sub>        | T <sub>A</sub> = 25°C                                                                                                                         | _     | 240   | _     | kΩ    |

| <b>CURRENT SENSE PERFORMANCE C</b>                      |                        | RISTICS                                                                                                                                       |       |       | ı     |       |

| VIOUT Analog Output Propagation<br>Time                 | t <sub>PROP</sub>      | $T_A$ = 25°C, $I_P$ = 0 $\rightarrow$ 20 A, capacitance from VIOUT to GND = 100 pF                                                            | _     | 2     | _     | μs    |

| VIOUT Analog Output 10-90% Rise<br>Time                 | t <sub>r</sub>         | $T_A$ = 25°C, $I_P$ = 0 $\rightarrow$ 20 A, capacitance from VIOUT to GND = 100 pF                                                            | _     | 5     | _     | μs    |

| VIOUT Analog Signal Bandwidth <sup>1</sup>              | f <sub>3dB</sub>       | $-3$ dB, Ip = 10 A peak-to-peak, $T_A$ = 25°C, no external device filter, capacitance from VIOUT to GND = 100 pF                              | _     | 50    | _     | kHz   |

|                                                         |                        | T <sub>A</sub> = 25°C                                                                                                                         | _     | 65    | _     | mV/A  |

| VIOLIT Analog Signal Consitivity                        | Cono                   | Over full ambient operating temperature range                                                                                                 | 63    | _     | 67    | mV/A  |

| VIOUT Analog Signal Sensitivity                         | Sens                   | T <sub>A</sub> = 25°C                                                                                                                         | _     | 5.416 | _     | mV/G  |

|                                                         |                        | Over full ambient operating temperature range                                                                                                 | 5.275 | _     | 5.558 | mV/G  |

| VIOUT Analog Noise Level                                | V <sub>NOISE(PP)</sub> | Mean peak-to-peak, T <sub>A</sub> = 25°C, 50 kHz external device filter                                                                       | _     | 20    | _     | mV    |

| VIOUT Analog Nonlinearity                               | E <sub>LIN</sub>       | Over full ambient operating temperature range and linear sensing range                                                                        | _     | ±0.5  | ±2.0  | %     |

| 7 0 101 111                                             | V <sub>IOUT(Q)</sub>   | T <sub>A</sub> = 0 to 55°C                                                                                                                    | 0.38  | _     | 0.42  | V     |

| Zero Current Output Voltage                             |                        | T <sub>A</sub> = 0 to 85°C                                                                                                                    | 0.37  | 0.4   | 0.43  | V     |

| Outrot Malla and Outrotal and Line Har?                 | V <sub>OL</sub>        | T <sub>A</sub> = 25°C                                                                                                                         | _     | 0.25  | _     | V     |

| Output Voltage Saturation Limits <sup>2</sup>           | V <sub>OH</sub>        | T <sub>A</sub> = 25°C                                                                                                                         | _     | 3.6   | _     | V     |

| \/\O\ \Tt-\ \F_\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\       |                        | T <sub>A</sub> = 25°C, I <sub>P</sub> = 20 A                                                                                                  | _     | ±1.0  | _     | %     |

| VIOUT Total Error % of I <sub>P</sub>                   | E <sub>TOT</sub>       | $T_A = 0 \text{ to } 85^{\circ}\text{C}, I_P = 20 \text{ A}$                                                                                  | _     | _     | ±3.5  | %     |

| VIOUT DC Output Resistance                              | R <sub>VIOUT</sub>     | I <sub>VIOUT</sub> = 1 mA                                                                                                                     | _     | 1     | _     | Ω     |

| <b>CURRENT FAULT PERFORMANCE CH</b>                     |                        |                                                                                                                                               |       |       |       |       |

| Load Power Fault Threshold                              | P <sub>F(th)</sub>     |                                                                                                                                               | 222   | 230   | 238   | W     |

| 240 V*A Fault Signal Delay                              | t <sub>PFH</sub>       | $T_A$ = 25°C, measured from FAULT signal to $V_{GATE}$ < 1 V, 2.2 µF capacitance from OPDLY pin to GND, load step from 17 A to 23 A in 100 ns | -     | 425   | -     | ms    |

|                                                         | t <sub>PFL</sub>       | $T_A$ = 25°C, measured from FAULT signal to $V_{GATE}$ < 1 V, OPDLY pin open, load step from 17 A to 23 A in 100 ns                           | _     | 10    | 12    | μs    |

| 240 V*A Fault Signal Delay Drift                        | $\Delta t_{PF}$        | Over full operating ambient temperature range, external capacitor with ±5% tolerance                                                          |       | _     | 15    | %     |

| Internal –3 dB Filter Frequency for FB+ and FB– Pins    | f <sub>FBFILT</sub>    | T <sub>A</sub> = 25°C                                                                                                                         | _     | 50    | _     | kHz   |

| I <sub>P</sub> Fault Switchpoint Tolerance <sup>3</sup> | E <sub>PF</sub>        | Percentage error of I <sub>PF</sub>                                                                                                           | -15   | _     | 15    | %     |

|                                                         | t <sub>IPFLmax</sub>   | Measured from FAULT signal to $V_{GATE}$ < 1 V, OCDLY pin open, load step from 17 A to 45 A in 100 ns                                         | -     | 8     | 12    | μs    |

| I <sub>PF</sub> Fault Signal Delay <sup>4</sup>         | t <sub>IPFH</sub>      | Measured from FAULT signal to $V_{\rm GATE}$ < 1 V, 2.2 nF capacitance from OCDLY pin to GND, load step from 17 A to 45 A in 100 ns           | -     | 425   | _     | μs    |

OPERATING CHARACTERISTICS, continued valid at V<sub>CC</sub> = 12 V, T<sub>A</sub> = 0°C to 85°C, unless otherwise noted

| Characteristic                                                 | Symbol               | Test Conditions                                                                                                                                                        | Min. | Тур.                | Max. | Units |

|----------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------------------|------|-------|

| Maximum Short Circuit/Overcurrent Fault Threshold <sup>5</sup> | I <sub>SC</sub>      |                                                                                                                                                                        |      | 110                 | 160  | Α     |

| Short Circuit/Overcurrent Fault Gate Delay                     | t <sub>SC</sub>      | Measured from FAULT signal to V <sub>GATE</sub> < 1 V, Includes t <sub>GF</sub>                                                                                        | _    | 2                   | 3    | μs    |

| <b>VOLTAGE FAULT PERFORMANCE CH</b>                            | ARACTER              | RISTICS                                                                                                                                                                |      |                     |      |       |

| Internal Pull Down Resistance Between EN and GND               | R <sub>EN</sub>      | T <sub>A</sub> = 25°C                                                                                                                                                  | _    | 100                 | _    | kΩ    |

| EN Voltage Threshold <sup>6</sup>                              | V <sub>ENH</sub>     | IC enabled when V <sub>EN</sub> > V <sub>ENH</sub>                                                                                                                     | 1.93 | _                   | _    | V     |

| Er Vollage Threshold                                           | $V_{ENL}$            | IC disabled when V <sub>EN</sub> < V <sub>ENL</sub>                                                                                                                    | _    | _                   | 1    | V     |

| S1 Short Circuit Detection Current <sup>7</sup>                | I <sub>S1S</sub>     | V <sub>GATE</sub> = 0 V or V <sub>GATE</sub> = 12 V                                                                                                                    | 0.9  | 1.5                 | 2.1  | Α     |

| S1 Short Circuit Detection Delay                               | t <sub>S1S</sub>     | Measured from disablement of the device to detection of an S1 fault                                                                                                    | _    | _                   | 15   | μs    |

| S1SHORT Output Voltage                                         | V <sub>S1SOL</sub>   | I <sub>S1SHORT</sub> = 3 mA sink current                                                                                                                               | _    | _                   | 0.4  | V     |

| S1SHORT Output Leakage Current                                 | I <sub>S1SIH</sub>   | V <sub>S1SHORT</sub> = 3.3 V                                                                                                                                           | _    | _                   | 5    | μΑ    |

| FAULT Output Voltage                                           | V <sub>FAULTOL</sub> | I <sub>FAULT</sub> = 3 mA sink current                                                                                                                                 | _    | _                   | 0.4  | V     |

| FAULT Output Leakage Current                                   | I <sub>FAULTIH</sub> | V <sub>FAULT</sub> = 3.3 V                                                                                                                                             | -    | _                   | 5    | μΑ    |

| GATE DRIVE PERFORMANCE CHARA                                   | CTERISTI             | CS                                                                                                                                                                     |      |                     |      |       |

| Internal Charge Pump Voltage                                   | V <sub>CP</sub>      | T <sub>A</sub> = 25°C                                                                                                                                                  | _    | V <sub>CC</sub> +10 | -    | V     |

| Average GATE Drive Current                                     | $I_{GD}$             | V <sub>CC</sub> = 12 V, T <sub>A</sub> = 25°C                                                                                                                          | 25   | 50                  | _    | μA    |

| Charge Pump Switching Frequency                                | f <sub>CP</sub>      | T <sub>A</sub> = 25°C                                                                                                                                                  | _    | 1                   | -    | MHz   |

| GATE Rise Time                                                 | +                    | $T_A$ = 25°C, external MOSFET S1 gate capacitance = 5.8 nF, measured from $V_{GATE}$ = 0 V to 15 V, CG pin open, no output load capacitance                            | -    | 1                   | _    | ms    |

| GALL RISE TIME                                                 | t <sub>GR</sub>      | $T_A=25^{\circ}C,$ external MOSFET S1 gate capacitance = 5.8 nF, measured from $V_{GATE}=0$ V to 15 V, 3.75 $\mu F$ capacitor connected between CG and GND pins        | _    | 500                 | _    | ms    |

| GATE Sink Resistance                                           | R <sub>Gsink</sub>   |                                                                                                                                                                        | _    | 20                  | 30   | Ω     |

| GATE Discharge Current                                         | I <sub>GD</sub>      | $V_{GATE} = V_{CC} + 10 V$                                                                                                                                             | _    | 1000                | _    | mA    |

| GATE Shutdown Delay                                            | t <sub>GSD</sub>     | Measured from fault event to start of GATE pull down                                                                                                                   | _    | 200                 | _    | ns    |

| GATE Maximum Fall Time                                         | t <sub>GF</sub>      | Measured from $V_{GATE}$ = 90% of maximum to $V_{GATE}$ < 1 V, external MOSFET S1 gate capacitance = 5.8 nF. EN pin switched from high to low, FAULT or S1SHORT signal |      | 800                 | _    | ns    |

| CG Output Current                                              | I <sub>SLEW</sub>    | T <sub>A</sub> = 25°C                                                                                                                                                  | 18   | 20                  | 22   | μΑ    |

<sup>&</sup>lt;sup>1</sup>The small signal, ac bandwidth of this device is approximately 90 kHz.

<sup>&</sup>lt;sup>2</sup>This test requires currents sufficient to swing the output driver between the fully off state and the saturated state. Assumes that the VIOUT pin is connected to an analog-to-digital converter that saturates at 2.5 V. The VIOUT signal is linear above 2.5 V, however, this test is NOT intended to indicate a range of linear operation.

<sup>3</sup>Assumes that a 1% resistor with a flat temperature coefficient is connected between the ISET and GND pins.

<sup>&</sup>lt;sup>4</sup>Can exceed t<sub>IPFH</sub>(max) delay period via the use of a larger external capacitor. Voltage trip point on the high side of the capacitor is 3.85 V.

<sup>&</sup>lt;sup>5</sup>This parameter is internally programmed and cannot be controlled by the end user.

<sup>&</sup>lt;sup>6</sup>The FAULT output signal is latched. After a latched fault event, the device will be reset only when either: (a) V<sub>EN</sub> drops below V<sub>ENL</sub>, or (b) the power to the device (applied to the IP+ pins) is toggled off and then back on.

<sup>&</sup>lt;sup>7</sup>The voltage on the gate of the external MOSFET S1 does not need to be < 1 V in order for the device to detect an S1 short circuit condition. The device does detect a faulty S1 when the gate of S1 is shorted to the S1 source or drain terminal.

#### Soft Start and Fault Characteristics

Gate turn on rise time,  $t_{GR}$ . Set by external capacitance,  $C_G$ , on the CG pin, such that  $C_G = 7.5 \times t_{GR}$ , where  $C_G$  is in  $\mu F$  and  $t_{GR}$ is rise time in seconds. For example, a  $3.9~\mu F$  capacitor connected from the CG pin to GND (without an output load) will yield a rise time of approximately 500 ms:  $C_G \cong 7.5 \times 0.5 \text{ s} = 3.75 \mu\text{F}$ ,  $\approx$  3.9 µF (a common capacitor value).

When the CG pin is kept open, the ACS760 has a minimum t<sub>GR</sub> of 1 ms typical.

$I_{PF}$  fault signal delay,  $t_{IPF}$ . This is the delay from high current level fault sense to the start of turn-off of the external MOSFET S1 turn-off. Set by external capacitance, C<sub>OCD</sub>, on the OCDLY pin, such that  $C_{OCD} = 5.17 \times t_{rOCD}$ ; where  $C_{OCD}$  is in  $\mu F$  and  $t_{rOCD}$  is rise time in seconds.

When the OCDLY pin is kept open, the IC has a minimum fault delay, t<sub>IPFLmax</sub>, of 8 μs maximum.

**Load power fault signal delay, t**<sub>PFL</sub>. This is the delay from maximum power level fault, P<sub>F(th)</sub>, sense to the start of external MOSFET S1 turn-off. Set by external capacitance, C<sub>OPD</sub>, on the OPDLY pin, such that  $C_{OPD} = 5.17 \times t_{rOPD}$ ; where  $C_{OPD}$  is in  $\mu F$ and  $t_{rOPD}$  is rise time in seconds.

The IC has a minimum fault delay when the OPDLY pin kept open of 10 µs typical.

$I_{PF}$  fault current setting,  $I_{PF}$ . The  $I_{PF}$  upper trip level may be set by using a resistor between the ISET pin and GND, such that  $R_{SET} = 10^4 (0.4 + 0.065 \times I_{PF})$ , where  $I_{PF}$  is in A and  $R_{SET}$  in  $\Omega$ .

#### **Accuracy Characteristics**

**Sensitivity, Sens.** The change in sensor output in response to a 1 A change through the primary conductor. Sens is the product of the magnetic circuit sensitivity (G/A) and the linear IC amplifier gain (mV/G). The linear IC amplifier gain is trimmed at Allegro final test to optimize the sensitivity (mV/A) for the full-scale current range of the device.

Noise, V<sub>NOISE(PP)</sub>. The product of the linear IC amplifier gain (mV/G) and the noise floor for the Allegro Hall effect linear IC. Dividing the noise (mV) by the sensitivity (mV/A) provides the smallest current that the device is able to resolve.

**Nonlinearity, E\_{LIN}.** The linearity of the  $V_{IOUT}$  signal is the degree to which the voltage output from the sensor varies in direct proportion to the primary sensed current, through its fullscale amplitude. Nonlinearity reveals the maximum deviation in the slope of the device transfer function compared to the slope of the ideal transfer curve for this transducer. The following equation is used to derive the linearity:

$$100 \left\{ 1 - \left[ \frac{(V_{\text{IOUT}} \text{ full-scale amperes } -V_{\text{IOUT}(Q)})}{2 (V_{\text{IOUT}} \text{ half-scale amperes } -V_{\text{IOUT}(Q)})} \right] \right\}$$

Zero Current Output Voltage,  $V_{IOUT(Q)}$ . The output of the sensor when the primary current,  $I_p$ , is 0 A. Variation in  $V_{IOUT(O)}$  can be attributed to the resolution of the Allegro linear IC quiescent voltage trim and thermal drift.

**VIOUT Total Error, E**<sub>TOT</sub>. The maximum percentage deviation of the actual output from its ideal value.

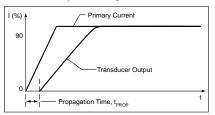

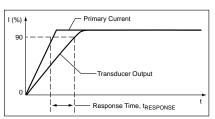

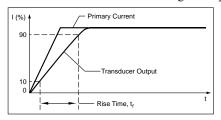

#### **Dynamic Response Characteristics**

**Propagation delay, t\_{PROP}.** The time required for the sensor output to reflect a change in the primary current signal. Propagation delay is attributed to inductive loading within the linear IC package, as well as in the inductive loop formed by the primary conductor geometry. Propagation delay can be considered as a fixed time offset and may be compensated.

**Response time,**  $t_{RESPONSE}$ . The time interval between a) when the primary current signal reaches 90% of its final value, and b) when the sensor reaches 90% of its output corresponding to the applied current.

**Rise time**  $(t_r)$ . The time interval between a) when the sensor reaches 10% of its full scale value, and b) when it reaches 90% of its full scale value. The rise time to a step response is used to derive the bandwidth of the current sensor, in which f(-3 dB) = $0.35/t_r$ . Both  $t_r$  and  $t_{RESPONSE}$  are detrimentally affected by eddy current losses observed in the conductive IC ground plane.

#### 240 V\*A Fault Operation

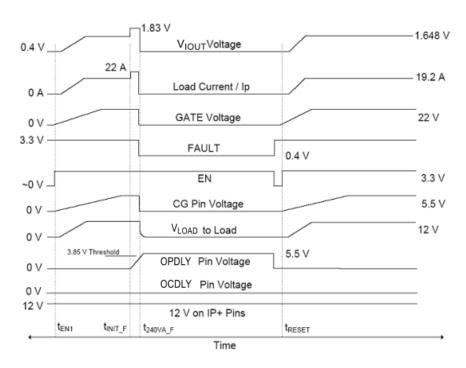

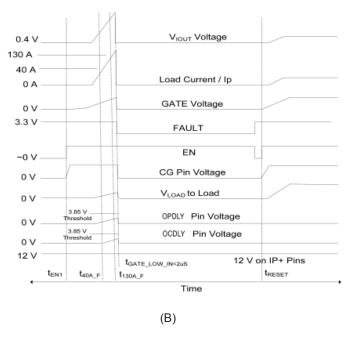

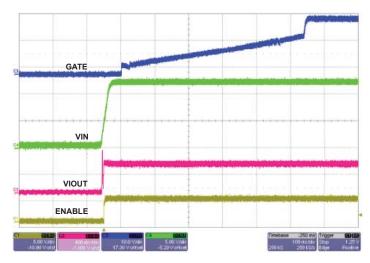

The timing diagram in figure 1 shows characteristic operation of the ACS760 when the power consumed from the 12 V system bus exceeds a 240 V\*A or 240 W level. The system power supply bus reaches the nominal steady state level of 12 V before the EN pin (Enable pin, active high) of the ACS760 transitions to the high state at time  $t_{EN1}$ . Note that, when the EN pin is in the low state, the GATE pin is actively pulled low. However, as shown in the timing diagram, the voltage on the GATE pin increases with a positive slope after the EN pin transitions to the high state. The ramp rate of the GATE pin is controlled by the value of the capacitor connected to the CG pin.

At a certain GATE voltage, current begins to flow through the external protection MOSFET, S1, and this current increases as the GATE voltage increases. The voltage at the VIOUT pin, which is the current sensor output voltage of the ACS760, proportionally tracks the current that flows through the MOSFET.

In the timing diagram, the system is in normal, steady state operation up until the time t<sub>INIT F</sub>. At t<sub>INIT F</sub>, the current load on the 12 V power supply increases from 19.2 to 22 A and the ACS760 internally registers a 240 V\*A fault condition. At this time, the

voltage on the OPDLY pin increases with a constant slope. (This slope is controlled by the value of the capacitor connected to the OPDLY pin). This voltage continues to increase with a constant slope until either:

- The OPDLY pin voltage reaches a threshold of 3.85 V (if this occurs, the FAULT signal is latched in the low state), or

- The power consumption of the system falls below 240 V\*A (at which time the OPDLY pin voltage is pulled to ground)

A 240 V\*A fault event is detected at t<sub>240VA F</sub>. At this time, the FAULT signal transitions to the low state and the GATE pin is pulled to ground. The FAULT signal is latched and the chip will pull down the GATE voltage until the EN pin of the ACS760 transitions to the low state and then back to the high state. As shown in the timing diagram, certain ACS760 signals (the FAULT signal and the OPDLY pin voltage) are reset when the EN pin transitions to the low state. These signals are reset in order to guarantee normal device operation (soft start and fault monitoring) when the EN signal transitions back to the high state.

Figure 1. Timing Diagram for 240 V\*A Fault

#### **Soft Short Circuit Fault Operation**

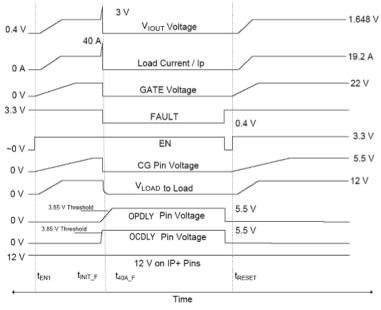

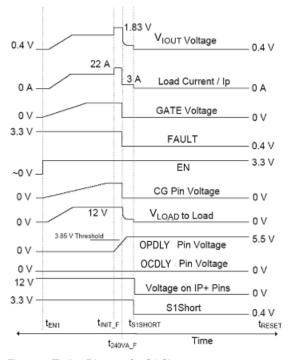

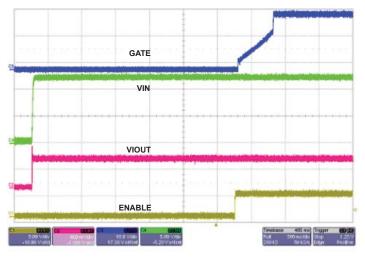

The timing diagram in figure 2 shows the characteristic operation of the ACS760 when the current load on the 12 V system bus jumps from the 19 to 20 A level to the 40 A level. The 40 A load is typically indicative of a soft short circuit on the  $I_{LOAD}$  side of the external MOSFET.

In figure 2, the system power supply bus reaches the nominal steady state level of 12 V before the EN pin (Enable pin, active high) of the ACS760 transitions to the high state at time  $t_{\rm EN1}$ . Note that when the EN pin is in the low state, the GATE pin is actively pulled low. However, as shown in the timing diagram, the voltage on the GATE pin increases with a positive slope after the EN pin transitions to the high state. The ramp rate of the GATE pin is controlled by the value of the capacitor connected to the CG pin.

At a certain GATE voltage, current begins to flow through the external protection MOSFET, S1, and this current increases as the GATE voltage increases. The voltage at the VIOUT pin, which is the current sensor output voltage of the ACS760, proportionally tracks the current that flows through the MOSFET.

In the timing diagram the system is in normal, steady state operation up until the time  $t_{INIT\_F}$ . At  $t_{INIT\_F}$  the current load on the 12 V power supply increases from 19.2 A to 40 A and the ACS760 internally registers both a 240 V\*A fault condition and an  $I_{PF}$  fault condition. In this example, the  $I_{SET}$  voltage was set at 3.0 V, which corresponds to a 40 A fault threshold. At  $t_{INIT\_F}$ ,

the voltage on the OPDLY and OCDLY pins increases with a constant slope. The slope of the voltage on the two delay pins is controlled by the value of the capacitor connected to each pin. In this case the capacitor on the OCDLY pin is smaller than the capacitor on the OPDLY pin and the voltage on the OCDLY pin ramps much faster than the voltage on the OPDLY pin (both pins are connected to separate 20  $\mu A$  current sources). The voltages on each delay pin continues to increase with a constant slope until either:

- Either the OPDLY or the OCDLY pin voltages reach a threshold of 3.85 V (if this occurs, the FAULT signal is latched in the low state), or

- The current load of the system falls below 20 A for the OPDLY pin and 40 A for the OCDLY pin

In figure 2 a short circuit fault event is detected at  $t_{40A\_F}$ . At this time, the FAULT signal transitions to the low state and the GATE pin is pulled to ground. The FAULT state is latched and the chip will pull down the GATE voltage until the EN pin of the ACS760 transitions to the low state and then back to the high state. As shown in the timing diagram, certain ACS760 signals (the FAULT signal and the OCDLY pin voltage) are reset when the EN pin transitions to the low state. These signals are reset in order to guarantee normal device operation (soft start and fault monitoring) when the EN signal transitions back to the high state.

Figure 2. Timing Diagram for 30 to 40 A Load Fault

#### Hard Short Circuit (50 m $\Omega$ from V<sub>LOAD</sub> to GND) **Fault Operation**

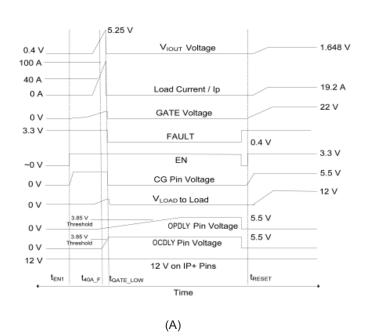

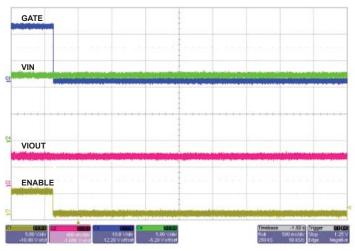

The timing diagram below specifically shows characteristic operation of the ACS760 when the device is powered on (via the EN pin) and a 50 m $\Omega$  short circuit is present from load side of the external MOSFET, S1, to ground.

In figure 3 the system power supply bus reaches the nominal steady state level of 12 V before the EN pin of the ACS760 transitions to the high state at time t<sub>EN1</sub>. The voltage on the GATE pin increases with a positive slope after the EN pin transitions to the high state. The ramp rate of the GATE pin is controlled by the value of the capacitor connected to the CG pin. In the example shown below a small capacitor is connected to the CG pin and the pin ramps to 5.5 V in  $< 10 \mu s$ .

In panel A of figure 3, the device is enabled into a 50 m $\Omega$  short circuit. Therefore, as the GATE voltage increases the current through the external MOSFET increases at a rapid rate. In this example case it is assumed that there is no capacitor on the OCDLY pin. When the current through the MOSFET exceeds the threshold set by the R<sub>SET</sub> resistor, the voltage on the OCDLY pin rises quickly beginning at  $t_{40A}$  F. As the voltage on the OCDLY pin rises, so does the voltage on the CG pin and the current through the external MOSFET. If there is no capacitor on the OCDLY pin, and if the ACS760 Short Circuit Fault Threshold,

I<sub>SC</sub>, is greater than 100 A, then the OCDLY pin will reach the 3.85 V threshold before the current through the external MOS-FET exceeds I<sub>SC</sub>. This is the case depicted in the panel A. The fault event is detected at t<sub>GATE LOW</sub>. At this time. the FAULT signal transitions to the low state and the GATE pin is pulled to ground.

In the event that a large capacitor is connected to the OCDLY pin, the ACS760 will not pull down the gate of the external MOS-FET until the current flowing through the MOSFET exceeds I<sub>SC</sub> (shown in panel B, under the assumption that  $I_{SC}$  equals 130 A). The device pulls down the MOSFET GATE approximately 2 µs after the load current exceeds this threshold. If a large capacitor is connected to the OCDLY pin a significant current (> 40 A but < 160 A) may flow through the MOSFET for tens of microseconds before the Short Circuit Fault Threshold trips. These tens of microseconds elapse as the GATE charges and the load current increases, finally exceeding the short circuit threshold.

The FAULT signal is latched and the chip will pull down the GATE voltage until the EN pin of the ACS760 transitions to the low state and then back to the high state. Certain ACS760 signals (soft start and fault monitoring) are reset when the EN pin transitions to the low state. These signals are reset in order to guarantee normal device operation when the EN signal transitions to the high state.

Figure 3. (A) Timing Diagram for a 50 m $\Omega$  Short Circuit from  $V_{LOAD}$  to GND; (B) Timing Diagram for a 50 m $\Omega$  Short Circuit from  $V_{LOAD}$  to GND, capacitor C<sub>OCD</sub> with high rating connected.

#### **S1 Short Fault Operation**

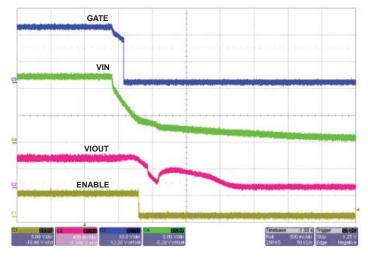

The timing diagram in figure 4 shows the characteristic operation of the ACS760 when the power consumed from the 12 V system bus exceeds a 240 V\*A or 240 W level. For the operation during a 240 V\*A fault condition, refer to figure 1. That section describes the operation of the ACS760 until the time  $t_{240\text{VA}\_F}$ . Figure 4 depicts a 240 V\*A fault, but continues on to demonstrate the ability of the ACS760 to detect damage and improper operation of the external MOSFET in an S1 short circuit event.

At t<sub>240VA\_F</sub> the FAULT signal transitions to the low state and the ACS760 pulls down the voltage on the GATE pin. During normal

Figure 4. Timing Diagram for S1 Short

operation, when the GATE pin is at 0 V, the current through the S1 MOSFET (and therefore through the ACS760) equals approximately 0 A. However, in the case depicted in figure 4, current through the S1 MOSFET flows even though the GATE pin is pulled low. If a FAULT has occurred and more than 2.1 A flow through the ACS760, then the S1SHORT signal transitions to the low state. When the S1SHORT signal is low, that indicates to the system that the ACS760 cannot turn off the external MOSFET (for example, when a short circuit exists between the source and the drain of the MOSFET). In the case depicted, the system shuts down the 12 V power supply after the S1SHORT signal transitions to the low state.

Note that, in some cases, the GATE of the S1 MOSFET may be shorted to the source or drain of the MOSFET. In this case the ACS760 may not be able to pull down the gate of the S1 MOSFET. However, in this case the ACS760 will still register an S1 Short even if the gate potential is equal to or greater than 12 V.

If the ACS760 is disabled (EN pin in the low state) and greater than 2.1 A flows through the ACS760, then the device will register an S1 Short condition and the S1SHORT pin will transition to the low state. The voltage on the GATE pin is not used as a determining factor when sensing an S1 Short condition.

The S1SHORT signal will not reset to a high state until power to the device is cycled. Toggling the EN pin does not reset the latched S1 Short state.

#### **Determining the Root Cause of an ACS760 Fault Event**

The following truth table provides system debugging information in the event of a fault event during use of the ACS760. Note that for all of the fault conditions listed, it is possible to monitor the voltages of various ACS760 output pins and determine the cause of the ACS760 FAULT event.

#### **Fault Condition Truth Table**

|           | Pin Logic State |           | Probable Root Cause                                                |  |

|-----------|-----------------|-----------|--------------------------------------------------------------------|--|

| FAULT Pin | OPDLY Pin       | OCDLY Pin | Probable Root Gause                                                |  |

| Low       | High            | Low       | 240 V*A system power level, P <sub>F(th)</sub> , exceeded          |  |

| Low       | Don't Care      | High      | I <sub>P</sub> Fault Current Threshold, I <sub>PF</sub> , exceeded |  |

| Low       | Low             | Low       | Short Circuit Fault Threshold, I <sub>SC</sub> , exceeded          |  |

#### **Fault Condition Characteristics**

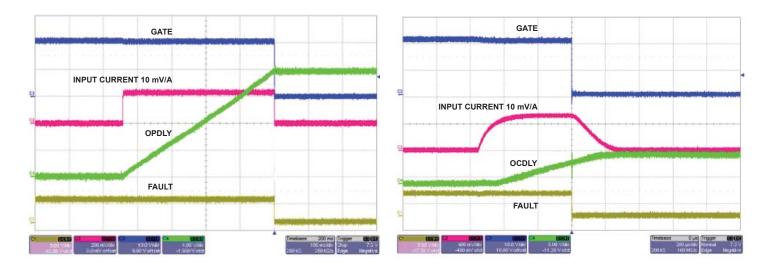

Figure 5. 240 V\*A fault: with  $V_{CC}$  = 12 V and ACS760 enabled, apply load

Figure 6. I $_{\rm PF}$  event: with V $_{\rm CC}$  = 12 V and ACS760 enabled, apply load

Figure 7. Hot-swap with 1  $\mu\text{F}$  capacitor from CG pin to GND, resistive load approximately 0.17  $\Omega.$  capacitive load approximately 3300  $\mu\text{F}$ ;  $C_G$  capacitor limits inrush current to 720 mA during hot swap event (15 A current probe used)

### ACS760ELF-20B

## 12 V High-Side Hot-Swap Hall Effect Based Current Monitor

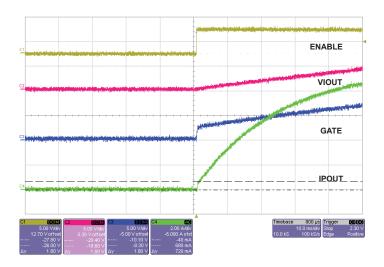

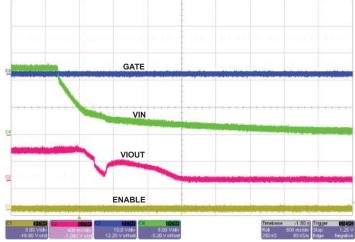

Figure 8. Power-up: with the enable jumper on, apply  $V_{CC}$

Figure 9. Power-up: with  $V_{\text{CC}}$  on, apply the enable jumper (enables ACS760)

Figure 11. Power-up to power-down (a): remove enable jumper (disables ACS760, but  $V_{CC}$  and  $V_{IOUT}$  stay high (see figure 12)

Figure 10. Power-down: with enable jumper on, remove supply (disables ACS760)

Figure 12. Power-up to power-down (b): with ACS760 disabled (see figure 11), remove supply ( $V_{CC}$  and  $V_{IOUT}$  brought low)

#### **Application Information: Current Mode Operation**

The ACS760 has the ability to operate in pure Current Mode. If the Allegro ACS760 detects power in excess of 240 V\*A, the FAULT output of the device transitions from a logic high to a logic low level and the integrated gate driver circuitry pulls the gate of an external MOSFET to GND. The delay between the detection of an excess power condition and gate shutdown is set by an external capacitor on the OPDLY pin to GND. The ACS760, however, has the ability to override the Power Mode fault condition to operate in pure Current Mode.

Pulling the OPDLY pin to GND, disables the 240 V\*A power fault to allow the ACS760 to operate in pure Current Mode. The user may then set the current fault threshold by adjusting the resistor value from the ISET pin to GND. If the current exceeds the set threshold, the FAULT output of the device trips and the gate of the external MOSFET is pulled to GND. The delay between the detection of a soft short circuit condition and gate shutdown is set by the capacitor on the OCDLY pin. In Current Mode Operation, the ACS760 has the ability to detect a S1 Short and Hard Short.

| ACS                           | Allegro Current Sensor                        |

|-------------------------------|-----------------------------------------------|

| 760                           | Device family number                          |

| T                             | Indicator of 100% matte tin leadframe plating |

| R                             | Operating ambient temperature range code      |

| LC                            | Package type designator                       |

| WA PPP Primary sensed current |                                               |

| YY                            | Date code: Calendar year (last two digits)    |

| WW                            | Date code: Calendar week                      |

| Α                             | Date code: Shift code                         |

|                               | 760<br>T<br>R<br>LC<br>PPP<br>YY<br>WW        |

|         | ACS   | Allegro Current Sensor                        |

|---------|-------|-----------------------------------------------|

|         | 760   | Device family number                          |

| ACS760T | Т     | Indicator of 100% matte tin leadframe plating |

| RLCPPP  | R     | Operating ambient temperature range code      |

| II      | LC    | Package type designator                       |

|         | , PPP | Primary sensed current                        |

| YYWW    | LL    | Lot code                                      |

|         | YY    | Date code: Calendar year (last two digits)    |

|         | WW    | Date code: Calendar week                      |

Copyright ©2006, 2007, Allegro MicroSystems, Inc.

The products described herein are manufactured under one or more of the following U.S. patents: 5,045,920; 5,264,783; 5,442,283; 5,389,889; 5,581,179; 5,517,112; 5,619,137; 5,621,319; 5,650,719; 5,686,894; 5,694,038; 5,729,130; 5,917,320; and other patents pending.