# 1Gb DDR2 SDRAM

HY5PS1G431C(L)FP HY5PS1G831C(L)FP HY5PS1G1631C(L)FP

# **Revision Details**

| Rev. | History                     | Draft Date |

|------|-----------------------------|------------|

| 0.1  | Initial data sheet released | Nov. 2006  |

| 0.2  | IDD Values added            | Dec. 2006  |

#### **Contents**

## 1. Description

- 1.1 Device Features and Ordering Information

- 1.1.1 Κεγ Φεατυρεσ

- 1.1.2 Ordering Information

- 1.1.3 Ordering Frequency

- 1.2 Pin configuration

- 1.3 Pin Description

# 2. Maximum DC ratings

- 2.1 Absolute Maximum DC Ratings

- 2.2 Operating Temperature Condition

## 3. AC & DC Operating Conditions

- 3.1 DC Operating Conditions

- 5.1.1 Recommended DC Operating Conditions(SSTL\_1.8)

- 5.1.2 ODT DC Electrical Characteristics

- 3.2 DC & AC Logic Input Levels

- 3.2.1 Input DC Logic Level

- 3.2.2 Input AC Logic Level

- 3.2.3 AC Input Test Conditions

- 3.2.4 Differential Input AC Logic Level

- 3.2.5 Differential AC output parameters

- 3.3 Output Buffer Levels

- 3.3.1 Output AC Test Conditions

- 3.3.2 Output DC Current Drive

- 3.3.3 OCD default χηαραχτεριστιχσ

- 3.4 IDD Specifications & Measurement Conditions

- 3.5 Input/Output Capacitance

## 4. AC Timing Specifications

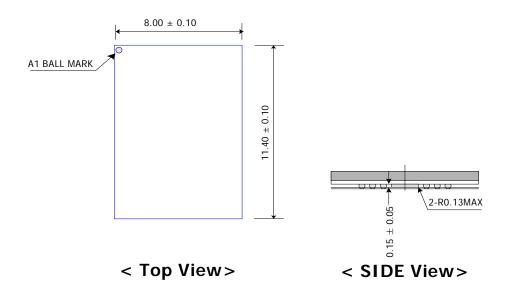

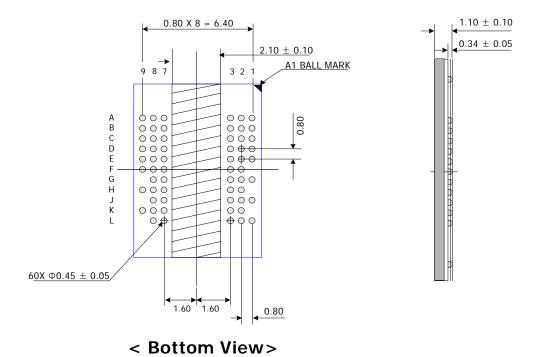

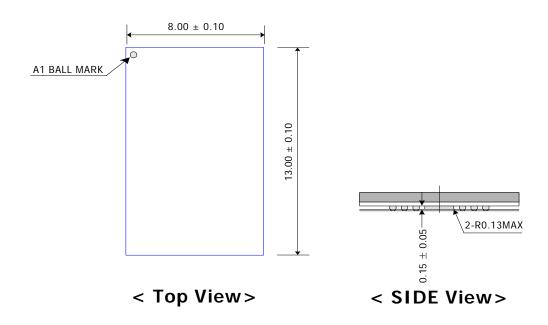

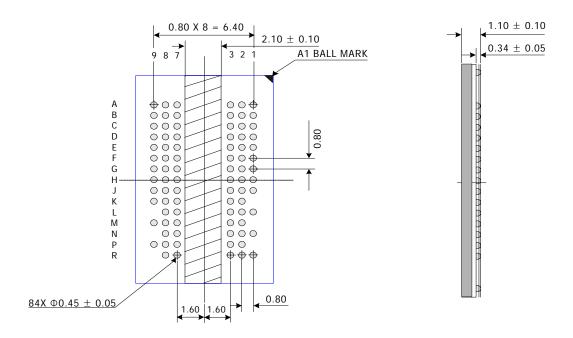

## 5. Package Dimensions

# 1. Description

# 1.1 Device Features & Ordering Information

# 1.1.1 Key Features

- VDD = 1.8V +/- 0.1V

- VDDQ = 1.8V +/- 0.1V

- · All inputs and outputs are compatible with SSTL\_18 interface

- 8 banks

- Fully differential clock inputs (CK, /CK) operation

- · Double data rate interface

- Source synchronous-data transaction aligned to bidirectional data strobe (DQS, DQS)

- Differential Data Strobe (DQS, DQS)

- Data outputs on DQS, DQS edges when read (edged DQ)

- Data inputs on DQS centers when write(centered DQ)

- On chip DLL align DQ, DQS and DQS transition with CK transition

- · DM mask write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 3, 4, 5 and 6 supported

- Programmable additive latency 0, 1, 2, 3, 4 and 5 supported

- Programmable burst length 4/8 with both nibble sequential and interleave mode

- · Internal eight bank operations with single pulsed RAS

- · Auto refresh and self refresh supported

- · tRAS lockout supported

- 8K refresh cycles /64ms

- JEDEC standard 60ball FBGA(x4/x8), 84ball FBGA(x16)

- · Full strength driver option controlled by EMRS

- · On Die Termination supported

- · Off Chip Driver Impedance Adjustment supported

- Read Data Strobe supported (x8 only)

- Self-Refresh High Temperature Entry

# **Ordering Information**

# **Operating Frequency**

| Part No.              | Configuration | Package |

|-----------------------|---------------|---------|

| HY5PS1G431C(L)FP-XX*  | 256Mx4        | 60 Ball |

| HY5PS1G831C(L)FP-XX*  | 128Mx8        | OO Dali |

| HY5PS1G1631C(L)FP-XX* | 64Mx16        | 84 Ball |

| Grade | tCK(ns) | CL | tRCD | tRP | Unit |

|-------|---------|----|------|-----|------|

| E3    | 5       | 3  | 3    | 3   | Clk  |

| C4    | 3.75    | 4  | 4    | 4   | Clk  |

| Y5    | 3       | 5  | 5    | 5   | Clk  |

| S5    | 2.5     | 5  | 5    | 5   | Clk  |

#### Note:

<sup>-</sup>XX\* is the speed bin, refer to the Operation Frequency table for complete Part No.

# 1.2 Pin Configuration & Address Table

# 256Mx4 DDR2 Pin Configuration(Top view: see balls through package)

1 2 3 7 8 9

| VDD  | NC   | VSS        | Α | VSSQ  | DQS  | VDDQ |

|------|------|------------|---|-------|------|------|

| NC   | VSSQ | DM         | В | DQS   | VSSQ | NC   |

| VDDQ | DQ1  | VDDQ       | С | VDDQ  | DQ0  | VDDQ |

| NC   | VSSQ | DQ3        | D | DQ2   | VSSQ | NC   |

| VDDL | VREF | VSS        | E | VSSDL | CK   | VDD  |

|      | CKE  | WE         | F | RAS   | CK   | ODT  |

| BA2  | BA0  | BA1        | G | CAS   | CS   |      |

|      | A10  | A1         | Н | A2    | A0   | VDD  |

| VSS  | А3   | <b>A</b> 5 | J | A6    | A4   |      |

|      | A7   | Α9         | K | A11   | A8   | VSS  |

| VDD  | A12  | NC         | L | NC    | A13  |      |

## **ROW AND COLUMN ADDRESS TABLE**

| ITEMS               | 256Mx4      |

|---------------------|-------------|

| # of Bank           | 8           |

| Bank Address        | BA0,BA1,BA2 |

| Auto Precharge Flag | A10/AP      |

| Row Address         | A0 - A13    |

| Column Address      | A0-A9, A11  |

| Page size           | 1 KB        |

# 128Mx8 DDR2 PIN CONFIGURATION(Top view: see balls through package)

1 2 3 7 8 9

| VDD  | NU/RDQS | VSS        | Α | VSSQ  | DQS  | VDDQ |

|------|---------|------------|---|-------|------|------|

| DQ6  | VSSQ    | DM/RDQS    | В | DQS   | VSSQ | DQ7  |

| VDDQ | DQ1     | VDDQ       | С | VDDQ  | DQ0  | VDDQ |

| DQ4  | VSSQ    | DQ3        | D | DQ2   | VSSQ | DQ5  |

| VDDL | VREF    | VSS        | E | VSSDL | CK   | VDD  |

|      | CKE     | WE         | F | RAS   | CK   | ODT  |

| BA2  | BA0     | BA1        | G | CAS   | CS   |      |

|      | A10     | A1         | Н | A2    | A0   | VDD  |

| VSS  | A3      | <b>A</b> 5 | J | A6    | A4   |      |

|      | A7      | A9         | K | A11   | A8   | VSS  |

| VDD  | A12     | NC         | L | NC    | A13  |      |

## **ROW AND COLUMN ADDRESS TABLE**

| ITEMS               | 128Mx8        |

|---------------------|---------------|

| # of Bank           | 8             |

| Bank Address        | BA0, BA1, BA2 |

| Auto Precharge Flag | A10/AP        |

| Row Address         | A0 - A13      |

| Column Address      | A0-A9         |

| Page size           | 1 KB          |

# 64Mx16 DDR2 PIN CONFIGURATION(Top view: see balls through package)

1 2 3 7 8

| VDD     | NC     | VSS        | Α | VSSQ    | UDQS    | VDDQ |

|---------|--------|------------|---|---------|---------|------|

| DQ14    | VSSQ   | UDM        | В | UDQS    | VSSQ    | DQ15 |

| VDDQ    | DQ9    | VDDQ       | С | VDDQ    | DQ8     | VDDQ |

| DQ12    | VSSQ   | DQ11       | D | DQ10    | VSSQ    | DQ13 |

| VDD     | NC     | VSS        | Е | VSSQ    | LDQS    | VDDQ |

| DQ6     | VSSQ   | LDM        | F | LDQS    | VSSQ    | DQ7  |

| VDDQ    | DQ1    | VDDQ       | G | VDDQ    | DQ0     | VDDQ |

| DQ4     | VSSQ   | DQ3        | Н | DQ2     | VSSQ    | DQ5  |

| VDDL    | VREF   | VSS        | J | VSSDL   | CK      | VDD  |

|         | CKE    | WE         | K | RAS     | CK      | ODT  |

| NC, BA2 | BA0    | BA1        | L | CAS     | CS      |      |

|         | A10/AP | A1         | M | A2      | A0      | VDD  |

| VSS     | А3     | <b>A</b> 5 | N | A6      | A4      |      |

|         | A7     | A9         | Р | A11     | A8      | VSS  |

| VDD     | A12    | NC, A14    | R | NC, A15 | NC, A13 |      |

## **ROW AND COLUMN ADDRESS TABLE**

| ITEMS               | 64Mx16        |

|---------------------|---------------|

| # of Bank           | 8             |

| Bank Address        | BA0, BA1, BA2 |

| Auto Precharge Flag | A10/AP        |

| Row Address         | A0 - A12      |

| Column Address      | A0-A9         |

| Page size           | 2 KB          |

# **IDD Test Conditions**

(IDD values are for full operating range of Voltage and Temperature, Notes 1-5)

| Symbol | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                     | Units |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|-------|--|

| IDD0   | Operating one bank active-precharge current; ${}^{t}CK = {}^{t}CK(IDD)$ , ${}^{t}RC = {}^{t}RC(IDD)$ , ${}^{t}RAS = {}^{t}RAS min(IDD)$ ; CKE is HIGH, $\overline{CS}$ is HIGH between valid commands; Address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |       |  |

| IDD1   | Operating one bank active-read-precharge current; IOUT = 0mA;BL = 4, CL = CL(IDD), AL = 0; $^{\dagger}$ CK = $^{\dagger}$ CK(IDD), $^{\dagger}$ RC = $^{\dagger}$ RC (IDD), $^{\dagger}$ RAS = $^{\dagger}$ RASmin(IDD), $^{\dagger}$ RCD = $^{\dagger}$ RCD(IDD); CKE is HIGH, CS is HIGH between valid commands; Address bus inputs are SWITCHING; Data pattern is same as IDD4W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |       |  |

| IDD2P  | <b>Precharge power-down current</b> ; All banks idle; $tCK = tCK(ID)$ and address bus inputs are STABLE; Data bus inputs are FLOATING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                     | mA    |  |

| IDD2Q  | <b>Precharge quiet standby current</b> ; All banks idle; <sup>t</sup> CK = <sup>t</sup> CK(IDE Other control and address bus inputs are STABLE; Data bus inputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                     | mA    |  |

| IDD2N  | <b>Precharge standby current</b> ; All banks idle; ${}^{t}CK = {}^{t}CK(IDD)$ ; CKE is HIGH, $\overline{CS}$ is HIGH; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                     |       |  |

| IDD3P  | Active power-down current; All banks open; ${}^{\dagger}CK = {}^{\dagger}CK(IDD)$ ; Fast PDN Exit MRS(12) = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                     | mA    |  |

| IDD3P  | CKE is LOW; Other control and address bus inputs are STABLE; Data bus inputs are FLOATING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Slow PDN Exit MRS(12) = 1                                                           | mA    |  |

| IDD3N  | Active standby current; All banks open; <sup>†</sup> CK = <sup>†</sup> CK(IDD), <sup>†</sup> RAS = <sup>†</sup> RASmax(IDD), <sup>†</sup> RP = <sup>†</sup> RP(IDD); CKE is HIGH, CS is HIGH between valid commands; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                     |       |  |

| IDD4W  | <b>Operating burst write current</b> ; All banks open, Continuous burst $AL = 0$ ; ${}^{\dagger}CK = {}^{\dagger}CK(IDD)$ , ${}^{\dagger}RAS = {}^{\dagger}RASmax(IDD)$ , ${}^{\dagger}RP = {}^{\dagger}RP(IDD)$ ; between valid commands; Address bus inputs are SWITCHING; Date of the property of the pr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | CKE is HIGH, CS is HIGH                                                             | mA    |  |

| IDD4R  | Operating burst read current; All banks open, Continuous burs $CL = CL(IDD)$ , $AL = 0$ ; $^{\dagger}CK = ^{\dagger}CK(IDD)$ , $^{\dagger}RAS = ^{\dagger}RASmax(IDD)$ , $^{\dagger}RAS = ^{\dagger}RASm$ | $P = {}^{t}RP(IDD); CKE is HIGH, \overline{CS}$                                     | mA    |  |

| IDD5B  | <b>Burst refresh current</b> ; †CK = †CK(IDD); Refresh command at every †RFC(IDD) interval; CKE is HIGH, CS is HIGH between valid commands; Other control and address bus inputs are SWITCH-ING; Data bus inputs are SWITCHING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                     |       |  |

| IDD6   | Self refresh current; CK and CK at 0V; CKE £ 0.2V; Other control and address bus inputs are FLOATING; Data bus inputs are FLOATING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                     |       |  |

| IDD7   | Operating bank interleave read current; All bank interleaving $= CL(IDD)$ , $AL = {}^{\dagger}RCD(IDD) - 1 {}^{\dagger}CK(IDD)$ ; ${}^{\dagger}CK = {}^{\dagger}CK(IDD)$ , ${}^{\dagger}RC = {}^{\dagger}RCD = 1 {}^{\dagger}CK(IDD)$ ; CKE is HIGH, $\overline{CS}$ is HIGH between valid comm STABLE during DESELECTs; Data pattern is same as IDD4R; - Refedetailed timing conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RC(IDD), <sup>t</sup> RRD = <sup>t</sup> RRD(IDD),<br>nands; Address bus inputs are | mA    |  |

#### Note:

- 1. VDDQ = 1.8 +/- 0.1V; VDD = 1.8 +/- 0.1V (exclusively VDDQ = 1.9 +/- 0.1V; VDD = 1.9 +/- 0.1V for C3 speed grade)

- 2. IDD specifications are tested after the device is properly initialized

- 3. Input slew rate is specified by AC Parametric Test Condition

- 4. IDD parameters are specified with ODT disabled.

- 5. Data bus consists of DQ, DM, DQS, DQS, RDQS, RDQS, LDQS, UDQS, and UDQS. IDD values must be met with all combinations of EMRS bits 10 and 11.

- 6. Definitions for IDD

LOW is defined as Vin £ VILAC(max)

HIGH is defined as Vin Š VIHAC(min)

STABLE is defined as inputs stable at a HIGH or LOW level

FLOATING is defined as inputs at VREF = VDDQ/2

SWITCHING is defined as: inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control signals, and inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.

# 2. Maximum DC Ratings

# 2.1 Absolute Maximum DC Ratings

| Symbol                            | Parameter                                                                         | Rating          | Units | Notes |

|-----------------------------------|-----------------------------------------------------------------------------------|-----------------|-------|-------|

| VDD                               | Voltage on VDD pin relative to Vss                                                | - 1.0 V ~ 2.3 V | V     | 1     |

| VDDQ                              | Voltage on VDDQ pin relative to Vss                                               | - 0.5 V ~ 2.3 V | V     | 1     |

| VDDL                              | Voltage on VDDL pin relative to Vss                                               | - 0.5 V ~ 2.3 V | V     | 1     |

| V <sub>IN,</sub> V <sub>OUT</sub> | Voltage on any pin relative to Vss                                                | - 0.5 V ~ 2.3 V | V     | 1     |

| T <sub>STG</sub>                  | Storage Temperature                                                               | -55 to +100     | °C    | 1, 2  |

| lı                                | Input leakage current; any input 0V VIN VDD; all other balls not under test = 0V) | -2 uA ~ 2 uA    | uA    |       |

| loz                               | Output leakage current; 0V VOUT VDDQ; DQ and ODT disabled                         | -5 uA ~ 5 uA    | uA    |       |

#### Note:

- 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

- 2. Storage Temperature is the case surface temperature on the  $\chi \epsilon \nu \tau \epsilon \rho / top$  side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

## 2.2 Operating Temperature Condition

| Symbol            | Parameter             | Rating  | Units | Notes |

|-------------------|-----------------------|---------|-------|-------|

| T <sub>OPER</sub> | Operating Temperature | 0 to 95 | °C    | 1,2   |

#### Note:

- 1. Operating Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please refer to JESD51-2 standard.

- 2. At  $85 \sim 95^{\circ}$  T<sub>OPER</sub>, Double refresh rate(tREFI: 3.9us) is required, and to enter the self refresh mode at this temperature range, an EMRS command is required to change internal refresh rate.

# 3. AC & DC Operating Conditions

# 3.1 DC Operating Conditions

## 3.1.1 Recommended DC Operating Conditions (SSTL\_1.8)

| C      | D                         |           | Rating    |           | 11-24- | Nista |

|--------|---------------------------|-----------|-----------|-----------|--------|-------|

| Symbol | Parameter                 | Min.      | Тур.      | Max.      | Units  | Notes |

| VDD    | Supply Voltage            | 1.7       | 1.8       | 1.9       | V      | 1     |

| VDDL   | Supply Voltage for DLL    | 1.7       | 1.8       | 1.9       | V      | 1,2   |

| VDDQ   | Supply Voltage for Output | 1.7       | 1.8       | 1.9       | V      | 1,2   |

| VREF   | Input Reference Voltage   | 0.49*VDDQ | 0.50*VDDQ | 0.51*VDDQ | mV     | 3,4   |

| VTT    | Termination Voltage       | VREF-0.04 | VREF      | VREF+0.04 | V      | 5     |

#### Note:

- 1. Min. Typ. and Max. values increase by 100mV for C3(DDR2-533 3-3-3) speed option.

- 2. VDDQ tracks with VDD, VDDL tracks with VDD. AC parameters are measured with VDD, VDDQ and VDD.

- 3. The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ

- 4. Peak to peak ac noise on VREF may not exceed +/-2% VREF (dc).

- 5. VTT of transmitting device must track VREF of receiving device.

#### 3.1.2 ODT DC electrical characteristics

| PARAMETER/CONDITION                                        | SYMBOL    | MIN | NOM | MAX | UNITS | NOTES |

|------------------------------------------------------------|-----------|-----|-----|-----|-------|-------|

| Rtt effective impedance value for EMRS(A6,A2)=0,1; 75 ohm  | Rtt1(eff) | 60  | 75  | 90  | ohm   | 1     |

| Rtt effective impedance value for EMRS(A6,A2)=1,0; 150 ohm | Rtt2(eff) | 120 | 150 | 180 | ohm   | 1     |

| Rtt effective impedance value for EMRS(A6,A2)=1,1; 50 ohm  | Rtt3(eff) | 40  | 50  | 60  | ohm   | 1     |

| Deviation of VM with respect to VDDQ/2                     | delta VM  | -6  |     | +6  | %     | 1     |

#### Note:

1. Test condition for Rtt measurements

Measurement Definition for Rtt(eff): Apply  $V_{IH}$  (ac) and  $V_{IL}$  (ac) to test pin separately, then measure current  $I(V_{IH}$  (ac)) and  $I(V_{II}$  (ac)) respectively.  $V_{IH}$  (ac),  $V_{IL}$  (ac), and VDDQ values defined in SSTL\_18

$$Rtt(eff) = \frac{V_{IH} (ac) - V_{IL} (ac)}{I(V_{IH} (ac)) - I(V_{IL} (ac))}$$

Measurement Definition for VM: Measurement Voltage at test pin(mid point) with no load.

$$delta VM = \frac{2 \times Vm}{VDDQ} - 1 \times 100\%$$

## 3.2 DC & AC Logic Input Levels

#### 3.2.1 Input DC Logic Level

| Symbol               | Parameter           | Min.         | Max.         | Units | Notes |

|----------------------|---------------------|--------------|--------------|-------|-------|

| V <sub>IH</sub> (dc) | dc input logic high | VREF + 0.125 | VDDQ + 0.3   | V     |       |

| V <sub>IL</sub> (dc) | dc input logic low  | - 0.3        | VREF - 0.125 | V     |       |

#### 3.2.2 Input AC Logic Level

| C                    | D                   | DDR2 4       | 00,533       | DDR2 6       | 67,800       | 11    | Blotos |

|----------------------|---------------------|--------------|--------------|--------------|--------------|-------|--------|

| Symbol               | Parameter           | Min.         | Max.         | Min.         | Max.         | Units | Notes  |

| V <sub>IH</sub> (ac) | ac input logic high | VREF + 0.250 | -            | VREF + 0.200 | -            | V     |        |

| V <sub>IL</sub> (ac) | ac input logic low  | -            | VREF - 0.250 | -            | VREF - 0.200 | V     |        |

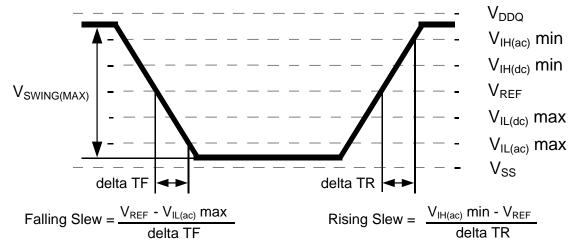

## 3.2.3 AC Input Test Conditions

| Symbol                  | Condition                               | Value                  | Units | Notes |

|-------------------------|-----------------------------------------|------------------------|-------|-------|

| V <sub>REF</sub>        | Input reference voltage                 | 0.5 * V <sub>DDQ</sub> | V     | 1     |

| V <sub>SWING(MAX)</sub> | Input signal maximum peak to peak swing | 1.0                    | V     | 1     |

| SLEW                    | Input signal minimum slew rate          | 1.0                    | V/ns  | 2, 3  |

#### Note:

- Input waveform timing is referenced to the input signal crossing through the V<sub>REF</sub> level applied to the device under test.

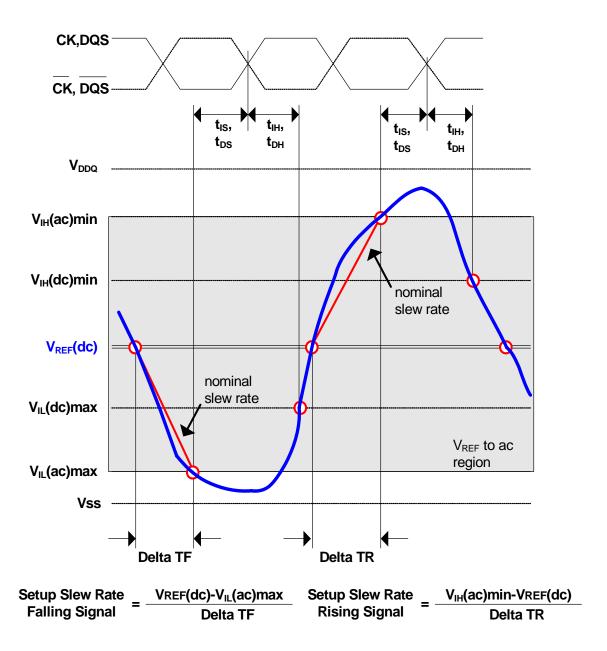

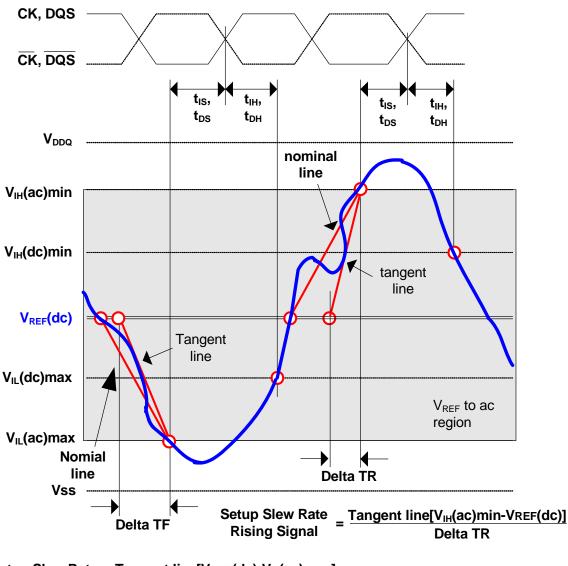

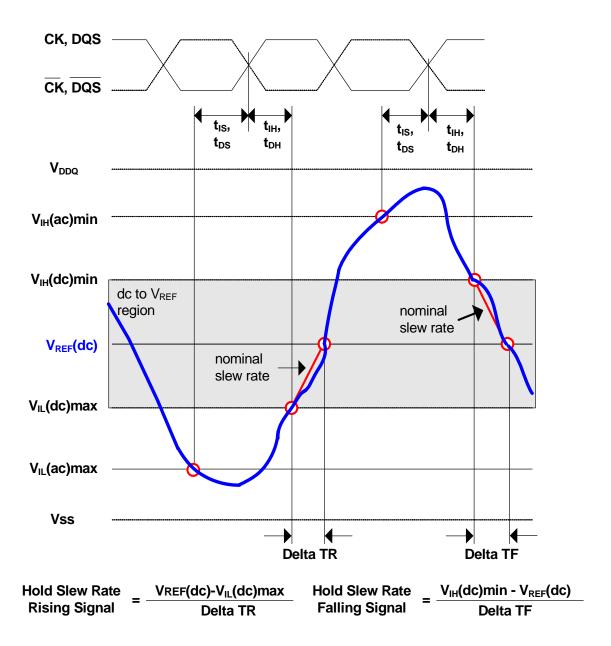

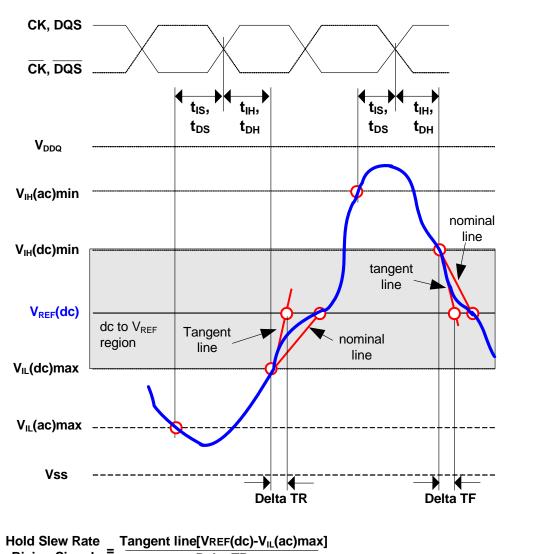

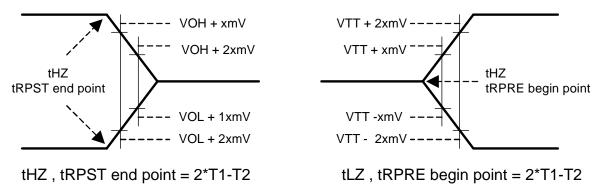

- 2. The input signal minimum slew rate is to be maintained over the range from  $V_{REF}$  to  $V_{IH(ac)}$  min for rising edges and the range from  $V_{REF}$  to  $V_{IL(ac)}$  max for falling edges as shown in the figure below.

- 3. AC timings are referenced with input waveforms switching from VIL(ac) to VIH(ac) on the positive transitions and VIH(ac) to VIL(ac) on the negative transitions.

< Figure : AC Input Test Signal Waveform>

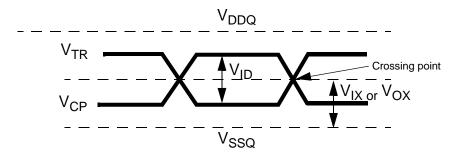

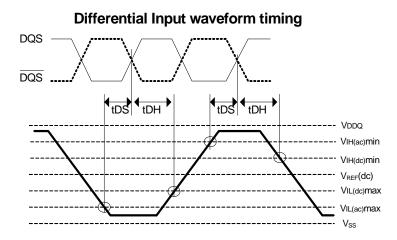

# 3.2.4 Differential Input AC logic Level

| Symbol               | Parameter                           | Min.               | Max.               | Units | Notes |

|----------------------|-------------------------------------|--------------------|--------------------|-------|-------|

| V <sub>ID</sub> (ac) | ac differential input voltage       | 0.5                | VDDQ + 0.6         | V     | 1     |

| V <sub>IX</sub> (ac) | ac differential cross point voltage | 0.5 * VDDQ - 0.175 | 0.5 * VDDQ + 0.175 | V     | 2     |

#### Note:

- 1. VIN(DC) specifies the allowable DC execution of each input of differential pair such as CK, CK, DQS, DQS, LDQS, LDQS, UDQS and UDQS.

- VID(DC) specifies the input differential voltage |VTR -VCP | required for switching, where VTR is the true input (such as CK, DQS, LDQS or UDQS) level and VCP is the complementary input (such as CK, DQS, LDQS or UDQS) level.

The minimum value is equal to VIH(DC) - V IL(DC).

< Differential signal levels >

#### Note:

- 1. VID(AC) specifies the input differential voltage |VTR -VCP | required for switching, where VTR is the true input signal

- (such as CK, DQS, LDQS or UDQS) and VCP is the complementary input signal (such as  $\overline{CK}$ ,  $\overline{DQS}$ ,  $\overline{LDQS}$  or  $\overline{UDQS}$ ). The minimum value is equal to V IH(AC) V IL(AC).

- 2. The typical value of VIX(AC) is expected to be about 0.5 \* VDDQ of the transmitting device and VIX(AC) is expected to track variations in VDDQ. VIX(AC) indicates the voltage at which differential input signals must cross.

#### 3.2.5 Differential AC output parameters

| Symbol               | Parameter                           | Min.               | Max.               | Units | Notes |

|----------------------|-------------------------------------|--------------------|--------------------|-------|-------|

| V <sub>OX</sub> (ac) | ac differential cross point voltage | 0.5 * VDDQ - 0.125 | 0.5 * VDDQ + 0.125 | V     | 1     |

#### Note:

1. The typical value of VOX(AC) is expected to be about 0.5 \* V DDQ of the transmitting device and VOX(AC) is expected to track variations in VDDQ. VOX(AC) indicates the voltage at  $\omega\eta\iota\chi\eta$  differential output signals must cross.

# 3.3 Output Buffer Characteristics

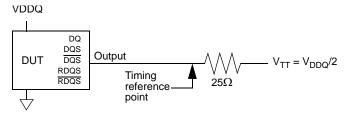

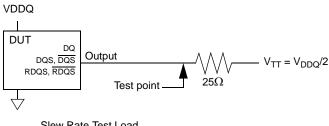

#### 3.3.1 Output AC Test Conditions

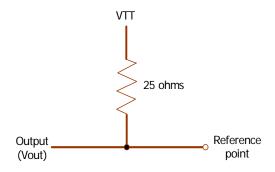

| Symbol           | Parameter                                 | SSTL_18 Class II       | Units | Notes |

|------------------|-------------------------------------------|------------------------|-------|-------|

| V <sub>OTR</sub> | Output Timing Measurement Reference Level | 0.5 * V <sub>DDQ</sub> | V     | 1     |

#### Note:

1. The VDDQ of the device under test is referenced.

#### 3.3.2 Output DC Current Drive

| Symbol              | Parameter                        | SSTI_18 | Units | Notes   |

|---------------------|----------------------------------|---------|-------|---------|

| I <sub>OH(dc)</sub> | Output Minimum Source DC Current | - 13.4  | mA    | 1, 3, 4 |

| I <sub>OL(dc)</sub> | Output Minimum Sink DC Current   | 13.4    | mA    | 2, 3, 4 |

#### Note:

- 1.  $V_{DDQ} = 1.7 \text{ V}$ ;  $V_{OUT} = 1420 \text{ mV}$ .  $(V_{OUT} V_{DDQ})/I_{OH}$  must be less than 21 ohm for values of  $V_{OUT}$  between  $V_{DDQ}$  and  $V_{DDQ}$  280 mV.

- 2.  $V_{DDQ} = 1.7 \text{ V}$ ;  $V_{OUT} = 280 \text{ mV}$ .  $V_{OUT}/I_{OL}$  must be less than 21 ohm for values of  $V_{OUT}$  between 0 V and 280 mV.

- 3. The dc value of  $V_{REF}$  applied to the receiving device is set to  $V_{TT}$

- 4. The values of I<sub>OH(dc)</sub> and I<sub>OL(dc)</sub> are based on the conditions given in Notes 1 and 2. They are used to test device drive current capability to ensure V<sub>IH</sub> min plus a noise margin and V<sub>IL</sub> max minus a noise margin are delivered to an SSTL\_18 receiver. The actual current values are derived by shifting the desired driver operating point (see Section 3.3) along a 21 ohm load line to define a convenient driver current for measurement.

#### 3.3.3 OCD default characteristics

| Description                                    | Parameter | Min | Nom | Max | Unit | Notes       |

|------------------------------------------------|-----------|-----|-----|-----|------|-------------|

| Output impedance                               |           | -   | -   | -   | ohms | 1           |

| Output impedance step size for OCD calibration |           | 0   |     | 1.5 | ohms | 6           |

| Pull-up and pull-down mismatch                 |           | 0   |     | 4   | ohms | 1,2,3       |

| Output slew rate                               | Sout      | 1.5 | -   | 5   | V/ns | 1,4,5,6,7,8 |

#### Note:

- 1. Absolute Specifications ( Toper; VDD =  $\pm 1.8V \pm 0.1V$ , VDDQ =  $\pm 1.8V \pm 0.1V$ )

- Impedance measurement condition for output source dc current: VDDQ=1.7V; VOUT=1420mV; (VOUT-VDDQ)/Ioh must be less than 23.4 ohms for values of VOUT between VDDQ and VDDQ-280mV.

Impedance measurement condition for output sink dc current: VDDQ = 1.7V; VOUT = 280mV; VOUT/IoI must be less than 23.4 ohms for values of VOUT between 0V and 280mV.

- 3. Mismatch is absolute value between pull-up and pull-dn, both are measured at same temperature and voltage.

- 4. Slew rate measured from vil(ac) to vih(ac).

- 5. The absolute value of the slew rate as measured from DC to DC is equal to or greater than the slew rate as measured from AC to AC. This is guaranteed by design and characterization.

- 6. This represents the step size when the OCD is near 18 ohms at nominal conditions across all process corners/variations and represents only the DRAM uncertainty. A 0 ohm value(no calibration) can only be achieved if the OCD impedance is 18 ohms +/- 0.75 ohms under nominal conditions.

#### **Output Slew rate load:**

- 7. DRAM output slew rate specification applies to 400, 533 and 667 MT/s speed bins.

- 8. Timing skew due to DRAM output slew rate mis-match between DQS / DQS and associated DQs is included in tDQSQ and tQHS specification.

# 3.4 IDD Specifications & Test Conditions

# IDD Specifications(max)

| Symbol |              | DDR | 2 400 | DDR2 533 |     | DDR2 667 |     | DDR2 800 |     |     | Units |     |    |

|--------|--------------|-----|-------|----------|-----|----------|-----|----------|-----|-----|-------|-----|----|

|        |              | x4  | х8    | x4       | х8  | x16      | x4  | х8       | x16 | x4  | х8    | x16 |    |

| ID     | DO           | 60  | 60    | 65       | 65  | 85       | 70  | 70       | 90  | 75  | 75    | 95  | mA |

| ID     | D1           | 70  | 70    | 75       | 75  | 110      | 80  | 80       | 115 | 85  | 85    | 120 | mA |

| IDI    | D2P          | 8   | 8     | 8        | 8   | 8        | 8   | 8        | 8   | 8   | 8     | 8   | mA |

| IDI    | D2Q          | 22  | 22    | 27       | 27  | 27       | 30  | 30       | 30  | 32  | 32    | 32  | mA |

| IDI    | D2N          | 30  | 30    | 35       | 35  | 35       | 40  | 40       | 40  | 45  | 45    | 45  | mA |

| IDD3P  | F            | 20  | 20    | 20       | 20  | 20       | 25  | 25       | 25  | 25  | 25    | 25  | mA |

| IDD3F  | S            | 9   | 9     | 9        | 9   | 9        | 9   | 9        | 9   | 9   | 9     | 9   | mA |

| IDI    | O3N          | 35  | 35    | 45       | 45  | 45       | 50  | 50       | 50  | 55  | 55    | 55  | mA |

| IDE    | 04W          | 100 | 100   | 125      | 125 | 160      | 150 | 150      | 195 | 170 | 170   | 225 | mA |

| IDI    | D4R          | 100 | 100   | 125      | 125 | 160      | 150 | 150      | 195 | 170 | 170   | 225 | mA |

| ID     | D5           | 165 | 165   | 165      | 165 | 165      | 175 | 175      | 175 | 175 | 175   | 175 | mA |

|        | Normal       | 8   | 8     | 8        | 8   | 8        | 8   | 8        | 8   | 8   | 8     | 8   | mA |

| IDD6   | Low<br>power | 5   | 5     | 5        | 5   | 5        | 5   | 5        | 5   | 5   | 5     | 5   | mA |

| ID     | D7           | 165 | 165   | 175      | 175 | 260      | 180 | 180      | 265 | 185 | 185   | 270 | mA |

## **IDD Test Conditions**

(IDD values are for full operating range of Voltage and Temperature, Notes 1-5)

| Symbol | Conditions                                                                                                                                                                                                                                                                            |                                             | Units |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-------|--|

| IDD0   | <b>Operating one bank active-precharge current</b> ; <sup>†</sup> CK = <sup>†</sup> CK(IDD min(IDD) ; CKE is HIGH, CS is HIGH between valid commands; Add ING; Data bus inputs are SWITCHING                                                                                          |                                             | mA    |  |

| IDD1   | Operating one bank active-read-precharge χυρρεντ ; IOUT = $=$ 0; $^t$ CK = $^t$ CK(IDD), $^t$ RC = $^t$ RC (IDD), $^t$ RAS = $^t$ RASmin(IDD), $^t$ RC is HIGH between valid commands ; Address bus inputs are SWI as IDD4W                                                           | $D = {}^{t}RCD(IDD)$ ; CKE is HIGH,         | mA    |  |

| IDD2P  | <b>Precharge power-down current</b> ; All banks idle; $tCK = tCK(ID)$ and address bus inputs are STABLE; Data bus inputs are FLOATING                                                                                                                                                 |                                             | mA    |  |

| IDD2Q  | <b>Precharge quiet standby current</b> ; All banks idle; ${}^{t}CK = {}^{t}CK(IDD)$ Other control and address bus inputs are STABLE; Data bus inputs                                                                                                                                  |                                             | mA    |  |

| IDD2N  | <b>Precharge standby current</b> ; All banks idle; ${}^{t}CK = {}^{t}CK(IDD)$ ; CKE is HIGH, $\overline{CS}$ is HIGH; Other control and address bus inputs are SWITCHING; Data bus inputs are SWITCHING                                                                               |                                             |       |  |

| IDD3P  | <b>Active power-down current</b> ; All banks open; <sup>†</sup> CK = <sup>†</sup> CK(IDD); CKE is LOW; Other control and address bus inputs are STABLE;                                                                                                                               | Fast PDN Exit MRS(12) = 0                   | mA    |  |

|        | Data bus inputs are FLOATING                                                                                                                                                                                                                                                          | Slow PDN Exit MRS(12) = 1                   | mA    |  |

| IDD3N  | <b>Active standby current</b> ; All banks open; ${}^{t}CK = {}^{t}CK(IDD)$ , ${}^{t}RAS = {}^{t}RP(IDD)$ ; CKE is HIGH, $\overline{CS}$ is HIGH between valid commands; Ot inputs are SWITCHING; Data bus inputs are SWITCHING                                                        |                                             | mA    |  |

| IDD4W  | <b>Operating burst write current</b> ; All banks open, Continuous burs $AL = 0$ ; $^{\dagger}CK = ^{\dagger}CK(IDD)$ , $^{\dagger}RAS = ^{\dagger}RASmax(IDD)$ , $^{\dagger}RP = ^{\dagger}RP(IDD)$ ; Cl valid commands; Address bus inputs are SWITCHING; Data bus inputs            | KE is HIGH, $\overline{CS}$ is HIGH between | mA    |  |

| IDD4R  | Operating burst read current; All banks open, Continuous burst reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = 0; tCK = tCK(IDD), tRAS = tRASmax(IDD), tRP = tRP(IDD); CKE is HIGH, CS is HIGH between valid commands; Address bus inputs are SWITCHING;; Data pattern is same as IDD4W |                                             |       |  |

| IDD5B  | <b>Burst refresh current</b> ; ${}^tCK = {}^tCK(IDD)$ ; Refresh command at every ${}^tRFC(IDD)$ interval; CKE is HIGH, $\overline{CS}$ is HIGH between valid commands; Other control and address bus inputs are SWITCH-ING; Data bus inputs are SWITCHING                             |                                             |       |  |

| IDD6   | <b>Self refresh current</b> ; CK and CK at 0V; CKE £ 0.2V; Other contro FLOATING; Data bus inputs are FLOATING                                                                                                                                                                        | I and address bus inputs are                | mA    |  |

FLOATING is defined as inputs at VREF = VDDQ/2

SWITCHING is defined as: inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control signals, and inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.

|  | Operating bank interleave read current; All bank interleaving reads, IOUT = 0mA; BL = 4, CL = CL(IDD), AL = <sup>†</sup> RCD(IDD)-1* <sup>†</sup> CK(IDD); <sup>†</sup> CK = <sup>†</sup> CK(IDD), <sup>†</sup> RC = <sup>†</sup> RC(IDD), <sup>†</sup> RRD = <sup>†</sup> RRD(IDD), <sup>†</sup> RCD = 1* <sup>†</sup> CK(IDD); CKE is HIGH, CS is HIGH between valid commands; Address bus inputs are STABLE during DESELECTs; Data pattern is same as IDD4R; - Refer to the following page for detailed timing conditions | mA |

|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

#### Note:

- 1. VDDQ = 1.8 +/- 0.1V; VDD = 1.8 +/- 0.1V (exclusively VDDQ = 1.9 +/- 0.1V; VDD = 1.9 +/- 0.1V for C3 speed grade)

- 2. IDD specifications are tested after the device is properly initialized

- 3. Input slew rate is specified by AC Parametric Test Condition

- 4. IDD parameters are specified with ODT disabled.

- 5. Data bus consists of DQ, DM, DQS, DQS, RDQS, RDQS, LDQS, UDQS, and UDQS. IDD values must be met with all combinations of EMRS bits 10 and 11.

- 6. Definitions for IDD

LOW is defined as Vin £ VILAC(max)

HIGH is defined as Vin Š VIHAC(min)

STABLE is defined as inputs stable at a HIGH or LOW level

FLOATING is defined as inputs at VREF = VDDQ/2

SWITCHING is defined as: inputs changing between HIGH and LOW every other clock cycle (once per two clocks) for address and control signals, and inputs changing between HIGH and LOW every other data transfer (once per clock) for DQ signals not including masks or strobes.

## For purposes of IDD testing, the following parameters are to be utilized

|                             | DDR2        | 2-800 | DDR2-<br>667 | DDR2-<br>533 | DDR2-<br>400 |       |

|-----------------------------|-------------|-------|--------------|--------------|--------------|-------|

| Parameter                   | 5-5-5 6-6-6 |       | 5-5-5        | 4-4-4        | 3-3-3        | Units |

| CL(IDD)                     | 5           | 6     | 5            | 4            | 3            | tCK   |

| tRCD(IDD)                   | 12.5        | 15    | 15           | 15           | 15           | ns    |

| <sup>t</sup> RC(IDD)        | 57.5        | 60    | 60           | 60           | 55           | ns    |

| tRRD(IDD)-x4/x8             | 7.5         | 7.5   | 7.5          | 7.5          | 7.5          | ns    |

| <sup>†</sup> RRD(IDD)-x16   | 10          | 10    | 10           | 10           | 10           | ns    |

| <sup>†</sup> CK(IDD)        | 2.5         | 2.5   | 3            | 3.75         | 5            | ns    |

| <sup>t</sup> RASmin(IDD)    | 45          | 45    | 45           | 45           | 40           | ns    |

| tRASmax(IDD)                | 70000       | 70000 | 70000        | 70000        | 70000        | ns    |

| <sup>†</sup> RP(IDD)        | 12.5        | 15    | 15           | 15           | 15           | ns    |

| <sup>†</sup> RFC(IDD)-256Mb | 75          | 75    | 75           | 75           | 75           | ns    |

| <sup>†</sup> RFC(IDD)-512Mb | 105         | 105   | 105          | 105          | 105          | ns    |

| <sup>†</sup> RFC(IDD)-1Gb   | 127.5       | 127.5 | 127.5        | 127.5        | 127.5        | ns    |

| <sup>t</sup> RFC(IDD)-2Gb   | 197.5       | 197.5 | 197.5        | 197.5        | 197.5        | ns    |

#### **Detailed IDD7**

The detailed timings are shown below for IDD7. Changes will be required if timing parameter changes are made to the specification.

Legend: A = Active; RA = Read with Autoprecharge; D = Deselect

#### IDD7: Operating Current: All Bank Interleave Read operation

All banks are being interleaved at minimum  ${}^{\dagger}RC(IDD)$  without violating  ${}^{\dagger}RRD(IDD)$  using a burst length of 4. Control and address bus inputs are STABLE during DESELECTs. IOUT = 0mA

#### Timing Patterns for 4 bank devices x4/x8/x16

-DDR2-400 4/4/4: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D D D

-DDR2-400 3/3/3: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D D

-DDR2-533 5/4/4: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D D

-DDR2-533 4/4/4: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D D

Timing Patterns for 8 bank devices x4/8

-DDR2-400 all bins: A0 RA0 A1 RA1 A2 RA2 A3 RA3 A4 RA4 A5 RA5 A6 RA6 A7 RA7

-DDR2-533 all bins: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D A4 RA4 A5 RA5 A6 RA6 A7 RA7 D D

Timing Patterns for 8 bank devices x16

-DDR2-400 all bins: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D A4 RA4 A5 RA5 A6 RA6 A7 RA7 D D

-DDR2-533 all bins: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 D A6 RA6 D A7 RA7 D D D

# 3.5. Input/Output Capacitance

| Parameter                                              | Symbol |     | 2 400<br>2 533 | DDR: | Units |    |

|--------------------------------------------------------|--------|-----|----------------|------|-------|----|

|                                                        | ,      | Min | Max            | Min  | Max   |    |

| Input capacitance, CK and $\overline{\text{CK}}$       | ССК    | 1.0 | 2.0            | 1.0  | 2.0   | pF |

| Input capacitance delta, CK and $\overline{\text{CK}}$ | CDCK   | х   | 0.25           | х    | 0.25  | pF |

| Input capacitance, all other input-only pins           | CI     | 1.0 | 2.0            | 1.0  | 2.0   | pF |

| Input capacitance delta, all other input-only pins     | CDI    | х   | 0.25           | х    | 0.25  | pF |

| Input/output capacitance, DQ, DM, DQS, DQS             | CIO    | 2.5 | 4.0            | 2.5  | 3.5   | pF |

| Input/output capacitance delta, DQ, DM, DQS, DQS       | CDIO   | х   | 0.5            | х    | 0.5   | pF |

# 4. Electrical Characteristics & AC Timing Specification

( 0 % %  $T_{CASE}$  % 95% ;  $V_{DDQ}$  = 1.8 V +/- 0.1V;  $V_{DD}$  = 1.8V +/- 0.1V)

# Refresh Parameters by Device Density

| Parameter                              |       | Symbol                         | 256Mb | 512Mb | 1Gb   | 2Gb | 4Gb   | Units |

|----------------------------------------|-------|--------------------------------|-------|-------|-------|-----|-------|-------|

| Refresh to Active/Refresh command time |       | tRFC                           | 75    | 105   | 127.5 | 195 | 327.5 | ns    |

| Average periodic refresh interval      |       | 0 近 駅 T <sub>CASE</sub> 駅 95近  | 7.8   | 7.8   | 7.8   | 7.8 | 7.8   | ns    |

| Average periodic refresit interval     | tREFI | 85℃ ≤. T <sub>CASE</sub> ℜ 95℃ | 3.9   | 3.9   | 3.9   | 3.9 | 3.9   | ns    |

# DDR2 SDRAM speed bins and tRCD, tRP and tRC for corresponding bin