# 3.3V/5V 3.2Gbps CML LOW-POWER LIMITING POST AMPLIFIER w/TTL SD

SY88823V

### **FEATURES**

- Multi-rate up to 3.2Gbps operation

- Wide gain-bandwidth product

- · 38dB differential gain

- · 2GHz 3dB bandwidth

- Low noise 50Ω CML data outputs

- 800mV<sub>pp</sub> output swing

- 60ps edge rates

- 5ps<sub>rms</sub> typ. random jitter

- 15ps<sub>pp</sub> typ. deterministic jitter

- Chatter-free, Signal-Detect (SD) output

- · 4.6dB electrical hysteresis

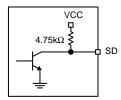

- OC-TTL output with internal 4.75k $\Omega$  pull-up resistor

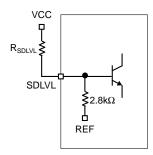

- Programmable SD sensitivity using single external resistor

- Integrated input bias reference

- TTL EN input allows feedback from SD

- Wide operating range

- Single 3.3V  $\pm$ 10% or 5V  $\pm$ 10% power supply

- -40°C to +85°C ambient industrial temperature range

- Available in tiny 10-pin EPAD-MSOP and 16-pin MLF<sup>™</sup> packages

### **APPLICATIONS**

- 1.25Gbps and 2.5Gbps Gigabit Ethernet

- 1.062Gbps and 2.125Gbps Fibre Channel

- 155Mbps, 622Gbps, 1.25Gbps, and 2.5Gbps SONET/ SDH

- Gigabit interface converter (GBIC)

- Small form factor (SFF) and small form factor pluggable (SFP) transceivers

- Parallel 10G Ethernet

- High-gain line driver and line receiver

# DESCRIPTION

The SY88823V low-power, limiting post amplifier is designed for use in fiber optic receivers. The device connects to typical transimpedance amplifiers (TIAs). The linear signal output from TIAs can contain significant amounts of noise and may vary in amplitude over time. The SY88823V quantizes these signals and outputs typically  $800 \text{mV}_{PP}$  voltage-limited waveforms.

The SY88823V operates from a single +3.3V  $\pm 10\%$  or +5V  $\pm 10\%$  power supply, over an industrial temperature range of -40°C to +85°C. With its wide bandwidth and high gain, signals with data rates up to 3.2Gbps and as small as  $10mV_{pp}$  can be amplified to drive devices with CML inputs or AC-coupled PECL inputs.

The SY88823V incorporates a signal detect (SD), open-collector TTL output with internal 4.75k $\Omega$  pull-up resistor. A programmable, signal-detect level set pin (SDLVL) sets the sensitivity of the input amplitude detection. SD asserts high if the input amplitude rises above the threshold set by SDLVL and de-asserts low otherwise. SD can be fed back to the enable (EN) input to maintain output stability under a loss-of-signal condition. EN de-asserts the true output signal without removing the input signal. Typically 4.6dB SD hysteresis is provided to prevent chattering.

Please see Micrel's website at www.micrel.com for a complete selection of optical module ICs.

The following table summarizes the differences between devices in Micrel's latest family of Limiting Amplifiers.

| Part Number | Integrated 50 $\Omega$<br>Input Termination | LOS<br>or SD | Active LOW or HIGH Enable |

|-------------|---------------------------------------------|--------------|---------------------------|

| SY88773V    | No                                          | LOS          | LOW                       |

| SY88823V    | No                                          | SD           | HIGH                      |

| SY88843V    | Yes                                         | SD           | HIGH                      |

| SY88973V    | Yes                                         | LOS          | LOW                       |

**Table 1. Limiting Amplifiers Selection Guide**

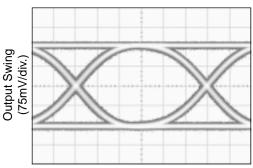

### **TYPICAL PERFORMANCE**

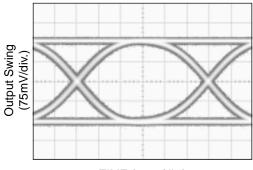

3.3V, 25°C, 10mV  $_{pp}$  Input @3.2Gbps 2  $^{31}$  –1 PRBS,  $R_{LOAD}$  = 50  $\Omega$  to  $V_{CC}$

TIME (50ps/div.)

MicroLeadFrame and MLF are trademarks of Amkor Technology, Inc.

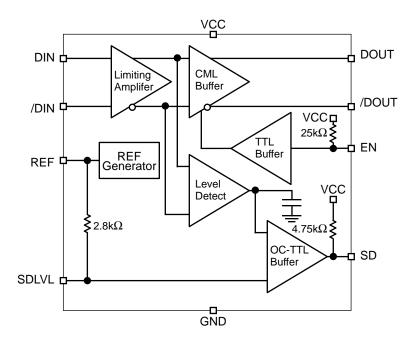

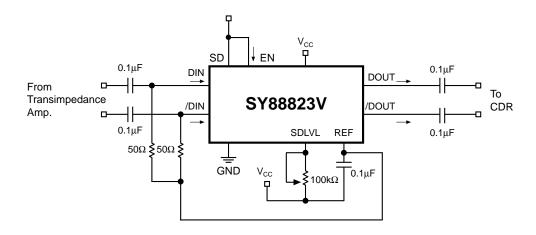

# **FUNCTIONAL BLOCK DIAGRAM**

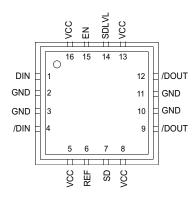

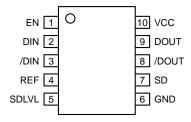

# PACKAGE/ORDERING INFORMATION

# 16-Pin MLF™ (MLF-16)

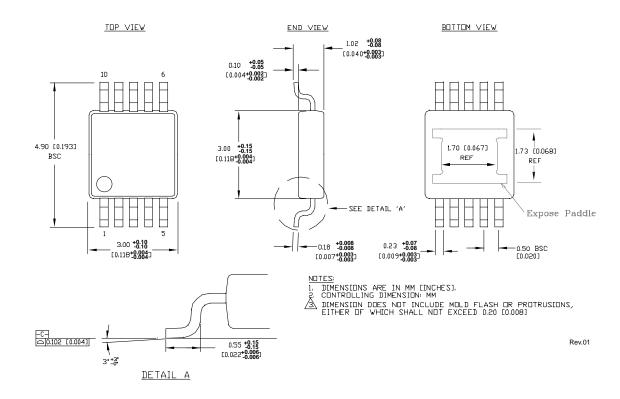

10-Pin EPAD-MSOP (K10-2)

# Ordering Information<sup>(1)</sup>

| Part Number                    | Package<br>Type | Operating<br>Range | Package<br>Marking                      | Lead<br>Finish      |

|--------------------------------|-----------------|--------------------|-----------------------------------------|---------------------|

| SY88823VKI                     | K10-2           | Industrial         | 823V                                    | Sn-Pb               |

| SY88823VKITR <sup>(2)</sup>    | K10-2           | Industrial         | 823V                                    | Sn-Pb               |

| SY88823VMI                     | MLF-16          | Industrial         | 823V                                    | Sn-Pb               |

| SY88823VMITR <sup>(2)</sup>    | MLF-16          | Industrial         | 823V                                    | Sn-Pb               |

| SY88823VEY <sup>(3)</sup>      | K10-2           | Industrial         | 823V with Pb-Free bar-line indicator    | Pb-Free<br>Matte-Sn |

| SY88823VEYTR <sup>(2, 3)</sup> | K10-2           | Industrial         | 823V with Pb-Free bar-line indicator    | Pb-Free<br>Matte-Sn |

| SY88823VMG <sup>(3)</sup>      | MLF-16          | Industrial         | 823V with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu   |

| SY88823VMGTR <sup>(2, 3)</sup> | MLF-16          | Industrial         | 823V with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu   |

### Notes:

- 1. Contact factory for die availability. Dice are guaranteed at  $T_A$  = 25°C, DC Electricals only.

- 2. Tape and Reel

- 3. Pb-Free package is recommended for new designs.

# PIN DESCRIPTION

| Pin Number<br>(MSOP) | Pin Number<br>(MLF™)        | Pin Name    | Туре                                                                       | Pin Function                                                                                                                                      |

|----------------------|-----------------------------|-------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | 15                          | EN          | TTL Input:<br>Default is high.                                             | Enable: De-asserts true data output when low. Incorporates $25k\Omega$ pull-up to VCC.                                                            |

| 2, 3                 | 1, 4                        | DIN, /DIN   | Differential<br>Data Input                                                 | Differential Data Input. Input must be biased to meet common mode range.                                                                          |

| 4                    | 6                           | REF         |                                                                            | Reference Voltage: Bypass with 0.01µF low ESR capacitor from REF to VCC to stabilize SDLVL and REF.                                               |

| 5                    | 14                          | SDLVL       | Input:<br>Default is<br>maximum sensitivity.                               | Signal-Detect Level Set: A resistor from this pin to VCC sets the threshold for the data input amplitude at which the SD output will be asserted. |

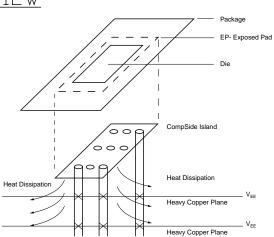

| 6<br>Exposed Pad     | 2, 3, 10, 11<br>Exposed Pad | GND         | Ground                                                                     | Device Ground. Exposed pad must be soldered (or equivalent) to the same potential as the ground pins.                                             |

| 7                    | 7                           | SD          | Open Collector TTL Output with internal $4.75$ k $\Omega$ pull-up resistor | Signal-Detect: asserts high when the data input amplitude rises above the threshold set by SDLVL.                                                 |

| 8, 9                 | 9, 12                       | DOUT, /DOUT | Differential<br>CML Output                                                 | Differential Data Output.                                                                                                                         |

| 10                   | 5, 8, 13, 16                | VCC         | Power Supply                                                               | Positive Power Supply. Bypass with 0.1μF   0.01μF low ESR capacitors. 0.01μF capacitors should be as close as possible to VCC pins.               |

# **Absolute Maximum Ratings**(1)

| Supply Voltage (V <sub>CC</sub> )     | 0V to +7.0V          |

|---------------------------------------|----------------------|

| DIN, /DIN, EN, SDLVL Voltage          | 0 to V <sub>CC</sub> |

| REF Current                           | ±1mA                 |

| SD Current                            | ±5mA                 |

| DOUT, /DOUT Current                   | ±25mA                |

| Storage Temperature (T <sub>S</sub> ) | 65°C to +150°C       |

| Lead Temperature (Soldering, 20 sec.) | 260°C                |

# Operating Ratings<sup>(2)</sup>

| Supply Voltage (V <sub>CC</sub> )         | +3.0V to +3.6V or |

|-------------------------------------------|-------------------|

|                                           | +4.5V to +5.5V    |

| Ambient Temperature (T <sub>A</sub> )     | 40°C to +85°C     |

| Junction Temperature (T <sub>J</sub> )    |                   |

| Package Thermal Resistance <sup>(3)</sup> |                   |

| MLFTM                                     |                   |

| θ <sub>.IA</sub> (Still-Air)              | 61°C/W            |

| Ψ <sub>JB</sub>                           | 38°C/W            |

| EPAD-MSOP                                 |                   |

| θ <sub>JA</sub> (Still-Air)               | 38°C/W            |

| ΨΒ                                        | 22°C/W            |

### DC ELECTRICAL CHARACTERISTICS

$V_{CC}$  = 3.0V to 3.6V or 4.5V to 5.5V;  $R_{LOAD}$  = 50 $\Omega$  to  $V_{CC}$ ;  $T_A$  = -40°C to +85°C; typical values at  $V_{CC}$  = 3.3V,  $T_A$  = 25°C.

| Symbol              | Parameter                     | Condition                                | Min                                              | Тур                                              | Max                                              | Units    |

|---------------------|-------------------------------|------------------------------------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|----------|

| I <sub>CC</sub>     | Power Supply Current          | 3.3V, <b>Note 4</b><br>5V, <b>Note 4</b> |                                                  | 28<br>30                                         | 42<br>45                                         | mA<br>mA |

|                     | Power Supply Current          | 3.3V, <b>Note 5</b><br>5V, <b>Note 5</b> |                                                  | 45<br>47                                         | 62<br>65                                         | mA<br>mA |

| $V_{REF}$           | Reference Voltage             |                                          |                                                  | V <sub>CC</sub> -1.3                             |                                                  | V        |

| V <sub>SDLVL</sub>  | SDLVL Voltage Range           |                                          | V <sub>REF</sub>                                 |                                                  | V <sub>CC</sub>                                  | V        |

| $V_{OH}$            | DOUT, /DOUT HIGH Voltage      | Note 6                                   | V <sub>CC</sub> -0.020                           | V <sub>CC</sub> -0.005                           | V <sub>CC</sub>                                  | V        |

| V <sub>OL</sub>     | DOUT, /DOUT LOW Voltage       | 3.3V, <b>Note 6</b><br>5V, <b>Note 6</b> | V <sub>CC</sub> -0.475<br>V <sub>CC</sub> -0.510 | V <sub>CC</sub> -0.400<br>V <sub>CC</sub> -0.400 | V <sub>CC</sub> -0.350<br>V <sub>CC</sub> -0.350 | V<br>V   |

| V <sub>OFFSET</sub> | Differential Output Offset    | Note 6                                   |                                                  |                                                  | ±80                                              | mV       |

| $\overline{Z_O}$    | Single-Ended Output Impedance |                                          | 40                                               | 50                                               | 60                                               | Ω        |

| V <sub>IHCMR</sub>  | Input Common Mode Range       | Note 7                                   | GND+2.15                                         |                                                  | V <sub>CC</sub>                                  | V        |

### TTL DC ELECTRICAL CHARACTERISTICS

$V_{CC} = 3.0V$  to 3.6V or 4.5V to 5.5V;  $T_A = -40$ °C to +85°C.

| Symbol          | Parameter             | Condition                         | Min  | Тур | Max             | Units    |

|-----------------|-----------------------|-----------------------------------|------|-----|-----------------|----------|

| $V_{OH}$        | SD Output HIGH Level  | Sourcing 100μA                    | 2.4  |     | V <sub>CC</sub> | V        |

| $V_{OL}$        | SD Output LOW Level   | Sinking 2mA                       |      |     | 0.5             | V        |

| $V_{IH}$        | EN Input HIGH Voltage |                                   | 2.0  |     |                 | V        |

| $V_{\rm IL}$    | EN Input LOW Voltage  |                                   |      |     | 0.8             | V        |

| I <sub>IH</sub> | EN Input HIGH Current | $V_{IN} = 2.7V$ $V_{IN} = V_{CC}$ |      |     | 20<br>100       | μA<br>μA |

| I <sub>IL</sub> | EN Input LOW Current  | V <sub>IN</sub> = 0.5V            | -0.3 |     |                 | mA       |

### Notes:

- 1. Permanent device damage may occur if Absolute Maximum Ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to Absolute Maximum Ratings conditions for extended periods may affect device reliability.

- 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

- Thermal performance assumes the use of 4-layer PCB. Exposed pad must be soldered (or equivalent) to the device's most negative potential on the PCB.

- 4. Excludes current of CML output stage. See "Detailed Description."

- 5. Total device current with no output load.

- Output levels are based on a 50Ω to V<sub>CC</sub> load impedance. If the load impedance is different, the output level will be changed. Amplifier is in a limiting mode.

- 7. The  $V_{\mbox{\scriptsize IHCMR}}$  range is referenced to the most positive side of the differential input signal.

# **AC ELECTRICAL CHARACTERISTICS**

$V_{CC}$  = 3.0V to 3.6V or 4.5V to 5.5V;  $T_A$  = -40°C to +85°C;  $R_{LOAD}$  = 50 $\Omega$  to  $V_{CC}$ ; typical values at  $V_{CC}$  = 3.3V,  $T_A$  = 25°C

| Symbol                          | Parameter                             | Condition                                | Min        | Тур        | Max         | Units                                 |

|---------------------------------|---------------------------------------|------------------------------------------|------------|------------|-------------|---------------------------------------|

| PSRR                            | Power Supply Rejection Ratio          |                                          |            | 35         |             | dB                                    |

| t <sub>r</sub> , t <sub>f</sub> | Output Rise/Fall Time<br>(20% to 80%) | Note 8                                   |            | 60         | 120         | ps                                    |

| t <sub>JITTER</sub>             | Deterministic<br>Random               | Note 9                                   |            | 15<br>5    |             | ps <sub>PP</sub><br>ps <sub>RMS</sub> |

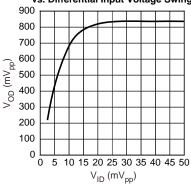

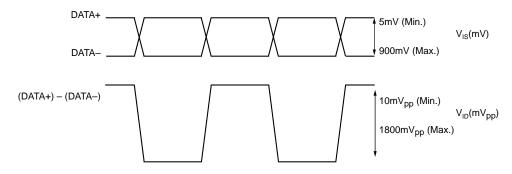

| $V_{ID}$                        | Differential Input Voltage Swing      |                                          | 10         |            | 1800        | mV <sub>PP</sub>                      |

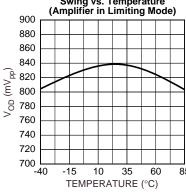

| V <sub>OD</sub>                 | Differential Output Voltage Swing     | 3.3V, <b>Note 8</b><br>5V, <b>Note 8</b> | 700<br>700 | 800<br>800 | 950<br>1020 | $mV_{PP}$ $mV_{PP}$                   |

| HYS                             | SD Hysteresis                         | Note 10                                  | 2          | 4.6        | 8           | dB                                    |

| t <sub>OFF</sub>                | SD Release Time                       |                                          |            | 0.1        | 0.5         | μs                                    |

| t <sub>ON</sub>                 | SD Assert Time                        |                                          |            | 0.2        | 0.5         | μs                                    |

| $V_{SR}$                        | SD Sensitivity Range                  | Note 11                                  | 10         |            | 35          | $mV_{PP}$                             |

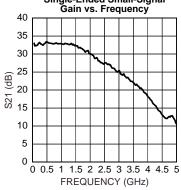

| B <sub>-3dB</sub>               | -3dB Bandwidth                        |                                          |            | 2.0        |             | GHz                                   |

| $A_{V(Diff)}$                   | Differential Voltage Gain             |                                          | 32         | 38         |             | dB                                    |

| S <sub>21</sub>                 | Single-Ended Small Signal-Gain        |                                          | 26         | 32         |             | dB                                    |

### Notes:

- 8. Amplifier in limiting mode. Input is a 200MHz square wave,  $t_r < 300ps$ .

- 9. Deterministic jitter measured using 2.488Gbps K28.5 pattern,  $V_{ID} = 10 \text{mV}_{pp}$ . Random jitter measured using 2.488Gbps K28.7 pattern,  $V_{ID} = 10 \text{mV}_{pp}$ .

- 10. Electrical signal.

- 11. This is the detectable range of input amplitudes that can de-assert SD. The input amplitude to assert SD is 2–8dB higher than the de-assert amplitude. See "Typical Operating Characteristics" for graphs showing how to choose a particular R<sub>SDLVL</sub> or V<sub>SDLVL</sub> for a particular SD de-assert, and its associated assert, amplitude. If increased SD sensitivity and hysteresis are required, an application note entitled "Notes on Sensitivity and Hysteresis in Micrel Post Amplifiers" is available at http://www.micrel.com/product-info/app\_hints+notes.shtml.

# SY88823V

$V_{CC}$  = 3.3V,  $T_A$  = 25°C,  $R_{LOAD}$  = 50 $\Omega$  to  $V_{CC}$ , unless otherwise stated.

TYPICAL OPERATING CHARACTERISTICS

10mV<sub>pp</sub> Input @3.2Gbps 2<sup>31</sup>-1 PRBS

TIME (50ps/div.)

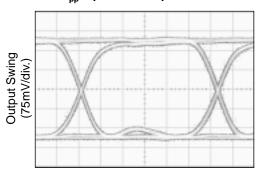

1.8V<sub>pp</sub> Input @3.2Gbps 2<sup>31</sup>–1 PRBS

TIME (50ps/div.)

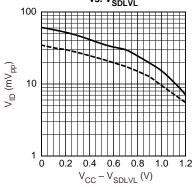

V<sub>ID</sub> to Assert/De-assert SD

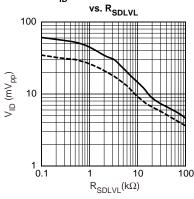

V<sub>ID</sub> to Assert/De-assert SD

Single-Ended Small-Signal Gain vs. Frequency

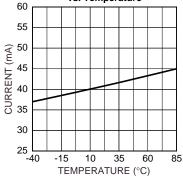

Power Supply Current vs. Temperature 60 55

**Differential Output Voltage** Swing vs. Temperature (Amplifier in Limiting Mode) 900 880

Differential Output Voltage Swing vs. Differential Input Voltage Swing

The SY88823V low-power, limiting post amplifier operate from a single  $+3.3V\pm10\%$  or  $+5V\pm10\%$  power supply, over an industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. Signa with data rates up to 3.2Gbps and as small as  $10mV_{PP}$  can be amplified. Figure 1 shows the allowed input voltage swing The SY88823V generates an SD output, providing feedback to EN for output stability. SDLVL sets the sensitivity of the input amplitude detection.

### Input Amplifier/Buffer

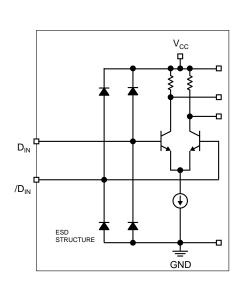

The SY88823V's input is designed for V<sub>REF</sub> as its nomin DC-bias point. If AC-coupling to the SY88823V, REF cabe used as the DC-bias point by externally connecting the inputs through appropriate termination resistors to REF. DC-coupling to the SY88823V, ensure the upstream device output swing meets the SY88823V's common-mode range Figure 2 shows a simplified schematic of the input structure.

The high sensitivity of the input amplifier detects ar amplifies signals as small as 10mVpp. The input amplificallows input signals as large as 1800mVpp. Input signals are linearly amplified with a typically 38dB differential voltage gain. Since it is a limiting amplifier, the SY88823V outputs typically 800mVpp voltage-limited waveforms for input signals that are greater than 10mVpp. Applications requiring the SY88823V to operate with high gain should have the upstream TIA placed as close as possible to the SY88823V's input pins to ensure the device's best performance.

### **Output Buffer**

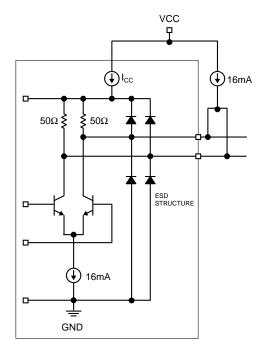

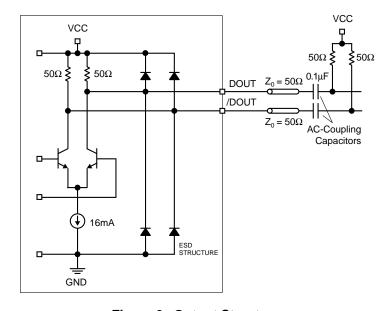

The SY88823V's CML output buffer is designed to drive  $50\Omega$  lines. The output buffer requires appropriate termination for proper operation. An external  $50\Omega$  resistor to VCC or equivalent for each output pin provides this. Figure 3 shows a simplified schematic of the output structure and includes an appropriate termination method. Of course, driving a downstream device with a CML input that is internally terminated with  $50\Omega$  to VCC eliminates the need for external termination. As noted in the previous section, the amplifier outputs, typically  $800\text{mV}_{PP}$ , waveforms across  $25\Omega$  total loads. The output buffer thus switches typically 16mA tail-current. Figure 4 shows the power supply current measurement which excludes the 16mA tail-current.

### Signal Detect

The SY88823V incorporates a chatter-free, signal detect (SD) open-collector TTL output with internal  $4.75 \mathrm{k}\Omega$  pull-up resistor as shown in Figure 5. SD is used to determine that the input amplitude large enough to be considered a valid input. SD asserts high if the input amplitude rises above the threshold set by SDLVL and de-asserts low otherwise. SD can be fed back to the enable (EN) input to maintain output stability under a loss of signal condition. EN de-asserts low the true output signal without removing the input signals. Typically, 4.6dB SD hysteresis is provided to prevent chattering.

### ignal Detect-Level Set

A programmable, signal-detect level set pin (SDLVL) sets e threshold of the input amplitude detection. Connecting n external resistor between VCC and SDLVL sets the bltage at SDLVL. This voltage ranges from  $V_{CC}$  to  $V_{REF}$  ne external resistor creates a voltage divider between VCC nd REF as shown in Figure 6. If desired, an appropriate sternal voltage may be applied rather than using a resistor. The relationship between  $V_{SDLVL}$  and  $R_{SDLVL}$  is given by:

$$V_{SDLVL} = V_{CC} - 1.3 \frac{R_{SDLVL}}{R_{SDLVL} + 2.8}$$

here voltages are in volts and resistances are in  $k\Omega$ .

The smaller the external resistor, which implies a smaller pltage difference from SDLVL to VCC, the lower the SD ensitivity. Hence, larger input amplitude is required to assert D. The "Typical Operating Characteristics" section contains raphs showing the relationship between the input amplitude etection sensitivity and  $V_{\text{SDLVL}}$  and  $R_{\text{SDLVL}}$ .

### **Hysteresis**

The SY88823V provides typically 4.6dB SD electrical hysteresis. By definition, a power ratio measured in dB is 10log(power ratio). Power is calculated as V<sup>2</sup><sub>IN</sub>/R for an electrical signal. Hence, the same ratio can be stated as 20log(voltage ratio). While in linear mode, the electrical voltage input changes linearly with the optical power and, hence, the ratios change linearly as well. Therefore, the optical hysteresis in dB is half the electrical hysteresis in dB given in the datasheet. The SY88823V provides typically 2.3dB SD optical hysteresis. As the SY88823V is an electrical device, this datasheet refers to hysteresis in electrical terms. With 4.6dB SD hysteresis, a voltage factor of 1.7 is required to assert SD.

### **Hysteresis and Sensitivity Improvement**

If increased SD sensitivity and hysteresis are required, an application note entitled "Notes on Sensitivity and Hysteresis in Micrel Post Amplifiers" is available at http://www.micrel.com/product-info/app\_hints+notes.shtml.

Figure 1.  $V_{\rm IS}$  and  $V_{\rm ID}$  Definition

Figure 2. Input Structure

**Figure 4. Power Supply Current Measurement**

Figure 3. Output Structure

Figure 5. SD Output Structure

Figure 6.  $SD_{LVL}$  Setting Circuit

# **TYPICAL APPLICATIONS CIRCUIT**

# RELATED PRODUCT AND SUPPORT DOCUMENTATION

| Part Number       | Function                                                             | Data Sheet Link                                          |

|-------------------|----------------------------------------------------------------------|----------------------------------------------------------|

| SY88773V          | 3.3V/5V 3.2Gbps CML Low-Power,<br>Limiting Post Amplifier w/ TTL LOS | http://www.micrel.com/_PDF/HBW/sy88773v.pdf              |

| SY88823V          | 3.3V/5V 3.2Gbps CML Low-Power,<br>Limiting Post Amplifier w/ TTL SD  | http://www.micrel.com/_PDF/HBW/sy88823v.pdf              |

| SY88843V          | 3.3V/5V 3.2Gbps CML Low-Power,<br>Limiting Post Amplifier w/ TTL SD  | http://www.micrel.com/_PDF/HBW/sy88843v.pdf              |

| SY88973V          | 3.3V/5V 3.2Gbps CML Low-Power,<br>Limiting Post Amplifier w/ TTL LOS | http://www.micrel.com/_PDF/HBW/sy88973v.pdf              |

| Application Notes | Notes on Sensitivity and Hysteresis in Micrel Post Amplifiers        | http://www.micrel.com/product-info/app_hints+notes.shtml |

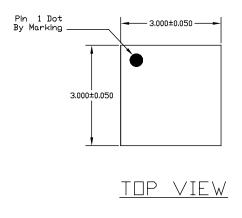

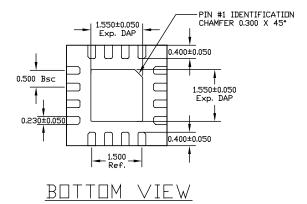

# 10 LEAD EPAD-MSOP (K10-2)

# 16-PIN *Micro*LEADFRAME™ (MLF-16)

0.850±0.050

0.203±0.025

SIDE VIEW

0.000-0.050

NOTE

- ALL DIMENSIONS ARE IN MILLIMETERS.

MAX. PACKAGE WARPAGE IS 0.05 mm.

MAXIMUM ALLOWABE BURRS IS 0.076 mm IN ALL DIRECTIONS.

PIN #1 ID ON TOP WILL BE LASER/INK MARKED.

PCB Thermal Consideration for 16-Pin MLF™ Package (Always solder, or equivalent, the exposed pad to the PCB)

### Package Notes:

- 1. Package meets Level 2 qualification.

- 2. All parts are dry-packaged before shipment.

- 3. Exposed pads must be soldered to a ground for proper thermal management.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2005 Micrel, Incorporated.