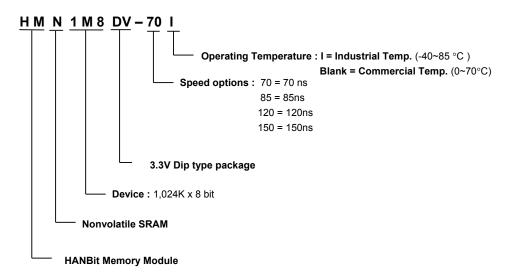

Non-Volatile SRAM MODULE 8Mbit (1024k x 8bit) 36Pin – DIP, 3.3V Part No. HMN1M8DV

## **GENERAL DESCRIPTION**

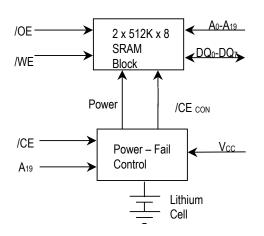

The HMN1M8DV Nonvolatile SRAM is a 8,388,608-bit static RAM organized as 1,048,576 bytes by 8 bits. The HMN1M8DV has a self-contained lithium energy source provide reliable non-volatility coupled with the unlimited write cycles of standard SRAM and integral control circuitry which constantly monitors the single 3.3V supply for an out-of-tolerance condition. When such a condition occurs, the lithium energy source is automatically switched on to sustain the memory until after  $V_{CC}$  returns valid and write protection is unconditionally enabled to prevent garbled data. In addition the SRAM is unconditionally write-protected to prevent an inadvertent write operation. At this time the integral energy source is switched on to sustain the memory until after  $V_{CC}$  returns valid.

The HMN1M8DV uses extremely low standby current CMOS SRAM's, coupled with small lithium coin cells to provide nonvolatility without long write-cycle times and the write-cycle limitations associated with EEPROM.

# FEATURES

- Access time : 70, 85, 120, 150 ns

- High-density design : 8Mbit Design

- Battery internally isolated until power is applied

- Industry-standard 36-pin 1,024K x 8 pinout

- Unlimited write cycles

**OPTIONS**

70 ns

85 ns

120 ns

150 ns

Timing

- $\bullet$  Data retention in the absence of  $\,V_{\text{CC}}$

- 10-years minimum data retention in absence of power

- Automatic write-protection during power-up/power-down cycles

MARKING

- 70

- 85

-100

-150

Data is automatically protected during power loss

#### 36 1 ⊐ V<sub>cc</sub> NC [ 2 35 NC A19 3 34 A18 C ⊐ NC 4 33 □ A<sub>15</sub> A16 5 32 A14 A17 A<sub>12</sub> 6 31 /WE 30 7 A13 A7 29 8 A<sub>8</sub> A<sub>6</sub> 28 9 A۹ A<sub>5</sub> 10 27 A11 A<sub>4</sub> 11 26 1 /OE Aз 12 25 A<sub>2</sub> 1 A10 13 24 /CE $A_1$ A₀ ⊏ 14 23 DQ7 15 22 DQ<sub>6</sub> 16 21 DQ<sub>5</sub> 17 20 $\Box DQ_4$ Vss C 18 19 ⊐ DQ<sub>3</sub>

36-pin Encapsulated Package

# PIN ASSIGNMENT

#### FUNCTIONAL DESCRIPTION

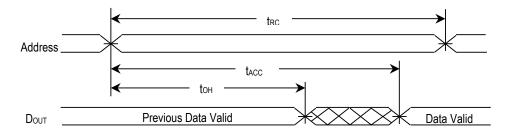

The HMN1M8DV executes a read cycle whenever /WE is inactive(high) and /CE is active(low). The address specified by the address inputs( $A_0$ - $A_{19}$ ) defines which of the 1,048,576 bytes of data is accessed. Valid data will be available to the eight data output drivers within  $t_{ACC}$  (access time) after the last address input signal is stable.

When power is valid, the HMN1M8DV operates as a standard CMOS SRAM. During power-down and power-up cycles, the HMN1M8DV acts as a nonvolatile memory, automatically protecting and preserving the memory contents.

The HMN1M8DV is in the write mode whenever the /WE and /CE signals are in the active (low) state after address inputs are stable. The later occurring falling edge of /CE or /WE will determine the start of the write cycle. The write cycle is terminated by the earlier rising edge of /CE or /WE. All address inputs must be kept valid throughout the write cycle. /WE must return to the high state for a minimum recovery time ( $t_{WR}$ ) before another cycle can be initiated. The /OE control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if the output bus been enabled (/CE and /OE active) then /WE will disable the outputs in  $t_{ODW}$  from its falling edge.

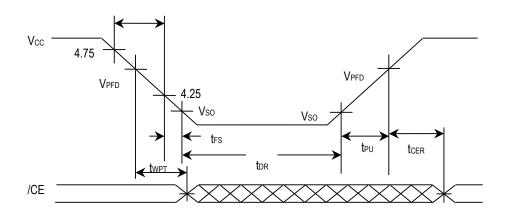

The HMN1M8DV provides full functional capability for Vcc greater than 3.0 V and write protects by 2.8 V nominal. Powerdown/power-up control circuitry constantly monitors the Vcc supply for a power-fail-detect threshold  $V_{PFD}$ . When  $V_{CC}$  falls below the  $V_{PFD}$  threshold, the SRAM automatically write-protects the data. All inputs to the RAM become "don't care" and all outputs are high impedance. As Vcc falls below approximately 2.5V, the power switching circuit connects the lithium energy soure to RAM to retain data. During power-up, when Vcc rises above approximately 2.5 volts, the power switching circuit connects external Vcc to the RAM and disconnects the lithium energy source. Normal RAM operation can resume after Vcc exceeds 3.0 volts.

## **BLOCK DIAGRAM**

#### **PIN DESCRIPTION**

### TRUTH TABLE

| MODE           | /OE | /CE | /WE | I/O OPERATION    | POWER   |

|----------------|-----|-----|-----|------------------|---------|

| Not selected   | х   | Н   | х   | High Z           | Standby |

| Output disable | Н   | L   | Н   | High Z           | Active  |

| Read           | L   | L   | Н   | D <sub>OUT</sub> | Active  |

| Write          | Х   | L   | L   | D <sub>IN</sub>  | Active  |

## **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER                                                                           | SYMBOL              | RATING           | CONDITIONS             |

|-------------------------------------------------------------------------------------|---------------------|------------------|------------------------|

| DC voltage applied on $V_{CC}$ relative to $V_{SS}$                                 | V <sub>CC</sub>     | -0.5V to Vcc+0.5 |                        |

| DC Voltage applied on any pin excluding $V_{\text{CC}}$ relative to $V_{\text{SS}}$ | V <sub>T</sub>      | -0.3V to 4.6V    | $V_T \leq V_{CC}$ +0.3 |

| Operating temperature                                                               | T <sub>OPR</sub>    | 0 to 70°C        |                        |

| Storage temperature                                                                 | T <sub>STG</sub>    | -65°C to 150°C   |                        |

| Soldering temperature                                                               | T <sub>SOLDER</sub> | 260°C            | For 10 second          |

NOTE: Permanent device damage may occur if Absolute Maximum Ratings are exceeded.

Functional operation should be restricted to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to higher than recommended voltage for extended periods of time could affect device reliability.

# **RECOMMENDED DC OPERATING CONDITIONS** (T<sub>A</sub>= T<sub>OPR</sub>)

| PARAMETER          | SYMBOL          | MIN  | TYPICAL | MAX                  |

|--------------------|-----------------|------|---------|----------------------|

| Supply Voltage     | V <sub>cc</sub> | 3.0V | 3.3V    | 3.6V                 |

| Ground             | V <sub>SS</sub> | 0    | 0       | 0                    |

| Input high voltage | V <sub>IH</sub> | 2.2  | -       | V <sub>CC+</sub> 0.3 |

| Input low voltage  | V <sub>IL</sub> | -0.3 | -       | 0.6V                 |

NOTE: Typical values indicate operation at  $T_A$  = 25  $^\circ\!\!\!\mathrm{C}$

# **CAPACITANCE** (T<sub>A</sub>=25 °C, f=1MHz, V<sub>CC</sub>=3.3V)

| DESCRIPTION              | CONDITIONS          | SYMBOL           | MAX | MIN | UNIT |

|--------------------------|---------------------|------------------|-----|-----|------|

| Input Capacitance        | Input voltage = 0V  | C <sub>IN</sub>  | 8   | -   | pF   |

| Input/Output Capacitance | Output voltage = 0V | C <sub>I/O</sub> | 10  | -   | pF   |

1. Only sampled, not 100% tested

| <b>DC ELECTRICAL CHARACTERISTICS</b> ( $I_A = I_{OPR}, V_{CCmin} \leq V_{CC} \geq V_{CCmax}$ ) |                                                                                                                                                         |                  |     |      |      |      |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|------|------|------|

| PARAMETER                                                                                      | CONDITIONS                                                                                                                                              | SYMBOL           | MIN | TYP. | MAX  | UNIT |

| Input Leakage Current                                                                          | $V_{IN}=V_{SS}$ to $V_{CC}$                                                                                                                             | ILI              | -   | -    | ±3.0 | μA   |

| Output Leakage Current                                                                         | /CE=V <sub>IH</sub> or /OE=V <sub>IH</sub><br>or /WE=V <sub>IL</sub>                                                                                    | I <sub>LO</sub>  | -   | -    | ±3.0 | μA   |

| Output high voltage                                                                            | I <sub>OH</sub> =-1.0mA                                                                                                                                 | V <sub>OH</sub>  | 2.4 | -    | -    | V    |

| Output low voltage                                                                             | I <sub>OL</sub> = 2.0mA                                                                                                                                 | V <sub>OL</sub>  | -   | -    | 0.4  | V    |

| Power-fail Deselect Voltage                                                                    | Threshold Select<br>Voltage<br>(THS = V <sub>SS</sub> )                                                                                                 | V <sub>PFD</sub> | 2.8 | 2.9  | 3.0  | V    |

| Standby supply current                                                                         | /CE=2.2v                                                                                                                                                | I <sub>SB</sub>  | -   | -    | 0.6  | mA   |

| Standby supply current                                                                         | $\label{eq:CE} \begin{array}{l} /CE \geq V_{CC} \text{-} 0.2V, \\ 0V \leq V_{IN} \leq 0.2V, \\ \text{or } V_{IN} \geq V_{CC} \text{-} 0.2V \end{array}$ | I <sub>SB1</sub> | -   | -    | 30   | μA   |

| Operating Power supply<br>current                                                              | /CE=V <sub>IL</sub> , I <sub>I/O</sub> =0mA,<br>V <sub>IN</sub> = V <sub>IL</sub> or V <sub>IH</sub> , Read                                             | I <sub>CC</sub>  | -   |      | 12   | mA   |

| Supply switch-over voltage                                                                     |                                                                                                                                                         | V <sub>SO</sub>  | -   | 2.5  | -    | V    |

## **DC ELECTRICAL CHARACTERISTICS** ( $T_A = T_{OPR}, V_{CCmin} \leq V_{CC} \leq V_{CCmax}$ )

# CHARACTERISTICS (Test Conditions)

| CHARACTERISTICS (Test C                                                     | 5010110115)                   | ې<br>+5               | 5V +5V                                      |

|-----------------------------------------------------------------------------|-------------------------------|-----------------------|---------------------------------------------|

| PARAMETER                                                                   | VALUE                         | {                     |                                             |

| Input pulse levels                                                          | 0.4 to 2.2V                   | D <sub>OUT</sub> 1.9K | D <sub>OUT</sub><br>→ 1.9KΩ                 |

| Input rise and fall times                                                   | 5 ns                          |                       | $00 \text{ pF}$ $\leq$ $\pm$ $5 \text{ pF}$ |

| Input and output timing reference                                           | 5V                            |                       |                                             |

| levels                                                                      | ( unless otherwise specified) | 는 두<br>Figure 1.      | 는<br>Figure 2.                              |

| Output load (CL <sup>1)</sup> =30pF+1TTL)<br>(CL <sup>1)</sup> =100pF+1TTL) | See Figures                   | Output Load A         | Output Load B                               |

Note : Including scope and jig capacitance

|                                  |                  |               | -70 |     | -85 |     | -120 |     | -150 |     |      |

|----------------------------------|------------------|---------------|-----|-----|-----|-----|------|-----|------|-----|------|

| PARAMETER                        | SYMBOL           | CONDITIONS    | MIN | МАХ | MIN | МАХ | MIN  | MAX | MIN  | МАХ | UNIT |

| Read Cycle Time                  | t <sub>RC</sub>  |               | 70  | -   | 85  | -   | 120  | -   | 150  | -   | ns   |

| Address Access Time              | t <sub>ACC</sub> | Output load A | -   | 70  | -   | 85  | -    | 120 | -    | 150 | ns   |

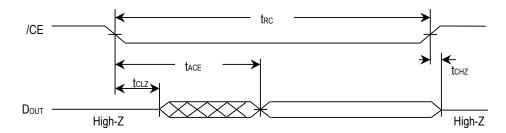

| Chip enable access time          | t <sub>ACE</sub> | Output load A | -   | 70  | -   | 85  | -    | 120 | -    | 150 | ns   |

| Output enable to Output valid    | t <sub>OE</sub>  | Output load A | -   | 35  | -   | 45  | -    | 60  | -    | 70  | ns   |

| Chip enable to output in low Z   | t <sub>CLZ</sub> | Output load B | 5   | -   | 5   | -   | 5    | -   | 10   | -   | ns   |

| Output enable to output in low Z | t <sub>oLZ</sub> | Output load B | 5   | -   | 0   | -   | 0    | -   | 5    | -   | ns   |

| Chip disable to output in high Z | t <sub>снz</sub> | Output load B | 0   | 25  | 0   | 35  | 0    | 45  | 0    | 60  | ns   |

| Output disable to output high Z  | t <sub>онz</sub> | Output load B | 0   | 25  | 0   | 25  | 0    | 35  | 0    | 50  | ns   |

| Output hold from address change  | t <sub>он</sub>  | Output load A | 10  | -   | 10  | -   | 10   | -   | 10   | -   | ns   |

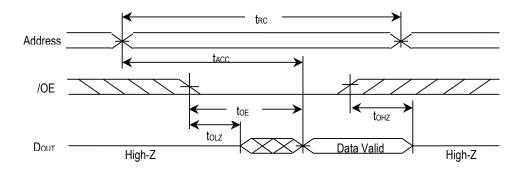

# **READ CYCLE** (T<sub>A</sub>= T<sub>OPR</sub>, V<sub>CCmin</sub> $\leq$ V<sub>CC</sub> $\leq$ V<sub>CCmax</sub>)

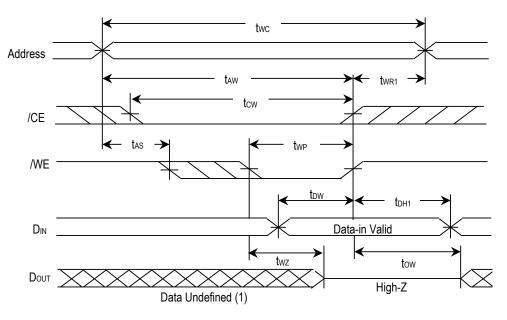

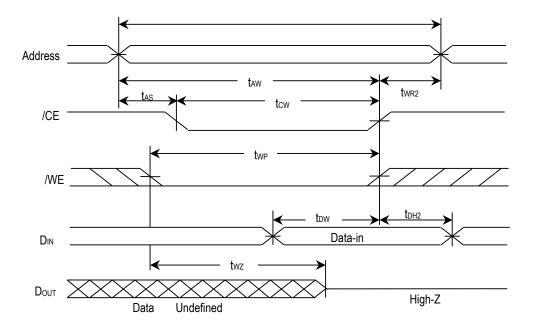

**WRITE CYCLE** (T<sub>A</sub>= T<sub>OPR</sub>,  $V_{ccmin} \leq V_{cc} \leq V_{ccmax}$ )

|                                     |                  |            | -7  | 70  | -{  | 35  | -1  | 20  | -1  | 50  | UNI |

|-------------------------------------|------------------|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| PARAMETER                           | SYMBOL           | CONDITIONS | MIN | MAX | MIN | MAX | MIN | MAX | Min | Мах | т   |

| Write Cycle Time                    | t <sub>wc</sub>  |            | 70  | -   | 85  | -   | 120 | -   | 150 | -   | ns  |

| Chip enable to end of write         | t <sub>cw</sub>  | Note 1     | 65  | -   | 75  | -   | 100 | -   | 100 | -   | ns  |

| Address setup time                  | t <sub>AS</sub>  | Note 2     | 0   | -   | 0   | -   | 0   | -   | 0   | -   | ns  |

| Address valid to end of write       | t <sub>AW</sub>  | Note 1     | 65  | -   | 75  | -   | 100 | -   | 90  | -   | ns  |

| Write pulse width                   | t <sub>WP</sub>  | Note 1     | 55  | -   | 65  | -   | 85  | -   | 90  | -   | ns  |

| Write recovery time (write cycle 1) | t <sub>WR1</sub> | Note 3     | 5   | -   | 5   | -   | 5   | -   | 5   | -   | ns  |

| Write recovery time (write cycle 2) | t <sub>WR2</sub> | Note 3     | 15  | -   | 15  | -   | 15  | -   | 15  | -   | ns  |

| Data valid to end of write          | t <sub>DW</sub>  |            | 30  | -   | 35  | -   | 45  | -   | 50  | -   | ns  |

| Data hold time (write cycle 1)      | t <sub>DH1</sub> | Note 4     | 0   | -   | 0   | -   | 0   | -   | 0   | -   | ns  |

| Data hold time (write cycle 2)      | t <sub>DH2</sub> | Note 4     | 10  | -   | 10  | -   | 10  | -   | 0   | -   | ns  |

| Write enabled to output in high Z   | t <sub>wz</sub>  | Note 5     | 0   | 25  | 0   | 30  | 0   | 40  | 0   | 50  | ns  |

| Output active from end of write     | t <sub>ow</sub>  | Note 5     | 5   | -   | 0   | -   | 0   | -   | 5   | -   | ns  |

**NOTE:** 1. A write ends at the earlier transition of /CE going high and /WE going high.

2. A write occurs during the overlap of allow /CE and a low /WE. A write begins at the later transition of /CE going low and /WE going low.

3. Either  $t_{\text{WR1}}$  or  $t_{\text{WR2}}$  must be met.

4. Either  $t_{DH1}$  or  $t_{DH2}$  must be met.

5. If /CE goes low simultaneously with /WE going low or after /WE going low, the outputs remain in high-impedance state.

## **POWER-DOWN/POWER-UP CYCLE**

| PARAMETER                                                                                               | SYMBOL           | CONDITIONS                                                                             | MIN | TYP. | MAX | UNIT |

|---------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------|-----|------|-----|------|

| V <sub>PFD</sub> (max) to V <sub>PFD</sub> (min) V <sub>CC</sub> Fail Time                              | t <sub>F</sub>   |                                                                                        | 300 | -    | -   | μS   |

| V <sub>PFD</sub> (max) to V <sub>SS</sub> V <sub>CC</sub> Fail Time                                     | t <sub>FB</sub>  |                                                                                        | 150 | -    | -   | μS   |

| $V_{\text{PFD}}(\text{max})~\text{to}~V_{\text{PFD}}(\text{min})~V_{\text{CC}}~\text{Rise}~\text{Time}$ | t <sub>R</sub>   |                                                                                        | 10  | -    | -   | μs   |

| Write Protect Time                                                                                      | t <sub>wpт</sub> | Delay after Vcc slews down<br>past V <sub>PFD</sub> before SRAM is<br>Write-protected. | 40  |      | 250 | μs   |

| Chip Enable Recovery                                                                                    | t <sub>CER</sub> |                                                                                        | 40  | -    | 120 | ms   |

| $V_{\text{SS}}$ to $V_{\text{PFD}}$ (min) $V_{\text{CC}}$ Rise Time                                     | t <sub>RB</sub>  |                                                                                        | 1   | -    | -   | μS   |

## TIMING WAVEFORM

# - READ CYCLE NO.1 (Address Access)\*<sup>1,2</sup>

# - READ CYCLE NO.2 (/CE Access)<sup>\*1,3,4</sup>

# - READ CYCLE NO.3 (/OE Access)<sup>\*1,5</sup>

**NOTES:** 1. /WE is held high for a read cycle.

- 2. Device is continuously selected: /CE = /OE =V<sub>IL</sub>.

- 3. Address is valid prior to or coincident with /CE transition low.

- 4. /OE = V<sub>IL</sub>.

- 5. Device is continuously selected: /CE =  $V_{IL}$

# - WRITE CYCLE NO.1 (/WE-Controlled)\*1,2,3

# - WRITE CYCLE NO.2 (/CE-Controlled)\*1,2,3,4,5

- **NOTE:** 1. /CE or /WE must be high during address transition.

- 2. Because I/O may be active (/OE low) during this period, data input signals of opposite polarity to the outputs must not be applied.

- 3. If  $\overline{\text{OE}}$  is high, the I/O pins remain in a state of high impedance.

- 4. Either  $t_{\rm WR1}$  or  $t_{\rm WR2}$  must be met.

- 5. Either  $t_{\text{DH1}}$  or  $t_{\text{DH2}}$  must be met.

## **POWER-DOWN/POWER-UP TIMING**

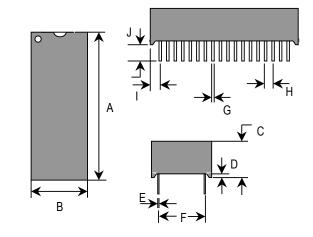

#### PACKAGE DIMENSION

| Dimension | Min   | Max   |

|-----------|-------|-------|

| А         | 2.070 | 2.100 |

| В         | 0.710 | 0.740 |

| С         | 0.365 | 0.375 |

| D         | 0.015 | -     |

| Е         | 0.008 | 0.013 |

| F         | 0.590 | 0.630 |

| G         | 0.017 | 0.023 |

| Н         | 0.090 | 0.110 |

| I         | 0.080 | 0.110 |

| J         | 0.120 | 0.150 |

All dimensions are in inches.

#### **ODERING INFORMATION**