# P-Channel JFET Switch

## J174 - J177 / SST174 - SST177

#### **FEATURES**

- Low Insertion Loss

- No Offset or Error Generated By Closed Switch

- Purely Resistive

- High Isolation Resistance From Driver

- Short Sample and Hold Aperture Time

- Fast Switching

#### **APPLICATIONS**

- Analog Switches

- Choppers

- Commutators

#### **ABSOLUTE MAXIMUM RATINGS**

$(T_A = 25^{\circ}C \text{ unless otherwise specified})$

| Gate-Drain or Gate-Source Voltage   | 30V             |

|-------------------------------------|-----------------|

| Gate Current                        |                 |

| Storage Temperature Range           | -55°C to +150°C |

| Operating Temperature Range         | -55°C to +135°C |

| Lead Temperature (Soldering, 10sec) |                 |

| Power Dissipation                   |                 |

| Derate above 25°C                   | 3.3mW/°C        |

**NOTE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

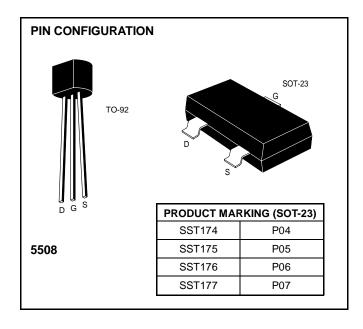

#### **ORDERING INFORMATION**

| Part                       | Package                         | Temperature Range                  |

|----------------------------|---------------------------------|------------------------------------|

| J174-J177<br>SST174-SST177 | Plastic TO-92<br>Plastic SOT-23 | -55°C to +135°C<br>-55°C to +135°C |

| For Sorted Chips in        | Carriers see 2N511              | 4 series.                          |

### **ELECTRICAL CHARACTERISTICS** (T<sub>A</sub> = 25°C unless otherwise specified)

| SYMBOL PARAMETER                             | J174                                                |     |     | J175 |     |     | J176 |     |     | J177 |      | UNITS | TEST CONDITIONS |                 |                                                                                                                                   |

|----------------------------------------------|-----------------------------------------------------|-----|-----|------|-----|-----|------|-----|-----|------|------|-------|-----------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                                              | MIN                                                 | TYP | MAX | MIN  | TYP | MAX | MIN  | TYP | MAX | MIN  | TYP  | MAX   | UNITS           | TEST CONDITIONS |                                                                                                                                   |

| I <sub>GSS</sub>                             | Gate Reverse<br>Current<br>(Note 1)                 |     |     | 1    |     |     | 1    |     |     | 1    |      |       | 1               | nA              | V <sub>DS</sub> = 0, V <sub>GS</sub> = 20V                                                                                        |

| V <sub>GS(off)</sub>                         | Gate Source<br>Cutoff Voltage                       | 5   |     | 10   | 3   |     | 6    | 1   |     | 4    | 0.8  |       | 2.25            |                 | V <sub>DS</sub> = -15V, I <sub>D</sub> = -10nA                                                                                    |

| BV <sub>GSS</sub>                            | Gate Source<br>Breakdown<br>Voltage                 | 30  |     |      | 30  |     |      | 30  |     |      | 30   |       |                 | V               | $V_{DS}=0,I_G=1\mu A$                                                                                                             |

| I <sub>DSS</sub>                             | Drain<br>Saturation<br>Current<br>(Note 2)          | -20 |     | -135 | -7  |     | -70  | -2  |     | -35  | -1.5 |       | -20             | mA              | V <sub>DS</sub> = -15V, V <sub>GS</sub> = 0                                                                                       |

| I <sub>D(off)</sub>                          | Drain Cutoff<br>Current<br>(Note 1)                 |     |     | -1   |     |     | -1   |     |     | -1   |      |       | -1              | nA              | V <sub>DS</sub> = -15V, V <sub>GS</sub> = 10V                                                                                     |

| r <sub>DS(on)</sub>                          | Drain-Source<br>ON Resistance                       |     |     | 85   |     |     | 125  |     |     | 250  |      |       | 300             | Ω               | V <sub>GS</sub> = 0, V <sub>DS</sub> = -0.1V                                                                                      |

| C <sub>dg(off)</sub>                         | Drain-Gate<br>OFF<br>Capacitance                    |     | 5.5 |      |     | 5.5 |      |     | 5.5 |      |      | 5.5   |                 |                 | V <sub>DS</sub> = 0,                                                                                                              |

| C <sub>sg(off)</sub>                         | Source-Gate<br>OFF<br>Capacitance                   |     | 5.5 |      |     | 5.5 |      |     | 5.5 |      |      | 5.5   |                 | pF              | $V_{GS} = 10V$ $f = 1MHz (Note 3)$                                                                                                |

| C <sub>dg(on)</sub><br>+ C <sub>sg(on)</sub> | Drain-Gate<br>Plus Source<br>Gate ON<br>Capacitance |     | 32  |      |     | 32  |      |     | 32  |      |      | 32    |                 |                 | $V_{DS} = V_{GS} = 0$                                                                                                             |

| t <sub>d(on)</sub>                           | Turn On Delay<br>Time                               |     | 2   |      |     | 5   |      |     | 15  |      |      | 20    |                 |                 | Switching Time Test Conditions (Note 3)  J174 J175 J176 J177  VDD -10V -6V -6V -6V VGS(off) 12V 8V 3V 3V  RL 560Ω 12kΩ 5.6kΩ 10kΩ |

| t <sub>r</sub>                               | Rise Time                                           |     | 5   |      |     | 10  |      |     | 20  |      |      | 25    |                 | ns              |                                                                                                                                   |

| t <sub>d(off)</sub>                          | Turn Off Delay<br>Time                              |     | 5   |      |     | 10  |      |     | 15  |      |      | 20    |                 | 113             |                                                                                                                                   |

| t <sub>f</sub>                               | Fall Time                                           |     | 10  |      |     | 20  |      |     | 20  |      |      | 25    |                 |                 | V <sub>GS(on)</sub> 0V 0V 0V                                                                                                      |

NOTES: 1. Approximately doubles for every 10°C increase in T<sub>A</sub>.

2. Pulse test duration -300μs; duty cycle ≤3%.

3. For design reference only, not 100% tested.