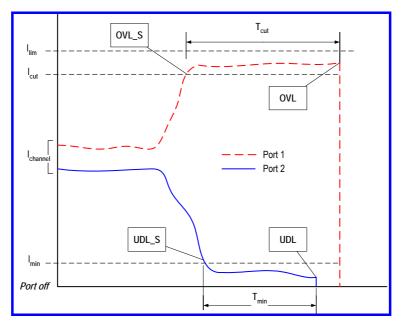

# PD64012

# 12-channel PoE Manager

### **Preliminary Datasheet**

### Description

PowerDsine's<sup>™</sup> PD64012 Power over Ethernet (PoE) Manager chip integrates power, analog and logic functions into a single 64-pin, plastic pack. It is used in Ethernet switches and Midspans to allow next generation network devices to share power and data over the same cable.

The device is a twelve-port, mix-signal, high-voltage Power over Ethernet driver. The PoE Manager allows the detection of IEEE 802.3af-2003 compliant terminals, referred to as powered devices or PDs, ensuring safe power feeding and removal over Ethernet ports. With full digital control via a serial communication interface and a minimum of external components, the device integrates in multi-port and highly populated Ethernet switches.

The PD64012 implements all real time functions according to IEEE 802.3af-2003, including: detection, classification, and port status monitoring; as well as system level activities such as: power management and MIB support, for system management. The PoE Manager is designed to detect and disable disconnected ports, using both DC and AC disconnect methods, as defined in IEEE 802.3af-2003.

The PD64012 has two possible working configurations: an Auto mode (stand-alone topology) for basic PoE functions and an Enhanced mode for extended functions.

## Pin Configuration \_\_\_\_

### Features

- IEEE 802.3af-2003 compliant

- Drives 12 independent power ports

- Can be cascaded for up to 48 ports, using a master/slave architecture

- Supports IETF Power Ethernet MIB (RFC 3621)

- Thermal protection per port

- Thermal monitoring capabilities

- Multi-point resistor detection

- Supports DC modulation method under-current detection according to IEEE 802.3af-2003

- AC & DC disconnect functions

- PD classification function

- Operates from single input (44 to 57 V)

- I<sup>2</sup>C bus interface

- Supports foldback current limiting

- Digitally programmable overcurrent protection per port

- Digitally programmable timers

- Power management algorithm for up to 48 ports

- Internal power-on reset

- Power soft-start algorithm

- Fast power shutdown, in case of power supply failure

- Automatic on/off sequencer for up to 48 ports

- Disable/enable power feeding

- Continuous port current monitoring

- Supports back-off feature for Midspan implementation

- Additional features for Enhanced mode:

- UART interface

- Pre-standard PD detection

- Supports non-standard terminals

- Advanced power management

- Programmable port matrix

### **Ordering Information**

| PART    | TEMP. RANGE   | PIN PACKAGE |

|---------|---------------|-------------|

| PD64012 | -20 to +85 °C | LQFP-64     |

**Date code**: see the bottom line (*04202AL1W07*) in the Pin Configuration drawing. "*0420*" is the date code. "*04*" the year (2004), while "*20*" is the week.

#### PowerDsine

#### The Power over Ethernet Pioneers

This document contains information that is proprietary to PowerDsine. As such, it is confidential and its disclosure is strictly prohibited by applicable law. If you and/or your company and PowerDsine have executed a Non-Disclosure Agreement, then this document is being provided in connection with the Agreement, and the information contained herein is covered by the Agreement and under its terms may not be disclosed or used and must be protected by you and/or your company.

## Maximum Ratings \_

| 0.3 to 80 V <sup>(1)</sup>  | MISO, MOSI, SCK, SCL, SDA,                                                                                   |

|-----------------------------|--------------------------------------------------------------------------------------------------------------|

| 0.3 to 0.3 $V^{(2)}$        | CLK, RESETN, CS0_N, CS1_N0.3 to (V <sub>PERI</sub> + 0.3) V                                                  |

| -0.3 to 80 V <sup>(1)</sup> | ESD (Human Body Model)2 to 2 kV <sup>(3)</sup>                                                               |

|                             | Max junction temperature (T <sub>junc</sub> )+150 °C                                                         |

|                             | Junction-ambient thermal resistance (θ <sub>JA</sub> ) 25 °C/W                                               |

|                             | Junction-case thermal resistance (0,c)16 °C/W                                                                |

|                             | Lead temperature (soldering, 10 s)                                                                           |

| 0.3 to 3 V                  | Storage temperature                                                                                          |

| 4 V                         |                                                                                                              |

| 0.3 to 6 V                  |                                                                                                              |

| 0.3 to 3 V                  |                                                                                                              |

|                             | 0.3 to 0.3 V <sup>(2)</sup><br>-0.3 to 80 V <sup>(1)</sup><br>0.3 to 15 V<br>0.3 to 3 V<br>4 V<br>0.3 to 6 V |

Notes: "x" defines port numbers, 0 thru 11, inclusive.

(1) 80 V is the transient voltage that can be applied for at most one minute.

(2) Maximum value between grounds.

(3) ESD testing is performed in accordance with the Human Body Model ( $C_{Zap} = 100 \text{ pF}$ ,  $R_{Zap} = 1500 \Omega$ ).

Stresses beyond those listed above, may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods, may affect device reliability.

## Operating Conditions \_\_\_\_\_

| PARAMETER                   | MIN.     | NOM.     | MAX.     | UNIT |

|-----------------------------|----------|----------|----------|------|

| Operating temperature       | -20      |          | +85      | °C   |

| Operational limitations (1) | 15 to 44 | 44 to 55 | 55 to 57 | V    |

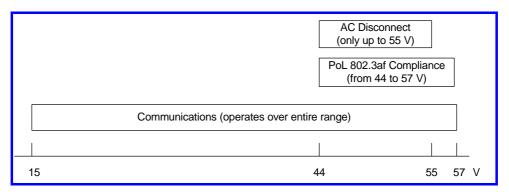

(1) Operating functions depend on the input voltage, as shown in the distribution of Figure 1.

Figure 1 - Operational Ranges

### Electrical Characteristics \_\_\_\_\_

#### DC Characteristics for Digital Inputs and Outputs

| PARAMETER                | SYMBOL        | MIN.           | MAX.           | UNIT        | REMARKS |

|--------------------------|---------------|----------------|----------------|-------------|---------|

| Pin Name                 | DISABLE_PO    | ORTS           |                |             |         |

| Туре                     | Schmitt Trigg | er CMOS input, | TTL level with | internal pu | ıllup   |

| High level input voltage | VIH           | 2.0            |                | V           |         |

| Low level input voltage  | VIL           |                | 0.8            | V           |         |

| Input voltage hysteresis |               | 0.3            |                | V           |         |

| Input high current       | Iн            | +10            | +150           | μA          |         |

| Input low current        | IIL           | NA             | NA             | μA          |         |

#### DC Characteristics for Digital Inputs and Outputs (continued)

| PARAMETER                 | SYMBOL                                                          | MIN.             | MAX.           | UNIT        | REMARKS                 |  |  |

|---------------------------|-----------------------------------------------------------------|------------------|----------------|-------------|-------------------------|--|--|

| Pin Name                  | SCL                                                             |                  |                |             |                         |  |  |

| Туре                      | Schmitt Trigg                                                   | er CMOS input,   | TTL level with | internal pu | ıllup                   |  |  |

| High level input voltage  | VIH                                                             | 2.0              |                | V           |                         |  |  |

| Low level input voltage   | VIL                                                             |                  | 0.8            | V           |                         |  |  |

| Input voltage hysteresis  |                                                                 | 0.3              |                | V           |                         |  |  |

| Input high current        | I <sub>IH</sub>                                                 | NA               | NA             | μA          |                         |  |  |

| Input low current         | IIL                                                             | -150             | -10            | μA          |                         |  |  |

| Pin Name                  | MOSI, MISO,                                                     | CS0_N, CS1_N     | N, SCK         |             |                         |  |  |

| Туре                      | CMOS I/O, TTL level with no internal pull up/pull down resistor |                  |                |             | n resistor              |  |  |

| High level input voltage  | Vih                                                             | 2.0              |                | V           |                         |  |  |

| Low level input voltage   | VIL                                                             |                  | 0.8            | V           |                         |  |  |

| Input voltage hysteresis  |                                                                 | 0.3              |                | V           |                         |  |  |

| Input high current        | IIH                                                             | -1               | +1             | μA          |                         |  |  |

| Input low current         | IIL                                                             | -1               | +1             | μA          |                         |  |  |

| High level output voltage |                                                                 | $V_{PERI}$ -0.4V |                | V           | I <sub>out</sub> = 3 mA |  |  |

| Low level output voltage  |                                                                 |                  | 0.4            | V           | I <sub>out</sub> = 3 mA |  |  |

| Tri state output current  |                                                                 | -1               | +1             | μA          |                         |  |  |

| Pin Name                  | RESET_N, SDA                                                    |                  |                |             |                         |  |  |

| Туре                      | CMOS open drain output with Schmitt Trigger input, TTL level    |                  |                |             |                         |  |  |

| High level input voltage  |                                                                 |                  | 0.4            | V           | I <sub>out</sub> = 3mA  |  |  |

| Low level input voltage   | VIL                                                             |                  | 0.8            | V           |                         |  |  |

| Input voltage hysteresis  |                                                                 | 0.3              |                | V           |                         |  |  |

| OFF state output current  |                                                                 | -1               | +1             | μA          |                         |  |  |

### **Electrical Characteristics for Analog I/O Pads**

| PARAMETER                                          | MIN.                     | MAX.             | UNIT      | REMARKS                                                                           |

|----------------------------------------------------|--------------------------|------------------|-----------|-----------------------------------------------------------------------------------|

| Pin Name                                           | VPORT_POS                | x, VPORT_NE      | Gx, REF_P | PORT_NEG                                                                          |

| Operating voltage                                  | 44                       | 62               | V         |                                                                                   |

| Pin current consumption                            | -5                       | +5               | μA        | Port driver off, V <sub>port</sub> differential measurement off, AC generator off |

| Pin Name                                           | PORT_SENS                | Ex               |           |                                                                                   |

| Operating voltage                                  | 0                        | 1.48             | V         | With external 2 ohms (1%) to ground                                               |

| Internal current consumption                       |                          | 20               | μA        |                                                                                   |

| Pin Name                                           | VMAIN                    |                  |           |                                                                                   |

| Operating voltage                                  | 44                       | 57               | V         |                                                                                   |

| V <sub>main</sub> current consumption              |                          | 20               | mA        | Total on V <sub>main</sub>                                                        |

| Pin Name                                           | CP out                   |                  |           |                                                                                   |

| Operating voltage                                  | 44                       | 67               | V         |                                                                                   |

| Pin current consumption                            |                          | 5                | mA        |                                                                                   |

| Pin Name                                           | ADC <sub>2p5</sub> , VCC | 2p5, Vperi, EXT_ | REG       |                                                                                   |

| ADC <sub>2p5</sub> output voltage                  | 2.45                     | 2.55             | V         |                                                                                   |

| ADC <sub>2p5</sub> internal current<br>consumption |                          | 6                | mA        | Recommended external cap. = 47 to 135 nF                                          |

| VCC <sub>2p5</sub> output voltage                  | 2.37                     | 2.62             | V         | Recommended external cap. = 47 to 135 nF                                          |

| VCC <sub>2p5</sub> internal current<br>consumption |                          | 5                | mA        |                                                                                   |

| VPERI output voltage                               | 3.13                     | 3.46             | V         | Recommended external cap. = 1 to 4.7 µF                                           |

| VPERI external current load                        |                          | 6                | mA        | Without external NPN                                                              |

| EXT_REG output current                             |                          | 6                | mA        | When using external NPN for VPERI                                                 |

#### Electrical Characteristics for Analog I/O Pads (continued)

| PARAMETER           | MIN.             | MAX.               | UNIT | REMARKS                                          |

|---------------------|------------------|--------------------|------|--------------------------------------------------|

| Pin Name            | ASICINI, I2C     | INI                |      |                                                  |

| Operating voltage   | 0                | ADC <sub>2p5</sub> | V    |                                                  |

| Current consumption | -1               | +1                 | μA   |                                                  |

| Pin Name            | I <sub>REF</sub> |                    |      |                                                  |

| Output voltage      | 1.21             | 1.34               | V    | With external 24.9 k $\Omega$ resistor to ground |

#### **Dynamic Characteristics**

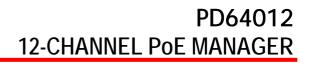

The PD64012 is an advanced power-limiting device that uses three programmable current level thresholds ( $I_{min}$ ,  $I_{cut}$ ,  $I_{lim}$ ) and two timers ( $T_{min}$ ,  $T_{cut}$ ), to operate as shown in Figure 2. Loads that dissipate more than  $I_{cut}$  for longer than  $T_{cut}$  (OVL\_S to OVL) are classified as overloads and are automatically shutdown. Output power dissipation below  $I_{min}$  for during more than  $T_{min}$  (UDL\_S to UDL) will be classified as no-load and will also be shutdown. Automatic recovery from overload and no-load conditions are attempted every  $T_{OVLREC}$  and  $T_{UDLREC}$  periods (typically 5 and 1 seconds, respectively). In any case, output power is limited to  $I_{lim}$ , which is a maximum peak power allowed at the port.

| PARAMETER                                              |                                                                                   | CONDITIONS                                                                                                                  | MIN. | TYP. | MAX. | UNIT |

|--------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Automatic recovery from<br>overload shutdown           | Toverec value, measured from port shutdown (can be modified through control port) |                                                                                                                             |      | 5    |      | S    |

| Automatic recovery from<br>no-load shutdown            |                                                                                   | alue, measured from port shutdown<br>nodified through control port)                                                         |      | 1    |      | S    |

| Cutoff timers accuracy                                 | Typical a                                                                         | ccuracy of T <sub>cut</sub>                                                                                                 |      | 10   |      | ms   |

| Inrush current                                         | I <sub>Inrsh</sub>                                                                | For t=50 ms, Cload=180 uF max.                                                                                              | 400  |      | 450  | mA   |

| Output current operating range                         | I <sub>port</sub>                                                                 | Continuous operation after<br>startup period.                                                                               | 10   |      | 350  | mA   |

| Output power available, operating range                | P <sub>port</sub>                                                                 | Continuous operation after startup period, at port output.                                                                  | 0.57 |      | 15.4 | W    |

| Off mode current                                       | I <sub>min1</sub>                                                                 | Must disconnect for t greater than T <sub>UVL</sub>                                                                         | 0    |      | 5    | mA   |

|                                                        | I <sub>min2</sub>                                                                 | May or may not disconnect for t greater than TuvL                                                                           | 5    | 7.5  | 10   | mA   |

| PD power maintenance<br>request drop-out time<br>limit | T <sub>PMDO</sub>                                                                 |                                                                                                                             |      |      | 400  | ms   |

| Over load current detection range                      | I <sub>cut</sub>                                                                  | Time limited to TovL                                                                                                        | 350  |      | 400  | mA   |

| Over load time limit                                   | Tovl                                                                              |                                                                                                                             | 50   |      | 75   | ms   |

| Turn on rise time                                      | Trise                                                                             | From 10% to 90% of $V_{port}$<br>(specified for PD load consisting<br>of 100 uF capacitor in parallel to<br>200 $\Omega$ ). | 15   |      |      | us   |

| Turn off time                                          | Toff                                                                              | From V <sub>port</sub> to 5 Vdc                                                                                             |      |      | 500  | ms   |

### **Thermal Data**

**Power consumption** – the internal power consumption of a single device from the DC input is based on:

Input voltage range...... 44 to 57 VDC Input current...... 10 mA typ.; 15 mA max.

$\begin{array}{l} \mathsf{P}_{main} = \mathsf{V}_{main} \; x \; \mathsf{I}_{main} \\ \mathsf{P}_{main} \; typ. = 48 \; \mathsf{VDC} \; x \; 10 \; \mathsf{mA} = 0.480 \; \mathsf{W}_{.} \\ \mathsf{P}_{main} \; \mathsf{max.} = 57 \; \mathsf{VDC} \; x \; 15 \; \mathsf{mA} = 0.855 \; \mathsf{W} \end{array}$

**Device Power Dissipation** – the PD64012 incorporates 12 power MOSFETs, each characterized by:

Resistance from drain-source R\_{ds(on)} = 0.3  $\Omega$  typ. ; 0.5  $\Omega$  max. Drain-source current I\_ds = 360 mA max.

Maximum power dissipation P<sub>MOSFET</sub> max. of a single PD64012 device (for 12 MOSFETs) :

$[(I_{ds})^2 \times R_{ds(on)}] \times 12 = [(0.36 \text{ A})^2 \times 0.5 \Omega] \times 12 = 0.78 \text{ W}$

Charge pump (see Analog Section of Block Diagram Description, hereafter) power dissipation  $P_{CP}$  is 0.21 W.

Total power dissipation P<sub>total</sub> by device, under maximum conditions:

$P_{total} = P_{main} max. + P_{MOSFET} max. + P_{CP} = 0.855 \text{ W} + 0.78 \text{ W} + 0.21 \text{ W} = 1.845 \text{ W}$

#### Figure 2: Power Limits

#### **Protection Mechanism**

The PD64012 includes internal thermal protection to avoid junction overheat. Three types of temperature sensors are integrated into the device: two are used for protection and one for temperature monitoring.

<u>*Hi-temp protection*</u> – the device contains thermal shutdowns. This protection system is activated in extreme conditions.

**Lo-temp protection** – there are thermal sensors that are intended to protect the functionality of the device, in cases of temperature rise.

**Indicator sensors** – four temperature sensors monitor the local temperature in the device. Their average is also calculated by the PD64012. All values are stored in internal registers for data retrieval. The register values are calculated by:

Decimal value = 684 - 1.514 x [( $T_{junc}$ )+ 40 °C].

## Pins Descriptions \_\_\_\_\_

| PIN       | PIN NAME               | PIN TYPE                 | PIN DESCRIPTION                                                    |

|-----------|------------------------|--------------------------|--------------------------------------------------------------------|

| 1.        | VPORT_POS0             | Analog I/O               | Port 0 positive voltage feeding                                    |

| 2.        | VPORT_POS1             | Analog I/O               | Port 1 positive voltage feeding                                    |

| 3.        | VPORT_POS2             | Analog I/O               | Port 2 positive voltage feeding                                    |

| 4.        |                        | Analog I/O               | Port 3 positive voltage feeding                                    |

| 4.<br>5.  | VPORT_POS3             | ,                        | Port 4 positive voltage feeding                                    |

| 5.<br>6.  | VPORT_POS4             | Analog I/O               |                                                                    |

| 0.<br>7.  | VPORT_POS5             | Analog I/O               | Port 5 positive voltage feeding<br>Port 6 positive voltage feeding |

| 7.<br>8.  | VPORT_POS6             | Analog I/O               | Port 8 positive voltage feeding                                    |

| 0.<br>9.  | VPORT_POS7             | Analog I/O<br>Analog I/O | Port 8 positive voltage feeding                                    |

| 9.<br>10. | VPORT_POS8             | Analog I/O               | Port 9 positive voltage feeding                                    |

| 10.       | VPORT_POS9             | Analog I/O               | Port 10 positive voltage feeding                                   |

| 11.       | VPORT_POS10            | Analog I/O               | Port 10 positive voltage feeding                                   |

| 12.       | VPORT_POS11<br>Vmain   | Supply                   | Main Voltage supply                                                |

| 14.       | CP_IN                  | Analog I/O               | Charge Pump input, 48V+5V                                          |

| 14.       | CP_IN<br>CP_OUT        | Analog I/O               | Charge Pump Pulse Output                                           |

| 15.       | REF_PORT_NEG           | Analog I/O               | Port negative reference                                            |

| 10.       | TEST_MODE              | Analog I/O               | Test Mode Pin (connect to ground)                                  |

| 17.       | VPORT_NEG11            | Analog I/O               | Port 11 negative voltage feeding                                   |

| 10.       | AGND                   | Supply                   | Analog ground                                                      |

| 20.       | PORT_SENSE11           | Analog I/O               | Channel current monitoring                                         |

| 20.       | VPORT_NEG10            | Analog I/O               | Port 10 negative voltage feeding                                   |

| 21.       | PORT SENSE10           | Analog I/O               | Channel current monitoring                                         |

| 23.       | VPORT_NEG9             | Analog I/O               | Port 9 negative voltage feeding                                    |

| 24.       | PORT_SENSE9            | Analog I/O               | Channel current monitoring                                         |

| 25.       | PORT SENSE8            | Analog I/O               | Channel current monitoring                                         |

| 26.       | VPORT_NEG8             | Analog I/O               | Port 8 negative voltage feeding                                    |

| 27.       | PORT_SENSE7            | Analog I/O               | Channel current monitoring                                         |

| 28.       | VPORT_NEG7             | Analog I/O               | Port 7 negative voltage feeding                                    |

| 29.       | PORT_SENSE6            | Analog I/O               | Channel current monitoring                                         |

| 30.       | DISABLE_PORTS_N        | Digital input            | Disable all ports power (active low)                               |

| 31.       | VPORT_NEG6             | Analog I/O               | Port 6 negative voltage feeding                                    |

| 32.       | CS1_N                  | Digital I/O              | SPI bus, Chip Select 1                                             |

| 33.       | DGND                   | Supply                   | Digital ground                                                     |

| 34.       | CS0_N                  | Digital I/O              | SPI bus, Chip Select 0                                             |

| 35.       | MISO                   | Digital I/O              | SPI bus, Master in/slave out                                       |

| 36.       | MOSI                   | Digital I/O              | SPI bus, Master out/slave in                                       |

| 37.       | SCK                    | Digital input            | SPI bus, Serial clock I/O                                          |

| 38.       | SCL                    | Digital input            | I2C bus, Serial Clock Input                                        |

| 39.       | SDA                    | Digital I/O              | I2C bus, open drain                                                |

| 40.       | RESET_N                | Digital I/O              | Active Low Reset I/O                                               |

| 41.       | IREF                   | Analog I/O               | Current reference                                                  |

| 42.       | ASICINI                | Analog input             | Analog input for ASIC initialization                               |

| 43.       | VCC <sub>2p5</sub>     | Supply                   | Internal 2.5 V supply (do not use!)                                |

| 44.       | I2CINI                 | Analog input             | Analog input for I2C initialization                                |

| 45.       | QGND                   | Supply                   | Quiet analog ground                                                |

| 46.       | ADC <sub>2p5</sub>     | Supply                   | ADC reference (do not use!)                                        |

| 47.       | EXT_REG                | Analog out               | External regulation                                                |

| 48.       | V <sub>PERI</sub>      | Analog out               | Regulated 3.3 V power source                                       |

| 49.       | Reserved               | Digital input            | (Connect to ground)                                                |

| 50.       | V <sub>PORT_NEG5</sub> | Analog I/O               | Port 5 negative voltage feeding                                    |

| PIN | PIN NAME    | PIN TYPE   | PIN DESCRIPTION                 |  |

|-----|-------------|------------|---------------------------------|--|

| 51. | AGND        | Supply     | Analog ground                   |  |

| 52. | PORT_SENSE5 | Analog I/O | Channel current monitoring      |  |

| 53. | VPORT_NEG4  | Analog I/O | Port 4 negative voltage feeding |  |

| 54. | PORT_SENSE4 | Analog I/O | Channel current monitoring      |  |

| 55. | Vport_neg3  | Analog I/O | Port 3 negative voltage feeding |  |

| 56. | PORT_SENSE3 | Analog I/O | Channel current monitoring      |  |

| 57. | PORT_SENSE2 | Analog I/O | Channel current monitoring      |  |

| 58. | VPORT_NEG2  | Analog I/O | Port 2 negative voltage feeding |  |

| 59. | PORT_SENSE1 | Analog I/O | Channel current monitoring      |  |

| 60. | VPORT_NEG1  | Analog I/O | Port 1 negative voltage feeding |  |

| 61. | PORT_SENSE0 | Analog I/O | Channel current monitoring      |  |

| 62. | SENSE_NEG   | Analog I/O | Port sense reference            |  |

| 63. | VPORT_NEG0  | Analog I/O | Port 0 negative voltage feeding |  |

| 64. | Reserved    | TBD        | Not connected                   |  |

## Functional Description \_

#### **Operational Modes**

The PD64012 supports two main modes of operation, based on two different architectures, as described hereafter. The two modes are: Enhanced mode and Automatic mode.

<u>Enhanced mode</u> – in this mode of operation, the PD64012s communicate with the PD63000 PoE MCU (dedicated MCU for Power over Ethernet tasks), through a Serial Parallel Interface (SPI) bus. In this mode, all PD64012s are directly connected to the PD63000 through the SPI, in slave mode. The MCU is used for additional Power over Ethernet features, such as:

- Legacy PDs detection (including Cisco discovery)

- Enhanced power management algorithms

- LED indicators support

- Port matrix control

- Communication protocol translator.

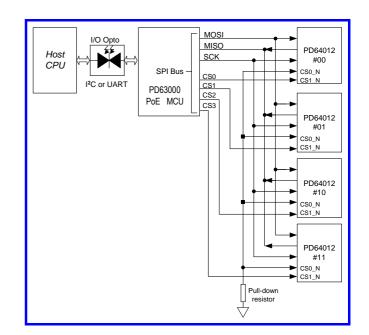

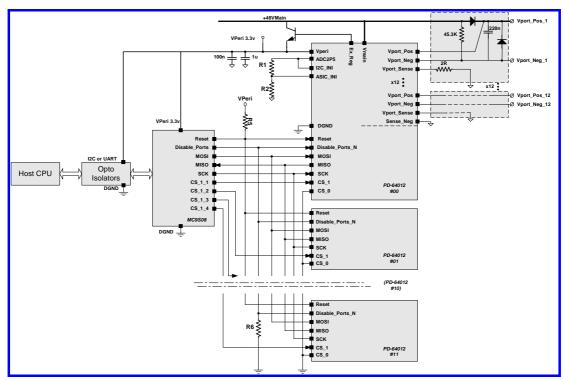

The switch host CPU communicates with the PD63000, via an isolated  $\rm l^2C$  or UART bus, as shown in Figure 3.

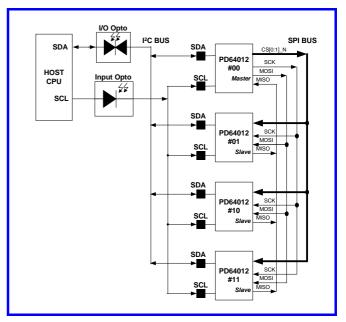

Figure 3: Enhanced Mode

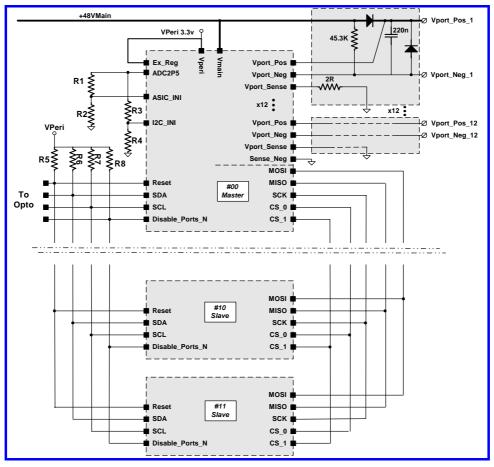

<u>Automatic mode</u> – in this mode the PD64012 PoE Managers communicate with the host CPU, through an isolated  $I^2C$  bus. The PD64012 SPI bus is dedicated for internal communication among PD64012s (for power management), as illustrated in Figure 4.

Anyone of the devices (for example, PD64012 #00) may be configured as Master, while the others are Slaves. This Master/Slave configuration only affects the Serial Peripheral Interface (SPI) bus. It is critical that only one of them be set-up as a Master, with the others acting as Slaves, in order to avoid SPI clock and data I/Os contentions.

Figure 4: Automatic Mode

#### Mode Configuration Method

The PoE Manager's configuration is done via the ASIC\_INI pin, according to the following table. The ASIC\_INI analog signal is converted into a 10-bit register (A/D). Once a hard Reset pulse is detected, the data is latched into an internal mode register.

| MODE NAME           | ASIC_INI<br>VOLTAGE LEVEL | ASIC_INI INTERNAL A/D<br>REGISTER | I <sup>2</sup> C 2 LSB ADDRESS<br>(set internally) |

|---------------------|---------------------------|-----------------------------------|----------------------------------------------------|

| Enhanced mode       | 0.31 to 0.63 V            | 001                               | 00                                                 |

| Auto mode – Slave 1 | 0.63 to 0.94 V            | 010                               | 01                                                 |

| Auto mode – Slave 2 | 0.94 to 1.25 V            | 011                               | 10                                                 |

| Auto mode – Slave 3 | 1.25 to 1.56 V            | 100                               | 11                                                 |

| Auto mode - Master  | 2.19 to 2.5 V             | 111                               | 00                                                 |

Notes:

In the Auto mode – the PD64012 is communicating with the host via  $l^2C$ .

In the Enhanced mode - the PD64012 is communicating with the controller via SPI.

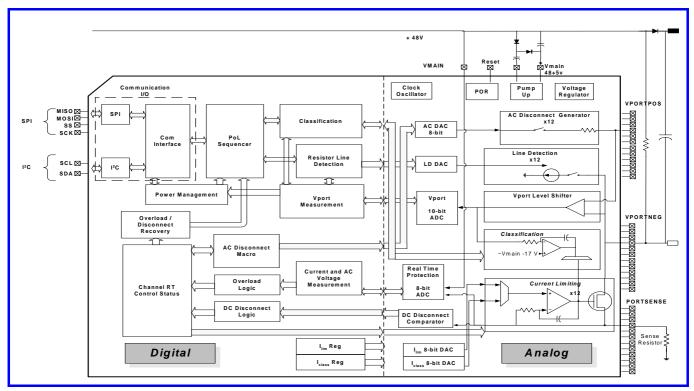

#### Block Diagram Description (see Figure 5)

The PD64002 PoE Manager complies with all requirements of IEEE standard 802.3af-2003, for detection. The device has been designed around two major sections:

- 1. A common Digital section, that serves all 12 channels

- 2. Twelve separate and identical channels for driving ports.

## PD64012 12-CHANNEL PoE MANAGER

#### Figure 5: Internal Block Diagram

#### **Digital Section**

#### **Communication I/O**

The PD64012 incorporates two communication interfaces. When operating in the Enhanced mode, an SPI bus connects the PD63000 MCU to the PD64012s. The second interface is the  $I^2C$ , used in the Automatic mode (with the host).

Both interfaces are used to communicate the contents of internal registers between the PD64012 logic and the MCU.

#### **PoE Sequencer**

This central block of the Digital section includes a combination of internal state machines (macros). It is fed from the Overload/Disconnect Recovery circuit and from the Power Management block.

#### **Power Management**

Receives data from the Vport Measurement block and receives commands and controls from the Communication Interface. This, in order to control the power allocated to the system, as defined by the host. Power Management receives requests to enable ports and decides, by communicating with the Sequencer, whether power is to be allocated.

#### **Overload /Disconnect Recovery**

There is a number of macros which decide on port enable and some on port disconnect. *Port enabling:* Classification, Resistor Line Detection and Vport Measurement.

*Port disable*: AC Disconnect, DC Disconnect and Overload Logic. These macros are connected to the Channel RT Control Status block. Based on the inputs from these macros, the Channel RT controller starts the shutdown operation or the recovery process. This is done according to preprogrammed parameters for different time windows, as shown in Figure 2, Power Limits.

#### Macros (802.3 Standard)

<u>Classification</u> – upon request from the MCU, a state machine applies a regulated 18 V on the port output. The internal current is measured by a metering circuit, compared with a number of preset ranges and in this manner, the classification is established.

<u>Line Detection</u> – the MCU generates a request to have four separate voltage levels applied to the output port. A unique measurement circuit monitors the delta between the second and third levels, and between the third and fourth levels. The voltage differences are compared with values stored in registers. By comparing the values, the system can decide whether or not to enable the port.

<u>AC Disconnect</u> – the system applies a sinusoidal signal to the positive terminal of the port. The voltage developed on the port terminals is proportional to the value of the load. If the load is high, the AC component riding on the port terminals, will be small and reversed. If the load low, the AC component will be large. A special circuit measures the level of the AC component and compares it with a value stored in a register. Based on the comparison results, the system decides to disable the port or not.

<u>DC Disconnect for DC Modulation</u>: senses if the port current falls below 7.5 mA. If so, a flag is raised and timers in the Channel RT Controller are enabled. The Channel RT Controller acts according to pre-programmed limits for thresholds and time windows, prior to initiating a disconnect status for that port. The circuitry takes into account PD's that modulate their current consumption, disconnecting them only if necessary.

#### Analog Section

#### **Clock Oscillator**

A 4 MHz oscillator, used for internal logic and timers.

#### Power on Reset (POR)

Monitors the internal regulated +3.3 V and generates a Reset signal, if this value drops below 2.8 V. The Reset signal resets the ASIC's logic and generates an output flag to the other PD64012 ASICs, via the RESET\_N pin.

#### Charge Pump

This circuit block generates a voltage which increases the main input voltage by 10 VDC (approx.). This potential is used to operate the AC Disconnect circuits.

#### **Current Limit**

This circuit continuously checks the current for enabled ports. Once the current exceeds a specific level, the system starts to measure the elapsed time. If this period is greater than a preset threshold, the port is disabled. In all cases, the output current will not exceed a pre-established maximum.

#### **Real Time Protection**

This circuit receives flags from two locations in the PD64012: from the sense resistor and from the main input voltage (48 V). A 10-bit A/D Converter feeds the Digital section, at the Current and AC Voltage Measurement block. From there on, the system handles the levels according to pre-programmed limits.

#### **DC Disconnect Comparator**

Once the port current drops below a set limit, the comparator provides an indication to the DC Disconnect Logic to that effect.

### PD-IM-7348 Evaluation Board

The performance features of the PD64012 PoE Manager can be fully appreciated with the PD-IM-7348 Evaluation Board. This board allows to investigate all functions accessible to the designer. The evaluation board supports up to 48 ports, has both I<sup>2</sup>C and UART interfaces and can demonstrate the Enhanced and Auto modes.

### I<sup>2</sup>C Interface

A standard  $I^2C$  interface is used to communicate between the PD64012 and the host controller. The PD64012's  $I^2C$  interface is designed to support the following features:

- SLAVE mode only

- Normal-mode and Fast-mode data rate (0 to 400 kb/s)

- 7-bit addressing the 7-bit addressing (128 addresses) uses the following address code:

- First MSB = "0" (forced by internal logic)

- 4 MSB address bits are set via the I2C\_INI pin, according to the following table

- "mm" bits are set through the ASIC\_INI pin (Enhanced mode = "00"; Automatic mode Master ="00"; Automatic mode Slave = "01", "10", "11")

- "*xxx*" 3 LSB are ignored.

| I <sup>2</sup> C ADDRESS | I2C_INI VOLTAGE LEVEL | I2C_INI INTERNAL A/D REGISTER | NOTES                             |

|--------------------------|-----------------------|-------------------------------|-----------------------------------|

| Address #0               | 0 to 0.15 V           | 0,0000, <i>mm,xxx</i>         |                                   |

| Address #1               | 0.16 to 0.31 V        | 0,0001, <i>mm,xxx</i>         | General call addresses; not to be |

| Address #2               | 0.32 to 0.47 V        | 0,0010, <i>mm,xxx</i>         | used                              |

| Address #3               | 0.48 to 0.62 V        | 0,0011, <i>mm,xxx</i>         |                                   |

| Address #4               | 0.63 to 0.77 V        | 0,0100, <i>mm,xxx</i>         |                                   |

| Address #5               | 0.78 to 0.93 V        | 0,0101, <i>mm,xxx</i>         |                                   |

| Address #6               | 0.94 to 1.09 V        | 0,0110, <i>mm,xxx</i>         |                                   |

| Address #7               | 1.10 to 1.24 V        | 0,0111, <i>mm,xxx</i>         |                                   |

| Address #8               | 1.25 to 1.40 V        | 0,1000, <i>mm,xxx</i>         |                                   |

| Address #9               | 1.41 to 1.55 V        | 0,1001, <i>mm,xxx</i>         |                                   |

| Address #10              | 1.56 to 1.71 V        | 0,1010, <i>mm,xxx</i>         |                                   |

| Address #11              | 1.72 to 1.87          | 0,1011, <i>mm,xxx</i>         |                                   |

| Address #12              | 1.88 to 2.02 V        | 0,1100, <i>mm,xxx</i>         |                                   |

| Address #13              | 2.03 to 2.18 V        | 0,1101, <i>mm,xxx</i>         |                                   |

| Address #14              | 2.19 to 2.33 V        | 0,1110, <i>mm,xxx</i>         |                                   |

| Address #15              | 2.34 to 2.5 V         | 1,1111, <i>mm,xxx</i>         |                                   |

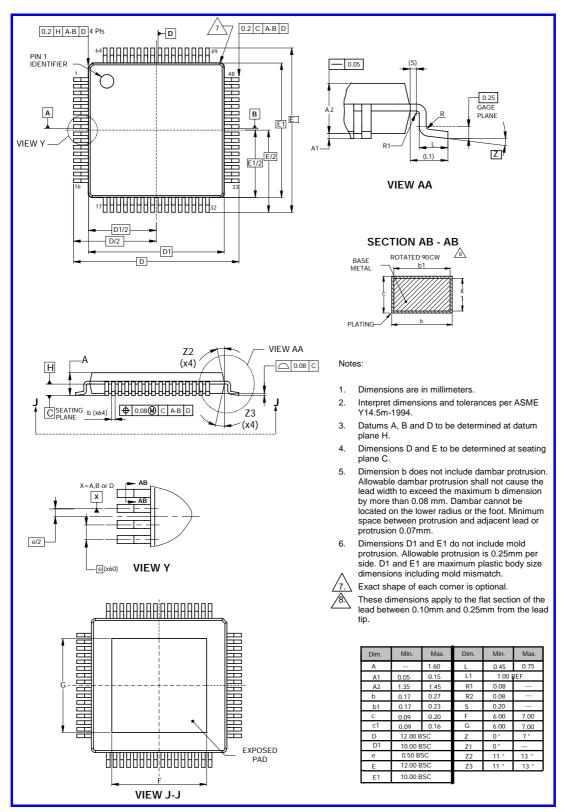

### Package Information

The PD64012 is housed in a 64-pin plastic package, 10 x 10 x 1.4 mm, meeting JEDEC's MS-026 package outline and dimensions. Exposed pad (for heat-sinking purposes) dimensions are 6.00 by 7.00 mm.

#### Figure 6: PD64012 Mechanical Dimensions

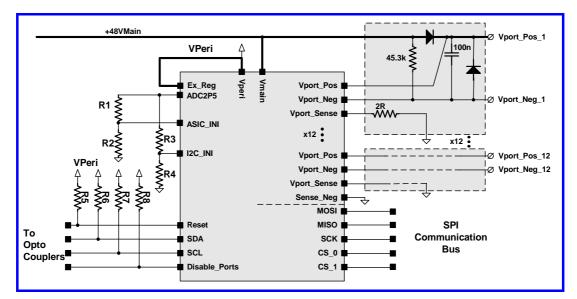

## Applications

The PD64012 may be integrated into a number of applications, ranging from daughter boards to full integration into Ethernet switches. Examples of such applications are:

<u>Integrated directly in a switch</u> – facilitates the entire PoE concept, by including the ASIC(s) on the main switch PCB. <u>Daughter board add-on</u> – in which the ASIC is integrated into a small PCB for PoE, mounted on top of the switch's main PCB.

<u>Midspan units</u> – stand alone devices, installed between the Ethernet switch and powered devices (telephone, camera, wireless LAN, etc..). These Midspan units include the PD64012 ASIC as a PoE control element, to inject power over the communication lines.

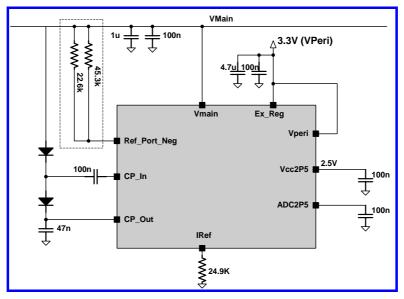

Figures 7 thru 10 provide detailed schematic diagrams for various applications of the PD64012.

Figure 7 - Single-port Application with AC Disconnect Support

**Figure 8 - Typical Power Filtering**

06-0003-058 (Rev. 2.8) / 5 August 2004

### PD64012 12-CHANNEL PoE MANAGER

Figure 9 - Enhanced Mode Application

**Reader Notes**

#### Notice

PowerDsine assumes no responsibility or liability arising from the use of this Data Sheet, as described herein, nor does it convey any license under its patent rights or the rights of others.

The information contained herein is believed to be accurate and reliable at the time of printing. However, due to ongoing product improvements and revisions, PowerDsine cannot accept responsibility for inadvertent errors, inaccuracies, subsequent changes or omissions of printed material.

PowerDsine Ltd. reserves the right to make changes to products and to their specifications as described in this document, at any time, without prior notice. No rights to any PowerDsine Ltd. Intellectual property are licensed to any third party, directly, by implication or by any other method.

Covered under one or more of the following patents: 6,643,566; 6,473,608.

#### No Use with Life-Support or Critical Applications

PowerDsine's products are not designed, intended, or authorized for use as components in systems intended for:

- (1) surgical implant into the body, or other applications intended to support or sustain life, or

- (2) any other applications whereby a failure of the PowerDsine's product could create a situation where personal injury, death or damage to persons, systems, data or business may occur.

PowerDsine assumes no liability in connection with use in these situations and the disclaimers provided below in this manual shall apply. Should a buyer purchase or use PowerDsine's products for any such unintended use or unauthorized applications, buyer shall indemnify PowerDsine and its officers and employees against any and all claims arising out of or in connection with any claim of personal injury, death or other damage of the type described above, associated with such use.

#### DISCLAIMERS

POWERDSINE MAKES NO WARRANTY, REPRESENTATION OR GUARANTEE REGARDING THE SUITABILITY OF THE PRODUCTS CONTAINED HEREIN FOR ANY PARTICULAR PURPOSE, NOR DOES POWERDSINE ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCTS OR CIRCUIT, AND SPECIFICALLY DISCLAIMS ANY AN ALL LIABILITY, INCLUDING, WITHOUT LIMITATION, CONSEQUENTIAL OR INCIDENTAL DAMAGES. BY USING OUR PRODUCTS USER AGREES NOT TO MAKE ANY CLAIM FOR PUNITIVE DAMAGES.

POWERDSINE MAKES NO REPRESENTATION OR WARRANTY, EXPRESSED OR IMPLIED, WITH RESPECT TO THE SUFFICIENCY OR ACCURACY OR UTILITY OF ANY INFORMATION CONTAINED HEREIN. POWERDSINE EXPRESSLY ADVISES THAT ANY USE OF OR RELIANCE UPON SAID INFORMATION IS AT THE RISK OF THE USER AND THAT POWERDSINE SHALL NOT BE LIABLE FOR ANY DAMAGE OR INJURY INCURRED BY ANY PERSON OR ORGANIZATION ARISING OUT OF THE SUFFICIENCY, ACCURACY, OR UTILITY OF ANY INFORMATION CONTAINED HEREIN OR IN CONNECTION WITH THE USE OF ANY OF THE PRODUCTS DESCRIBED HEREIN. POWERDSINE IS NOT RESPONSIBLE FOR ANY CHANGES IN THE SPECIFICATIONS OR ERRATA OF THIS PRODUCT. INFORMATION ON THE BASIC PRODUCT CAN BE FOUND AT MOTOROLA'S HOMEPAGE.

#### Revision History

| Revision Level / Date | Para. Affected/page                                                       | Description                                                                                                                            |

|-----------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| 2.3 / 10 Dec. 03      | Ordering<br>Information/page 1                                            | Lower temperature range deleted. Remains single range only: -20 to +85 °C.                                                             |

| 2.4 / 18 Dec. 03      | Mode Configuration<br>Method/page 8<br>I <sup>2</sup> C Interface/page 11 | Deleted extreneous values for ASIC_INI and deleted default Mode value.<br>Deleted primary default value in the table column for Notes. |

| 2.41 / 10 Jan. 04     | Features/page 1                                                           | Changed MIB from draft to RFC 3621.                                                                                                    |

| 2.5 / 9 Feb. 04       | Front & back pages                                                        | Added policy statements and disclaimers.                                                                                               |

| 2.6 / 10 Mar. 04      | Several                                                                   | Added temp. of junction-case, under max ratings; added thermal data on page 4; added protection mechanism on page 5.                   |

| 2.7 / 1 Aug. 04       | Macros/page 8<br>Analog section/page 9                                    | Corrected inacuracies in descriptions.                                                                                                 |

| 2.8 / 5 Aug. 04       | Pin Configuration/1                                                       | Added part number and associated description.                                                                                          |

#### © 2003 PowerDsine Ltd. All rights reserved.

PowerDsine is a registered trademark of PowerDsine LTD. All other products or trademarks are property of their respective owners. The product described by this manual is a licensed product of PowerDsine.