# General Purpose Controller / Memory Chip for Hearing Instruments

GP521 - DATA SHEET

**FEATURES**

- · general purpose

- EEPROM non-volatile memory

- 8 programmable current sink (PCS) control outputs

- can be configured with 6 PCS outputs for hearing instruments (two switchable, four non-switchable)

- · status register

- · data transmission error detection

- synchronization of GP521 internal clocks with program unit clock

#### STANDARD PACKAGING

• Chip (129 x 112 mils)

Au Bump

#### DESCRIPTION

The GP521 is a general purpose controller/memory chip intended for use with audio signal path circuits in programmable hearing instruments.

The GP521 uses a flexible communication standard which allows room for future growth in programmable functions for hearing instruments. The communication with the program unit is over a bi-directional serial data link. Error detection circuitry is used to avoid undesired changes in programmed settings.

An information transfer dialogue consists of the address and data for a register sent to the GP521 and the register contents returned by the GP521. The function controlled by an output of the GP521 is defined by the signal path circuit allowing current controlled parameters. The relationship between the GP521 register addresses and the function on the signal path circuit is defined by a data file in the programming unit. With this format, any software developed for the GP521 can be used for future generations of Gennum's controller/memory circuits and audio signal path circuits.

The GP521 uses EEPROM cells as the long term memory element. These cells will retain the stored data when the power supply is disconnected. Each EEPROM cell is combined with a temporary (RAM) memory cell which makes it possible to evaluate various control settings prior to saving them in the long term EEPROM memory.

The GP521 controls the audio signal path circuit using eight Programmable Current Sinks (PCS). Each PCS has 16 programmable settings. The circuit can be configured for either 6 or 8 PCS outputs. When used with a single pole single throw switch (SPST) under the 6 PCS configuration, it is possible to design a hearing instrument with two programmed settings (i.e. adjusting a low cut filter for either noisy or quiet background environments). The 8 output configuration may be used for circuits that require more programmable but non-switchable settings. An external reference current is used for the PCS's so that the PCS outputs can track with the currents in the audio signal path circuit.

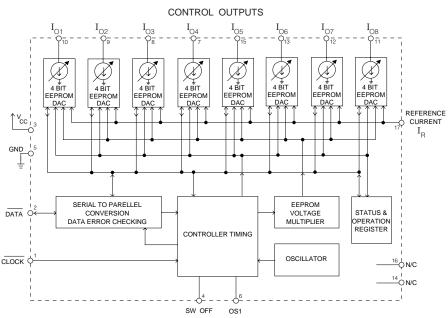

# **BLOCK DIAGRAM**

Revision Date: May 1998 Document No. 510 - 79 - 06

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETER             | VALUE / UNITS            |

|-----------------------|--------------------------|

| Supply Voltage        | 3 V DC                   |

| Min. voltage any pin  | GND - 200 mV             |

| Max. voltage any pin  | V <sub>CC</sub> + 200 mV |

| Operating temperature | 0 to 50 °C               |

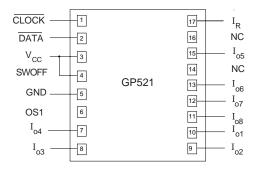

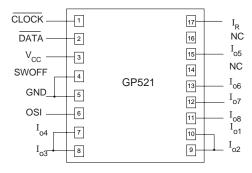

Fig. 1 Chip Pad Diagram

# **ELECTRICAL CHARACTERISTICS**

Current into IC considered positive.

Conditions: Temperature = 25  $^{\rm o}$ C,  $\rm I_R = ~4~\mu A, ~V_{\rm CC} = 1.3~V$

| PARAMETER                   | SYMBOL                     | CONDITIONS                                         | MIN.                  | TYP. | MAX     | UNITS    |

|-----------------------------|----------------------------|----------------------------------------------------|-----------------------|------|---------|----------|

| Supply Voltage              | V <sub>CC</sub>            |                                                    | -                     | 1.3  | 3       | V        |

| Supply Current:             | I <sub>CC</sub>            | Normal operation mode Program mode                 | -                     | -    | 25<br>1 | μA<br>mA |

| EEPROM read / write cycles  |                            |                                                    | 1000                  | -    | -       | cycles   |

| Low Input Voltage "low"     | V <sub>L</sub>             |                                                    | -                     | -    | 200     | mV       |

| High Input Voltage "high"   | V <sub>H</sub>             |                                                    | V <sub>CC</sub> - 0.2 | -    | -       | V        |

| Clock Rate                  | $f_{CL}$                   |                                                    | -                     | 6    | 50      | kHz      |

| PROGRAMMABLE CURREN         | PROGRAMMABLE CURRENT SINKS |                                                    |                       |      |         |          |

| Reference current           | I <sub>R</sub>             |                                                    | -                     | -    | 14      | μА       |

| PCS Bias Voltage            | V <sub>PCS</sub>           |                                                    | 400                   | 500  | -       | mV       |

| Number of Settings          |                            |                                                    | N/A                   | 16   | N/A     |          |

| Output Current for set "15" | I <sub>o15</sub>           | DAC set to 15 V <sub>PCS</sub> = 0.5 V (note 2)    | 6.81                  | 7.5  | 8.25    | μΑ       |

| Linearity Error             | η                          | DAC set for 1,2,4,8 (note 1, 2)                    | N/A                   | ±10% | N/A     | -        |

| Output Current offset "0"   | I <sub>OFFS</sub>          | DAC set to 0 (note 1, 2)                           | -                     | 0    | -       | nA       |

| Output Leakage Current      | IL                         | DAC set to 0 V <sub>PCS</sub> = 0.5 V (note 1, 2)  | -                     | 0    | -       | nA       |

| Early Voltage =             | V <sub>a</sub>             | DAC set to 15 (note 1, 2)                          |                       |      |         |          |

| 1 Channel length modulation |                            | Set $V_{PCS} = 0.5V$ and $V_{PCS} = 0.7V$ (S9 = b) | -                     | 37   | -       | V        |

All switches remain as shown in Test Circuit unless otherwise stated in condition columns.

- NOTES:

1. Refer to the definition section

2. Measurements performed for all DAC's separately (SWS 1 to 8 closed sequentially).

510 - 79 - 06 2

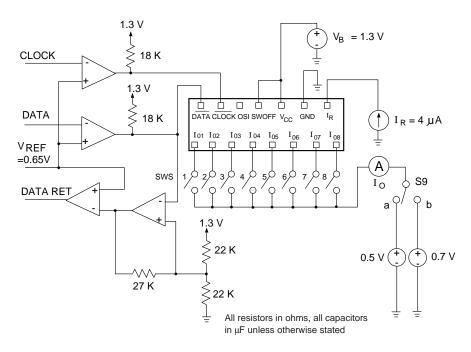

Fig. 2 Digital Test Circuit

3

### **GP521 DIGITAL TESTING**

The GP521 is tested for digital functionality via a series of *reads* and *writes* to the GP521. For a summary of the actual testing refer to Document No. 520-35

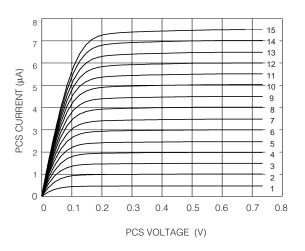

Fig. 3 PCS Current (Sink) vs PCS Voltage at DAC Setting 0 to 15,  $\rm~I_R = 4\mu A$

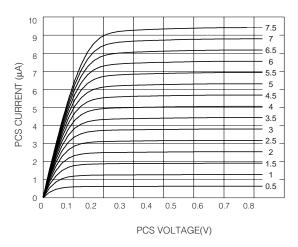

Fig. 4 PCS Current (Sink) vs PCS Voltage  $\rm I_R = 0 ~to~7.5 \mu A$  (step 0.5  $\mu A$ ) DAC set at 10

510 - 79 - 06

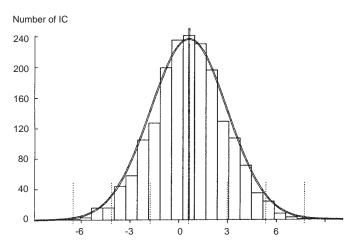

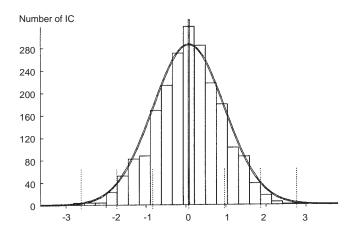

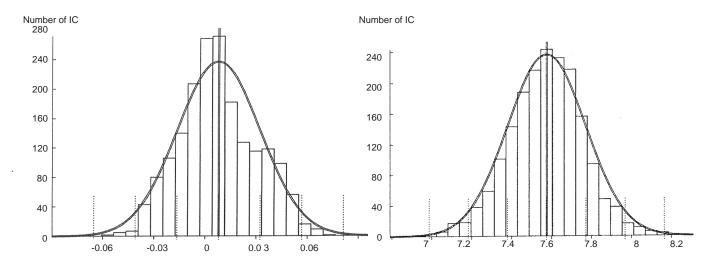

# TYPICAL DISTRIBUTION of PCS CURRENT

Number of IC

240 200 160 120 80 40 0 -6 -4 -2 0 2 4

Fig. 5 Linearity Error (Digital Input set to 2) [%]

Fig. 6 Linearity Error (Digital Input set to 4) [%]

Fig. 7 Linearity Error (Digital Input set to 8) [%]

Fig. 8 Output Current Off set  $[\mu A]$

Fig. 9 Output Current for Digital Input set to 15 [μA]

<sup>\*</sup> The data was collected on limited numbers of the chips.

#### PIN DESCRIPTION

CLOCK - The clock pulses for synchronization of the data transfer. The clock pulses are provided by the programming unit.

DATA - The input/output pin allow for serial data transfer between the GP521 and the programming unit.

$V_{\rm CC}$  - Recommended supply voltage for GP521 is 1.3V

SWOFF - The logic state of SWOFF determines whether the GP521 operates at 6 or 8 PCS configuration. When SWOFF is high, all eight ( $I_{O1}$  to  $I_{O8}$ ) PCS are available (8 PCS configuration) Figure 10.

Fig. 10 EIGHT OUTPUT CONFIGURATION

When SWOFF is low, four PCS  $(I_{O5}$  to  $I_{O8})$  are available; availablility of other two PCS is dependent on the voltage on pin OS1. For this configuration (6 PCS configuration) the necessary hardware connections are presented in Figure 11.

Fig. 11 SIX OUTPUT CONFIGURATION

OS1 - The voltage level on this pin determines the selection of four PCS ( $I_{\rm O_1}$  to  $I_{\rm O_4}$ ) for 6 PCS configuration. As indicated on Figure 11, pin  $I_{\rm O_1}$ ,  $I_{\rm O_2}$  and  $I_{\rm O_3}$ ,  $I_{\rm O_4}$  are connected together. If OS1 is low,  $I_{\rm O_1}$  and  $I_{\rm O_3}$  are set to high impedance. Therefore the PCS,  $I_{\rm O_2}$  and  $I_{\rm O_4}$  are permitted to sink current.

5

Similarly if OS1 is high,  $I_{\rm O2}$  and  $I_{\rm O4}$  are set as high impedance points. This allows PCS  $I_{\rm O4}$  and  $I_{\rm O3}$  to sink current.

TABLE 1 EFFECTS OF SWOFF AND OS1 INPUTS

| SWOFF | OS1 | OUTPUT                                   | PCS Register Address  |  |

|-------|-----|------------------------------------------|-----------------------|--|

| 0     | 1   | ( I <sub>O1</sub> and I <sub>O3</sub> )* | (0001000 and 0001010) |  |

| 0     | 0   | ( $I_{O2}$ and $I_{O4}$ )*               | (0001001 and 0001011) |  |

| 1     | Х   | I <sub>O1</sub>                          | 0001000               |  |

| 1     | X   | I <sub>O2</sub>                          | 0001001               |  |

| 1     | Х   | I <sub>O3</sub>                          | 0001010               |  |

| 1     | Х   | I <sub>O4</sub>                          | 0001011               |  |

| X     | Х   | I <sub>O5</sub>                          | 0001100               |  |

| ×     | Х   | I <sub>O6</sub>                          | 0001101               |  |

| ×     | X   | I <sub>O7</sub>                          | 0001110               |  |

| Х     | ×   | I <sub>O8</sub>                          | 0001110               |  |

Note\* The complementary outputs are set as high impedance points.

$I_{\text{O1}}$  -  $I_{\text{O8}}$  - Each pin is the output of the specific Programmable Current Sink (PCS). Each PCS consists of four bit EEPROM memory, Digital to Analog Converter (DAC) and current sink. The EEPROM stores the four bit information written during initialization of the system. Four bit memory allows for 16 settings of the current sink. For simplicity, consider the current sink as a variable resistor. The value of this resistor is dependent on the DAC setting; DAC is controlled by the binary value of the RAM memory. To define output current of the current sink, it is necessary to set the voltage applied to the PCS output. This voltage is recommended to be 0.5 V. If the binary value of the EEPROM increases by one, the value of the output current increases by 0.125 x  $I_{\rm B}$ .

$I_R$  - The reference current delivered from the outside source (eg. GP520A). This current determines the incremental value of the programmable current sink for each increase of the EEPROM address value. The valid addresses run from 0 through to 15. Each step is defined as  $\Delta I = I_R \times 0.125,$  therefore maximum current at setting 15 is equal to  $I_{15} = I_R \times 0.125 \times 15.$

#### **GP521 REGISTERS**

There are four types of registers used in the GP521. Their functions are described as follows:

$\mbox{ID}$  - Hearing instruments identification register. The contents are set to 0000000 indicating a visual identification is required.

STATUS - Monitors the present state of the GP521 and records whether an error has occurred in the previous dialogue with the program unit. The STATUS is *read only* register.

OPERATION - Performs EEPROM *read to (write from)*RAM operations. The desired operation is specified by the data sent to the register. This is *write-only* register.

PCS - Stores the programmable current sink settings.

The register address definitions and the data bit definitions are given in Tables 2 and 3. The STATUS and OPERATION registers are two different registers sharing a common address.

TABLE 2 REGISTER ADDRESS DEFINITIONS

| ADDRESS | FUNCTION            | TYPE       | MEMORY CELL |

|---------|---------------------|------------|-------------|

|         |                     |            | *           |

| 0000000 | ID                  | read only  | ROM         |

| 0000001 | STATUS/OP           | read/write | RAM / ROM   |

| 0000010 |                     |            |             |

| to      | unused*             |            |             |

| 0000111 |                     |            |             |

| 0001000 | PCS I <sub>O1</sub> | read/write | RAM +EEPROM |

| 0001001 | PCS I <sub>O2</sub> | read/write | RAM +EEPROM |

| 0001010 | PCS I <sub>O3</sub> | read/write | RAM +EEPROM |

| 0001011 | PCS I <sub>O4</sub> | read/write | RAM +EEPROM |

| 0001100 | PCS I <sub>O5</sub> | read/write | RAM +EEPROM |

| 0001101 | PCS I <sub>O6</sub> | read/write | RAM +EEPROM |

| 0001110 | PCS I <sub>O7</sub> | read/write | RAM +EEPROM |

| 0001111 | PCS I <sub>O8</sub> | read/write | RAM +EEPROM |

| 0010000 |                     |            |             |

| to      | unused*             |            |             |

| 1111111 |                     |            |             |

The GP521 will indicate an error if an unused register is accessed or a *write to* is attempted to a *read-only* register.

TABLE 3 DATA BIT DEFINITIONS

| DATA BIT | STATUS REGISTER                         | OPERATION REGISTER               | PCS REGISTER*                            |

|----------|-----------------------------------------|----------------------------------|------------------------------------------|

| 0000000  |                                         | No operation                     | set I <sub>O</sub> = 0                   |

| XXXXXX1  | PCS outputs may be different than       |                                  |                                          |

|          | EEPROM values                           | Load EEPROM values into PCS      | set $I_O = 0.125 I_R$                    |

| XXXXX1X  | Circuit busy with EEPROM write          | Save PCS values in EEPROM memory | set I <sub>O</sub> = 0.25 I <sub>R</sub> |

| XXXX1XX  | Transmission error on previous dialogue | unused                           | set I <sub>O</sub> = 0.5 I <sub>R</sub>  |

| XXX1XXX  | Bad Address and/or Operation Error      |                                  |                                          |

|          | on previous dialogue                    | unused                           | set I <sub>O</sub> = 1.0 I <sub>R</sub>  |

| XX1XXXX  | unused                                  | unused                           | unused                                   |

| X1XXXXX  | unused                                  | unused                           | unused                                   |

| 1XXXXXX  | unused                                  | unused                           | unused                                   |

<sup>\*</sup>Note: 1. Combining data bits in a word is equivalent to combining the corresponding definitions. (i.e. 0001101 in the PCS register would set the output to  $I_{\rm O}$  =1.625  $I_{\rm B}$ ).

510 - 79 - 06

<sup>2.</sup> The upper 3 data bits are ignored except for parity checking.

#### **ERROR DETECTION**

The errors detected and recorded in the STATUS register are defined as follows:

#### TRANSMISSION ERROR

This error occurs whenever an incoming parity error is detected and/or the GP521 detects that it is not synchronized with the programming unit. This type of error sets a STATUS bit and puts the circuit in unsynchronized mode. The STATUS bit clears after a successful *read/write* operation.

# BAD ADDRESS and / or OPERATION ERROR:

Status register is set when:

- any write operation is attempted while an EEPROM write is in progress

- a write operation is attempted on the ID register

- any operation is attempted on an unused address.

This type of error sets a STATUS bit and sets the parity bit of the returned data stream to the incorrect value. This bit is reset at the conclusion of a acceptable *read* or *write* operation.

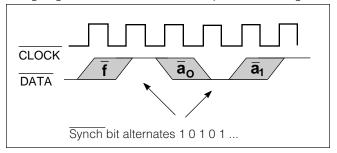

#### COMMUNICATION FORMAT

The dialogue between the programming unit and the GP521 consists of 32 bits being sent to the GP521 which responds by returning 16 bits to the programming unit. A complete dialogue consisting of 48 bits as seen on the DATA line is as follows:

From Program Unit:

From GP521:

$$r_0 1 r_1 0 r_2 1 r_3 0 r_4 1 r_5 0 r_6 1 p_1 0 -$$

The dialogue begins with the bit f and ends with the two bits  $p_{1}$ , 0. The data and synchronization bits must be correct on the falling edge of CLOCK. This relationship is shown in Figure 12.

Fig. 12

The alternating 1's and 0's between information bits are used to check whether the GP521 is synchronized with the prgramming unit. The information bits are defined as:

f (function bit) f = 0 Write data to specified memory address

f = 1 Read data from specified memory address

$a_6a_5a_4a_3a_2a_1a_0$  7 bit address to read/write to  $d_6d_5d_4d_3d_2d_1d_0$  7 bit data to write to memory

p<sub>O</sub> parity bit for information from program unit (odd parity)

r<sub>6</sub>r<sub>5</sub>r<sub>4</sub>r<sub>3</sub>r<sub>2</sub>r<sub>1</sub>r<sub>0</sub>

7 bit data. If f=0, the data will echo the 7 bit data sent by the programming unit. If f=1, the data is read from the memory address.

Parity bit for data sent by GP521 (odd parity)

р,

7

# SYNCHRONIZATION OF THE GP521 WITH PROGRAMMER

The synchronization of the program with the GP521 is done using a code in the data stream which cannot occur during a correct dialogue. The GP521 looks for the following data sequence in the data stream:

where the final synchronization bit is a low. The next bit following the 4 bit synch code is assumed to be part of a valid dialogue. Once the GP521 is synchronized with the program unit, it is possible to perform a continuous sequence of dialogues without having to re-synchronize unless transmission errors occur. It is also possible to pause and continue the transmission provided the proper relationship between CLOCK and DATA is maintained.

To guarantee that the circuit synchronizes properly, the internal shift registers should be cleared by preceding the synch code with a string of bits containing a synch error.

An example of the data sequence that guarantees a correctly synchronized circuit is:

<del>DATA</del> = 11111010

#### **DEFINITIONS**

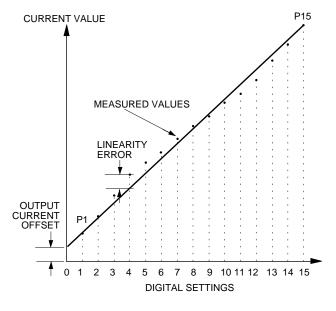

#### LINEARITY ERROR

Linearity error is defined as the difference between the actual current value for a given digital input setting and the current value indicated by the straight line through point  $P_1$  and  $P_{15}$ .

The point  $P_1$  is the current at the setting 1 (0001) of the digital input. (Figure 13)

The point P<sub>15</sub> is the current at the setting 15 (1111) of the digital input (Figure 13)

The current at set 0(0000) of the digital input is left out of the linearity error definition. This point on the characteristic is not correlated to other points (there is no current commutation through the current sink at set 0000).

Fig. 13 PCS Current vs Digital Setting

#### OUTPUT CURRENT OFFSET FOR SETTING 0

The current value determined by the extrapolation of the straight line (defined by the linearity error definition) at setting 0 (0000) of the digital input (Figure 13) is defined as the ouput current offset.

#### **OUTPUT LEAKAGE CURRENT**

Maximum sink current of the control output at setting 0 of the digital input is defined as output leakage current.

#### **EARLY VOLTAGE**

The early voltage is defined by the following equation:

$$= 0.5 - \frac{I_{0.5} (0.5 - 0.7)}{(I_{0.5} - I_{0.7})}$$

where

V<sub>a</sub> - Early Voltage

$I_{0.5}$  - sink output current at bias voltage  $V_{PCS}$  = 0.5 V

$I_{0.7}$  - sink output current at bias voltage  $V_{PCS}$  = 0.7 V

### **DOCUMENT IDENTIFICATION: DATA SHEET**

The product is in production. Gennum reserves the right to make changes at any time to improve reliability, function or design, in order to provide the best product possible.

**REVISION NOTES:**

Updated to Data sheet