### **Features**

- 4.5V-5.5V operation

- · CMOS SRAM for optimum speed and power

- Low active power (165 mW max.)

- Low standby power (L Version)—(110 μW max)

- 2V data retention (L Version)

- JEDEC-compatible pinout

- 32-pin, 0.6-inch-wide DIP package

- TTL-compatible inputs and outputs

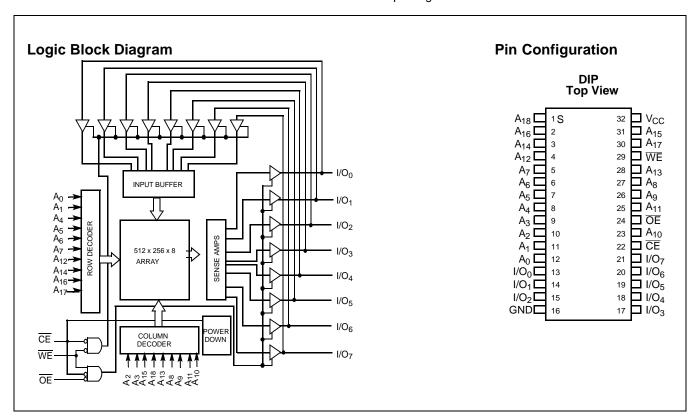

### **Functional Description**

The CYM1465A is a high-performance CMOS static RAM organized as 512K words by 8 bits. Easy memory expansion is provided by an active LOW chip enable (CE), an active LOW Output Enable (OE), and three-state drivers. This device has

# 512K x 8 PDIP Static RAM

an automatic power-down feature that reduces power consumption by more than 99% when deselected.

Writing to the SRAM is accomplished when the chip select (CS) and write enable (WE) inputs are both LOW. Data on the eight input/output pins (I/O<sub>0</sub> through I/O<sub>7</sub>) of the device is then written into the memory location specified on the address pins (A<sub>0</sub> through A<sub>18</sub>). Reading from the device is accomplished by taking chip select (CE) and output enable (OE) LOW while write enable (WE) remains inactive or HIGH. Under these conditions, the contents of the memory location specified on the address pins (A<sub>0</sub> through A<sub>18</sub>) will appear on the eight appropriate data input/output pins (I/O<sub>0</sub> through I/O<sub>7</sub>). The eight input/output pins (I/O0 through I/O7) are placed in a high impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), or during a write operation (CE LOW, and WE LOW).

The CYM1465A is available in a 32-pin 600-mil wide body PDIP package.

### **Selection Guide**

|                                | CYM1465A-70 | CYM1465A-85 |

|--------------------------------|-------------|-------------|

| Maximum Access Time (ns)       | 70          | 85          |

| Maximum Operating Current (mA) | 20          | 20          |

| Maximum Standby Current (μA)   | 20          | 20          |

### **Maximum Ratings**

(Above which the useful life may be impaired.)

Storage Temperature ......-55°C to +150°C

Ambient Temperature with

Power Applied .....-10°C to +85°C

Supply Voltage to Ground Potential .....-0.5V to +7.0V

DC Voltage Applied to Outputs

in High Z State ...... -0.5V to +7.0V

### DC Input Voltage .....-0.5V to +7.0V

## **Operating Range**

| Range      | Ambient<br>Temperature | v <sub>cc</sub> |

|------------|------------------------|-----------------|

| Commercial | 0°C to +70°C           | 5V ± 10%        |

| Industrial | –40°C to +85°C         | 5V ± 10%        |

### **Electrical Characteristics** Over the Operating Range

|                  |                                          |                                                                                               | CYM1465A |                       |      |

|------------------|------------------------------------------|-----------------------------------------------------------------------------------------------|----------|-----------------------|------|

| Parameter        | Description                              | Test Conditions                                                                               | Min.     | Max.                  | Unit |

| V <sub>OH</sub>  | Output HIGH Voltage                      | V <sub>CC</sub> = Min., I <sub>OH</sub> = -1.0 mA                                             | 2.4      |                       | V    |

| V <sub>OL</sub>  | Output LOW Voltage                       | V <sub>CC</sub> = Min., I <sub>OL</sub> = 2.1 mA                                              |          | 0.4                   | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                       |                                                                                               | 2.2      | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub>  | Input LOW Voltage                        |                                                                                               | -0.3     | 0.8                   | V    |

| I <sub>IX</sub>  | Input Load Current                       | $GND \le V_I \le V_{CC}$                                                                      | -1       | +1                    | μΑ   |

| I <sub>OZ</sub>  | Output Leakage Current                   | $GND \le V_O \le V_{CC}$ , Output Disabled                                                    | -1       | +1                    | μΑ   |

| I <sub>CC</sub>  | V <sub>CC</sub> Operating Supply Current | $V_{CC} = Max., I_{OUT} = 0 \text{ mA}, \overline{CS} \le V_{IL}$                             |          | 20                    | mA   |

| I <sub>SB1</sub> | Automatic CS Power-Down Current          | Max. $V_{CC}$ , $\overline{CE} \ge V_{IH}$ ,<br>Min. Duty Cycle = 100%                        |          | 1.5                   | mA   |

| I <sub>SB2</sub> | Automatic CS Power-Down Current          | Max. $V_{CC}$ , $\overline{CE} > V_{CC} - 0.3V$ , $V_{IN} > V_{CC} - 0.3V$ or $V_{IN} < 0.3V$ |          | 20                    | μА   |

## Capacitance<sup>[1]</sup>

| Parameter        | meter Description Test Conditions |                                         | Max. | Unit |

|------------------|-----------------------------------|-----------------------------------------|------|------|

| C <sub>IN</sub>  | Input Capacitance                 | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$ | 8    | pF   |

| C <sub>OUT</sub> | Output Capacitance                | $V_{CC} = 5.0V$                         | 10   | pF   |

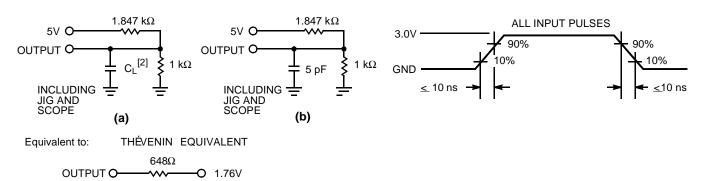

### **AC Test Loads and Waveforms**

### Notes:

- 1. Tested on a sample basis.

- Test conditions assume signal transition times of 10 ns or less, timing reference levels of 1.5V, input levels of 0 to 3.0V, and output loading of the specified I<sub>OL</sub>/I<sub>OH</sub> and 100-pF load capacitance for 85-, 100-, 120-, and 150-ns speeds. C<sub>L</sub> = 30 pF for 70-ns speed.

## Switching Characteristics Over the Operating Range<sup>[2]</sup>

|                            |                                  | CYM14 | 165A-70 | CYM14 |      |      |

|----------------------------|----------------------------------|-------|---------|-------|------|------|

| Parameter                  | Description                      | Min.  | Max.    | Min.  | Max. | Unit |

| READ CYCLE                 |                                  | 1     | •       |       | •    |      |

| t <sub>RC</sub>            | Read Cycle Time                  | 70    |         | 85    |      | ns   |

| t <sub>AA</sub>            | Address to Data Valid            |       | 70      |       | 85   | ns   |

| t <sub>OHA</sub>           | Data Hold from Address Change    | 10    |         | 10    |      | ns   |

| t <sub>ACE</sub>           | CE LOW to Data Valid             |       | 70      |       | 85   | ns   |

| t <sub>DOE</sub>           | OE LOW to Data Valid             |       | 35      |       | 45   | ns   |

| t <sub>LZOE</sub>          | OE LOW to Low Z                  | 5     |         | 5     |      | ns   |

| t <sub>HZOE</sub>          | OE HIGH to High Z <sup>[3]</sup> |       | 25      |       | 30   | ns   |

| t <sub>LZCS</sub>          | CE LOW to Low Z                  | 10    |         | 10    |      | ns   |

| t <sub>HZCS</sub>          | CE HIGH to High Z <sup>[3]</sup> |       | 25      |       | 30   | ns   |

| t <sub>PU</sub>            | CE LOW to Power Down             | 0     |         | 0     |      |      |

| t <sub>PD</sub>            | CE HIGH to Power Down            |       | 70      |       | 85   |      |

| WRITE CYCLE <sup>[4]</sup> |                                  | 1     |         | •     |      |      |

| t <sub>WC</sub>            | Write Cycle Time                 | 70    |         | 85    |      | ns   |

| t <sub>SCE</sub>           | CE LOW to Write End              | 60    |         | 75    |      | ns   |

| t <sub>AW</sub>            | Address Set-Up to Write End      | 60    |         | 75    |      | ns   |

| t <sub>HA</sub>            | Address Hold from Write End      | 0     |         | 0     |      | ns   |

| t <sub>SA</sub>            | Address Set-Up to Write Start    | 0     |         | 0     |      | ns   |

| t <sub>PWE</sub>           | E WE Pulse Width                 |       |         | 65    |      | ns   |

| t <sub>SD</sub>            | Data Set-Up to Write End         | 30    |         | 35    |      | ns   |

| t <sub>HD</sub>            | Data Hold from Write End         | 0     |         | 0     |      | ns   |

| t <sub>LZWE</sub>          | WE HIGH to Low Z                 | 5     |         | 5     |      | ns   |

| t <sub>HZWE</sub>          | WE LOW to High Z <sup>[3]</sup>  |       | 25      |       | 30   | ns   |

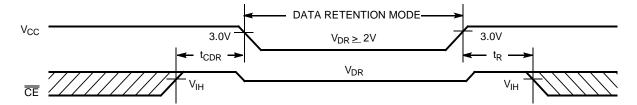

## Data Retention Characteristics Over the Operating Range (L Version Only)

|                                 |                                      |                                                                                                                                                                              | Commercial      |      | Industrial      |      |      |

|---------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|------|

| Parameter                       | Description                          | Test Conditions                                                                                                                                                              | Min.            | Max. | Min.            | Max. | Unit |

| $V_{DR}$                        | V <sub>CC</sub> for Retention Data   |                                                                                                                                                                              | 2               |      | 2               |      | V    |

| I <sub>CCDR3</sub>              | Data Retention Current               | No Input may exceed                                                                                                                                                          |                 | 20   |                 | 20   | μΑ   |

| t <sub>CDR</sub> <sup>[5]</sup> | Chip Deselect to Data Retention Time | Vcc+0.3V<br>Vcc = 3.0V                                                                                                                                                       | 0               |      | 0               |      | ns   |

| t <sub>R</sub> <sup>[5]</sup>   | Operation Recovery Time              | $\begin{array}{l} V_{DR} = 3.0 \text{V}, \\ \overline{\text{CE}} > V_{CC} - 0.3 \text{V}, \\ V_{IN} > V_{CC} - 0.3 \text{V} \text{ or} \\ V_{IN} < 0.3 \text{V} \end{array}$ | t <sub>RC</sub> |      | t <sub>RC</sub> |      | ns   |

- C<sub>L</sub> = 5 pF as in part (b) of AC Test Loads and Waveforms. Transition is measured ±500 mV from steady-state voltage.

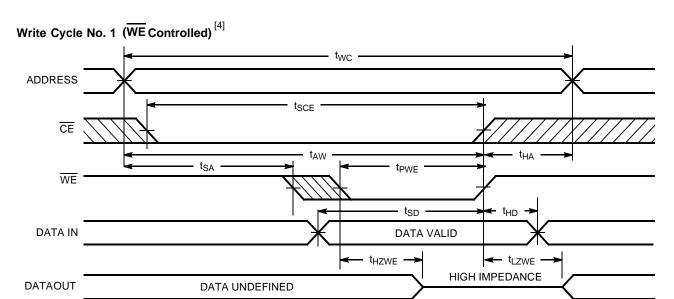

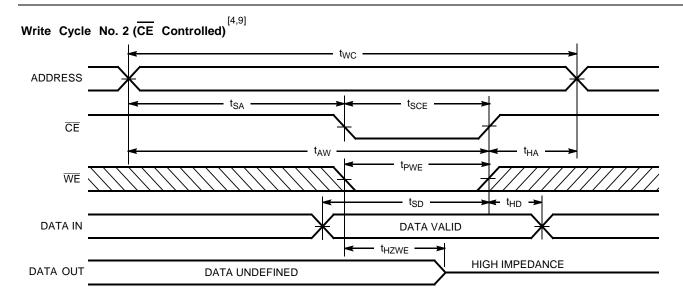

The internal write time of the memory is defined by the overlap of CS LOW and WE LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input set-up and hold timing should be referenced to the rising edge of the signal that terminates the write.

Guaranteed, not tested.

### **Data Retention Waveform**

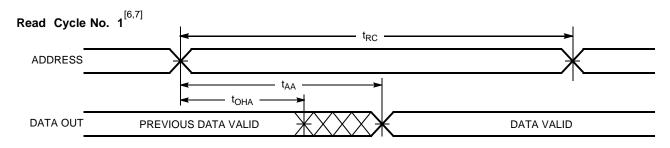

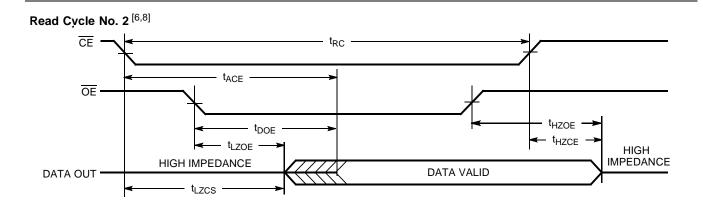

## **Switching Waveforms**

### Notes:

- WE is HIGH for read cycle.

Device is continuously selected, CE= V<sub>|L</sub>.

Address valid prior to or coincident with CE transition LOW.

## Switching Waveforms (continued)

### Note:

9. If  $\overline{\text{CE}}$  goes HIGH simultaneously with  $\overline{\text{WE}}$  HIGH, the output remains in a high-impedance state.

### **Truth Table**

| Inputs |    |    |          |                     |

|--------|----|----|----------|---------------------|

| CE     | WE | OE | Output   | Mode                |

| Н      | Х  | Χ  | High Z   | Deselect/Power-Down |

| L      | Н  | L  | Data Out | Read Word           |

| L      | L  | Χ  | Data In  | Write Word          |

| L      | Н  | Н  | High Z   | Deselect            |

# **Ordering Information**

| Speed (ns) | Ordering Code   | Package<br>Name | Package Type      | Operating<br>Range |

|------------|-----------------|-----------------|-------------------|--------------------|

| 70         | CYM1465ALPD-70C | P19             | 32-Pin DIP Module | Commercial         |

| 70         | CYM1465ALPD-70I | P19             | 32-Pin DIP Module | Industrial         |

| 85         | CYM1465ALPD-85C | P19             | 32-Pin DIP Module | Commercial         |

| 85         | CYM1465ALPD-85I | P19             | 32-Pin DIP Module | Industrial         |

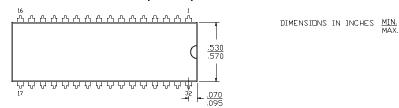

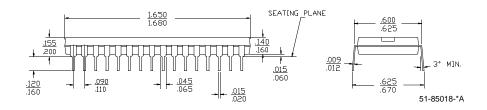

## **Package Diagram**

### 32-Lead (600-Mil) Molded DIP P19

# **Revision History**

| Document Title: CYM1465A 512K x 8 PDIP Static RAM Document Number: 38-05269 |                                                          |         |     |                                                 |  |

|-----------------------------------------------------------------------------|----------------------------------------------------------|---------|-----|-------------------------------------------------|--|

| REV.                                                                        | REV. ECN NO. ISSUE ORIG. OF CHANGE DESCRIPTION OF CHANGE |         |     |                                                 |  |

| **                                                                          | 114171                                                   | 3/19/02 | DSG | Change from Spec number: 38-M-00036 to 38-05269 |  |