# PIC24H Family Overview

High-Performance 16-Bit Microcontrollers

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not

mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE. MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Migratable Memory, MXDEV, MXLAB, PICMASTER, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Linear Active Thermistor, MPASM, MPLIB, MPLINK, MPSIM, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance and WiperLock are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2005, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

QUALITY MANAGEMENT SYSTEM

CERTIFIED BY DNV

ISO/TS 16949:2002

Microchip received ISO/TS-16949:2002 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona and Mountain View, California in October 2003. The Company's quality system processes and procedures are for its PICmicro® 8-bit MCUs, KEELoo® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

## PIC24H High-Performance 16-Bit MCU Overview

## **Operating Range**

- DC 40 MIPS (40 MIPS @ 3.0-3.6V, -40° to +85°C)

- Industrial temperature range (-40° to +85°C)

## **High-Performance DSC CPU**

- · Modified Harvard architecture

- · C compiler optimized instruction set

- · 16-bit wide data path

- 24-bit wide instructions

- Linear program memory addressing up to 4M instruction words

- Linear data memory addressing up to 64 Kbytes

- 74 base instructions: mostly 1 word/1 cycle

- · Sixteen 16-bit general-purpose registers

- · Flexible and powerful addressing modes

- · Software stack

- 16 x 16 integer multiply operations

- 32/16 and 16/16 divide operations

- Single-cycle multiply

- Up to ± 16-bit shifts

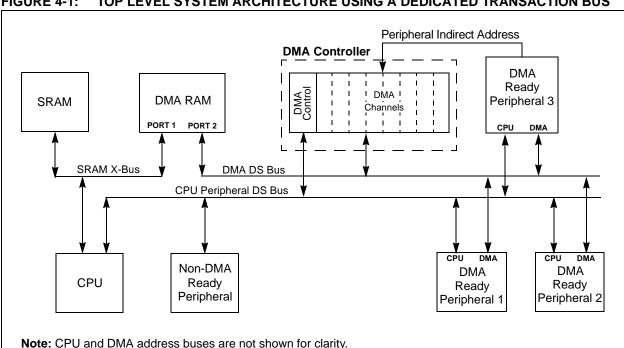

#### **Direct Memory Access (DMA)**

- · 8-channel hardware DMA

- Allows data transfer between RAM and a peripheral while CPU is executing code (no cycle stealing)

- 2 KB of dual-ported DMA buffer area (DMA RAM) to store data transferred via DMA

- Most peripherals support DMA

## **Interrupt Controller**

- · 5-cycle latency

- 118 interrupt vectors

- Up to 61 available interrupt sources, up to 5 external interrupts

- 7 programmable priority levels

- · 5 processor exceptions

### Digital I/O

- Up to 85 programmable digital I/O pins

- · Wake-up/Interrupt-on-Change on up to 24 pins

- · Output pins can drive from 3.0V to 3.6V

- · All digital input pins are 5V tolerant

- 4 mA sink and source on all I/O pins

#### On-Chip Flash and SRAM

- · Flash program memory, up to 256 Kbytes

- Data SRAM (up to 30 Kbytes):

- Includes 2 KB of DMA RAM

#### System Management

- · Flexible clock options:

- External, crystal, resonator, internal RC

- Fully integrated PLL

- Extremely low jitter PLL

- · Power-up timer

- · Oscillator Start-up Timer/Stabilizer

- · Watchdog timer with its own RC oscillator

- · Fail-Safe Clock Monitor

- · Reset by multiple sources

### **Power Management**

- On-chip 2.5V voltage regulator

- Switch between clock sources in real time

- · Idle, Sleep and Doze modes with fast wake-up

### Timers/Capture/Compare/PWM

- Timer/Counters: up to nine 16-bit timers:

- Can pair up to make four 32-bit timers

- 1 timer runs as Real-Time Clock with external 32 kHz oscillator

- Programmable prescaler

- Input Capture (up to 8 channels):

- Capture on up, down or both edges

- 16-bit capture input functions

- 4-deep FIFO on each capture

- Output Compare (up to 8 channels):

- Single or Dual 16-Bit Compare mode

- 16-Bit Glitchless PWM mode

#### **Communication Modules**

- 3-wire SPI™ (up to 2 modules):

- Framing supports I/O interface to simple codecs

- Supports 8-bit and 16-bit data

- Supports all serial clock formats and sampling modes

- 8-word FIFO buffers

- I<sup>2</sup>C<sup>™</sup> (up to 2 modules):

- Full Multi-Master Slave mode support

- 7-bit and 10-bit addressing

- Bus collision detection and arbitration

- Integrated signal conditioning

- Address masking

- · UART (up to 2 modules):

- Interrupt-on-address bit detect

- Wake-up-on-Start bit from Sleep mode

- 4-character TX and RX FIFO buffers

- LIN bus support

- IrDA® encoding and decoding in hardware

- High-Speed Baud mode

- Enhanced CAN 2.0B active (up to 2 modules):

- Up to 8 transmit and up to 32 receive buffers

- 16 receive filters and 3 masks

- Loopback, Listen Only and Listen All Messages modes for diagnostics and bus monitoring

- Wake-up on CAN message

- FIFO mode using DMA

### **Analog-to-Digital Converters (ADC)**

- Up to two 10-bit or 12-bit ADC modules in a device

- 10-bit 2.2 Msps or 12-bit 1 Msps conversion:

- 2, 4 or 8 simultaneous samples

- Up to 32 input channels with auto-scanning

- Conversion start can be manual or synchronized with 1 of 4 trigger sources

- Conversion possible in Sleep mode

- ±1 LSB max integral nonlinearity

- ±1 LSB max differential nonlinearity

## **CMOS Flash Technology**

- Low-power, high-speed Flash technology

- · Fully static design

- 3.3V (+/- 10%) operating voltage

- · Industrial temperature

- · Low-power consumption

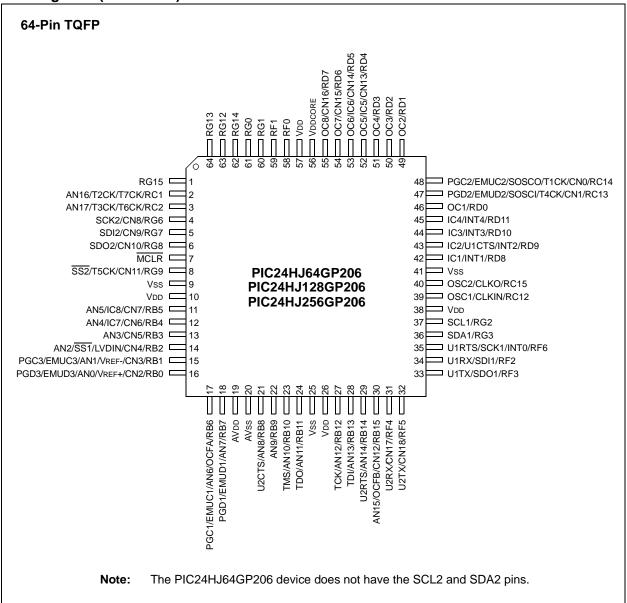

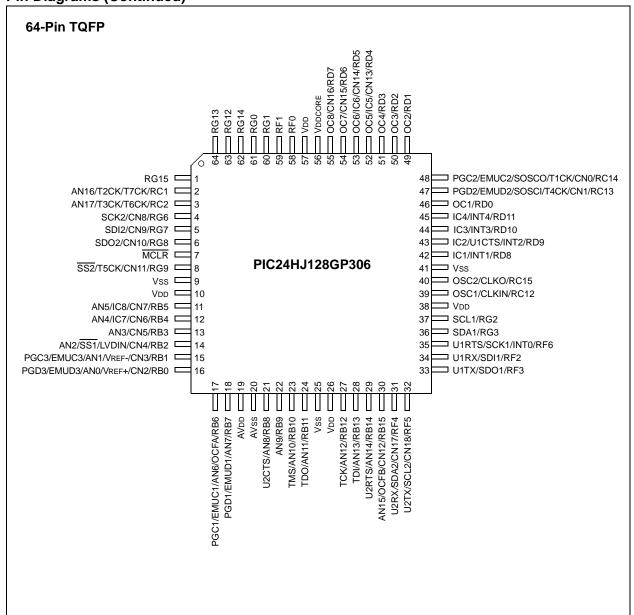

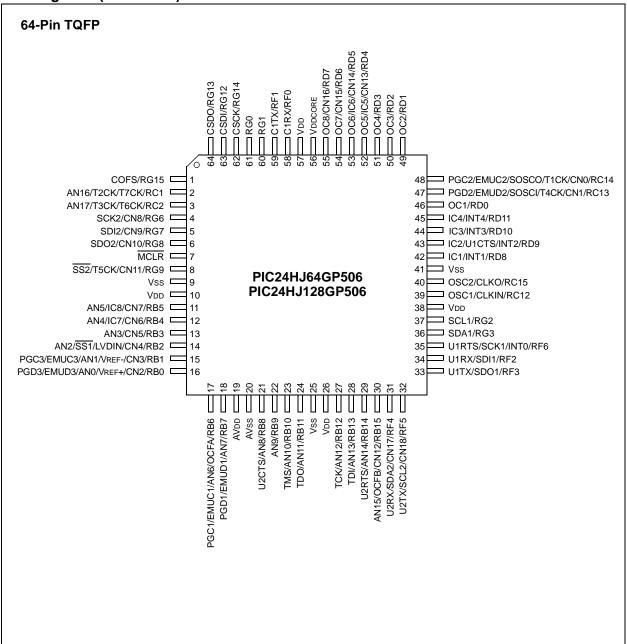

#### Packaging:

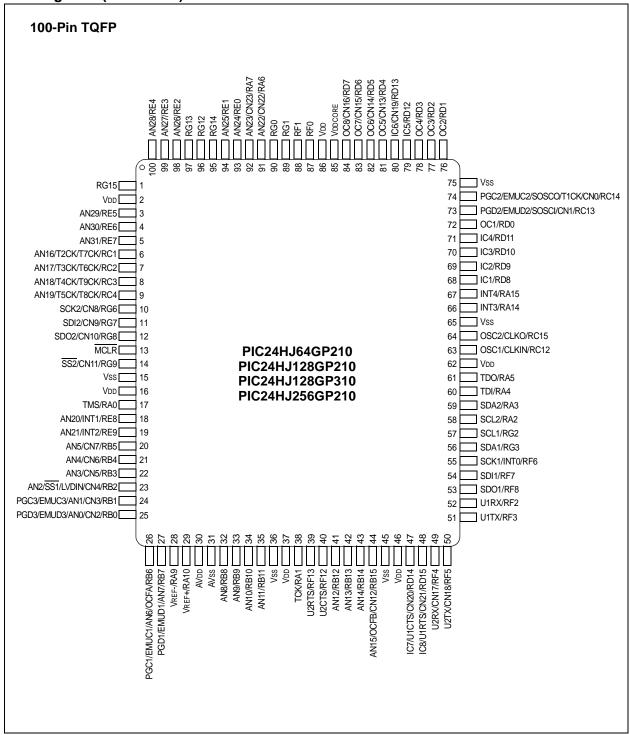

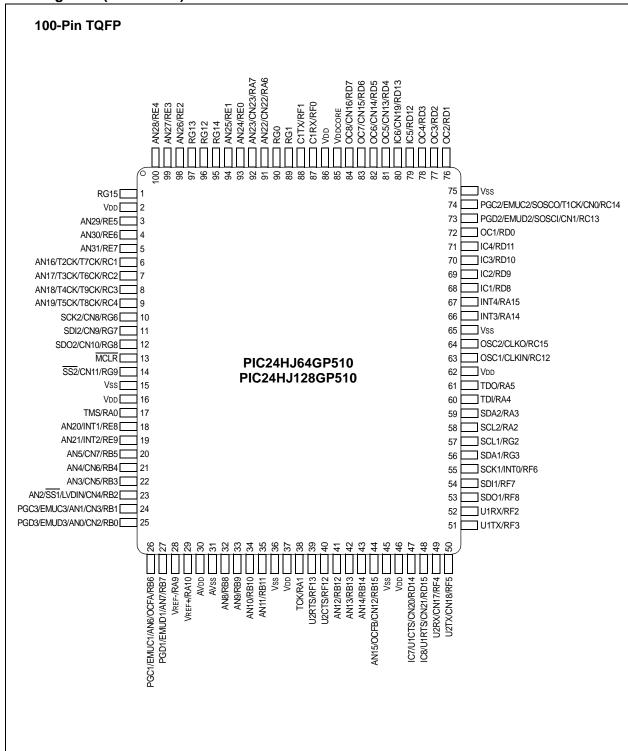

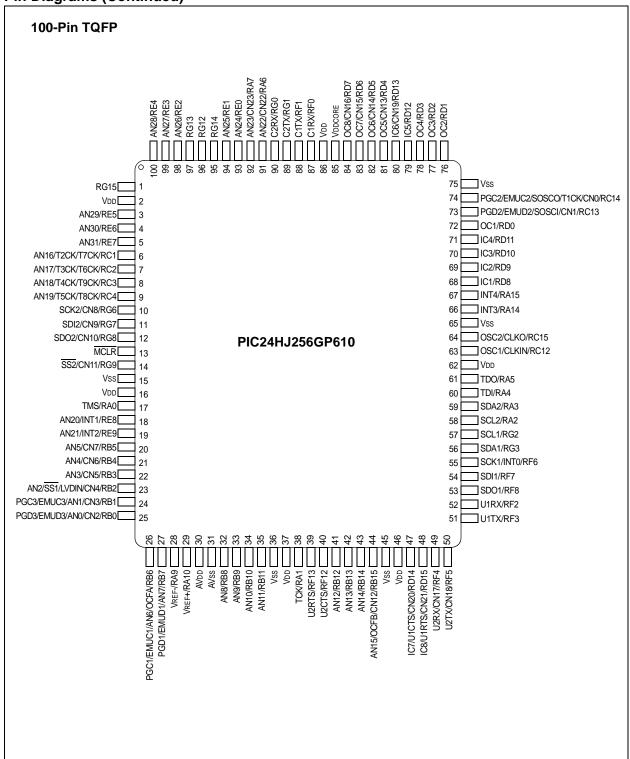

- 100-pin TQFP (14x14x1 mm and 12x12x1 mm)

- 64-pin TQFP (10x10x1 mm)

**Note:** See Table 1-1 for exact peripheral features per device.

## 1.0 PIC24H PRODUCT FAMILIES

## 1.1 General-Purpose Family

The PIC24H General-purpose Family (Table 1-1) is ideal for a wide variety of 16-bit MCU embedded applications. The variants with codec interfaces are well-suited for audio applications.

TABLE 1-1: PIC24H GENERAL-PURPOSE FAMILY VARIANTS

| Device       | Pins | Program Flash<br>Memory (KB) | RAM <sup>(1)</sup><br>(KB) | DMA Channels | Timer 16-bit | Input Capture | Output Compare<br>Std. PWM | Codec<br>Interface | ADC             | UART | мтIdS | I <sup>2</sup> Стм | CAN | I/O Pins (Max) <sup>(2)</sup> | Packages |

|--------------|------|------------------------------|----------------------------|--------------|--------------|---------------|----------------------------|--------------------|-----------------|------|-------|--------------------|-----|-------------------------------|----------|

| 24HJ64GP206  | 64   | 64                           | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2     | 1                  | 0   | 53                            | PT       |

| 24HJ64GP210  | 100  | 64                           | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2     | 2                  | 0   | 85                            | PT       |

| 24HJ64GP506  | 64   | 64                           | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2     | 2                  | 1   | 53                            | PF, PT   |

| 24HJ64GP510  | 100  | 64                           | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2     | 2                  | 1   | 85                            | PT       |

| 24HJ128GP206 | 64   | 128                          | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2     | 2                  | 0   | 53                            | PT       |

| 24HJ128GP210 | 100  | 128                          | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2     | 2                  | 0   | 85                            | PF, PT   |

| 24HJ128GP506 | 64   | 128                          | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2     | 2                  | 1   | 53                            | PT       |

| 24HJ128GP510 | 100  | 128                          | 8                          | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2     | 2                  | 1   | 85                            | PT       |

| 24HJ128GP306 | 64   | 128                          | 16                         | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2     | 2                  | 0   | 53                            | PF, PT   |

| 24HJ128GP310 | 100  | 128                          | 16                         | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2     | 2                  | 0   | 85                            | PT       |

| 24HJ256GP206 | 64   | 256                          | 16                         | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2     | 2                  | 0   | 53                            | PT       |

| 24HJ256GP210 | 100  | 256                          | 16                         | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2     | 2                  | 0   | 85                            | PF, PT   |

| 24HJ256GP610 | 100  | 256                          | 16                         | 8            | 9            | 8             | 8                          | 0                  | 2 ADC,<br>32 ch | 2    | 2     | 2                  | 2   | 85                            | PF, PT   |

Note 1: RAM size is inclusive of 2 KB DMA RAM.

2: Maximum I/O pin count includes pins shared by the peripheral functions.

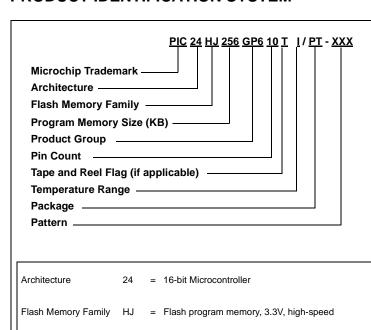

### PRODUCT IDENTIFICATION SYSTEM

Program Memory Size 64

= 64 Kbytes = 128 Kbytes = 256 Kbytes 128 256

Product Group

GP2 = General Purpose family GP3 = General Purpose family GP5 = General Purpose family GP6 = General Purpose family

T = Applicable Blank = Not applicable Tape & Reel

06 10 Pin Count = 64-pin = 100-pin

Temperature Range = -40°C to +85°C (Industrial)

= 10x10 or 12x12 mm TQFP (Thin Quad Flatpack) = 14x14 mm TQFP (Thin Quad Flatpack) Package

Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise) Pattern

ES = Engineering Sample

#### **Examples:**

- dsPIC24HJ64GP610I/PT: General Purpose dsPIC24H, 64 KB program memory, 100-pin, Industrial temp., TQFP package.

- dsPIC24HJ64GP206I/PT-ES: Motor Control dsPIC24H, 64 KB program memory, 64-pin, Industrial temp., TQFP package, Engineering Sample.

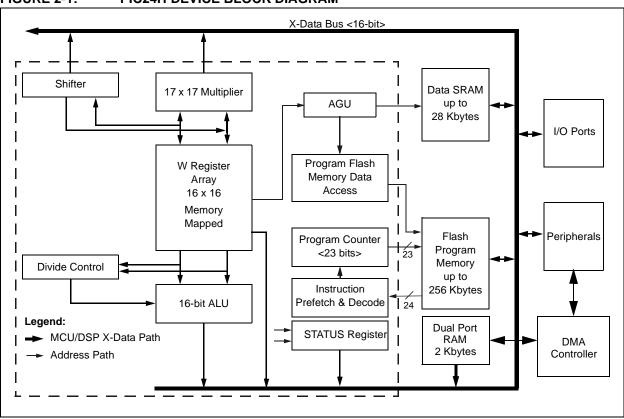

## 2.0 PIC24H DEVICE FAMILY OVERVIEW

The PIC24H device family employs a powerful 16-bit microcontroller (MCU). The resulting CPU functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the PIC24H devices suitable for control applications.

Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use PIC24H devices.

Figure 2-1 shows a sample device block diagram typical of the PIC24H product family.

FIGURE 2-1: PIC24H DEVICE BLOCK DIAGRAM

© 2005 Microchip Technology Inc. Preliminary DS70166A-page 5

#### 3.0 CPU ARCHITECTURE

#### 3.1 Overview

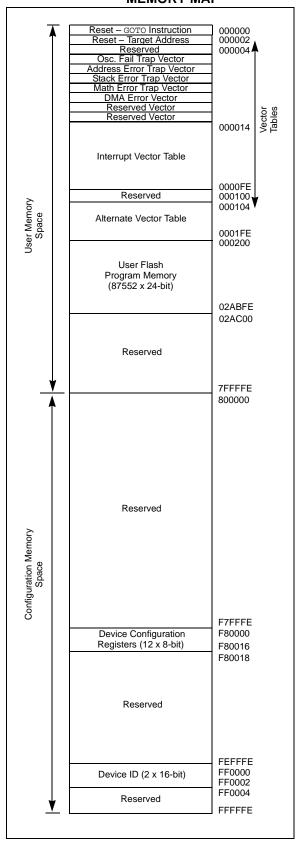

The PIC24H CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M x 24 bits of user program memory space. The actual amount of program memory implemented, as illustrated in Figure 3-1, varies from one device to another. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instruction, which is interruptible at any point.

The PIC24H devices have sixteen 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The PIC24H instruction set includes many addressing modes and is designed for optimum C compiler efficiency.

#### 3.1.1 DATA MEMORY OVERVIEW

The data space can be addressed as 32K words or 64 Kbytes. Reads and writes are performed using an Address Generation Unit (AGU), which accesses the entire memory map as one linear data space.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program-to-data space mapping feature lets any instruction access program space as if it were data space.

The data space includes 2 Kbytes of DMA RAM, which is primarily used for DMA data transfers, but may be used as general-purpose RAM.

FIGURE 3-1: PROGRAM SPACE MEMORY MAP

#### 3.1.2 ADDRESSING MODES OVERVIEW

The CPU supports Inherent (no operand), Relative, Literal, Memory Direct, Register Direct and Register Indirect Addressing modes. Each instruction is associated with a predefined addressing mode group depending upon its functional requirements. As many as 6 addressing modes are supported for each instruction.

For most instructions, the PIC24H is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

#### 3.1.3 SPECIAL MCU FEATURES

The PIC24H features a 17-bit by 17-bit, single-cycle multiplier. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication allows you to perform mixed-sign multiplication.

The PIC24H supports 16/16 and 32/16 divide operations, both fractional and integer. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A 40-bit data shifter is used to perform up to a 16-bit left or right shift in a single cycle.

## 3.1.4 INTERRUPT OVERVIEW

The PIC24H has a vectored exception scheme with up to 5 sources of non-maskable traps and 67 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

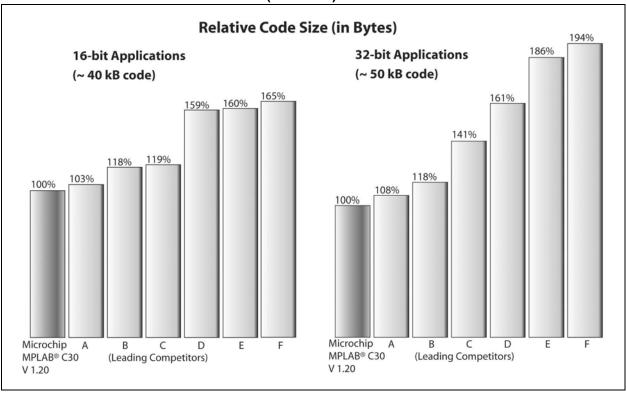

## 3.1.5 FEATURES TO ENHANCE COMPILER EFFICIENCY

The CPU architecture possesses several features that lead to a more efficient (code size and speed) C compiler.

- For most instructions, three-parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

- 2. Instruction addressing modes are extremely flexible to meet compiler needs.

- The working register array consists of 16 x 16-bit registers, each of which can act as data, address or offset registers. One working register (W15) operates as the software Stack Pointer for interrupts and calls.

- Linear indirect access of all data space is possible, plus the memory direct address range is up to 8 Kbytes. This capability, together with the addition of 16-bit direct address MOV-based instructions, has provided a contiguous linear addressing space.

- Linear indirect access of 32K word (64 Kbyte) pages within program space is possible, using any working register via new table read and write instructions.

- 6. Part of data space can be mapped into program space, allowing constant data to be accessed as if it were in data space.

### 3.2 Programmer's Model

The programmer's model, shown in Figure 3-2, consists of 16 x 16-bit working registers (W0 through W15), STATUS register (SR), Data Table Page register (TBLPAG), Program Space Visibility Page register (PSVPAG), REPEAT count register (RCOUNT) and Program Counter (PC). The working registers can act as data, address or offset registers. All registers are memory mapped. W0 is the W register for all instructions that perform file register addressing.

Some of these registers have a shadow register associated with them (see the legend in Figure 3-2). The shadow register is used as a temporary holding register and can transfer its contents to or from its host register upon some event occurring in a single cycle. None of the shadow registers are accessible directly.

When a byte operation is performed on a working register, only the Least Significant Byte (LSB) of the target register is affected. However, a benefit of memory mapped working registers is that both the Least and Most Significant Bytes (MSBs) can be manipulated through byte-wide data memory space accesses.

W15 is the dedicated software Stack Pointer (SP). It is automatically modified by exception processing and subroutine calls and returns. However, W15 can be referenced by any instruction in the same manner as all other W registers. This simplifies the reading, writing and manipulation of the Stack Pointer (e.g., creating stack frames).

W14 has been dedicated as a Stack Frame Pointer, as defined by the LNK and ULNK instructions. However, W14 can be referenced by any instruction in the same manner as all other W registers.

The Stack Pointer always points to the first available free word and grows from lower addresses towards higher addresses. It pre-decrements for stack pops (reads) and post-increments for stack pushes (writes).

FIGURE 3-2: PROGRAMMER'S MODEL 15 0 Legend: W0/WREG PUSH.S Shadow DIV and MUL W1 Result Registers W2 W3 W4 W5 W6 W7 Working Registers W8 W9 W10 W11 W12 W13 W14/Frame Pointer W15\*/Stack Pointer \*W15 and SPLIM not shadowed SPLIM\* Stack Pointer Limit Register **Program Counter** 0 **TBLPAG** Data Table Page Address PSVPAG Program Space Visibility Page Address 15 RCOUNT **REPEAT Loop Counter** 15 CORCON Core Configuration Register DC IPL2 IPL1 IPL0 RA Ν  $\mathsf{OV}$ Ζ С STATUS Register SRL

#### 3.3 Data Address Space

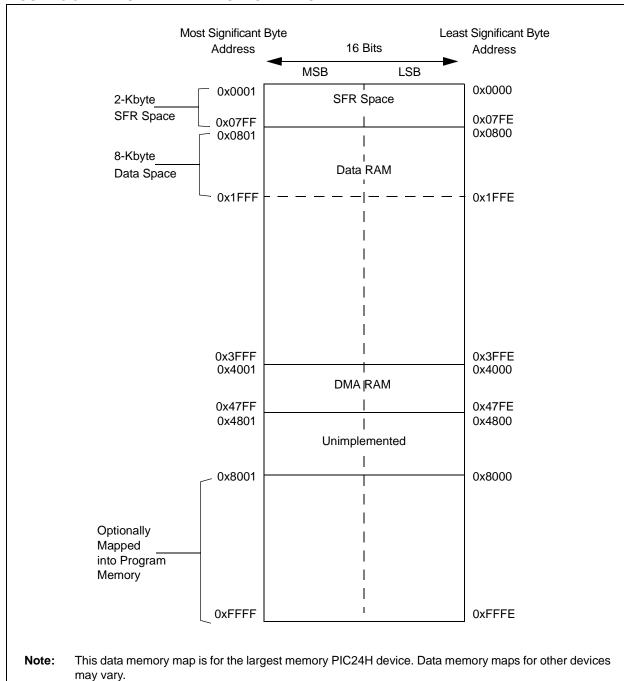

The data space is accessed as one unified linear address range (for MCU instructions). The data space is accessed using the Address Generation Unit (AGU). All Effective Addresses (EAs) are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes or 32K words, though the implemented memory locations vary from one device to another.

#### 3.3.1 DMA RAM

Every PIC24H device contains 2 Kbytes of DMA RAM located at the end of Y data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA Controller module. DMA RAM is utilized by the DMA Controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA.

When the CPU and the DMA Controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

#### 3.3.2 DATA SPACE WIDTH

The core data width is 16 bits. All internal registers are organized as 16-bit wide words. Data space memory is organized in byte addressable, 16-bit wide blocks. Figure 3-3 depicts a sample data space memory map for the PIC24H device with 16 Kbytes of RAM.

#### 3.3.3 DATA ALIGNMENT

To help maintain backward compatibility with PICmicro® MCU devices and improve data space memory usage efficiency, the PIC24H instruction set supports both word and byte operations. Data is aligned in data memory and registers as words, but all data space EAs resolve to bytes. Data byte reads will read the complete word which contains the byte, using the Least Significant bit (LSb) of any EA to determine which byte to select.

As a consequence of this byte accessibility, all Effective Address calculations are internally scaled. For example, the core would recognize that Post-Modified Register Indirect Addressing mode, [Ws++], will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported. Should a misaligned read or write be attempted, a trap will then be executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

FIGURE 3-3: SAMPLE DATA SPACE MEMORY MAP

#### 4.0 **DIRECT MEMORY ACCESS**

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer) and buffers or variables stored in RAM with minimal CPU intervention. The DMA Controller automatically copy entire blocks of data, without the user software having to read or write peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM space.

The DMA Controller features eight identical data transfer channels, each with its own set of control and status registers. The UART, SPI, DCI, Input Capture, Output Compare, ECAN™ technology and ADC modules can utilize DMA. Each DMA channel can be configured to copy data either from buffers stored in DMA RAM to peripheral SFRs or from peripheral SFRs to buffers in DMA RAM.

Each channel supports the following features:

- · Word or byte-sized data transfers

- · Transfers from peripheral to DMA RAM or DMA RAM to peripheral

- · Indirect addressing of DMA RAM locations with or without automatic post-increment

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral

- One-Shot Block Transfers Terminating DMA transfer after one block transfer

- · Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately

- Automatic or manual initiation of block transfers

- · Each channel can select from 32 possible sources of data sources or destinations

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled. Additionally, a DMA error trap is generated in either of the following Fault conditions:

- · DMA RAM data write collision between the CPU and a peripheral

- Peripheral SFR data write collision between the CPU and the DMA Controller

FIGURE 4-1: TOP LEVEL SYSTEM ARCHITECTURE USING A DEDICATED TRANSACTION BUS

### 5.0 EXCEPTION PROCESSING

The PIC24H has four processor exceptions (traps) and up to 61 sources of interrupts, which must be arbitrated based on a priority scheme.

The processor core is responsible for reading the Interrupt Vector Table (IVT) and transferring the address contained in the interrupt vector to the Program Counter.

The Interrupt Vector Table (IVT) and Alternate Interrupt Vector Table (AIVT) are placed near the beginning of program memory (0x000004) for ease of debugging.

The interrupt controller hardware pre-processes the interrupts before they are presented to the CPU. The interrupts and traps are enabled, prioritized and controlled using centralized Special Function Registers.

Each individual interrupt source has its own vector address and can be individually enabled and prioritized in user software. Each interrupt source also has its own status flag. This independent control and monitoring of the interrupt eliminates the need to poll various status flags to determine the interrupt source

Table 5-1 contains information about the interrupt vector.

Certain interrupts have specialized control bits for features like edge or level triggered interrupts, interrupton-change, etc. Control of these features remains within the peripheral module, which generates the interrupt.

The special DISI instruction can be used to disable the processing of interrupts of priorities 6 and lower for a certain number of instruction cycles, during which the DISI bit remains set.

TABLE 5-1: INTERRUPT VECTORS

| IABLE 3-1.       | INTERROFT VECTORS |              |                               |  |  |

|------------------|-------------------|--------------|-------------------------------|--|--|

| Vector<br>Number | IVT Address       | AIVT Address | Interrupt Source              |  |  |

| 8                | 0x000014          | 0x000114     | INT0 – External Interrupt 0   |  |  |

| 9                | 0x000016          | 0x000116     | IC1 – Input Compare 1         |  |  |

| 10               | 0x000018          | 0x000118     | OC1 – Output Compare 1        |  |  |

| 11               | 0x00001A          | 0x00011A     | T1 – Timer1                   |  |  |

| 12               | 0x00001C          | 0x00011C     | DMA0 – DMA Channel 0          |  |  |

| 13               | 0x00001E          | 0x00011E     | IC2 – Input Capture 2         |  |  |

| 14               | 0x000020          | 0x000120     | OC2 – Output Compare 2        |  |  |

| 15               | 0x000022          | 0x000122     | T2 – Timer2                   |  |  |

| 16               | 0x000024          | 0x000124     | T3 – Timer3                   |  |  |

| 17               | 0x000026          | 0x000126     | SPI1E – SPI1 Error            |  |  |

| 18               | 0x000028          | 0x000128     | SPI1 – SPI1 Transfer Done     |  |  |

| 19               | 0x00002A          | 0x00012A     | U1RX – UART1 Receiver         |  |  |

| 20               | 0x00002C          | 0x00012C     | U1TX – UART1 Transmitter      |  |  |

| 21               | 0x00002E          | 0x00012E     | ADC1 – ADC 1                  |  |  |

| 22               | 0x000030          | 0x000130     | DMA1 – DMA Channel 1          |  |  |

| 23               | 0x000032          | 0x000132     | Reserved                      |  |  |

| 24               | 0x000034          | 0x000134     | I2C1S – I2C1 Slave Event      |  |  |

| 25               | 0x000036          | 0x000136     | I2C1M – I2C1 Master Event     |  |  |

| 26               | 0x000038          | 0x000138     | Reserved                      |  |  |

| 27               | 0x00003A          | 0x00013A     | Change Notification Interrupt |  |  |

| 28               | 0x00003C          | 0x00013C     | INT1 – External Interrupt 1   |  |  |

| 29               | 0x00003E          | 0x00013E     | ADC2 – ADC 2                  |  |  |

| 30               | 0x000040          | 0x000140     | IC7 – Input Capture 7         |  |  |

| 31               | 0x000042          | 0x000142     | IC8 – Input Capture 8         |  |  |

| 32               | 0x000044          | 0x000144     | DMA2 – DMA Channel 2          |  |  |

| 33               | 0x000046          | 0x000146     | OC3 – Output Compare 3        |  |  |

| 34               | 0x000048          | 0x000148     | OC4 – Output Compare 4        |  |  |

| 35               | 0x00004A          | 0x00014A     | T4 – Timer4                   |  |  |

| 36               | 0x00004C          | 0x00014C     | T5 – Timer5                   |  |  |

| 37               | 0x00004E          | 0x00014E     | INT2 – External Interrupt 2   |  |  |

| 38               | 0x000050          | 0x000150     | U2RX – UART2 Receiver         |  |  |

| 39               | 0x000052          | 0x000152     | U2TX – UART2 Transmitter      |  |  |

TABLE 5-1: INTERRUPT VECTORS (CONTINUED)

| IABLE 3-1.       |                   | CTOKS (CONTINUI   |                                    |

|------------------|-------------------|-------------------|------------------------------------|

| Vector<br>Number | IVT Address       | AIVT Address      | Interrupt Source                   |

| 40               | 0x000054          | 0x000154          | SPI2E – SPI2 Error                 |

| 41               | 0x000056          | 0x000156          | SPI1 – SPI1 Transfer Done          |

| 42               | 0x000058          | 0x000158          | C1RX – ECAN1 Receive Data Ready    |

| 43               | 0x00005A          | 0x00015A          | C1 – ECAN1 Event                   |

| 44               | 0x00005C          | 0x00015C          | DMA3 – DMA Channel 3               |

| 45               | 0x00005E          | 0x00015E          | IC3 – Input Capture 3              |

| 46               | 0x000060          | 0x000160          | IC4 – Input Capture 4              |

| 47               | 0x000062          | 0x000162          | IC5 – Input Capture 5              |

| 48               | 0x000064          | 0x000164          | IC6 – Input Capture 6              |

| 49               | 0x000066          | 0x000166          | OC5 – Output Compare 5             |

| 50               | 0x000068          | 0x000168          | OC6 – Output Compare 6             |

| 51               | 0x00006A          | 0x00016A          | OC7 – Output Compare 7             |

| 52               | 0x00006C          | 0x00016C          | OC8 – Output Compare 8             |

| 53               | 0x00006E          | 0x00016E          | Reserved                           |

| 54               | 0x000070          | 0x000170          | DMA4 – DMA Channel 4               |

| 55               | 0x000072          | 0x000172          | T6 – Timer6                        |

| 56               | 0x000074          | 0x000174          | T7 – Timer7                        |

| 57               | 0x000076          | 0x000176          | I2C2S – I2C2 Slave Event           |

| 58               | 0x000078          | 0x000178          | I2C2M – I2C2 Master Event          |

| 59               | 0x00007A          | 0x00017A          | T8 – Timer8                        |

| 60               | 0x00007C          | 0x00017C          | T9 – Timer9                        |

| 61               | 0x00007E          | 0x00017E          | INT3 – External Interrupt 3        |

| 62               | 0x000080          | 0x000180          | INT4 – External Interrupt 4        |

| 63               | 0x000082          | 0x000182          | C2RX – ECAN2 Receive Data Ready    |

| 64               | 0x000084          | 0x000184          | C2 – ECAN2 Event                   |

| 65-68            | 0x000086-0x00008C | 0x000186-0x00018C | Reserved                           |

| 69               | 0x00008E          | 0x00018E          | DMA5 – DMA Channel 5               |

| 70-72            | 0x000090-0x000094 | 0x000190-0x000194 | Reserved                           |

| 73               | 0x000096          | 0x000196          | U1E – UART1 Error                  |

| 74               | 0x000098          | 0x000198          | U2E – UART2 Error                  |

| 75               | 0x00009A          | 0x00019A          | Reserved                           |

| 76               | 0x00009C          | 0x00019C          | DMA6 – DMA Channel 6               |

| 77               | 0x00009E          | 0x00019E          | DMA7 – DMA Channel 7               |

| 78               | 0x0000A0          | 0x0001A0          | C1TX – ECAN1 Transmit Data Request |

| 79               | 0x0000A2          | 0x0001A2          | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 0x0000A4-         | 0x0001A4-         | Reserved                           |

|                  | 0x0000FE          | 0x0001FE          |                                    |

#### 5.1 Interrupt Priority

Each interrupt source can be user-assigned to one of 8 priority levels, 0 through 7. Levels 7 and 1 represent the highest and lowest maskable priorities, respectively. A priority level of 0 disables the interrupt.

Since more than one interrupt request source may be assigned to a user-specified priority level, a means is provided to assign priority within a given level. This method is called "Natural Order Priority".

The Natural Order Priority of an interrupt is numerically identical to its vector number. The Natural Order Priority scheme has 0 as the highest priority and 74 as the lowest priority.

The ability for the user to assign every interrupt to one of eight priority levels implies that the user can assign a very high overall priority level to an interrupt with a low Natural Order Priority, thereby providing much flexibility in designing applications that use a large number of peripherals.

#### 5.2 Interrupt Nesting

Interrupts, by default, are nestable. Any ISR that is in progress may be interrupted by another source of interrupt with a higher user-assigned priority level. Interrupt nesting may be optionally disabled by setting the NSTDIS control bit (INTCON1<15>). When the NSTDIS control bit is set, all interrupts in progress will force the CPU priority to level 7 by setting IPL<2:0> = 111. This action will effectively mask all other sources of interrupt until a RETFIE instruction is executed. When interrupt nesting is disabled, the user-assigned interrupt priority levels will have no effect, except to resolve conflicts between simultaneous pending interrupts.

The IPL<2:0> bits become read-only when interrupt nesting is disabled. This prevents the user software from setting IPL<2:0> to a lower value, which would effectively re-enable interrupt nesting.

5.3 Traps

Traps can be considered as non-maskable, nestable interrupts that adhere to a fixed priority structure. Traps are intended to provide the user a means to correct erroneous operation during debug and when operating within the application. If the user does not intend to take corrective action in the event of a trap error condition, these vectors must be loaded with the address of a software routine that will reset the device. Otherwise, the trap vector is programmed with the address of a service routine that will correct the trap condition.

The PIC24H has five implemented sources of non-maskable traps:

- Oscillator Failure Trap

- · Address Error Trap

- Stack Error Trap

- · Math Error Trap

- · DMA Error Trap

Many of these trap conditions can only be detected when they happen. Consequently, the instruction that caused the trap is allowed to complete before exception processing begins. Therefore, the user may have to correct the action of the instruction that caused the trap.

Each trap source has a fixed priority as defined by its position in the IVT. An oscillator failure trap has the highest priority, while an arithmetic error trap has the lowest priority.

Table 5-2 contains information about the trap vector.

## 5.4 Generating a Software Interrupt

Any available interrupt can be manually generated by user software (even if the corresponding peripheral is disabled), simply by enabling the interrupt and then setting the interrupt flag bit when required.

TABLE 5-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000084     | Reserved           |

| 1             | 0x000006    | 0x000086     | Oscillator Failure |

| 2             | 0x000008    | 0x000088     | Address Error      |

| 3             | 0x00000A    | 0x00008A     | Stack Error        |

| 4             | 0x00000C    | 0x00008C     | Math Error         |

| 5             | 0x00000E    | 0x00008E     | DMA Error Trap     |

| 6             | 0x000010    | 0x000090     | Reserved           |

| 7             | 0x000012    | 0x000092     | Reserved           |

### 6.0 SYSTEM INTEGRATION

System management services provided by the PIC24H device family include:

- · Control of clock options and oscillators

- · Power-on Reset

- · Oscillator Start-up Timer/Stabilizer

- · Watchdog Timer with RC oscillator

- · Fail-Safe Clock Monitor

- · Reset by multiple sources

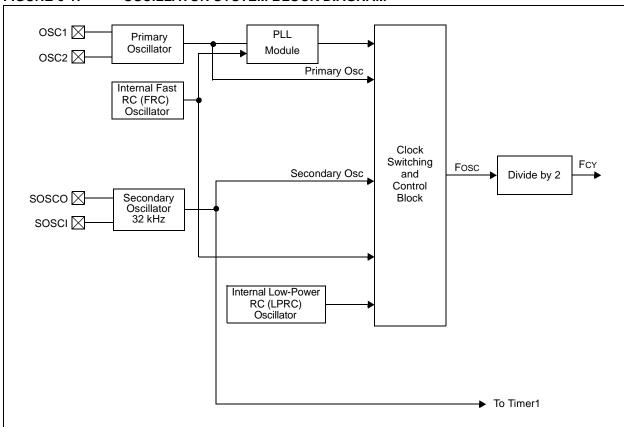

## 6.1 Clock Options and Oscillators

There are 7 clock options provided by the PIC24H:

- · FRC Oscillator

- · FRC Oscillator with PLL

- · Primary (XT, HS or EC) Oscillator

- · Primary Oscillator with PLL

- · Secondary (LP) Oscillator

- LPRC Oscillator

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can specify a factor by which this clock frequency is scaled.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- 3. EC (External Clock): External clock signal in the range of 0.8 MHz to 64 MHz. The external clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscillator runs at a nominal frequency of 32.768 kHz. Another scaled reference clock is used by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase Locked Loop (PLL) to provide a wide range of output frequencies for device operation. The input to the PLL can be in the range of 1.6 MHz to 16 MHz, and the PLL Phase Detector Input Divider, PLL Multiplier Ratio and PLL Voltage Controlled Oscillator (VCO) can be individually configured by user software to generate output frequencies in the range of 25 MHz to 160 MHz.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) is divided by 2 to generate the device instruction clock (Fcy). Fcy

defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24H architecture.

The PIC24H oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- · Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- A Clock Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified block diagram of the oscillator system is shown in Figure 6-1.

## FIGURE 6-1: OSCILLATOR SYSTEM BLOCK DIAGRAM

### 6.2 Power-on Reset (POR)

When a supply voltage is applied to the device, a Power-on Reset (POR) is generated. A new Power-on Reset event is generated if the supply voltage falls below the device threshold voltage (VPOR). An internal POR pulse is generated when the rising supply voltage crosses the POR circuit threshold voltage.

## 6.3 Oscillator Start-up Timer/Stabilizer (OST)

An Oscillator Start-up Timer (OST) is included to ensure that a crystal oscillator (or ceramic resonator) has started and stabilized. The OST is a simple, 10-bit counter that counts 1024 Tosc cycles before releasing the oscillator clock to the rest of the system. The timeout period is designated as Tost. The Tost time is involved every time the oscillator has to restart (i.e., on Power-on Reset and wake-up from Sleep). The Oscillator Start-up Timer is applied to the LP oscillator, XT and HS modes (upon wake-up from Sleep, POR and Brown-out Reset (BOR)) for the primary oscillator.

### 6.4 Watchdog Timer (WDT)

The primary function of the Watchdog Timer (WDT) is to reset the processor in the event of a software malfunction. The WDT is a free-running timer that runs off the on-chip LPRC oscillator, requiring no external component. The WDT continues to operate even if the main processor clock (e.g., the crystal oscillator) fails.

The Watchdog Timer can be "Enabled" or "Disabled" either through a Configuration bit (FWDTEN) in the Configuration register, or through an SFR bit (SWDTEN).

Any device programmer capable of programming dsPIC® DSC devices (such as Microchip's MPLAB® PM3 Programmer) allows programming of this and other Configuration bits to the desired state. If enabled, the WDT increments until it overflows or "times out". A WDT time-out forces a device Reset (except during Sleep).

## 6.5 Fail-Safe Clock Monitor (FSCM)

The Fail-Safe Clock Monitor (FSCM) allows the device to continue to operate even in the event of an oscillator failure. The FSCM function is enabled by programming. If the FSCM function is enabled, the LPRC internal oscillator runs at all times (except during Sleep mode) and is not subject to control by the Watchdog Timer.

In the event of an oscillator failure, the FSCM generates a clock failure trap event and switches the system clock over to the FRC oscillator. The application program then can either attempt to restart the oscillator, or execute a controlled shutdown. The trap can be treated as a warm Reset by simply loading the Reset address into the oscillator fail trap vector.

## 6.6 Reset System

The Reset system combines all Reset sources and controls the device Master Reset signal.

Device Reset sources include:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- SWR: RESET Instruction

- EXTR: MCLR Reset

- WDTR: Watchdog Timer Time-out Reset

- TRAPR: Trap Conflict

- IOPUWR: Attempted execution of an Illegal Opcode, or Indirect Addressing, using an Uninitialized W register

## 7.0 DEVICE POWER MANAGEMENT

Power management services provided by the PIC24H devices include:

- Real-Time Clock Source Switching

- · Power-Saving Modes

## 7.1 Real-Time Clock Source Switching

Configuration bits determine the clock source upon Power-on Reset (POR) and Brown-out Reset (BOR). Thereafter, the clock source can be changed between permissible clock sources. The OSCCON register controls the clock switching and reflects system clock related status bits. To reduce power consumption, the user can switch to a slower clock source.

### 7.2 Power-Saving Modes

The PIC24H devices have two reduced power modes that can be entered through execution of the PWRSAV instruction.

- Sleep Mode: The CPU, system clock source and any peripherals that operate on the system clock source are disabled. This is the lowest power mode of the device.

- Idle Mode: The CPU is disabled but the system clock source continues to operate. Peripherals continue to operate but can optionally be disabled.

- Doze Mode: The CPU clock is temporarily slowed down relative to the peripheral clock by a user-selectable factor.

These modes provide an effective way to reduce power consumption during periods when the CPU is not in use.

#### 7.2.1 SLEEP MODE

When the device enters Sleep mode:

- System clock source is shut down. If an on-chip oscillator is used, it is turned off.

- Device current consumption is at minimum provided that no I/O pin is sourcing current.

- Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode because the system clock source is disabled.

- LPRC clock continues to run in Sleep mode if the WDT is enabled.

- BOR circuit, if enabled, remains operative during Sleep mode

- WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some peripherals may continue to operate in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, or peripherals that use an external clock input. Any peripheral that is operating on the system clock source is disabled in Sleep mode.

The processor exits (wakes up) from Sleep on one of these events:

- · Any interrupt source that is individually enabled

- · Any form of device Reset

- A WDT time-out

#### 7.2.2 IDLE MODE

When the device enters Idle mode:

- CPU stops executing instructions

- · WDT is automatically cleared

- · System clock source remains active

- Peripheral modules, by default, continue to operate normally from the system clock source

- Peripherals, optionally, can be shut down in Idle mode using their 'stop-in-idle' control bit.

- If the WDT or FSCM is enabled, the LPRC also remains active

The processor wakes from Idle mode on these events:

- · Any interrupt that is individually enabled

- · Any source of device Reset

- · A WDT time-out

Upon wake-up from Idle, the clock is re-applied to the CPU and instruction execution begins immediately starting with the instruction following the PWRSAV instruction, or the first instruction in the Interrupt Service Routine (ISR).

#### 7.2.3 DOZE MODE

The Doze mode provides the user software the ability to temporarily reduce the processor instruction cycle frequency relative to the peripheral frequency. Clock frequency ratios of 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64 and 1:128 are supported.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps bit rate based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module will continue to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

This feature further reduces the power consumption during periods where relatively less CPU activity is required.

When the device is operating in Doze mode, the hardware ensures that there is no loss of synchronization between peripheral events and SFR accesses by the CPU.

#### 8.0 PIC24H PERIPHERALS

The Digital Signal Controller (DSC) family of 16-bit DSC devices provides the integrated functionality of many peripherals. Specific peripheral functions include:

- · Analog-to-Digital Converters (ADC)

- 10-bit High-Speed ADC

- 12-bit High-Resolution ADC

- · General-purpose 16-Bit Timers

- Motor Control PWM module

- · Quadrature Encoder Interface module

- · Input Capture module

- Output Compare/PWM module

- · Data Converter Interface

- Serial Peripheral Interface (SPI™) module

- UART module

- I<sup>2</sup>C<sup>™</sup> module

- Controller Area Network (CAN) module

- I/O pins

### 8.1 Analog-to-Digital Converters

The Analog-to-Digital Converters provide up to 32 analog inputs with both single-ended and differential inputs. These modules offer on-board sample and hold circuitry.

To minimize control loop errors due to finite update times (conversion plus computations), a high-speed low-latency ADC is required.

In addition, several hardware features have been included in the peripheral interface to improve real-time performance in a typical DSP-based application.

- · Result alignment options

- · Automated sampling

- · Automated channel scanning

- Dual port data buffer

- · External conversion start control

The ADC can be configured by the user application in either of the following configurations:

- 10-bit, 1.1 Msps ADC module (2.2 Msps ADC conversion using 2 A/D modules)

- 12-bit, 500 ksps ADC module (1 Msps ADC conversion using 2 A/D modules)

Key features of the ADC module include:

- 10-bit or 12-bit resolution

- Unipolar differential sample/hold amplifiers

- · Up to 32 input channels

- Selectable voltage reference sources (external VREF+ and VREF- pins available)

- ±1 LSB max Differential Nonlinearity (DNL) (3.3V ±10%)

- ±1 LSB max Integral Nonlinearity (INL) (3.3V ±10%)

- Up to 4 on-chip sample and hold amplifiers in each ADC (enables simultaneous sampling of 2, 4 or 8 analog inputs)

- Automated channel scanning

- Single-supply operation: 3.0-3.6V

- · 2.2 Msps or 1 Msps sampling rate at 3.0V

- Ability to convert during CPU Sleep and Idle modes

- Conversion start can be manual or synchronized with 1 of 4 trigger sources (automatic, Timer3 or 5, external interrupt, PWM period match)

- · ADC can use DMA for buffer storage

## 8.2 General-Purpose Timer Modules

The General-Purpose (GP) timer modules provide the time base elements for input capture and output compare/PWM. They can be configured for Real-Time Clock operation as well as various timer/counter modes. The timer modes count pulses of the internal time base, whereas counter modes count external pulses that appear on the timer clock pin.

The PIC24H device supports up to nine 16-bit timers (Timer1 through Timer9). Eight of the 16-bit timers can be configured as four 32-bit timers (Timer2/3, Timer4/5, Timer6/7 and Timer8/9). Each timer has several selectable operating modes.

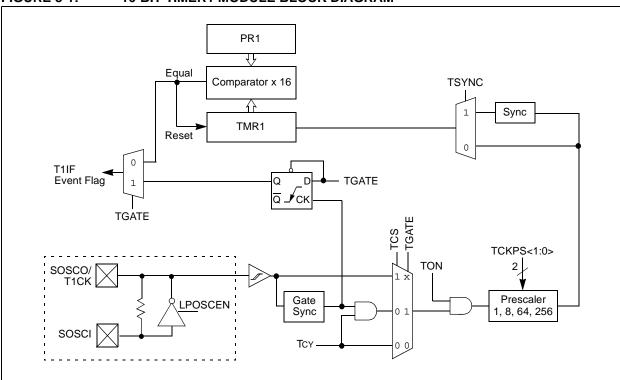

#### 8.2.1 TIMER1

The Timer1 module (Figure 8-1) is a 16-bit timer that can serve as the time counter for an asynchronous Real-Time Clock, or operate as a free-running interval timer/counter. The 16-bit timer has the following modes:

- 16-Bit Timer

- 16-Bit Synchronous Counter

- 16-Bit Asynchronous Counter

Further, the following operational characteristics are supported:

- Timer gated by external pulse

- Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period register match or falling edge of external gate signal

Timer1, when operating in Real-Time Clock (RTC) mode, provides time of day and event time-stamping capabilities. Key operational features of the RTC are:

- · Operation from 32 kHz LP oscillator

- 8-bit prescaler

- Low power

- · Real-Time Clock interrupts

FIGURE 8-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

#### 8.2.2 TIMER2/3

The Timer2/3 module is a 32-bit timer (which can be configured as two 16-bit timers) with selectable operating modes. These timers are used by other peripheral modules, such as:

- Input Capture

- Output Compare/Simple PWM

Timer2/3 has the following modes:

- Two independent 16-bit timers (Timer2 and Timer3) with Timer and Synchronous Counter modes

- Single 32-Bit Timer

- Single 32-Bit Synchronous Counter

Further, the following operational characteristics are supported:

- · ADC conversion start trigger

- 32-bit timer gated by external pulse

- · Selectable prescaler settings

- Timer counter operation during Idle and Sleep modes

- Interrupt on a 32-Bit Period register match

- Timer2/3 can use DMA for buffer storage

#### 8.2.3 TIMER4/5, TIMER6/7, TIMER8/9

The Timer4/5, Timer6/7 and Timer8/9 modules are similar in operation to the Timer2/3 module. Differences include:

- These modules do not support the ADC event trigger feature

- These modules can not be used by other peripheral modules, such as input capture and output compare

#### 8.3 Input Capture Module

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The PIC24H devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected time base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- 3. Prescaler Capture Event modes

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or an external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts.

Input capture channels IC1 and IC2 support DMA data transfers.

#### 8.4 Output Compare/PWM Module

The output compare module features are quite useful in applications that require controlled timing pulses or PWM modulated pulse streams.

The output compare module has the ability to compare the value of a selected time base with the value of one or two compare registers (depending on the operation mode selected). Furthermore, it has the ability to generate a single output pulse, or a repetitive sequence of output pulses, on a compare match event. Like most PIC24H peripherals, it also has the ability to generate interrupts on compare match events.

The PIC24H device may have up to eight output compare channels, designated OC1 through OC8. Refer to the specific device data sheet for the number of channels available in a particular device. All output compare channels are functionally identical.

Each output compare channel can use one of two selectable time bases. The time base is selected using the OCTSEL bit (OCxCON<3>). An 'x' in the pin, register or bit name denotes the specific output compare channel. Refer to the device data sheet for the specific timers that can be used with each output compare channel number.

Each output compare module has the following modes of operation:

- · Single Compare Match mode

- Dual Compare Match mode generating

- Single Output Pulse

- Continuous Output Pulses

- · Simple Pulse-Width Modulation mode

- With Fault Protection Input

- Without Fault Protection Input

Output compare channels, OC1 and OC2, support DMA data transfers.

## 8.5 SPI Module

The Serial Peripheral Interface (SPI) module is a synchronous serial interface for communicating with other peripheral or microcontroller devices such as serial EEPROMs, shift registers, display drivers, ADC, etc. It is compatible with Motorola® SPI and SIOP interfaces.

This SPI module includes all SPI modes. A Frame Synchronization mode is also included for support of voice band codecs.

Four pins make up the serial interface: SDI, Serial Data Input; SDO, Serial Data Output; SCK, Shift Clock Input or Output;  $\overline{SS}$ , Active-Low Slave Select, which also serves as the FSYNC (Frame Synchronization Pulse). A device set up as an SPI master provides the serial communication clock signal on its SCK pin.

A series of 8 or 16 clock pulses (depending on mode) shift out the 8 or 16 bits (depending on whether a byte or word is being transferred) and simultaneously shift in 8 or 16 bits of data from the SDI pin. An interrupt is generated when the transfer is complete.

Slave select synchronization allows selective enabling of SPI slave devices, which is particularly useful when a single master is connected to multiple slaves.

The SPI1 and SPI2 modules support DMA data transfers.

#### 8.6 UART Module

The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, RS-232 and RS-485 interfaces.

The PIC24H devices have one or more UARTs.

The key features of the UART module are:

- · Full-duplex operation with 8 or 9-bit data

- Even, odd or no parity options (for 8-bit data)

- · One or two Stop bits

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates range from up to 10 Mbps and down to 38 Hz at 40 MIPS

- · 4-character deep transmit data buffer

- 4-character deep receive data buffer

- · Parity, framing and buffer overrun error detection

- Full IrDA<sup>®</sup> support, including hardware encoding and decoding of IrDA<sup>®</sup> messages

- · LIN bus support

- Auto wake-up from Sleep or Idle mode on Start bit detect

- Auto-baud detection

- Break character support

- Support for interrupt on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- On transmission of 1 or 4 characters

- On reception of 1, 3 and 4 characters

- · Loopback mode for diagnostics

The UART1 and UART2 modules support DMA data transfers.

## 8.7 I<sup>2</sup>C Module

The Inter-Integrated Circuit (I<sup>2</sup>C) module is a synchronous serial interface, useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, ADC, etc.

The I<sup>2</sup>C module offers full hardware support for both slave and multi-master operations.

The key features of the I<sup>2</sup>C module are:

- I<sup>2</sup>C slave operation supports 7 and 10-bit address

- I<sup>2</sup>C master operation supports 7 and 10-bit address

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (serial clock stretching)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

- · Slew rate control for 100 kHz and 400 kHz bus speeds

In I<sup>2</sup>C mode, pin SCL is clock and pin SDA is data. The module will override the data direction bits for these pins.

## 8.8 Controller Area Network (CAN) Module

The Controller Area Network (CAN) module is a serial interface useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module supports CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. Details of these protocols can be found in the BOSCH CAN specification.

The CAN module features:

- Implementation of the CAN protocol CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- · Data lengths of 0-8 bytes

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote frames

- Up to 32 receive buffers in DMA RAM

- FIFO Buffer mode (up to 32 messages deep)

- 16 full (standard/extended identifier) acceptance filters

- · 3 full acceptance filter masks

- · Up to 8 transmit buffers in DMA RAM

- DMA can be used for transmission and reception

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to timer module for time-stamping and network synchronization

- Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### 8.9 I/O Pins

Some pins for the I/O pin functions are multiplexed with an alternate function for the peripheral features on the device. In general, when a peripheral is enabled, that pin may not be used as a general-purpose I/O pin.

All I/O port pins have three registers directly associated with the operation of the port pin. The Data Direction register determines whether the pin is an input or an output. The Port Data Latch register provides latched output data for the I/O pins. The Port register provides visibility of the logic state of the I/O pins. Reading the Port register provides the I/O pin logic state, while writes to the Port register write the data to the Port Data Latch register.

I/O port pins have latch bits (Port Data Latch register). This register, when read, yields the contents of the I/O latch and when written, modifies the contents of the I/O latch, thus modifying the value driven out on a pin if the corresponding Data Direction register bit is configured for output. This can be used in read-modify-write instructions that allow the user to modify the contents of the Port Data Latch register, regardless of the status of the corresponding pins.

The I/O pins have the following features:

- Schmitt Trigger input

- · CMOS output drivers

- Weak internal pull-up

All I/O pins configured as digital inputs can accept 5V signals. This provides a degree of compatibility with external signals of different voltage levels. However, all digital outputs and analog pins can only generate voltage levels up to 3.6V.

The input change notification module gives PIC24H devices the ability to generate interrupt requests to the processor in response to a change of state on selected input pins. This module is capable of detecting input changes of state, even in Sleep mode, when the clocks are disabled. There are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change of state. Each of the CN pins also has an optional weak pull-up feature.

#### 9.0 PIC24H INSTRUCTION SET

#### 9.1 Introduction

The PIC24H instruction set provides a broad suite of instructions which supports traditional microcontroller applications, and a class of instructions which supports math-intensive applications. Since almost all of the functionality of the PICmicro MCU instruction set has been maintained, this hybrid instruction set allows a friendly migration path for users already familiar with the PICmicro microcontroller.

#### 9.2 Instruction Set Overview

The PIC24H instruction set contains 76 instructions which can be grouped into the ten functional categories shown in Table 9-1. Table 9-2 defines the symbols used in the instruction summary tables, Table 9-3 through Table 9-11. These tables define the syntax, description, storage and execution requirements for each instruction. Storage requirements are represented in 24-bit instruction words and execution requirements are represented in instruction cycles. Most instructions have several different addressing modes and execution flows which require different instruction variants. For instance, there are six unique ADD instructions and each instruction variant has its own instruction encoding.

TABLE 9-1: PIC24H INSTRUCTION GROUPS

| Functional Group          | Summary Table |

|---------------------------|---------------|

| Move Instructions         | Table 9-3     |

| Math Instructions         | Table 9-4     |

| Logic Instructions        | Table 9-5     |

| Rotate/Shift Instructions | Table 9-6     |

| Bit Instructions          | Table 9-7     |

| Compare/Skip Instructions | Table 9-8     |

| Program Flow Instructions | Table 9-9     |

| Shadow/Stack Instructions | Table 9-10    |

| Control Instructions      | Table 9-11    |

#### 9.2.1 MULTI-CYCLE INSTRUCTIONS

As the instruction summary tables show, most instructions execute in a single cycle with the following exceptions:

- Instructions MOV.D, POP.D, PUSH.D, TBLRDH, TBLRDL, TBLWTH and TBLWTL require 2 cycles to execute.

- Instructions DIVF, DIV.S, DIV.U are singlecycle instructions, which should be executed 18 consecutive times as the target REPEAT instruction.

- Instructions that change the Program Counter also require 2 cycles to execute, with the extra cycle executed as a NOP. Skip instructions, which skip over a 2-word instruction, require 3 instruction cycles to execute with 2 cycles executed as a NOP.

- The RETFIE, RETLW and RETURN are special cases of instructions that change the Program Counter. These execute in 3 cycles unless an exception is pending, and then they execute in 2 cycles.

**Note:** Instructions that access program memory as data, using Program Space Visibility, incur some cycle count overhead.

#### 9.2.2 MULTI-WORD INSTRUCTIONS

As the instruction summary tables show, almost all instructions consume one instruction word (24 bits), with the exception of the CALL and GOTO instructions, which are flow instructions listed in Table 9-9. These instructions require two words of memory because their opcodes embed large literal operands.

TABLE 9-2: SYMBOLS USED IN SUMMARY TABLES

| Symbol | Description                                                      |

|--------|------------------------------------------------------------------|

| #      | Literal operand designation                                      |

| bit4   | 4-bit wide bit position (0:15)                                   |

| Expr   | Absolute address, label or expression (resolved by the linker)   |

| f      | File register address                                            |

| lit1   | 1-bit literal (0:1)                                              |

| lit4   | 4-bit literal (0:15)                                             |

| lit5   | 5-bit literal (0:31)                                             |

| lit8   | 8-bit literal (0:255)                                            |

| lit10  | 10-bit literal (0:255 for Byte mode, 0:1023 for Word mode)       |

| lit14  | 14-bit literal (0:16383)                                         |

| lit16  | 16-bit literal (0:65535)                                         |

| lit23  | 23-bit literal (0:8388607)                                       |

| Slit4  | Signed 4-bit literal (-8:7)                                      |

| Slit6  | Signed 6-bit literal (-16:16)                                    |

| Slit10 | Signed 10-bit literal (-512:511)                                 |

| Slit16 | Signed 16-bit literal (-32768:32767)                             |

| TOS    | Top-of-Stack                                                     |

| Wb     | Base working register                                            |

| Wd     | Destination working register (direct and indirect addressing)    |

| Wm, Wn | Working register divide pair (dividend, divisor)                 |

| Wm*Wm  | Working register multiplier pair (same source register)          |

| Wm*Wn  | Working register multiplier pair (different source registers)    |

| Wn     | Both source and destination working register (direct addressing) |

| Wnd    | Destination working register (direct addressing)                 |

| Wns    | Source working register (direct addressing)                      |

| WREG   | Default working register                                         |

| Ws     | Source working register (direct and indirect addressing)         |

TABLE 9-3: MOVE INSTRUCTIONS

| Assembly | Syntax           | Description                             | Words | Cycles |

|----------|------------------|-----------------------------------------|-------|--------|

| EXCH     | Wns,Wnd          | Swap Wns and Wnd                        | 1     | 1      |

| MOV      | f {,WREG}        | Move f to destination                   | 1     | 1      |

| MOV      | WREG, f          | Move WREG to f                          | 1     | 1      |

| MOV      | f,Wnd            | Move f to Wnd                           | 1     | 1      |

| MOV      | Wns,f            | Move Wns to f                           | 1     | 1      |

| MOV.b    | #lit8,Wnd        | Move 8-bit literal to Wnd               | 1     | 1      |

| MOV      | #lit16,Wnd       | Move 16-bit literal to Wnd              | 1     | 1      |

| MOV      | [Ws+Slit10],Wnd  | Move [Ws + signed 10-bit offset] to Wnd | 1     | 1      |

| MOV      | Wns, [Wd+Slit10] | Move Wns to [Wd + signed 10-bit offset] | 1     | 1      |

| MOV      | Ws,Wd            | Move Ws to Wd                           | 1     | 1      |

| MOV.D    | Ws,Wnd           | Move double Ws to Wnd:Wnd + 1           | 1     | 2      |

| MOV.D    | Wns,Wd           | Move double Wns:Wns + 1 to Wd           | 1     | 2      |

| SWAP     | Wn               | Wn = byte or nibble swap Wn             | 1     | 1      |

| TBLRDH   | Ws,Wd            | Read high program word to Wd            | 1     | 2      |

| TBLRDL   | Ws,Wd            | Read low program word to Wd             | 1     | 2      |

| TBLWTH   | Ws,Wd            | Write Ws to high program word           | 1     | 2      |

| TBLWTL   | Ws,Wd            | Write Ws to low program word            | 1     | 2      |

**Note:** When the optional {,WREG} operand is specified, the destination of the instruction is WREG. When {,WREG} is not specified, the destination of the instruction is the file register f.

**Note:** Table 9-3 through Table 9-11 present the base instruction syntax for the PIC24H. These instructions do not include all of the available addressing modes. For example, some instructions show the Byte Addressing mode and others do not.

TABLE 9-4: MATH INSTRUCTIONS

| Assembly | Syntax       | Description                                   | Words | Cycles   |

|----------|--------------|-----------------------------------------------|-------|----------|

| ADD      | f {,WREG}    | Destination = f + WREG                        | 1     | 1        |

| ADD      | #lit10,Wn    | Wn = lit10 + Wn                               | 1     | 1        |

| ADD      | Wb,#lit5,Wd  | Wd = Wb + lit5                                | 1     | 1        |

| ADD      | Wb,Ws,Wd     | Wd = Wb + Ws                                  | 1     | 1        |

| ADDC     | f {,WREG}    | Destination = f + WREG + (C)                  | 1     | 1        |

| ADDC     | #lit10,Wn    | Wn = lit10 + Wn + (C)                         | 1     | 1        |

| ADDC     | Wb,#lit5,Wd  | Wd = Wb + lit5 + (C)                          | 1     | 1        |

| ADDC     | Wb,Ws,Wd     | Wd = Wb + Ws + (C)                            | 1     | 1        |

| DAW.B    | Wn           | Wn = decimal adjust Wn                        | 1     | 1        |

| DEC      | f {,WREG}    | Destination = f – 1                           | 1     | 1        |

| DEC      | Ws,Wd        | Wd = Ws - 1                                   | 1     | 1        |

| DEC2     | f {,WREG}    | Destination = f – 2                           | 1     | 1        |

| DEC2     | Ws,Wd        | Wd = Ws - 2                                   | 1     | 1        |

| DIV.S    | Wm,Wn        | Signed 16/16-bit integer divide*              | 1     | 18       |

| DIV.SD   | Wm,Wn        | Signed 32/16-bit integer divide*              | 1     | 18       |

| DIV.U    | Wm,Wn        | Unsigned 16/16-bit integer divide*            | 1     | 18       |

| DIV.UD   | Wm,Wn        | Unsigned 32/16-bit integer divide*            | 1     | 18       |

| DIVF     | Wm,Wn        | Signed 16/16-bit fractional divide*           | 1     | 18       |

| INC      | f {,WREG}    | Destination = f + 1                           | 1     | 1        |

| INC      | Ws,Wd        | Wd = Ws + 1                                   | 1     | 1        |

| INC2     | f {,WREG}    | Destination = f + 2                           | 1     | 1        |

| INC2     | Ws,Wd        | Wd = Ws + 2                                   | 1     | 1        |

| MUL      | f            | W3:W2 = f * WREG                              | 1     | 1        |

| MUL.SS   | Wb,Ws,Wnd    | $\{Wnd + 1,Wnd\} = sign(Wb) * sign(Ws)$       | 1     | 1        |

| MUL.SU   | Wb,#lit5,Wnd | $\{Wnd + 1,Wnd\} = sign(Wb) * unsign(lit5)$   | 1     | 1        |

| MUL.SU   | Wb,Ws,Wnd    | $\{Wnd + 1,Wnd\} = sign(Wb) * unsign(Ws)$     | 1     | 1        |

| MUL.US   | Wb,Ws,Wnd    | $\{Wnd + 1,Wnd\} = unsign(Wb) * sign(Ws)$     | 1     | 1        |

| MUL.UU   | Wb,#lit5,Wnd | $\{Wnd + 1,Wnd\} = unsign(Wb) * unsign(Iit5)$ | 1     | 1        |

| MUL.UU   | Wb,Ws,Wnd    | $\{Wnd + 1,Wnd\} = unsign(Wb) * unsign(Ws)$   | 1     | 1        |

| SE       | Ws,Wnd       | Wnd = sign-extended Ws                        | 1     | 1        |

| SUB      | f {,WREG}    | Destination = f – WREG                        | 1     | 1        |

| SUB      | #lit10, Wn   | Wn = Wn – lit10                               | 1     | 1        |

| SUB      | Wb,#lit5,Wd  | Wd = Wb - lit5                                | 1     | 1        |

| SUB      | Wb,Ws,Wd     | Wd = Wb - Ws                                  | 1     | 1        |

| SUBB     | f {,WREG}    | Destination = f - WREG - (C)                  | 1     | 1        |

| SUBB     | #lit10, Wn   | Wn = Wn - lit10 - (C)                         | 1     | 1        |

| SUBB     | Wb,#lit5,Wd  | $Wd = Wb - lit5 - (\overline{C})$             | 1     | 1        |

| SUBB     | Wb,Ws,Wd     | $Wd = Wb - Ws - (\overline{C})$               | 1     | 1        |