Part Number S5320 Revision 5.03 – June 14, 2006

## Data Sheet

## S5320 PCI Match Maker, 3.3V

# S5320 PCI Match Maker

(This page intentionally left blank.)

Part Number S5320 Revision 5.03 – June 14, 2006

## S5320 PCI Match Maker

## Data Sheet

## FEATURES

- Full 132 Mbytes/sec Transfer Rate

- PCI Bus Operation to 33 MHz

- PCI 2.2 Compliant Target Device

- 3.3V Power Supply

- 5V Tolerant I/Os

- Add-On Bus up to 40 MHz

- Programmable Prefetch and Wait States

- 8/16/32-Bit Add-On Bus

- Four Definable Pass-Thru Regions

- Two 32-Byte Burstable FIFOs

- Active/Passive Add-On Bus Operation

- Mailbox Registers/w Byte Level Status

- Direct Mailbox Data Strobe/Int Pin

- Mailbox Read/Write Interrupts

- Direct PCI and Add-On Interrupt Pins

- Plug-N-Play Compatible

- Two-wire Serial Bus nvRAM Support

- Optional External BIOS capability

- 176-Pin Low Profile LQFP

- Environmental Friendly Lead-free Package

Option

## **APPLICATIONS**

- ISA Conversions

- Multimedia

- I/O Ports

- Data Storage

- CODEC5

- General Purpose PCI Bus Interfacing

## ARCHITECTURAL OVERVIEW

The AMCC S5320 was developed to provide the designer with a single multi-function device offering a flexible and easy way to connect to the PCI bus. By using the S5320, the designer eliminates the task of assuring PCI bus specification compliance and the necessity of understanding PCI bus timing requirements when interfacing a new application. The S5320 was designed for 3.3V environment but its inputs/outputs are tolerant to 5V signaling.

The complex 33 MHz PCI bus signals are converted through the S5320 into an easy-to-use 8/16/32-bit user bus referred to as the user Add-On bus. The Add-On bus allows user add-on designs bus clock speed independent operation to 40 MHz.

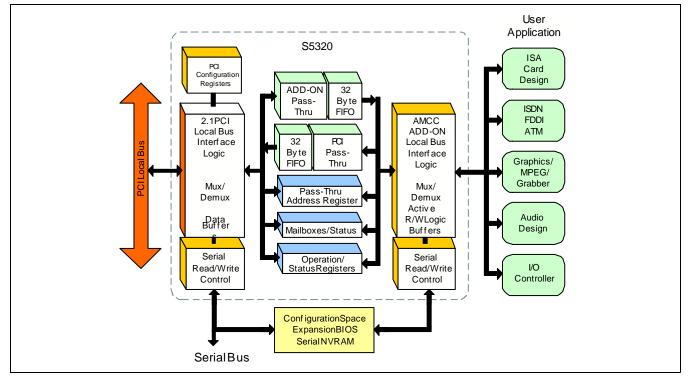

#### Figure 1. S5320 Block Diagram

| FEATURES                                                                             |    |

|--------------------------------------------------------------------------------------|----|

| APPLICATIONS                                                                         | 3  |

| ARCHITECTURAL OVERVIEW                                                               |    |

| ARCHITECTURAL OVERVIEW S5320                                                         |    |

| S5320 REGISTER ARCHITECTURE                                                          |    |

| PCI Configuration Registers                                                          |    |

| PCI Bus Accessible Registers                                                         |    |

| Add-On Bus Accessible Registers                                                      | 15 |

| SERIAL NON-VOLATILE INTERFACE                                                        |    |

| MAILBOX OPERATION                                                                    |    |

| PASS-THRU OPERATION                                                                  |    |

| PCI BUS SIGNALS                                                                      |    |

| ADD-ON BUS AND S5320 CONTROL SIGNALS                                                 |    |

| USER ADD-ON BUS PIN DESCRIPTIONS                                                     |    |

| PCI CONFIGURATIONS REGISTERS                                                         |    |

| Vendor Identification Register (VID)                                                 |    |

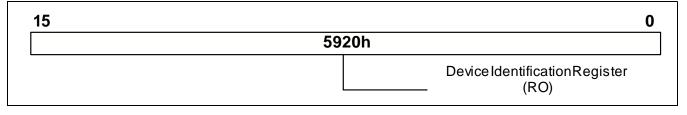

| Device Identification Register (DID)                                                 |    |

| PCI Command Register (PCICMD)                                                        |    |

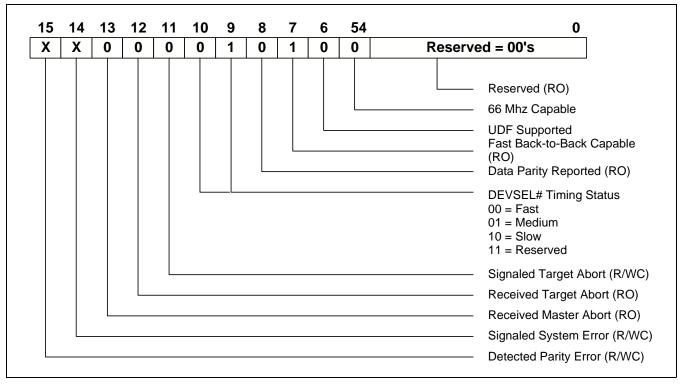

| PCI Status Register (PCISTS)<br>Revision Identification Register (RID)               |    |

| Class Code Register (CLCD)                                                           |    |

| Cache Line Size Register (CALN)                                                      |    |

| Latency Timer Register (LAT)                                                         |    |

| Header Type Register (HDR)                                                           |    |

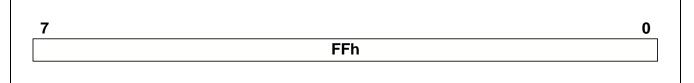

| Built-In Self-Test Register (BIST)                                                   |    |

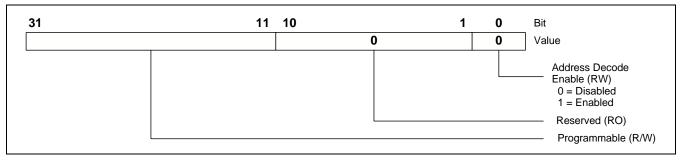

| Base Address Register (BADR)                                                         |    |

| Determining Base Address Size                                                        |    |

| Assigning the Base Address<br>Subsystem Vendor Identification Register (SVID)        |    |

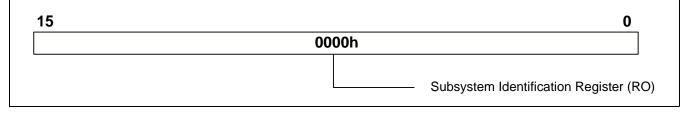

| Subsystem ID Register (SID)                                                          |    |

| Expansion ROM Base Address Register (XROM)                                           |    |

| Interrupt Line Register (INTLN)                                                      |    |

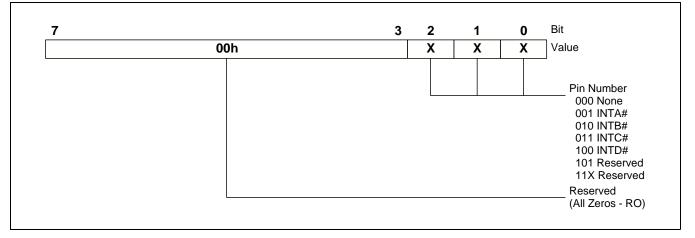

| Interrupt Pin Register (INTPIN)                                                      |    |

| Minimum Grant Register (MINGNT)                                                      |    |

| Maximum Latency Register (MAXLAT)                                                    |    |

| OPERATION REGISTERS                                                                  |    |

| PCI BUS OPERATION REGISTERS                                                          |    |

| PCI Outgoing Mailbox Register (OMB)                                                  |    |

| PCI Incoming Mailbox Register (IMB)<br>PCI Mailbox Empty/full Status Register (MBEF) |    |

| PCI Interrupt Control/Status Register (INTCSR)                                       |    |

| PCI Reset Control Register (RCR)                                                     |    |

| PCI Pass-Thru Configuration Register (PTCR)                                          |    |

| ADD-ON BUS OPERATION REGISTERS                                                       |    |

| Add-On Incoming Mailbox Register (AIMB)                                                 |   |

|-----------------------------------------------------------------------------------------|---|

| Add-On Outgoing Mailbox Register (AOMB)                                                 |   |

| Add-On Pass-Thru Address Register (APTA)                                                |   |

| Add-On Pass-Thru Data Register (APTD)                                                   |   |

| Add-On Mailbox Empty/full Status Register (AMBEF)                                       |   |

| Add-On Interrupt Control/status Register (AINT)                                         |   |

| Add-On Reset Control Register (ARCR)<br>Add-On Pass-thru Configuration Register (APTCR) |   |

| INITIALIZATION                                                                          |   |

| PCI RESET                                                                               |   |

| LOADING THE SERIAL NV MEMORY                                                            | - |

| LOADING THE SERIAL NV MEMORY<br>NON-VOLATILE MEMORY INTERFACE                           |   |

|                                                                                         |   |

| NVRAM READ/WRITE DESCRIPTION                                                            |   |

| PCI BUS CONFIGURATION CYCLES                                                            |   |

| EXPANSION BIOS ROMS                                                                     |   |

| PCI BUS INTERFACE                                                                       |   |

| PCI BUS TRANSACTIONS                                                                    |   |

| PCI BURST TRANSFERS                                                                     |   |

| PCI READ TRANSFERS                                                                      |   |

| PCI WRITE TRANSFERS                                                                     |   |

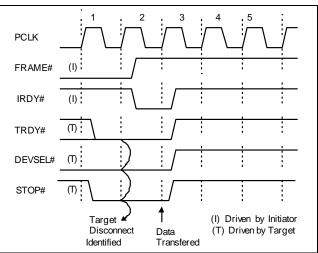

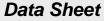

| Target-Initiated Termination                                                            |   |

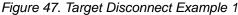

| Target Disconnects                                                                      |   |

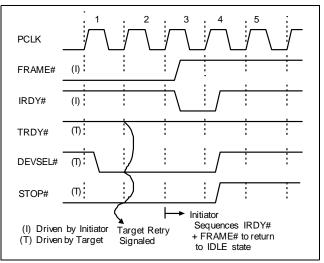

| Target Requested Retries                                                                |   |

| Target Aborts                                                                           |   |

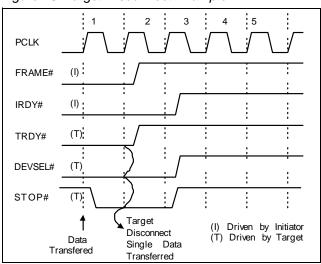

| Target Latency                                                                          |   |

| Target Locking                                                                          |   |

| PCI Bus Access Latency Components                                                       |   |

| PCI BUS INTERRUPTS                                                                      |   |

| PCI BUS PARITY ERRORS                                                                   |   |

| MAILBOX OVERVIEW                                                                        |   |

| FUNCTIONAL DESCRIPTION                                                                  |   |

| Mailbox Empty/Full Conditions                                                           |   |

| Mailbox Interrupts                                                                      |   |

| Add-On Outgoing Mailbox, Byte 3 Access                                                  |   |

| BUS INTERFACE                                                                           |   |

| PCI Bus Interface                                                                       |   |

| Add-On Bus Interface                                                                    |   |

| 8-Bit and 16-Bit Add-On Interfaces                                                      |   |

| CONFIGURATION                                                                           |   |

| Mailbox Status                                                                          |   |

| Writing the PCI Outgoing Mailbox:                                                       |   |

| Reading an Add-On Incoming Mailbox:                             |     |

|-----------------------------------------------------------------|-----|

| Writing an Add-On Outgoing Mailbox:                             |     |

| Mailbox Interrupts                                              |     |

| Servicing a PCI Mailbox Interrupt (INTA# Asserted):             |     |

| Servicing the Add-On mailbox interrupt (IRQ# Asserted):         | 106 |

| ADD-ON LOCAL BUS INTERFACE                                      | 108 |

| ADD-ON INTERFACE SIGNALS                                        |     |

| SYSTEM SIGNALS                                                  |     |

| ADD-ON S5320 REGISTER ACCESSES                                  |     |

| Register Access Signals                                         |     |

| S5320 General Register Accesses                                 |     |

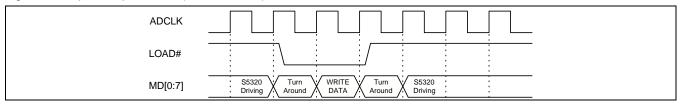

| S5320 16-bit Mode Register Accesses                             | 109 |

| MAILBOX OVERVIEW                                                |     |

| PASS-THRU OVERVIEW                                              |     |

| WRITE FIFO OVERVIEW                                             |     |

| READ FIFO OVERVIEW                                              |     |

| FUNCTIONAL DESCRIPTION                                          |     |

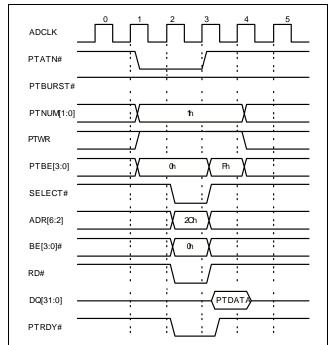

| Pass-Thru Transfers                                             |     |

| Pass-Thru Status/Control Signals                                |     |

| BUS INTERFACE                                                   |     |

| PCI Bus Interface                                               |     |

| PCI Pass-Thru Single Cycle Accesses                             |     |

| PCI Pass-Thru Burst Accesses                                    |     |

| PCI Disconnect Conditions                                       |     |

| PCI Write Disconnect                                            |     |

| PCI Read Disconnect                                             |     |

| S5320 PASSIVE MODE OPERATION                                    |     |

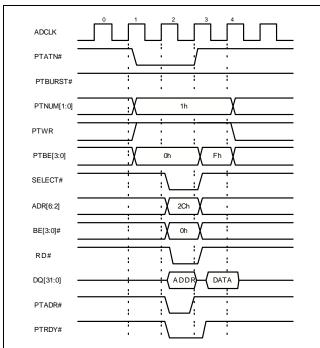

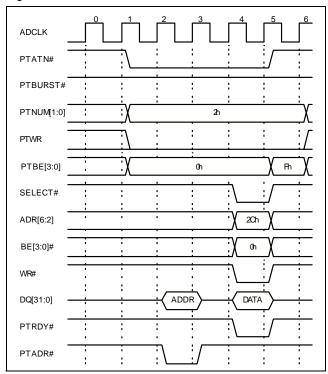

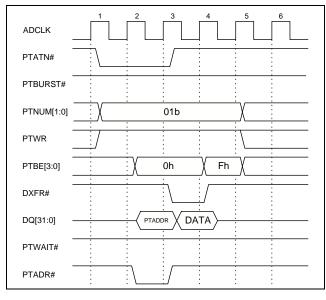

| Single-Cycle PCI to Pass-Thru Write                             |     |

| Single-Cycle PCI to Pass-Thru Read                              |     |

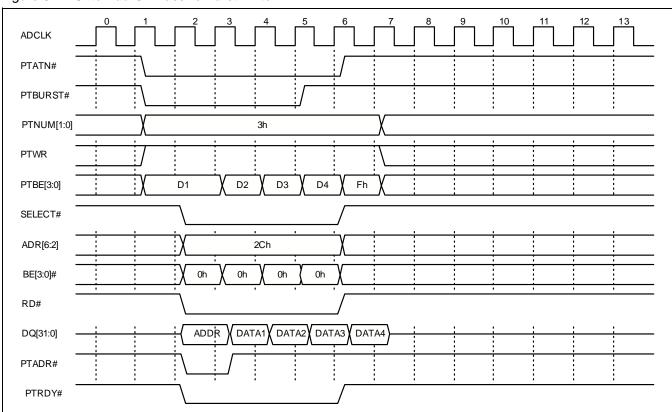

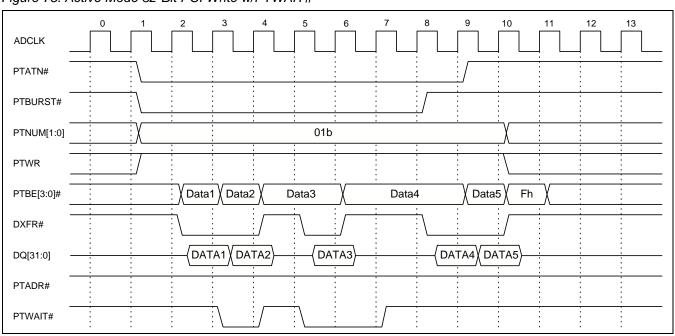

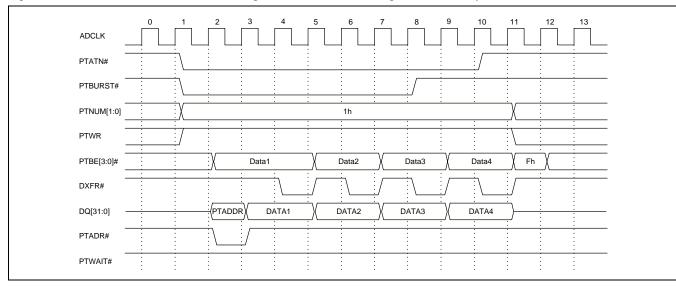

| PCI to Pass-Thru Burst Writes                                   |     |

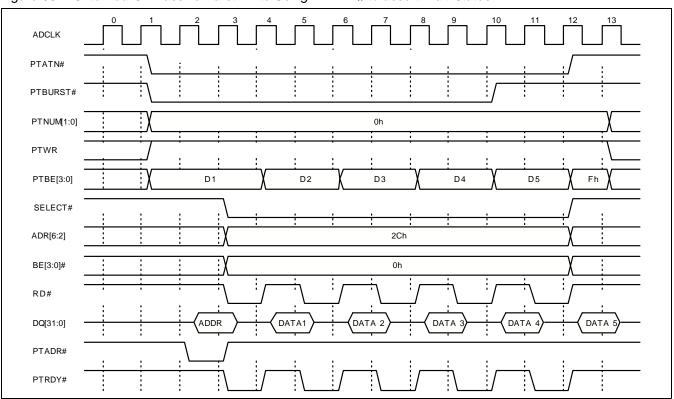

| Pass-Thru Burst Reads                                           |     |

| Using PTRDY# to assert Wait-States                              |     |

| 8-Bit and 16-Bit Pass-Thru Add-On Bus Interface in Passive Mode |     |

| Endian Conversion                                               |     |

| Active Operation                                                | 128 |

| Active mode Programmable Wait States                            | 131 |

| PTRDY#/PTWAIT#                                                  | 131 |

| DXFR#                                                           |     |

| Active Mode Figures and Descriptions                            |     |

| Active mode Burst cycles                                        |     |

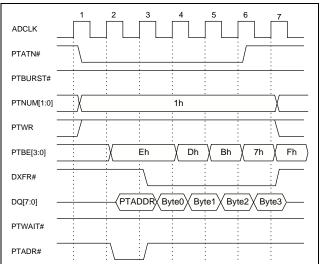

| Clock by Clock description of Figure 75                         | 133 |

| Clock by Clock description of Figure 76 |     |

|-----------------------------------------|-----|

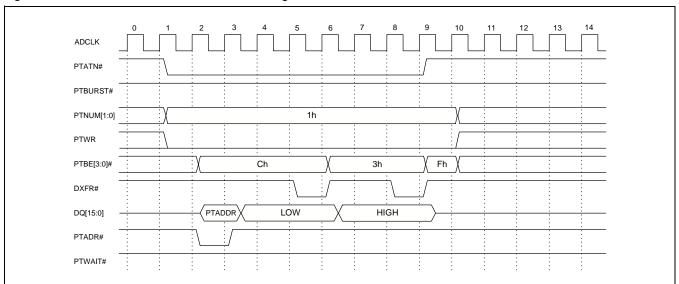

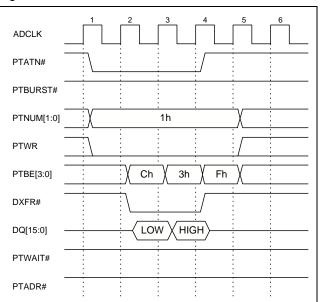

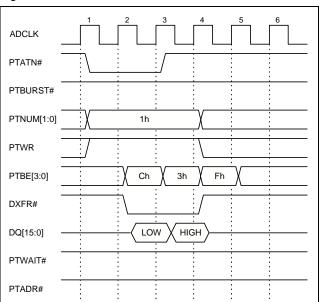

| Active Mode with 16/8-bit data buses    | 136 |

| CONFIGURATION                           | 137 |

| S5320 Base Address Register Definition  |     |

| Creating a Pass-Thru Region             | 138 |

| Accessing a Pass-Thru Region            |     |

| Special Programming Features            | 139 |

| ABSOLUTE MAXIMUM STRESS RATINGS         | 141 |

| RECOMMENDED OPERATING CONDITIONS        |     |

| PCI Signal DC Characteristics           |     |

| Add-On Signal DC Characteristics        | 143 |

| nvRAM Memory Interface Signals          | 143 |

| TIMING SPECIFICATION                    |     |

| PCI Clock Specification                 |     |

| Add-On Signal Timings                   |     |

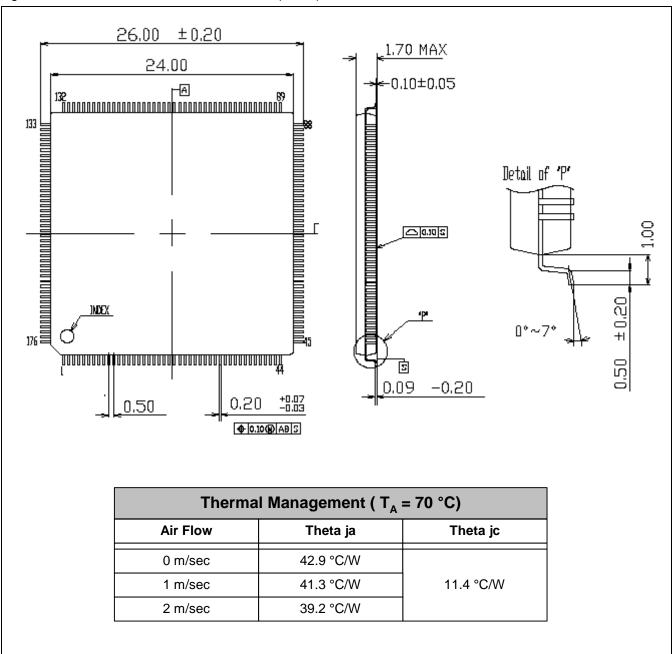

| PACKAGE INFORMATION                     | 153 |

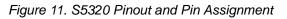

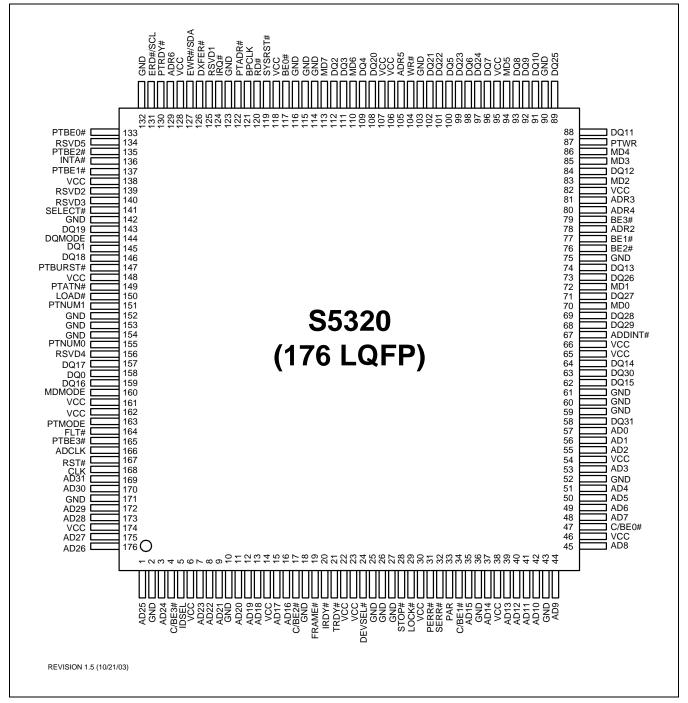

| S5320 Pin Assignment - 176 LQFP         | 155 |

| DOCUMENT REVISION HISTORY               | 158 |

| ORDERING INFORM ATION                   | 159 |

| Figure 1. S5320 Block Diagram                            | 4  |

|----------------------------------------------------------|----|

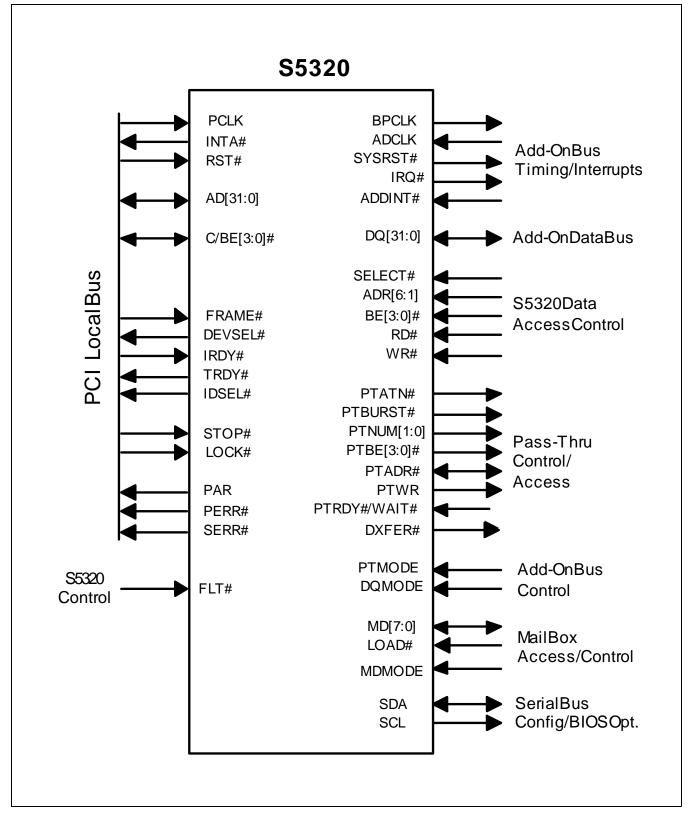

| Figure 2. S5320 Pinout                                   | 16 |

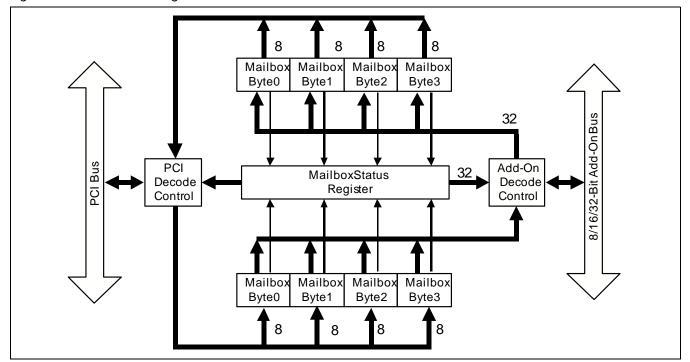

| Figure 3. Mailbox Block Diagram                          | 17 |

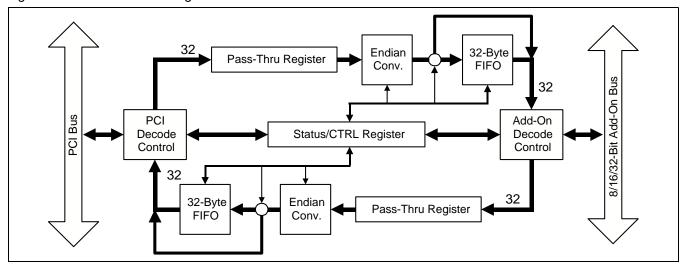

| Figure 4. Pass-Thru Block Diagram                        | 18 |

| Figure 5. S5320 Signal Assignment                        | 20 |

| Figure 6. Vendor Identification Register                 | 29 |

| Figure 7. Device Identification Register                 | 30 |

| Figure 8. PCI Command Register                           | 31 |

| Figure 9. PCI Status Register                            | 33 |

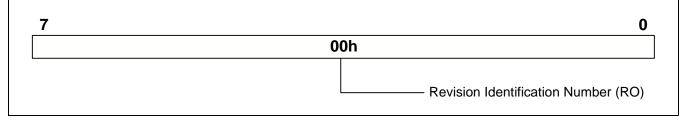

| Figure 10. Revision Identification Register              | 35 |

| Figure 11. Class Code Register                           | 36 |

| Figure 12. Cache Line Size Register                      | 41 |

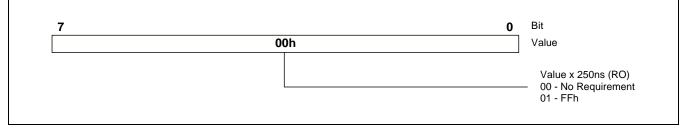

| Figure 13. Latency Timer Register                        | 42 |

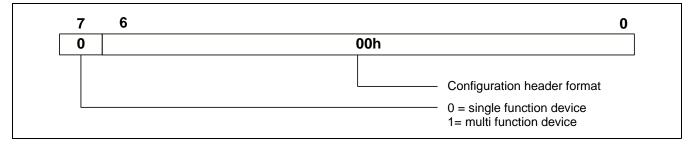

| Figure 14. Header Type Register                          | 43 |

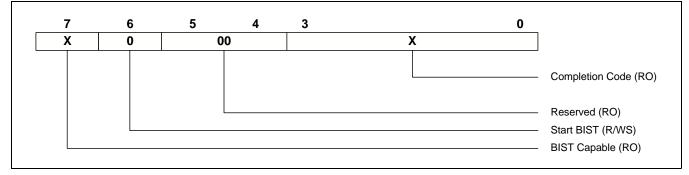

| Figure 15. Built-In Self-Test Register                   | 44 |

| Figure 16. Base Address Register - Memory                | 46 |

| Figure 17. Base Address Register - I/O                   | 47 |

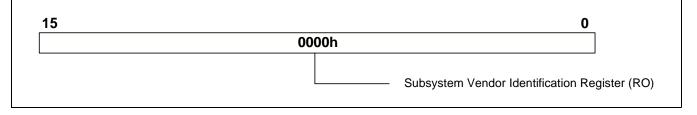

| Figure 18. Subsystem Vendor Identification Register      | 50 |

| Figure 19. Subsystem Identification Register             | 51 |

| Figure 20. Expansion ROM Base Address Register           | 52 |

| Figure 21. Interrupt Line Register                       | 54 |

| Figure 22. Interrupt Pin Register                        | 55 |

| Figure 23. Minimum Grant Register                        | 56 |

| Figure 24. Maximum Latency Register                      | 57 |

| Figure 25. Outgoing Mailbox                              | 60 |

| Figure 26. Incoming Mailbox                              | 61 |

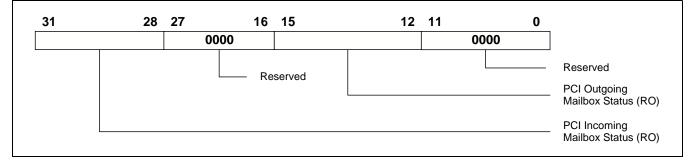

| Figure 27. Mailbox Empty/Full Status Register (MBEF)     | 62 |

| Figure 28. Interrupt Control Status Register             | 63 |

| Figure 29. FIFO Control/Status Register                  | 65 |

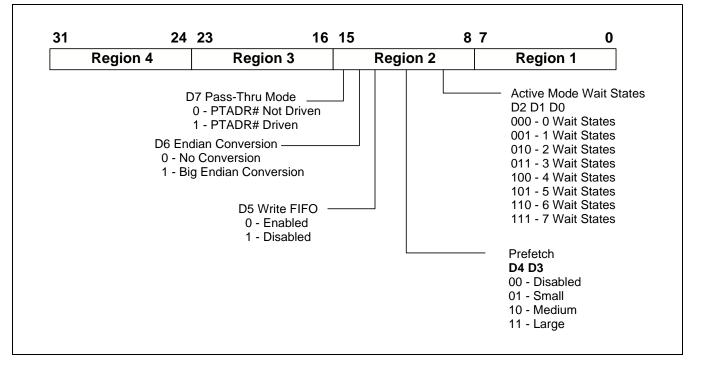

| Figure 30. Pass-Thru Configuration Register              | 67 |

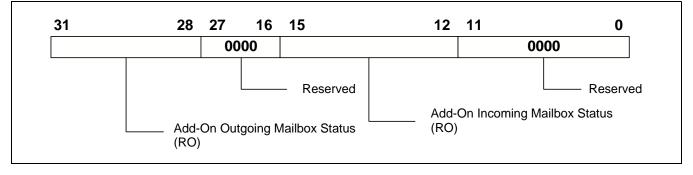

| Figure 31. Mailbox Empty/Full Status Register            | 71 |

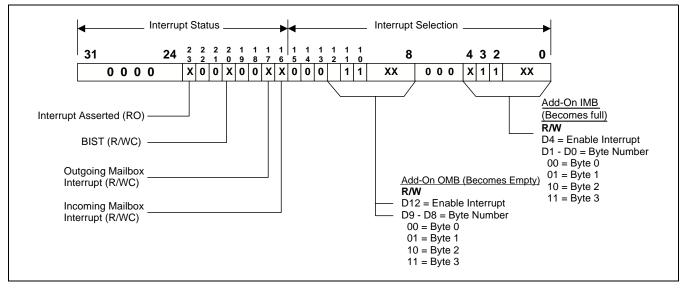

| Figure 32. Add-On Interrupt Control Status Register      | 73 |

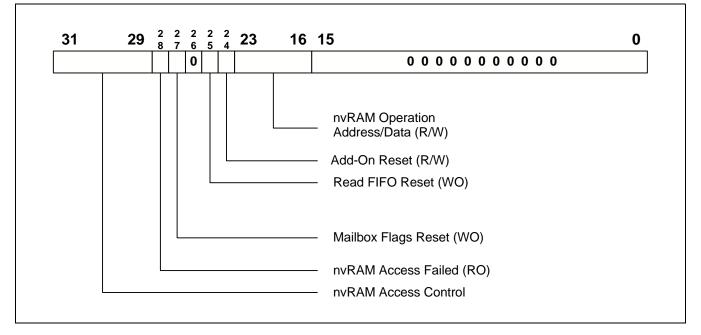

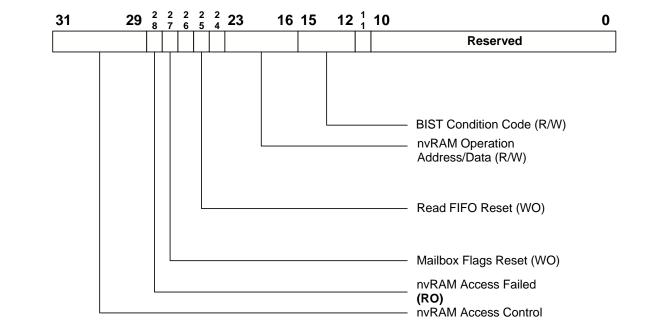

| Figure 33. Add-On General Control/Status Register        | 75 |

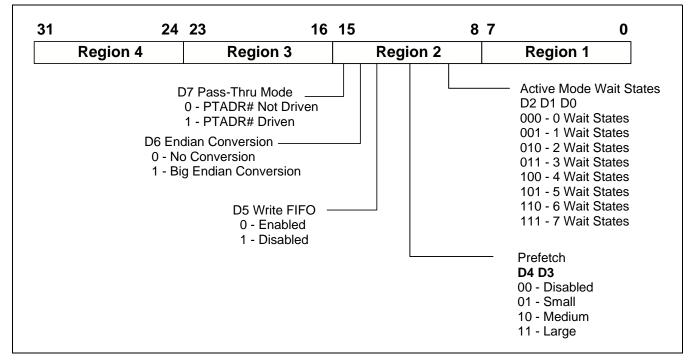

| Figure 34. Pass-Thru Configuration Register              | 77 |

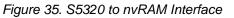

| Figure 35. S5320 to nvRAM Interface                      | 81 |

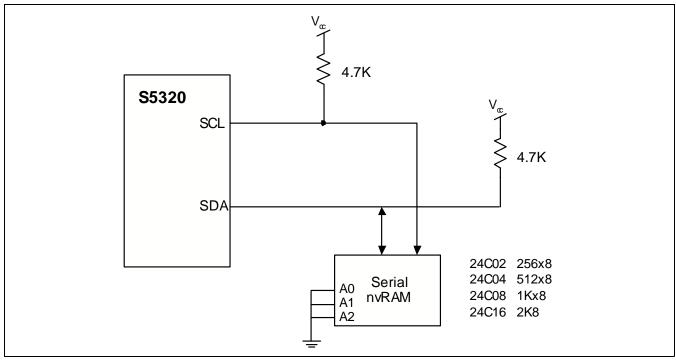

| Figure 36. Serial Interface Definition of Start and Stop | 81 |

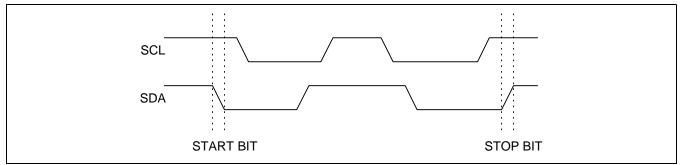

| Figure 37. Serial Interface Clock Data Relationship      | 81 |

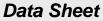

| Figure 38. Serial Interface Byte Access-Write                                    | 82  |

|----------------------------------------------------------------------------------|-----|

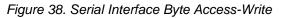

| Figure 39. Serial Interface Byte Access-Read                                     | 82  |

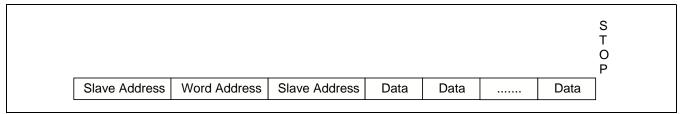

| Figure 40. Serial Byte Access- Sequential Read                                   | 82  |

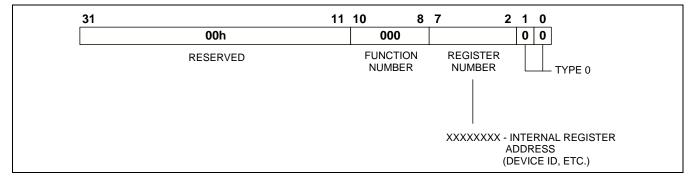

| Figure 41. PCI AD Bus Definition Type 0 Configuration Access                     | 86  |

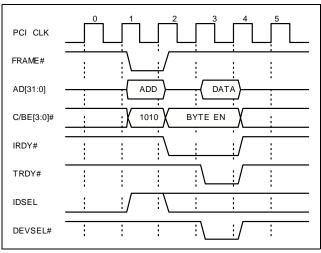

| Figure 42. Type 0 Configuration Read Cycles                                      | 86  |

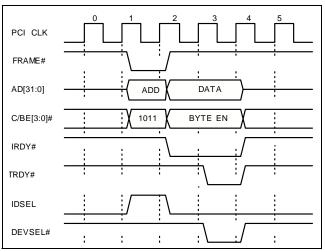

| Figure 43. Type 0 Configuration Write Cycles                                     | 87  |

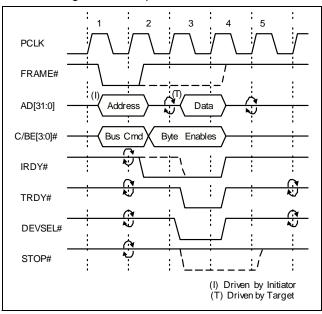

| Figure 44. Single Data Phase PCI Bus Read of S5320 Registers or Expansion ROM    | 93  |

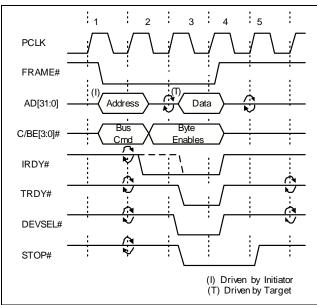

| Figure 45. Burst PCI Bus Read Attempt to S5320 Registers or Expansion ROM        |     |

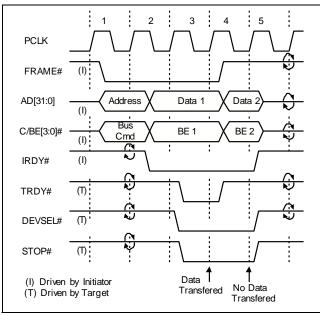

| Figure 46. Burst PCI Bus Write of S5320 Registers                                |     |

| Figure 47. Target Disconnect Example 1                                           |     |

| Figure 48. Target Disconnect Example 2                                           | 95  |

| Figure 49. Target-Initiated Retry                                                | 95  |

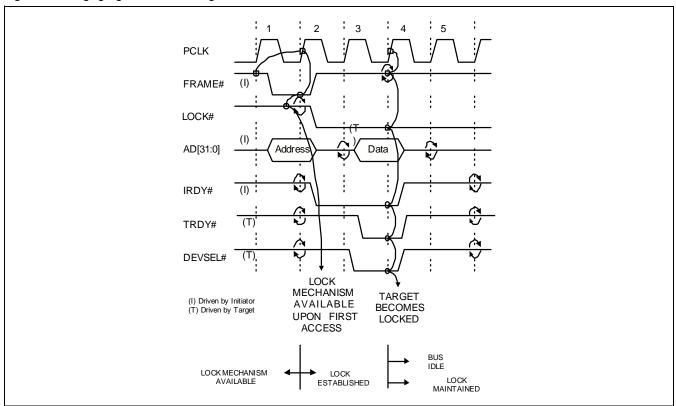

| Figure 50. Engaging the LOCK# Signal                                             |     |

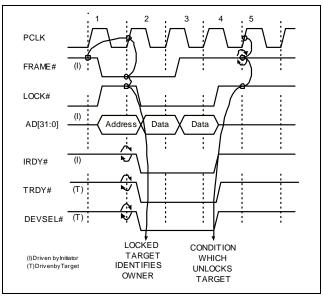

| Figure 51. Access to a Locked Target by its Owner                                |     |

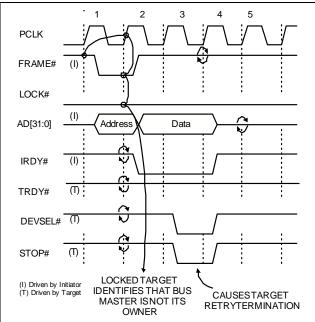

| Figure 52. Access Attempt to a Locked Target                                     |     |

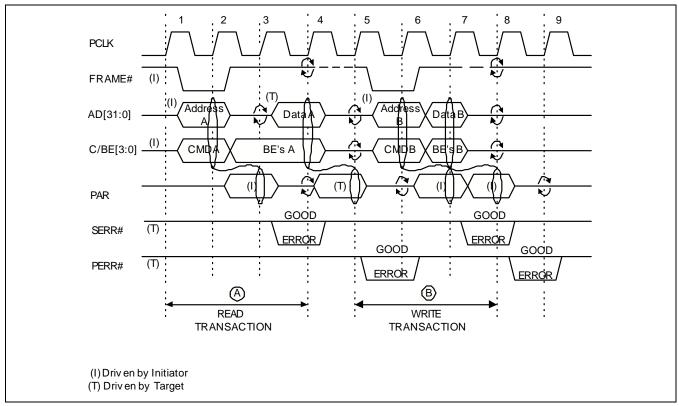

| Figure 53. Error Reporting Signal                                                |     |

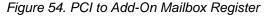

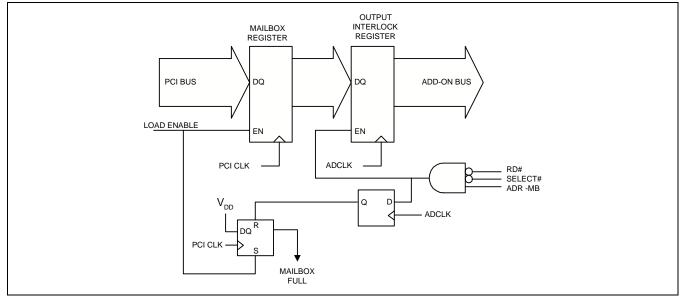

| Figure 54. PCI to Add-On Mailbox Register                                        | 100 |

| Figure 55. Add-On to PCI Mailbox Register                                        | 101 |

| Figure 56. Input/Output Mode (MDMODE=0)                                          | 103 |

| Figure 57. Input Mode (MDMODE=1)                                                 | 103 |

| Figure 58. Read Operation Register                                               | 109 |

| Figure 59. Write Operation Register                                              | 109 |

| Figure 60. 16 Bit Mode Operation Register DWORD Write/Read                       | 110 |

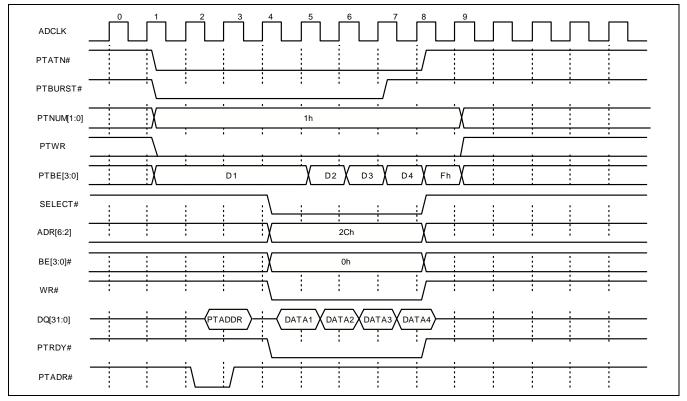

| Figure 61. PCI To Add-On Passive Write                                           | 116 |

| Figure 62. PCI To Add-On Passive Write w/Pass-Thru Address                       | 116 |

| Figure 63. PCI To Add-On Passive Read                                            | 117 |

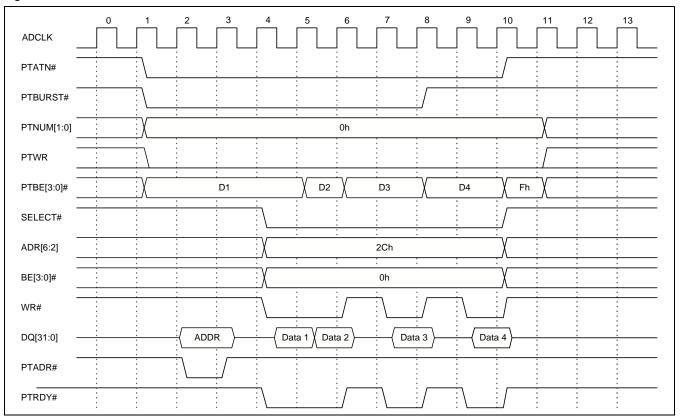

| Figure 64. PCI to Add-On Passive Burst Write                                     | 118 |

| Figure 65. PCI to Add-On Passive Burst Write Using PTRDY# to assert Wait-States  | 120 |

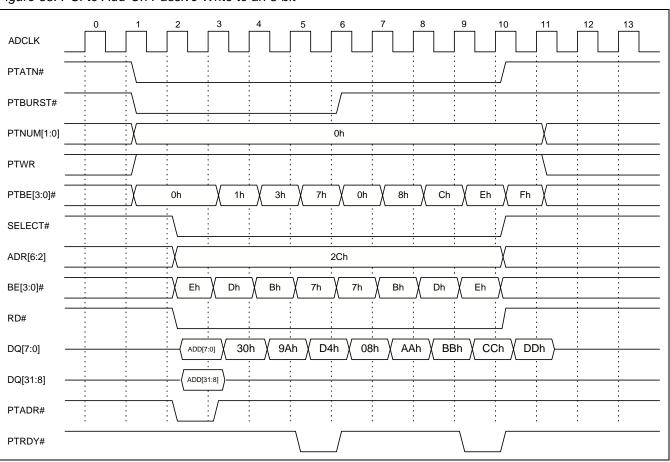

| Figure 66. PCI to Add-On Passive Burst Read Access                               | 120 |

| Figure 67. PCI to Add-On Passive Burst Read                                      | 122 |

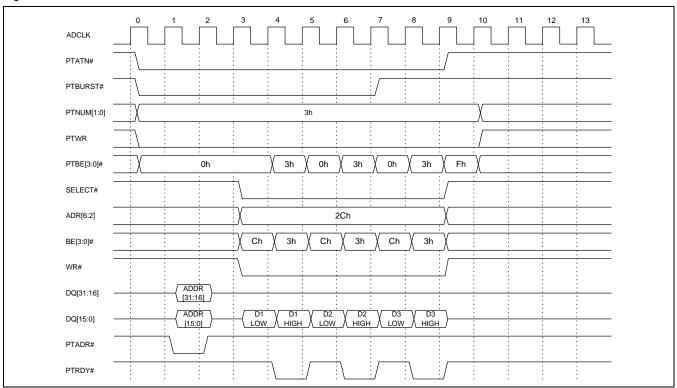

| Figure 68. PCI to Add-On Passive Write to an 8-bit                               | 127 |

| Figure 69. PCI to Add-On Passive Read to an 16-bit Add-On Device                 | 129 |

| Figure 70. Active mode PCI Read (Zero Programmed Wait States) with PTADR#        | 130 |

| Figure 71. Active Mode PCI Read without PTADR#                                   | 130 |

| Figure 72. Active Mode PCI Write without PTADR#                                  | 130 |

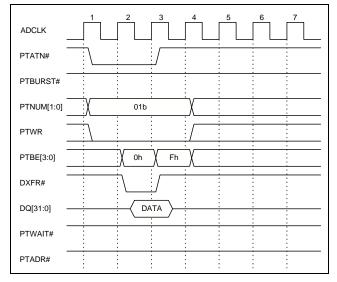

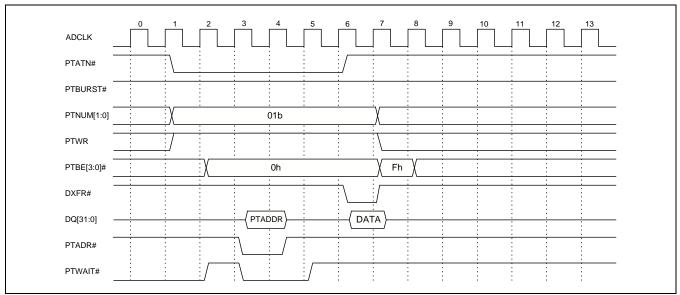

| Figure 73. Active Mode PCI Write with Add-On Initiated Wait States Using PTWAIT# | 131 |

| Figure 74. Active Mode 32-Bit PCI Write                                          | 131 |

| Figure 75. Active Mode 32-Bit PCI Write w/PTWAIT#                          | 133 |

|----------------------------------------------------------------------------|-----|

| Figure 76. Active Mode PCI Write Showing a One Wait State Programmed Delay |     |

| Figure 77. 16-Bit Active Mode PCI Read w/ Programmed Wait States           | 135 |

| Figure 78. Active Mode PCI Read w/ Programmed Wait States                  | 136 |

| Figure 79. Active Mode PCI Read                                            | 137 |

| Figure 80. Active Mode PCI Write                                           | 137 |

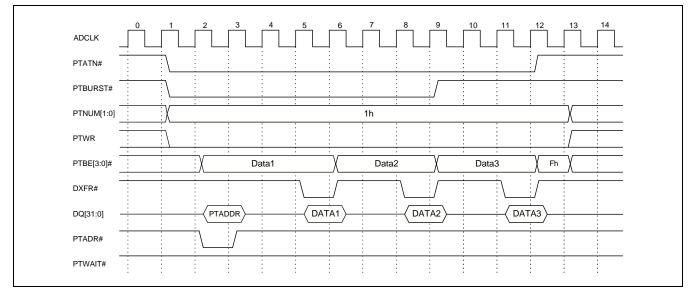

| Figure 81. 8-Bit Active Mode PCI Write                                     | 138 |

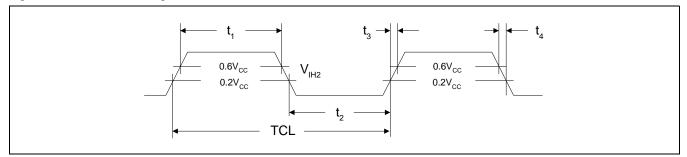

| Figure 82. PCI Clock Timing                                                | 144 |

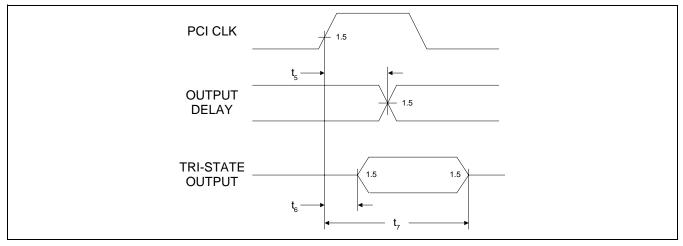

| Figure 83. PCI Signal Output Timing                                        | 145 |

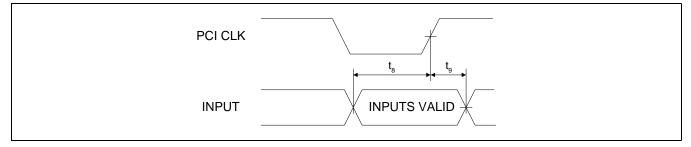

| Figure 84. PCI Signal Input Timing                                         | 145 |

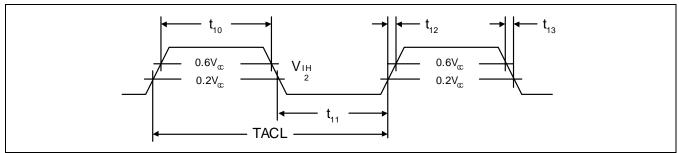

| Figure 85. Add-On Clock Timing                                             | 148 |

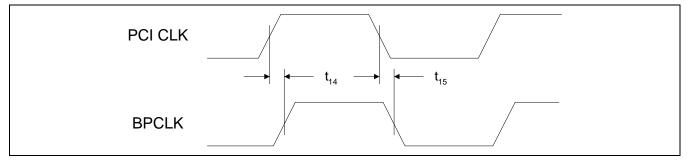

| Figure 86. Pass-Thru Clock Relationship to PCI Clock                       | 148 |

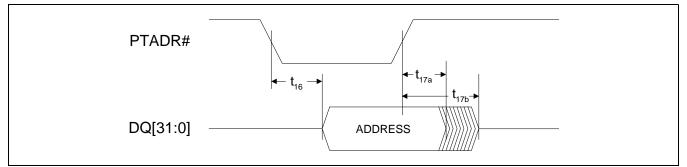

| Figure 87. PTADR Timing                                                    | 148 |

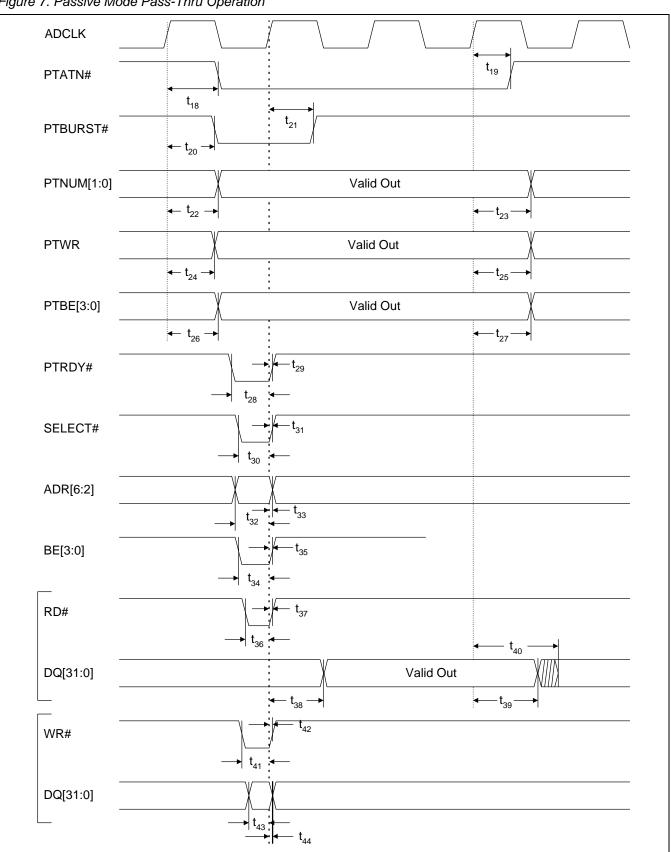

| Figure 88. Passive Mode Pass-Thru Operation                                | 149 |

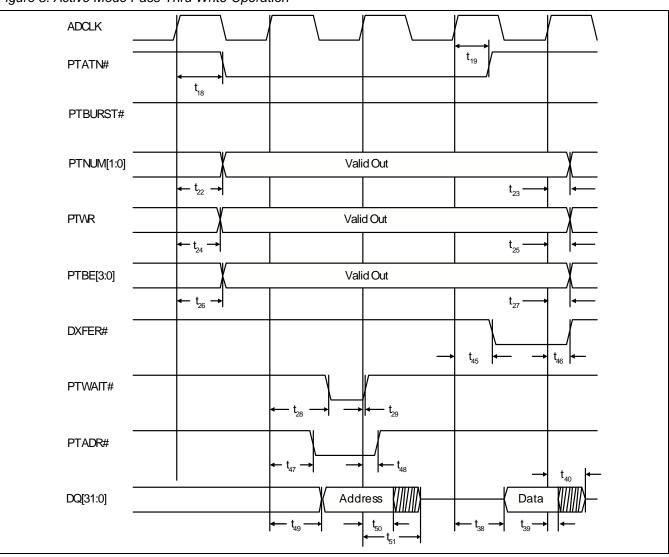

| Figure 89. Active Mode Pass-Thru Write Operation                           | 151 |

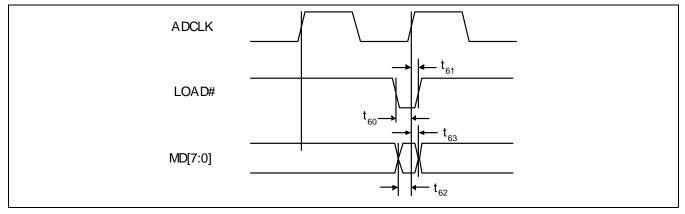

| Figure 90. Mailbox Data (Setup/Hold timing)                                | 152 |

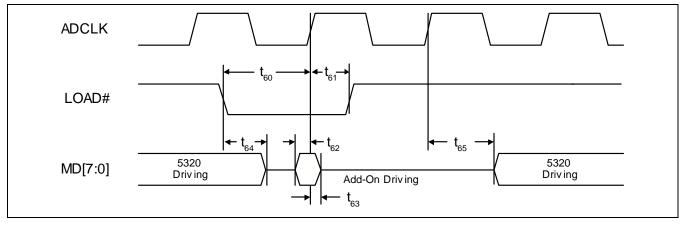

| Figure 91. Mailbox Data (Float/Active timing)                              | 152 |

| Figure 92. S5320 Pinout and Pin Assignment                                 | 153 |

| Figure 93. 176 Pin Low Profile Quad Flat Pack (LQFP), 24 mm x 24 mm        | 154 |

(This page intentionally left blank.)

## LIST OF TABLES

| Table 1. PCI Bus Address and Data Signal                                                         | 21 |

|--------------------------------------------------------------------------------------------------|----|

| Table 2. PCI Bus System Signals                                                                  | 22 |

| Table 3. PCI Bus Data Transfer Control Signals                                                   | 22 |

| Table 4. PCI Bus Error Reporting Signals                                                         | 22 |

| Table 5. Serial nvRAM Interface Signals                                                          | 23 |

| Table 6. Direct Mailbox Access Signals                                                           | 23 |

| Table 7. Pass-Thru Data Channel Pins                                                             | 24 |

| Table 8. S5320 Add-On Bus Register Access Pins                                                   | 25 |

| Table 9. Add-On Bus General Pins                                                                 | 26 |

| Table 10. Configuration Registers                                                                | 27 |

| Table 11. Defined Base Class Codes                                                               | 37 |

| Table 12. Base Class Code 00h: Early, Pre-2.0 Specification Devices                              | 37 |

| Table 13. Base Class Code 01h: Mass Storage Controllers                                          | 37 |

| Table 14. Base Class Code 02h: Network Controllers                                               | 37 |

| Table 15. Base Class Code 03h: Display Controllers                                               | 38 |

| Table 16. Base Class Code 04h: Multimedia Devices                                                | 38 |

| Table 17. Base Class Code 05h: Memory Controllers                                                | 38 |

| Table 18. Base Class Code 06h: Bridge Devices                                                    | 39 |

| Table 19. Base Class Code 07h: Simple Communications Controllers                                 | 39 |

| Table 20. Base Class Code 08h: Base System Peripherals                                           | 39 |

| Table 21. Base Class Code 09h: Input Devices                                                     | 40 |

| Table 22. Base Class Code 0Ah: Docking Stations                                                  | 40 |

| Table 23. Base Class Code 0Bh: Processors                                                        | 40 |

| Table 24. Base Class Code 0Ch: Serial Bus Controllers                                            | 40 |

| Table 25. Base Address Register Response (Memory Assigned) to All-Ones Write Operation           | 48 |

| Table 26. Read Response (I/O Assigned) to an All-Ones Write Operation to a Base Address Register | 49 |

| Table 27. Read Response to Expansion ROM Base Address Register (after all ones written)          | 53 |

| Table 28. Operation Registers - PCI Bus                                                          | 59 |

| Table 29. Mailbox Empty/Full Status Register                                                     | 62 |

| Table 30. Interrupt Control Status Register                                                      | 64 |

| Table 31. Reset Control Register                                                                 | 66 |

| Table 32. Pass-Thru Configuration Register                                                       | 68 |

| Table 33. Operation Registers - Add-On Interface                                                 | 69 |

| Table 34. Mailbox Empty/Full Status Register                                                     | 72 |

| Table 35. Interrupt Control Status Register                                                      | 74 |

| Table 36. Reset General Control/Status Register                                                  | 76 |

| Table 37. Pass-thru Configuration Register                                                       | 78 |

## LIST OF TABLES

| Table 38. Valid External Boot Memory Contents                                                                                                          | 80  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 39. PC Compatible Expansion ROM                                                                                                                  | 87  |

| Table 40. PCI Data Structure                                                                                                                           | 89  |

| Table 41. PCI Bus Commands                                                                                                                             | 92  |

| Table 42. Target Termination Type                                                                                                                      | 96  |

| Table 43. Byte Lane Steering for PCI Write (Add-On Read)                                                                                               | 125 |

| Table 44. Byte Lane Steering for PCI Read (Add-On Write)                                                                                               | 125 |

| Table 45. Showing Big Endian Conversion for 32-bit                                                                                                     | 129 |

| Table 46. Big Endian conversion for a 16-bit bus. The S5320 drives D[15:0] only                                                                        | 129 |

| Table 47. Big Endian conversion for an 8-bit bus. The S5320 drives D[7:0] only                                                                         | 129 |

| Table 48. Absolute Maximum Stress Ratings                                                                                                              | 141 |

| Table 49. Recommended Operating Conditions                                                                                                             | 141 |

| Table 50. PCI Signal DC Characteristics (V <sub>CC</sub> = 3.3V ± 5%, 0°C to 70°C, 50 pF load on outputs)                                              | 142 |

| Table 51. Add-On Operating Characteristics ( $V_{CC} = 3.3V \pm 5\%$ , 0°C to 70°C, 50 pF load on outputs)                                             | 143 |

| Table 52. Functional Operation Range<br>(V <sub>CC</sub> = 3.3V ± 5%, 0°C to 70°C, 50 pF load on outputs for MAX, 0 pF load for MIN)                   | 144 |

| Table 53. Add-On Timings, Functional Operation Range<br>(V <sub>CC</sub> = 3.3V ± 5%, 0°C to 70°C, 50 pF load on outputs for MAX, 0 pF load for MIN)   | 146 |

| Table 54. Add-On Timings<br>Functional Operation Range (V <sub>CC</sub> = 3.3V ± 5%, 0°C to 70°C, 50 pF load on outputs for MAX,<br>0 pF load for MIN) | 150 |

| Table 55. Mailbox Timings<br>Functional Operation Range ( $V_{CC}$ = 3.3V ± 5%, 0°C to 70°C, 50 pF load on outputs)                                    | 152 |

## ARCHITECTURAL OVERVIEW \$5320

Since the S5320 is a PCI Target or Slave device only, its cost is significantly less than PCI Bus Master solutions. The S5320 is PCI purposed 2.2 compliant and can support data transfer rates up to 132 Mbytes/sec. Burst transfers and single data transfers are both supported. Figure 1 shows the block diagram for the S5320.

Many additional S5320 features offer the user easier hardware and software implementation. Up to four memory or I/O size definable blocks, referred to as Pass-Thru regions, are provided for multiple device configurations. Data transfers via a Pass-Thru region can be performed either direct to the Add-On bus or through two 32-Byte burstable FIFOs. Added read prefetch and programmable FIFO wait state features allow the user to tune system performance. The Pass-Thru data channel also supports an active/passive mode bus interface. Passive mode requires the designer to transfer data by externally driving the Add-On bus. Active mode minimizes design components by enabling internal logic to drive or acquire the Add-On bus to read or write data independently. Active mode provides programmable wait state generation for slower Add-On designs.

Two 32-bit mailbox registers are implemented for additional data or user-defined status/command transfers. Each mailbox may be examined for empty or full, at the byte level, through a mailbox status register. Mailbox transfers can be either register style or hardware direct. Dedicated external mailbox data and strobe pins are provided for direct hardware read/writes and allow Add-On to PCI interrupt capabilities. A direct Add-On to a PCI bus interrupt pin is incorporated, adding design flexibility.

The S5320 supports a two-wire serial nvRAM. This allows the designer to customize the device configuration to be loaded during power-up initialization. An expansion BIOS may also be contained in the nvRAM.

## S5320 REGISTER ARCHITECTURE

S5320 communications, control and configuration is performed through three primary groups of registers: PCI Configuration Registers, PCI Operation Registers and Add-On Operation Registers. All of these registers are user configurable through their associated buses and from the external nvRAM. The following sections provide a brief overview of each register group and the nvRAM interface.

#### **PCI Configuration Registers**

All PCI compliant devices are required to provide a group of PCI configuration registers. These registers are polled by the host BIOS system during power-up initialization. They contain specific device and product information such as Vendor ID, Device ID, Subsystem Vendor ID, memory requirements, etc. These registers are located in the S5320 and are either initialized with predefined default values or user customized definitions contained in the external nvRAM.

#### PCI Bus Accessible Registers

The second group of registers are the PCI Operation Registers. This group of registers is accessible to the PCI Bus. These are the primary registers through which the PCI Host configures the S5320 operation and communicates with the Add-On Bus. These registers encompass the PCI bus mailboxes, Pass-Thru/ FIFO data channel and Status/ Control registers.

#### Add-On Bus Accessible Registers

The last register group consists of the Add-On Operation Registers. This group of registers is accessible via the Add-On Bus. These are the primary registers through which the Add-On application configures S5320 operation and communicates with the PCI Bus. These registers encompass the Add-On bus mailboxes, Pass-Thru/FIFO Registers and Status/Control Registers.

## SERIAL NON-VOLATILE INTERFACE

Previously indicated, the S5320 contains the required set of PCI Configuration Registers. These registers can be initialized with default values or with customized values contained in an external nvRAM. The nvRAM allows Add-On card manufacturers to initialize the S5320 with their specific Vendor ID values, along with other desired S5320 operation characteristics.

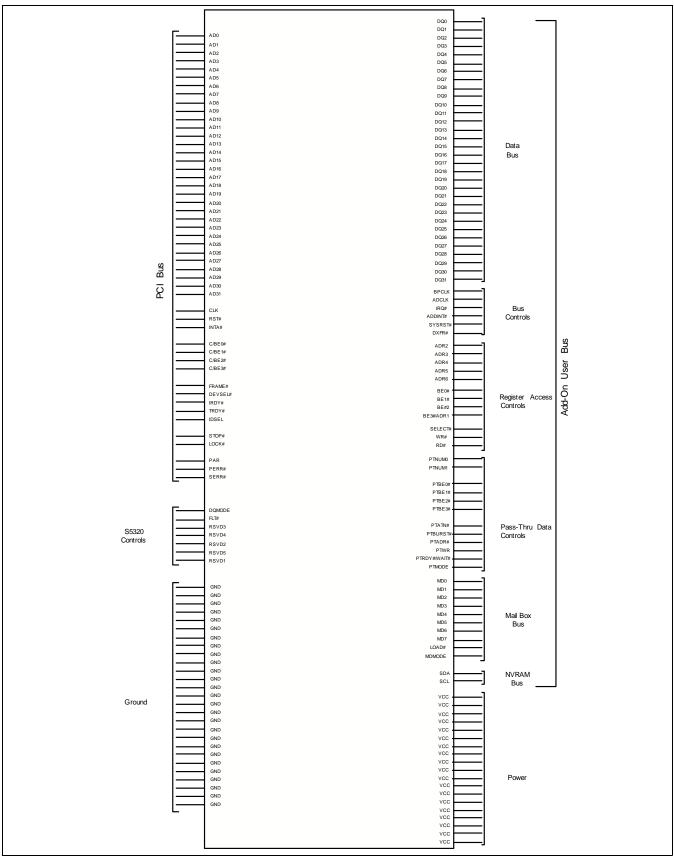

#### Figure 2. S5320 Pinout

### MAILBOX OPERATION

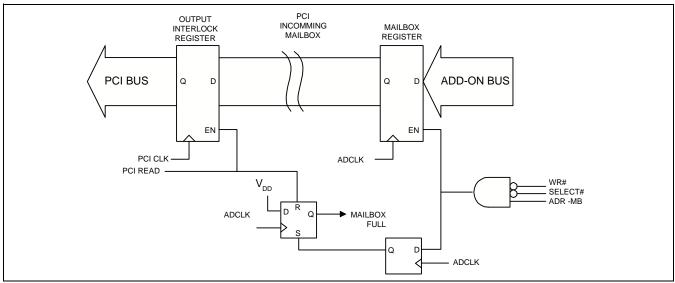

The mailbox registers are divided into two 4-byte sets. Each set is dedicated to one bus for data transfer to the other bus. Figure 3 shows a block diagram of the mailbox section of the S5320. The provision of mailbox registers provides data or user defined command/status transfer capability between two buses. An empty/ full indication for each mailbox register, at the byte level, is determined by polling a status register accessible to both the PCI and Add-On buses. Providing mailbox byte level full indications allows greater flexibility in 8-, 16-or 32-bit designs; i.e., transferring a single byte in 8-bit Add-On bus without requiring the assembly or disassembly of 32-bit data.

A mailbox byte level interrupt feature for PCI or Add-On buses is provided. Bit locations configured within the S5320 operation registers can select which mailbox byte is to generate an interrupt when the mailbox is written to. Interrupts can be generated to the PCI or Add-On buses. PCI bus interrupts may also be generated from direct hardware interfacing due to a unique S5320 feature. The Add-On mailbox is hardware accessible via a set of dedicated device pins. A single load pulse latches data into the mailbox generating an interrupt, if enabled.

## **PASS-THRU OPERATION**

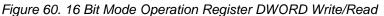

Pass-Thru region accesses can execute PCI bus cycles in real time or through an internal FIFO. Real time operation allows the PCI bus to directly read or write to Add-On bus resources. The S5320 allows the designer to declare up to four individual Pass-Thru regions. Each region may be defined as 8, 16 or 32 bits wide, mapped into memory or I/O system space and may be up to 512 MB in size. Figure 4 shows a basic block diagram of the S5320 Pass-Thru architecture.

Host communications to the Pass-Thru data channel utilizes dedicated Add-On bus pins to signal that a PCI read or write has been requested. User logic decodes these signals to determine if it must read or write data to the S5320 to satisfy the PCI request. Information decoded includes: PCI read/write transaction request, the byte lanes involved, the specific Pass-Thru region accessed and whether the request is a burst or single cycle access.

Pass-Thru operation supports single PCI data cycles and PCI data bursts. During PCI burst operations, the S5320 is capable of transferring data at the full PCI bandwidth. Should slower Add-On logic be implemented, the S5320 will issue a PCI bus retry until the requested transfer is completed.

Figure 3. Mailbox Block Diagram

#### To increase data throughput, the Pass-Thru channel incorporates two 32-byte FIFOs. One FIFO is dedicated to PCI read data while the other is dedicated to PCI write data. Enabling the write FIFO allows the S5320 to accept zero wait state bursts from the PCI bus regardless of the Add-On bus application design speed. Figure 4 illustrates the Pass-Thru block.

Enabling the read FIFO allows data to be optionally prefetched from the Add-On Bus. This can greatly improve performance of slow Add-On bus designs. PCI read cycles can be performed with zero wait states since data has been prefetched into the FIFO. Either of the write/read FIFOs can be disabled or enabled to tune system performance.

The Add-On bus can be operated in two different modes: active or passive. The passive mode of operation mimics that of the S5335 Add-On bus operation. The user design drives S5320 pins to read or write data. In active mode, the Add-On bus is driven from an S5320 internal state machine. This reduces component count in cost-sensitive designs. Active mode also incorporates programmable wait states from 0 to 7.

Figure 4. Pass-Thru Block Diagram

#### **Signal Type Definitions**

The following signal types are taken from the PCI Bus Specification.

- in Input is a standard input-only signal.

- out Totem Pole Output is a standard active driver.

- t/s Tri-State ®is a bi-directional, tri-state input/output pin.

- s/t/s Sustained Tri-State is an active low tri-state signal owned and driven by one and only one agent at a time. The agent that drives an s/t/s pin low must drive it high for at least one clock before letting it float. A new agent cannot start driving an s/t/s signal any sooner than one clock after the previous owner tri-states it. A pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central source.

- o/d Open Drain allows multiple devices to share as a wire-OR.

Each signal that assumes the logic low state when asserted is followed by the pound sign (#). Example: TRDY# signal is asserted low when the target is ready to complete a data transfer. Signals that are not followed by the pound sign are asserted when they assume the logic high state.

The following designations are used throughout this book when referring to the size of data objects:

A BYTE is an 8-bit object.

A WORD is a 16-bit, or 2-byte object.

A DWORD is a double word and is a 32-bit or 4-byte object.

All hex numbers are followed by an "h". Examples:

9A4Fh

0110h

All binary numbers are followed by an "b". Examples:

1010b

0110b

All decimal numbers are followed by an "d". Examples:

4356d

1101d

Note:  $Tri-State^{\ensuremath{\mathbb{B}}}$  is a Registered Trademark of National Semiconductor.

#### Figure 5. S5320 Signal Assignment

## PCI BUS SIGNALS

The following sets of signals represent the interface pins available for the S5320 to PCI bus.

Table 1. PCI Bus Address and Data Signal

| Signal     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                             |  |

|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--|

| AD[31:0]   | t/s  | Address/Data. Address and data are multiplexed on the same PCI bus pins. A PCI bus transaction consists of an address phase followed by one or more data phases. An address phase occurs on the PCLK cycle in which FRAME# is asserted. A data phase occurs on the PCLK cycles in which IRDY# and TRDY# are both asserted.                                                                                                                                                                                                   |                             |  |

| C/BE[3:0]# | in   | Command/Byte Enable. Bus commands and byte enables are multiplexed on the same pins. These pins define the current bus command during an address phase. During a data phase, these pins are used as Byte Enables, with C/BE[0]# enabling byte 0 (LSB) and C/BE[3]# enabling byte 3 (MSB).                                                                                                                                                                                                                                    |                             |  |

|            |      | C/BE[3:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Command Type                |  |

|            |      | 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Interrupt Acknowledge       |  |

|            |      | 0001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Special Cycle               |  |

|            |      | 0010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O Read                    |  |

|            |      | 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | I/O Write                   |  |

|            |      | 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved                    |  |

|            |      | 0101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved                    |  |

|            |      | 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory Read                 |  |

|            |      | 0111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory Write                |  |

|            |      | 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved                    |  |

|            |      | 1001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Reserved                    |  |

|            |      | 1010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Configuration Read          |  |

|            |      | 1011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Configuration Write         |  |

|            |      | 1100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory Read Multiple        |  |

|            |      | 1101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Dual Address Cycle          |  |

|            |      | 1110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory Read Line            |  |

|            |      | 1111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory Write and Invalidate |  |

| PAR        | t/s  | Parity. Parity is always driven as even from all AD[31:0] and C/BE[3:0]# signals. The parity is valid dur-<br>ing the clock following the address phase and is driven by the bus master. During a data phase for<br>write transactions, the bus master sources this signal on the clock following IRDY# active; during a<br>data phase for read transactions, this signal is driven by the target and is valid on the clock following<br>TRDY# active. The PAR signal has the same timing as AD[31:0], delayed by one clock. |                             |  |

#### Table 2. PCI Bus System Signals

| Signal | Туре | Description                                                                                                                                                                                                                                                    |

|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK   | in   | PCI Clock. The rising edge of this signal is the reference upon which all other signals are based except for RST# and INTA#. The maximum PCLK frequency for the S5320 is 33 MHz and the minimum is DC (0 Hz).                                                  |

| RST#   | in   | Reset brings the S5320 to a known state:<br>- All PCI bus output signals tri-stated.<br>- All open drain signals (i.e., SERR#) floated.<br>- All registers set to their factory defaults.<br>- Pass-Thru is returned to an idle state.<br>- All FIFOs emptied. |

Table 3. PCI Bus Data Transfer Control Signals

| Signal  | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FRAME#  | in    | Frame. This signal is driven by the current bus master to indicate the beginning and duration of a bus transaction. When FRAME# is first asserted, it indicates a bus transaction is beginning with a valid addresses and bus command present on AD[31:0] and C/BE[3:0]. Data transfers continue while FRAME# is asserted. FRAME# de-assertion indicates the transaction is in a final data phase or has completed. |

| IRDY#   | in    | Initiator Ready. This signal is always driven by the bus master to indicate its ability to complete the cur-<br>rent data phase. During write transactions, it indicates AD[31:0] contains valid data.                                                                                                                                                                                                              |

| TRDY#   | s/t/s | Target Ready. This signal is driven by the selected target to indicate the target is able to complete the current data phase. During read transactions, it indicates AD[31:0] contains valid data. Wait states occur until both TRDY# and IRDY# are asserted together.                                                                                                                                              |

| STOP#   | s/t/s | Stop. The Stop signal is driven by a selected target and conveys a request to the bus master to stop the current transaction.                                                                                                                                                                                                                                                                                       |

| LOCK#   | in    | Lock. The lock signal provides for the exclusive use of a resource. The S5320 may be locked by one master at a time.                                                                                                                                                                                                                                                                                                |

| IDSEL   | in    | Initialization Device Select. This pin is used as a chip select during configuration read or write transac-<br>tions.                                                                                                                                                                                                                                                                                               |

| DEVSEL# | s/t/s | Device Select. This signal is driven by a target decoding and recognizing its bus address. This signal informs a bus master whether an agent has decoded a current bus cycle.                                                                                                                                                                                                                                       |

| INTA#   | o/d   | Interrupt A. This signal is defined as optional and level sensitive. Driving it low will interrupt to the host.<br>The INTA# interrupt is to be used for any single function device requiring an interrupt capability.                                                                                                                                                                                              |

| Signal | Туре  | Description                                                                                                                                                                                                                                                                                                           |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PERR#  | s/t/s | Parity Error. Only for reporting data parity errors for all bus transactions except for Special Cycles. It is driven by the agent receiving data two clock cycles after the parity was detected as an error. This signal is driven inactive (high) for one clock cycle prior to returning to the tri-state condition. |

| SERR#  | o/d   | System Error. Used to report address and data parity errors on Special Cycle commands and any other error condition having a catastrophic system impact. Special Cycle commands are not supported by the S5320.                                                                                                       |

## ADD-ON BUS AND \$5320 CONTROL SIGNALS

The following sets of signals represent the interface signals available for the user Add-On bus and S5320 control.

#### Table 5. Serial nvRAM Interface Signals

| Signal | Туре    | Description                                                                                                                                                                                                                                                                                       |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCL    | o/d-out | Serial Clock. This clock provides timing for all transactions on the two-wire serial bus. The S5320 drives this signal when performing as a serial bus master. SCL operates at the maximum allowable clock speed and enters the high Z state when FLT# is asserted or the serial bus is inactive. |

| SDA    | o/d     | Serial Data/Address. This bi-directional signal carries serial address and data information between nvRAMs and the S5320. This pin enters high Z state when FLT# is asserted or the serial bus is inactive.                                                                                       |

#### Table 6. Direct Mailbox Access Signals

| Signal  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDMODE  | in   | Mailbox Data Mode. The MD[7:0] signal pins are always inputs when this signal is high. The MD[7:0] signal pins are defined as inputs and outputs under LOAD# control when MDMODE is low. This pin is provided for software compatibility with the S5335. New designs should permanently connect this signal low. This signal is connected to an internal 50k Ohm pull-up.           |

| LOAD#   | in   | MD[7:0] is defined as an input bus when this signal is low. The next rising edge of the ADCLK will latch MD[7:0] data into byte three of the Add-On outgoing mailbox. When LOAD# is high and MDMODE is low, MD[7:0] are defined as outputs displaying byte three of the PCI outgoing mailbox. This signal is connected to an internal 50k Ohm pull-up.                              |

| MD[7:0] | t/s  | Mailbox Data bus. The mailbox data registers can be directly accessed using the LOAD# and MDMODE signals. When configured as an input, data byte three of the PCI incoming mailbox is directly written to from these pins. When configured as an output, data byte three of the PCI outgoing mailbox is output to these pins. All MD[7:0] signals have an internal 50k Ohm pull-up. |

## **USER ADD-ON BUS PIN DESCRIPTIONS**

The following sets of signals represent the interface pins available for the Add-On bus. The following defines three signal groups: S5320 register access signals, Pass-Thru channel signals, and general Add-On bus signals.

| Signal       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PTMODE       | in   | Pass-Thru Mode. Configures the Pass-Thru data channel operation. High configures the S5320 in Passive mode allowing other devices to read/write data bus data. Low configures the S5320 in Active mode. This mode allows the S5320 to actively drive signals and data onto the data bus. This signal is connected to an internal 50k Ohm pull-up.                                                                                  |

| PTATN#       | out  | Pass-Thru Attention. Signals a decoded PCI to Pass-Thru region bus cycle. PTATN# is generated to signal that Add-On logic Pass-Thru data must be read from or written to the S5320.                                                                                                                                                                                                                                                |

| PTBURST#     | out  | Pass-Thru Burst. Informs the Add-On bus that the current Pass-Thru region decoded PCI bus cycle is a burst access.                                                                                                                                                                                                                                                                                                                 |

| PTRDY#/WAIT# | in   | Pass-Thru Ready/Pass-Thru Wait. During passive mode, the signal is referred to as PTRDY# and is asserted low to indicate Add-On logic has read/written data in response to a PTATN# signal. During active mode operation, the signal is referred to as WAIT# and can be driven low to insert wait states or hold the S5320 from clocking data onto the data bus. PTRDY# or WAIT# is synchronous to ADCLK.                          |

| PTNUM[1:0]   | out  | Pass-Thru Number. Identifies which of the four Pass-Thru regions the PTATN# read/write is requesting. Only valid for the duration of PTATN# active. 00 = Base Address Register 1, 01 = Base Address Register 2, 10 = Base Address Register 3, 11 = Base Address Register 4.                                                                                                                                                        |

| PTBE[3:0]#   | out  | Pass-Thru Byte Enables. During a PCI to Pass-Thru read, PTBE[3:0] indicate which bytes of a DWORD are to be written into. During a PCI to Pass-Thru write, these pins indicate which bytes of a DWORD are valid to read. PTBE[3:0]# are only valid while PTATN# is asserted.                                                                                                                                                       |

| PTADR#       | t/s  | Pass-Thru Address. Is an input when in passive mode. When asserted, the 32-bit Pass-Thru address register contents are driven onto the DQ[31:0] bus. All other Add-On control signals must be inactive during the assertion of PTADR# in passive mode. In active mode, becomes an output and indicates a Pass-Thru address is on the DQ bus. The DQMODE signal does not affect DQ bus width while the Pass-Thru address is driven. |

| PTWR         | out  | Pass-Thru Write. This signal indicates whether the current PCI to Pass-Thru bus transaction is a read or write cycle. Valid only when PTATN# is active.                                                                                                                                                                                                                                                                            |

| DXFER#       | out  | ACTIVE Transfer complete. When in ACTIVE mode, this output is asserted at the end of every 8-<br>16- or 32-bit data transfer cycle. This signal is not used in Passive mode.                                                                                                                                                                                                                                                       |

Table 7. Pass-Thru Data Channel Pins

| Signal      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                          |                                                    |

|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| DQ[31:0]    | t/s  | Address/Data bus. The 32-bit Add-On data bus. The DQMODE signal configures the bus width for either 32 or 16 bits. All DQ[31:0] signals have an internal 50k Ohm pull-ups.                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                          |                                                    |

| ADR[6:2]    | in   | Address [6:2]. These inputs select which S5320 register is to be read from or written to. To be used in conjunction with SELECT#, BE[3:0]# and WR# or RD#. The register addresses are as follows:                                                                                                                                                                                        |                                                                                                                                                                                                                                                                          |                                                    |

|             |      | ADR[6:2]                                                                                                                                                                                                                                                                                                                                                                                 | Register Name                                                                                                                                                                                                                                                            |                                                    |

|             |      | 00011                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Incoming Mailbox Register                                                                                                                                                                                                                                         |                                                    |

|             |      | 00111                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Outgoing Mailbox Register                                                                                                                                                                                                                                         |                                                    |

|             |      | 01010                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Pass-Thru Address Register                                                                                                                                                                                                                                        |                                                    |

|             |      | 01011                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Pass-Thru Data Register                                                                                                                                                                                                                                           |                                                    |

|             |      | 01101                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Mailbox Status Register                                                                                                                                                                                                                                           |                                                    |

|             |      | 01110                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Interrupt Control Register                                                                                                                                                                                                                                        |                                                    |

|             |      | 01111                                                                                                                                                                                                                                                                                                                                                                                    | Add-On Reset ControlRegister                                                                                                                                                                                                                                             |                                                    |

|             |      | 10000                                                                                                                                                                                                                                                                                                                                                                                    | Pass-Thru/FIFO Configuration Register                                                                                                                                                                                                                                    |                                                    |

|             |      |                                                                                                                                                                                                                                                                                                                                                                                          | ts begin at bit position two. All references to an address, i<br>e: The Add-On incoming mailbox register is referenced as                                                                                                                                                |                                                    |

| BE[2:0]#    | in   | Byte Enable 2 through 0. Provides individual read/write byte enabling during register read or write transactions. BE2# enables activity over DQ[23:16], BE1# enables DQ[15:8], and BE0# enables DQ[7:0]. During read transactions, these pins enable the output driver for each byte lane; for write transactions, they serve as an input enable to perform the write to each byte lane. |                                                                                                                                                                                                                                                                          |                                                    |