# PIC16LC74B-16/PTL16

# 8-Bit CMOS Microcontrollers with A/D Converter

### PIC16LC74B-16/PTL16 Microcontroller Core Features:

- High-performance RISC CPU

- Specially tested

- 16MHz @ 3V

- Only 35 single word instructions to learn

- All single cycle instructions except for program branches which are two cycle

- Operating speed: DC 16 MHz clock input DC - 250 ns instruction cycle

- 4K x 14 words of Program Memory, 192 x 8 bytes of Data Memory (RAM)

- · Interrupt capability

- Eight level deep hardware stack

- Direct, indirect and relative addressing modes

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Watchdog Timer (WDT) with its own on-chip RC oscillator for reliable operation

- Programmable code-protection

- Power saving SLEEP mode

- Selectable oscillator options

- Low-power, high-speed CMOS EPROM technology

- Wide operating voltage range: 2.5V to 5.5V

- High Sink/Source Current 25/25 mA

- Commercial, Industrial and Automotive temperature ranges

- Low-power consumption:

- < 5 mA @ 5V, 4 MHz

- 23 μA typical @ 3V, 32 kHz

- < 3 µA typical standby current

### **Peripheral Features:**

- Timer0: 8-bit timer/counter with 8-bit prescaler

- Timer1: 16-bit timer/counter with prescaler can be incremented during sleep via external crystal/clock

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM module(s)

- Capture is 16 bit, max. resolution is 15.6 ns

- Compare is 16 bit, max. resolution is 250 ns

- PWM max. resolution is 10 bit

- 8-bit multichannel analog-to-digital converter

- Synchronous Serial Port (SSP) with SPI<sup>™</sup> and I<sup>2</sup>C<sup>™</sup>

- Universal Synchronous Asynchronous Receiver Transmitter (USART/SCI)

- Parallel Slave Port (PSP), 8-bits wide, with external RD, WR and CS controls

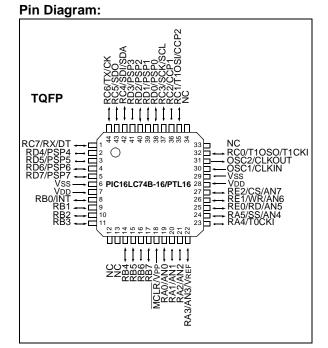

- Brown-out detection circuitry for Brown-out Reset (BOR) Pin Diagrams

### Table of Contents

| 1.0 0 | General Description                         | 3    |

|-------|---------------------------------------------|------|

| 2.0 E | Electrical Characteristics                  | 5    |

|       | DC and AC Characteristics Graphs and Tables |      |

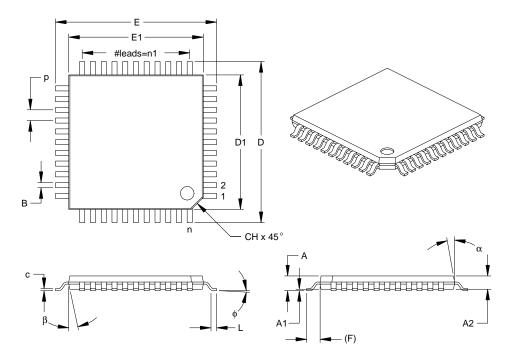

| 4.0 F | Packaging Information                       | . 29 |

|       | <pre></pre>                                 |      |

| On-L  | ine Support                                 | . 35 |

| Read  | ler Response                                | . 36 |

|       | uct Identification System                   |      |

### To Our Valued Customers

### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number. e.g., DS30000A is version A of document DS30000.

### Errata

An errata sheet may exist for current devices, describing minor operational differences (from the data sheet) and recommended workarounds. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (602) 786-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Corrections to this Data Sheet**

We constantly strive to improve the quality of all our products and documentation. We have spent a great deal of time to ensure that this document is correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error, please:

- Fill out and mail in the reader response form in the back of this data sheet.

- E-mail us at webmaster@microchip.com.

We appreciate your assistance in making this a better document.

# 1.0 GENERAL DESCRIPTION

This data sheet covers the PIC16LC74B-16/PTL16 device. The functional characteristics of this device are identical to the PIC16LC74B. For electrical specifications, see the electrical specifications contained within this document. For all other information about this device, see the PIC16C63A/65B/73B/74B data sheet (DS30605).

NOTES:

# 2.0 ELECTRICAL CHARACTERISTICS

# Absolute Maximum Ratings (†)

| Ambient temperature under bias                                                                                                                                                                                        |                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|

| Storage temperature                                                                                                                                                                                                   | 65°C to +150°C                     |

| Voltage on any pin with respect to Vss (except VDD, MCLR, and RA4)                                                                                                                                                    | 0.3V to (VDD + 0.3V)               |

| Voltage on VDD with respect to Vss                                                                                                                                                                                    | 0.3V to +7.5V                      |

| Voltage on MCLR with respect to Vss (Note 2)                                                                                                                                                                          | 0V to +13.25V                      |

| Voltage on RA4 with respect to Vss                                                                                                                                                                                    | 0V to +8.5V                        |

| Total power dissipation (Note 1)                                                                                                                                                                                      | 1.0W                               |

| Maximum current out of Vss pin                                                                                                                                                                                        | 300 mA                             |

| Maximum current into VDD pin                                                                                                                                                                                          | 250 mA                             |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                                                                                                                                                         | ±20 mA                             |

| Output clamp current, Ioк (Vo < 0 or Vo > VDD)                                                                                                                                                                        | ±20 mA                             |

| Maximum output current sunk by any I/O pin                                                                                                                                                                            | 25 mA                              |

| Maximum output current sourced by any I/O pin                                                                                                                                                                         | 25 mA                              |

| Maximum current sunk by PORTA, PORTB, and PORTE (combined)                                                                                                                                                            | 200 mA                             |

| Maximum current sourced by PORTA, PORTB, and PORTE (combined)                                                                                                                                                         | 200 mA                             |

| Maximum current sunk by PORTC and PORTD (combined)                                                                                                                                                                    | 200 mA                             |

| Maximum current sourced by PORTC and PORTD (combined)                                                                                                                                                                 | 200 mA                             |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = VDD x {IDD - $\Sigma$ IOH} + $\Sigma$ {(VDD-V                                                                                                       | /OH) x IOH} + $\Sigma$ (VOI x IOL) |

| <b>Note 2:</b> Voltage spikes below Vss at the MCLR/VPP pin, inducing currents greater than 8 Thus, a series resistor of 50-100Ω should be used when applying a "low" level to than pulling this pin directly to Vss. |                                    |

| + NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause per                                                                                                                                  | Ũ                                  |

+ NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device, at those or any other conditions above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

# PIC16LC74B-16/PTL16

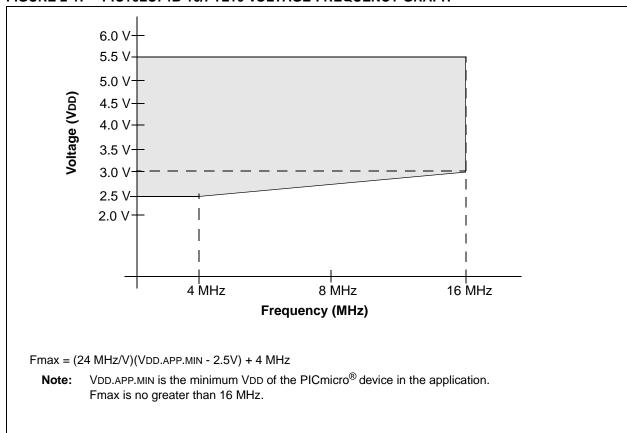

### FIGURE 2-1: PIC16LC74B-16/PTL16 VOLTAGE-FREQUENCY GRAPH

| DC CHA             | RACTE                          | RISTICS                                                                 | <b>Standa</b><br>Operatir |            |            |          | ons (unless otherwise stated)<br>$C \le TA \le +70^{\circ}C$ for commercial        |

|--------------------|--------------------------------|-------------------------------------------------------------------------|---------------------------|------------|------------|----------|------------------------------------------------------------------------------------|

| Param Sym C<br>No. |                                | Characteristic                                                          | Min                       | Тур†       | Max        | Units    | Conditions                                                                         |

| D001               | Vdd                            | Supply Voltage                                                          | 2.5<br>Vbor*              | -          | 5.5<br>5.5 | V<br>V   | RC, LP, XT, HS osc modes (DC - 4 MHz)<br>BOR enabled (Note 7)                      |

| D002*              | Vdr                            | RAM Data Retention<br>Voltage (Note 1)                                  | -                         | TBD        | -          | V        |                                                                                    |

| D003               | Vpor                           | <b>VDD Start Voltage</b> to<br>ensure internal<br>Power-on Reset signal | -                         | Vss        | -          | V        |                                                                                    |

| D004*<br>D004A*    | SVDD                           | <b>VDD Rise Rate</b> to<br>ensure internal<br>Power-on Reset signal     | 0.05<br>TBD               | -          | -          |          | PWRT enabled ( <u>PWRTE</u> bit clear)<br>PWRT disabled ( <u>PWRTE</u> bit set)    |

| D005               | VBOR                           | Brown-out Reset<br>voltage trip point                                   | 3.65                      | -          | 4.35       | V        | BODEN bit set                                                                      |

| D010               | Idd                            | Supply Current<br>(Note 2, 5)                                           | -                         | 2.0<br>3.0 | 3.8<br>6.0 | mA<br>mA | XT, RC osc modes<br>Fosc = 4 MHz, VDD = 3.0V (Note 4)<br>HS oscillator mode        |

| D010A              |                                |                                                                         | -                         | 22.5       | 48         | μA       | Fosc = 16MHz, VDD = 3.0V<br>LP osc mode<br>Fosc = 32 kHz, VDD = 3.0V, WDT disabled |

| D021               | Ipd                            | <b>Power-down Current</b> (Note 3, 5)                                   | -                         | 0.9        | 5          | μA       | VDD = 3.0V, WDT disabled, 0°C to +70°C                                             |

|                    |                                | Module Differential<br>Current (Note 6)                                 |                           |            |            |          |                                                                                    |

| D022*<br>D022A*    | $\Delta$ IWDT<br>$\Delta$ IBOR | Watchdog Timer<br>Brown-out Reset                                       | -                         | 6.0<br>350 | 20<br>425  | μΑ<br>μΑ | WDTE bit set, VDD = 4.0V<br>BODEN bit set, VDD = 5.0V                              |

### 2.1 DC Characteristics: PIC16LC74B-16/PTL-04 (Commercial)

\* These parameters are characterized but not tested.

- † Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: This is the limit to which VDD can be lowered without losing RAM data.

- 2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

- The test conditions for all IDD measurements in active operation mode are:

- OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD.

- MCLR = VDD; WDT enabled/disabled as specified.

- **3:** The power-down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc mode, current through Rext is not included. The current through the resistor can be estimated by the formula Ir = VDD/2Rext (mA) with Rext in kOhm.

- **5:** Timer1 oscillator (when enabled) adds approximately 20 μA to the specification. This value is from characterization and is for design guidance only. This is not tested.

- 6: The ∆ current is the additional current consumed when this peripheral is enabled. This current should be added to the base IDD or IPD measurement.

- 7: When BOR is enabled, the device will operate correctly until the VBOR voltage trip point is reached.

### 2.2 DC Characteristics: PIC16LC74B-16/PTL-04 (Commercial)

| DC CHA        | RACTE | RISTICS                            | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercialOperating voltage VDD range as described in DC spec Section 2.1 |      |                 |        |                                              |  |  |

|---------------|-------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------|--------|----------------------------------------------|--|--|

| Param<br>No.  | Sym   | Characteristic                     | Min                                                                                                                                                                                               | Тур† | Мах             | Units  | Conditions                                   |  |  |

|               | .,    | Input Low Voltage                  |                                                                                                                                                                                                   |      |                 |        |                                              |  |  |

| Dooo          | VIL   | I/O ports                          |                                                                                                                                                                                                   |      |                 |        |                                              |  |  |

| D030<br>D030A |       | with TTL buffer                    | Vss<br>Vss                                                                                                                                                                                        | -    | 0.15Vdd<br>0.8V | V<br>V | For entire VDD range<br>4.5V ≤ VDD ≤ 5.5V    |  |  |

| D030A         |       | with Schmitt Trigger buffer        | VSS                                                                                                                                                                                               | _    | 0.2VDD          | v      | 4.3 V 2 V 0 2 3.3 V                          |  |  |

| D032          |       | MCLR, OSC1 (in RC mode)            | Vss                                                                                                                                                                                               | -    | 0.2VDD          | v      |                                              |  |  |

| D033          |       | OSC1 (in XT, HS and LP<br>modes)   | Vss                                                                                                                                                                                               | -    | 0.3VDD          | v      | Note1                                        |  |  |

|               |       | Input High Voltage                 |                                                                                                                                                                                                   |      |                 |        |                                              |  |  |

|               | Viн   | I/O ports                          |                                                                                                                                                                                                   | -    |                 |        |                                              |  |  |

| D040          |       | with TTL buffer                    | 2.0                                                                                                                                                                                               | -    | Vdd             | V      | $4.5V \le VDD \le 5.5V$                      |  |  |

| D040A         |       |                                    | 0.25VDD<br>+ 0.8V                                                                                                                                                                                 | -    | Vdd             | V      | For entire VDD range                         |  |  |

| D041          |       | with Schmitt Trigger buffer        | 0.8Vdd                                                                                                                                                                                            | -    | Vdd             | V      | For entire VDD range                         |  |  |

| D042          |       | MCLR                               | 0.8Vdd                                                                                                                                                                                            | -    | Vdd             | V      |                                              |  |  |

| D042A         |       | OSC1 (XT, HS and LP modes)         | 0.7Vdd                                                                                                                                                                                            | -    | Vdd             | V      | Note1                                        |  |  |

| D043          |       | OSC1 (in RC mode)                  | 0.9Vdd                                                                                                                                                                                            | -    | Vdd             | V      |                                              |  |  |

|               |       | Input Leakage Current (Notes 2, 3) |                                                                                                                                                                                                   |      |                 |        |                                              |  |  |

| D060          | lı∟   | I/O ports                          | -                                                                                                                                                                                                 | -    | ±1              | μΑ     | $Vss \le VPIN \le VDD$ ,                     |  |  |

|               |       |                                    |                                                                                                                                                                                                   |      |                 |        | Pin at hi-impedance                          |  |  |

| D061          |       | MCLR, RA4/T0CKI                    | -                                                                                                                                                                                                 | -    | ±5              | μΑ     | $Vss \le VPIN \le VDD$                       |  |  |

| D063          |       | OSC1                               | -                                                                                                                                                                                                 | -    | ±5              | μA     | $Vss \leq VPIN \leq VDD,$                    |  |  |

| <b>D</b> 070  | 1     |                                    | 50                                                                                                                                                                                                | 050  | 400             | •      | XT, HS and LP osc modes                      |  |  |

| D070          | IPURB | PORTB weak pull-up current         | 50                                                                                                                                                                                                | 250  | 400             | μA     | VDD = 5V, VPIN = VSS                         |  |  |

| D080          | Vol   | Output Low Voltage<br>I/O ports    | -                                                                                                                                                                                                 | -    | 0.6             | V      | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C  |  |  |

|               |       |                                    | -                                                                                                                                                                                                 | -    | 0.6             | V      | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C |  |  |

| D083          |       | OSC2/CLKOUT (RC osc<br>mode)       | -                                                                                                                                                                                                 | -    | 0.6             | V      | IOL = 1.6 mA, VDD = 4.5V,<br>-40°C to +85°C  |  |  |

|               |       |                                    | -                                                                                                                                                                                                 | -    | 0.6             | V      | IOL = 1.2 mA, VDD = 4.5V,<br>-40°C to +125°C |  |  |

|               |       | Output High Voltage                |                                                                                                                                                                                                   |      |                 |        |                                              |  |  |

| D090          | Vон   | I/O ports (Note 3)                 | Vdd-0.7                                                                                                                                                                                           | -    | -               | V      | IOH = -3.0 mA, VDD = 4.5V,<br>-40°С to +85°С |  |  |

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as current sourced by the pin.

### 2.2 DC Characteristics: PIC16LC74B-16/PTL-04 (Commercial) (Cont.'d)

| DC CHA       | RACTE | RISTICS                                    | Standard Operating Conditions (unless otherwise stated)Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercialOperating voltage VDD range as described in DC spec Section 2.1 |      |     |       |                                                                         |  |

|--------------|-------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------------------------------------------------------------------------|--|

| Param<br>No. | Sym   | Characteristic                             | Min                                                                                                                                                                                               | Тур† | Max | Units | Conditions                                                              |  |

|              |       |                                            | VDD-0.7                                                                                                                                                                                           | -    | -   | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°С to +125°С                           |  |

| D092         |       | OSC2/CLKOUT (RC osc<br>mode)               | VDD-0.7                                                                                                                                                                                           | -    | -   | V     | IOH = -1.3 mA, VDD = 4.5V,<br>-40°С to +85°С                            |  |

|              |       |                                            | VDD-0.7                                                                                                                                                                                           | -    | -   | V     | IOH = -1.0 mA, VDD = 4.5V,<br>-40°C to +125°C                           |  |

| D150*        | Vod   | Open-Drain High Voltage                    | -                                                                                                                                                                                                 | -    | 8.5 | V     | RA4 pin                                                                 |  |

| <b>D</b> 400 | 0     | Capacitive Loading Specs<br>on Output Pins |                                                                                                                                                                                                   |      | 45  | _     |                                                                         |  |

| D100         | Cosc2 | OSC2 pin                                   | -                                                                                                                                                                                                 | -    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1. |  |

| D101         | Сю    | All I/O pins and OSC2 (in RC mode)         | -                                                                                                                                                                                                 | -    | 50  | pF    |                                                                         |  |

| D102         | Cb    | SCL, SDA in I <sup>2</sup> C mode          | -                                                                                                                                                                                                 | -    | 400 | pF    |                                                                         |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** In RC oscillator mode, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the device be driven with external clock in RC mode.

2: The leakage current on the MCLR/VPP pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

**3:** Negative current is defined as current sourced by the pin.

### 2.3 AC (Timing) Characteristics

### 2.3.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created using one of the following formats:

| 1. TppS2p             | pS                                     | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-----------------------|----------------------------------------|-----------|----------------------------------------|

| 2. TppS               |                                        | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                     |                                        |           |                                        |

| F                     | Frequency                              | т         | Time                                   |

| Lowerca               | ase letters (pp) and their meanings:   | ·         |                                        |

| рр                    |                                        |           |                                        |

| сс                    | CCP1                                   | osc       | OSC1                                   |

| ck                    | CLKOUT                                 | rd        | RD                                     |

| cs                    | CS                                     | rw        | RD or WR                               |

| di                    | SDI                                    | sc        | SCK                                    |

| do                    | SDO                                    | SS        | SS                                     |

| dt                    | Data in                                | tO        | TOCKI                                  |

| io                    | I/O port                               | t1        | T1CKI                                  |

| mc                    | MCLR                                   | wr        | WR                                     |

| Upperca               | ase letters and their meanings:        |           |                                        |

| S                     |                                        |           |                                        |

| F                     | Fall                                   | Р         | Period                                 |

| Н                     | High                                   | R         | Rise                                   |

| I                     | Invalid (Hi-impedance)                 | V         | Valid                                  |

| L                     | Low                                    | Z         | Hi-impedance                           |

| I <sup>2</sup> C only |                                        |           |                                        |

| AA                    | output access                          | High      | High                                   |

| BUF                   | Bus free                               | Low       | Low                                    |

| Tcc:st (              | (I <sup>2</sup> C specifications only) | ·         |                                        |

| CC                    |                                        |           |                                        |

| HD                    | Hold                                   | SU        | Setup                                  |

| ST                    |                                        |           |                                        |

| DAT                   | DATA input hold                        | STO       | STOP condition                         |

| STA                   | START condition                        |           |                                        |

### 2.3.2 TIMING CONDITIONS

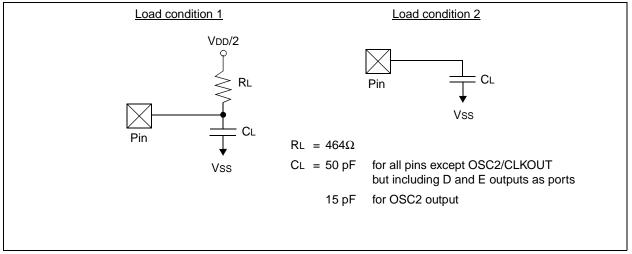

The temperature and voltages specified in Table 2-1 apply to all timing specifications unless otherwise noted. Figure 2-2 specifies the load conditions for the timing specifications.

### TABLE 2-1: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions (unless otherwise stated)                     |

|--------------------|-----------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial |

|                    | Operating voltage VDD range as described in DC spec Section 2.1.            |

|                    | LC parts operate for commercial/industrial temp's only.                     |

### FIGURE 2-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### 2.3.3 TIMING DIAGRAMS AND SPECIFICATIONS

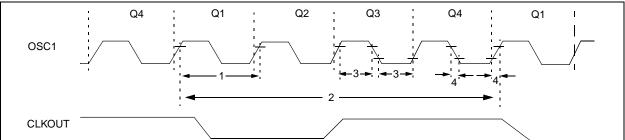

### FIGURE 2-3: EXTERNAL CLOCK TIMING

| Param<br>No. | Sym   | Characteristic                  | Min<br>(Note 2) | Тур† | Max<br>(Note 3) | Units | Conditions          |

|--------------|-------|---------------------------------|-----------------|------|-----------------|-------|---------------------|

| 1A           | Fosc  | External CLKIN Frequency        | DC              | —    | 4               | MHz   | RC and XT osc modes |

|              |       | (Note 1)                        | DC              |      | 4               | MHz   | HS osc mode (-04)   |

|              |       |                                 | DC              | _    | 20              | MHz   | HS osc mode (-20)   |

|              |       |                                 | DC              | _    | 200             | kHz   | LP osc mode         |

|              |       | Oscillator Frequency            | DC              | _    | 4               | MHz   | RC osc mode         |

|              |       | (Note 1)                        | 0.1             | _    | 4               | MHz   | XT osc mode         |

|              |       |                                 | 4               | _    | 20              | MHz   | HS osc mode         |

|              |       |                                 | 5               | _    | 200             | kHz   | LP osc mode         |

| 1            | Tosc  | External CLKIN Period           | 250             | _    |                 | ns    | RC and XT osc modes |

|              |       | (Note 3)                        | 250             | —    | —               | ns    | HS osc mode (-04)   |

|              |       |                                 | 50              | _    | —               | ns    | HS osc mode (-20)   |

|              |       |                                 | 5               | _    | —               | μs    | LP osc mode         |

|              |       | Oscillator Period               | 250             | _    | —               | ns    | RC osc mode         |

|              |       | (Note 3)                        | 250             | —    | 10,000          | ns    | XT osc mode         |

|              |       |                                 | 250             | —    | 250             | ns    | HS osc mode (-04)   |

|              |       |                                 | 50              | —    | 250             | ns    | HS osc mode (-20)   |

|              |       |                                 | 5               | —    | —               | μs    | LP osc mode         |

| 2            | Тсү   | Instruction Cycle Time (Note 1) | 200             | _    | DC              | ns    | TCY = 4/FOSC        |

| 3*           | TosL, | External Clock in (OSC1) High   | 100             | _    | —               | ns    | XT oscillator       |

|              | TosH  | or Low Time                     | 2.5             | —    | —               | μs    | LP oscillator       |

|              |       |                                 | 15              |      | —               | ns    | HS oscillator       |

| 4*           | TosR, | External Clock in (OSC1) Rise   | —               | _    | 25              | ns    | XT oscillator       |

|              | TosF  | or Fall Time                    | —               | —    | 50              | ns    | LP oscillator       |

|              |       |                                 | —               |      | 15              | ns    | HS oscillator       |

### TABLE 2-2: EXTERNAL CLOCK TIMING REQUIREMENTS

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time-base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption.

2: All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin.

3: When an external clock input is used, the "Max." cycle time limit is "DC" (no clock) for all devices.

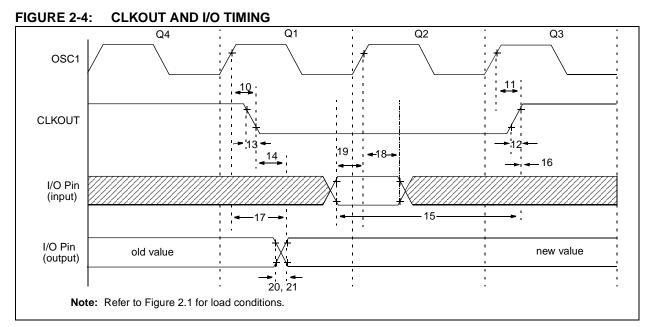

| TABLE 2-3: | <b>CLKOUT AND I/O TIMING REQUIREMENTS</b> |

|------------|-------------------------------------------|

|            |                                           |

| Param<br>No. | Sym      | Characteristic                                                        | Min        | Тур† | Max         | Units | Conditions |

|--------------|----------|-----------------------------------------------------------------------|------------|------|-------------|-------|------------|

| 10*          | TosH2ckL | OSC1 <sup>↑</sup> to CLKOUT↓                                          | —          | 75   | 200         | ns    | Note 1     |

| 11*          | TosH2ckH | OSC1↑ to CLKOUT↑                                                      | —          | 75   | 200         | ns    | Note 1     |

| 12*          | TckR     | CLKOUT rise time                                                      | —          | 35   | 100         | ns    | Note 1     |

| 13*          | TckF     | CLKOUT fall time                                                      | —          | 35   | 100         | ns    | Note 1     |

| 14*          | TckL2ioV | CLKOUT $\downarrow$ to Port out valid                                 | —          | -    | 0.5TCY + 20 | ns    | Note 1     |

| 15*          | TioV2ckH | Port in valid before CLKOUT ↑                                         | Tosc + 200 | -    | —           | ns    | Note 1     |

| 16*          | TckH2iol | Port in hold after CLKOUT ↑                                           | 0          | -    | —           | ns    | Note 1     |

| 17*          | TosH2ioV | OSC1 <sup>↑</sup> (Q1 cycle) to Port out valid                        | —          | 50   | 150         | ns    |            |

| 18A*         | TosH2iol | OSC1 <sup>↑</sup> (Q2 cycle) to Port input invalid (I/O in hold time) | 200        | -    | —           | ns    |            |

| 19*          | TioV2osH | Port input valid to OSC1↑ (I/O in setup time)                         | 0          | -    | —           | ns    |            |

| 20A*         | TioR     | Port output rise time                                                 | —          | -    | 80          | ns    |            |

| 21A*         | TioF     | Port output fall time                                                 | —          | _    | 80          | ns    |            |

| 22††*        | Tinp     | INT pin high or low time                                              | Тсү        | —    | —           | ns    |            |

| 23††*        | Trbp     | RB7:RB4 change INT high or low time                                   | Тсү        | _    | _           | ns    |            |

These parameters are characterized but not tested.

Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

these parameters are asynchronous events not related to any internal clock edge.

Note 1: Measurements are taken in RC mode where CLKOUT output is 4 x Tosc.

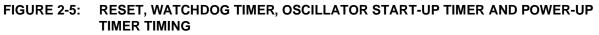

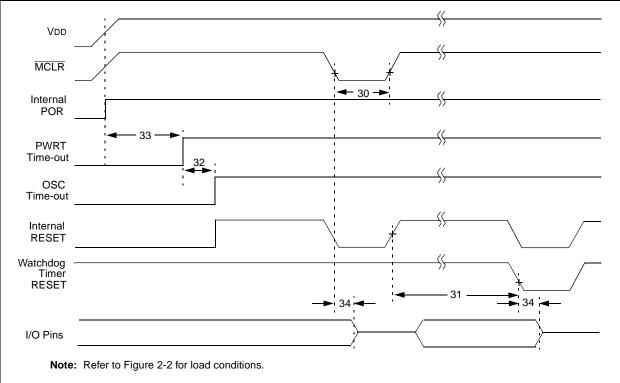

### FIGURE 2-6: BROWN-OUT RESET TIMING

# TABLE 2-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER<br/>AND BROWN-OUT RESET REQUIREMENTS

| Parameter | Sym   | Characteristic                                   | Min | Тур†      | Мах | Units | Conditions                |

|-----------|-------|--------------------------------------------------|-----|-----------|-----|-------|---------------------------|

| No.       |       |                                                  |     |           |     |       |                           |

| 30        | TmcL  | MCLR Pulse Width (low)                           | 2   | —         | _   | μs    | VDD = 5V, -40°C to +125°C |

| 31*       | Twdt  | Watchdog Timer Time-out Period<br>(No Prescaler) | 7   | 18        | 33  | ms    | VDD = 5V, -40°C to +125°C |

| 32        | Tost  | Oscillation Start-up Timer Period                | —   | 1024 Tosc | —   | -     | TOSC = OSC1 period        |

| 33*       | Tpwrt | Power-up Timer Period                            | 28  | 72        | 132 | ms    | VDD = 5V, -40°C to +125°C |

| 34        | Tioz  | I/O Hi-impedance from MCLR<br>Low or WDT reset   | —   | —         | 2.1 | μs    |                           |

| 35        | TBOR  | Brown-out Reset Pulse Width                      | 100 | —         | _   | μs    | VDD ≤ BVDD (D005)         |

These parameters are characterized but not tested.

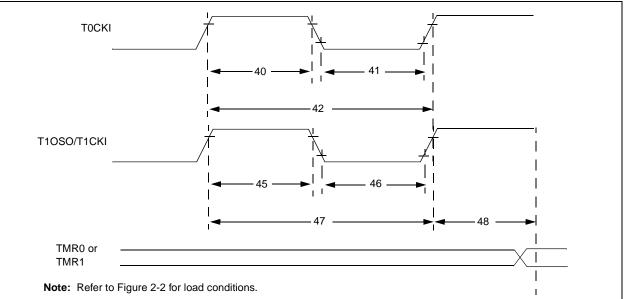

### FIGURE 2-7: TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS

| TABLE 2-5: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|------------|-----------------------------------------------|

|------------|-----------------------------------------------|

| Param<br>No. | Sym          | (                      | Characteristic                              |                   | Min                                              | Тур† | Max   | Units | Conditions                         |

|--------------|--------------|------------------------|---------------------------------------------|-------------------|--------------------------------------------------|------|-------|-------|------------------------------------|

| 40*          | Tt0H         | T0CKI High Pulse Width |                                             | No Prescaler      | 0.5TCY + 20                                      | —    |       | ns    | Must also meet                     |

|              |              |                        |                                             | With Prescaler    | 10                                               | _    | _     | ns    | parameter 42                       |

| 41*          | Tt0L         | T0CKI Low Pulse W      | /idth                                       | No Prescaler      | 0.5TCY + 20                                      | —    |       | ns    | Must also meet                     |

|              |              |                        |                                             | With Prescaler    | 10                                               | —    | _     | ns    | parameter 42                       |

| 42* Tt0P     | T0CKI Period |                        | No Prescaler                                | TCY + 40          | —                                                | —    | ns    |       |                                    |

|              |              |                        |                                             | With Prescaler    | Greater of:<br>20 or <u>Tcy + 40</u><br>N        | -    |       | ns    | N = prescale value<br>(2, 4,, 256) |

| 45*          | Tt1H         | T1CKI High Time        | Synchronous, Prescaler = 1                  |                   | 0.5TCY + 20                                      | —    | —     | ns    | Must also meet                     |

|              |              |                        | Synchronous, F                              | Prescaler = 2,4,8 | 25                                               | —    | _     | ns    | parameter 47                       |

|              |              |                        | Asynchronous                                |                   | 50                                               | —    |       | ns    |                                    |

| 46*          | Tt1L         | T1CKI Low Time         | Synchronous, Prescaler = 1                  |                   | 0.5TCY + 20                                      | —    |       | ns    | Must also meet                     |

|              |              |                        | Synchronous, F                              | Prescaler = 2,4,8 | 25                                               |      |       | ns    | parameter 47                       |

|              |              |                        | Asynchronous                                |                   | 50                                               | —    | —     | ns    |                                    |

| 47*          | Tt1P         | t1P T1CKI input period | Synchronous                                 |                   | <u>Greater of:</u><br>50 OR <u>TCY + 40</u><br>N |      |       |       | N = prescale value<br>(1, 2, 4, 8) |

|              |              |                        | Asynchronous                                | Asynchronous      |                                                  | —    | —     | ns    |                                    |

|              | Ft1          |                        | out frequency range by setting bit T1OSCEN) |                   | DC                                               | —    | 200   | kHz   |                                    |

| 48           | TCKEZtmr     | 1 Delay from external  | clock edge to ti                            | mer increment     | 2Tosc                                            | —    | 7Tosc | —     |                                    |

\* These parameters are characterized but not tested.

# PIC16LC74B-16/PTL16

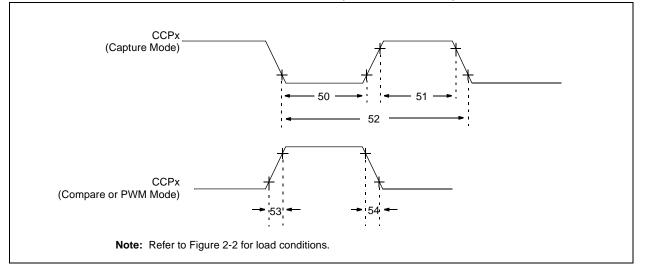

### FIGURE 2-8: CAPTURE/COMPARE/PWM TIMINGS (CCP1 AND CCP2)

### TABLE 2-6: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1 AND CCP2)

| Param<br>No. | Sym  |                               | Characteristic                 | Min         | Тур† | Max | Units | Conditions                        |

|--------------|------|-------------------------------|--------------------------------|-------------|------|-----|-------|-----------------------------------|

| 50* TccL     |      | CCP1 and CCP2                 | No Prescaler                   | 0.5Tcy + 20 | —    |     | ns    |                                   |

|              |      | input low time                | With Prescaler                 | 20          | _    | _   | ns    |                                   |

| 51* TccH     | TccH | CCP1 and CCP2 input high time | No Prescaler                   | 0.5Tcy + 20 | —    | _   | ns    |                                   |

|              |      |                               | With Prescaler                 | 20          | —    | _   | ns    |                                   |

| 52*          | TccP | CCP1 and CCP2 ir              | CP1 and CCP2 input period      |             | —    | _   | ns    | N = prescale value<br>(1,4 or 16) |

| 53*          | TccR | CCP1 and CCP2 of              | CCP1 and CCP2 output rise time |             | 25   | 45  | ns    |                                   |

| 54*          | TccF | CCP1 and CCP2 o               | CCP1 and CCP2 output fall time |             | 25   | 45  | ns    |                                   |

These parameters are characterized but not tested.

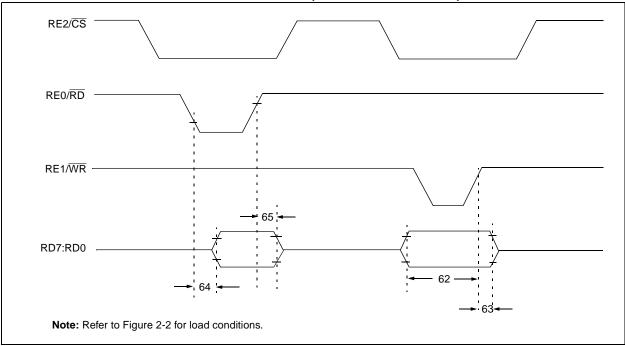

| TABLE 2-7: | PARALLEL SLAVE PORT REQUIREMENTS ( | (PIC16LC74B-16/PTL16) |

|------------|------------------------------------|-----------------------|

|            |                                    |                       |

| Parameter<br>No. | Sym      | Characteristic N                                                                        |    | Тур† | Max | Units | Conditions |

|------------------|----------|-----------------------------------------------------------------------------------------|----|------|-----|-------|------------|

| 62*              | TdtV2wrH | Data in valid before $\overline{WR}\uparrow$ or $\overline{CS}\uparrow$ (setup time)    | 20 | _    | _   | ns    |            |

| 63*              | TwrH2dtl | $\overline{WR}^{\uparrow}$ or $\overline{CS}^{\uparrow}$ to data–in invalid (hold time) | 35 | —    | _   | ns    |            |

| 64               | TrdL2dtV | $\overline{RD}\downarrow$ and $\overline{CS}\downarrow$ to data–out valid               | —  | —    | 80  | ns    |            |

| 65*              | TrdH2dtl | $\overline{RD}$ for $\overline{CS}$ for data-out invalid                                | 10 |      | 30  | ns    |            |

\* These parameters are characterized but not tested.

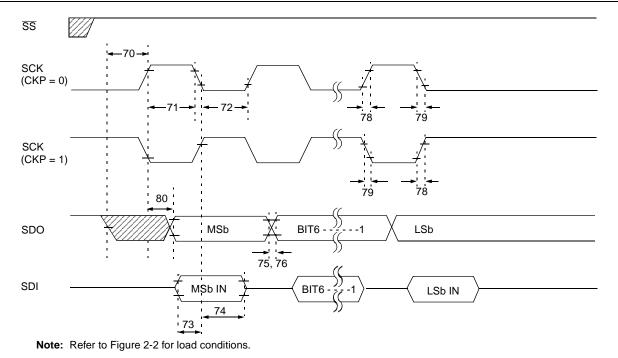

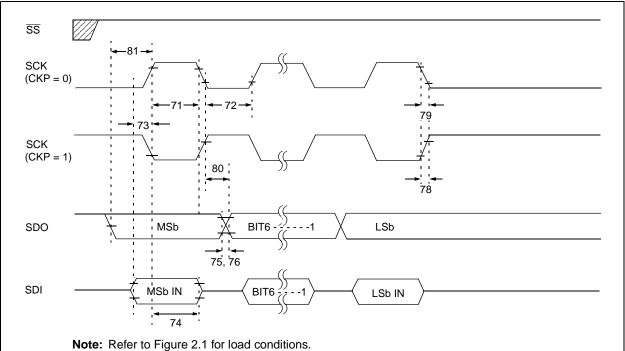

### FIGURE 2-10: EXAMPLE SPI MASTER MODE TIMING (CKE = 0)

### TABLE 2-8: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 0)

| Param.<br>No. | Symbol                | Characteris                                             | Characteristic |              | Тур† | Max | Units | Conditions |

|---------------|-----------------------|---------------------------------------------------------|----------------|--------------|------|-----|-------|------------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ inp                                 | ut             | Тсү          |      |     | ns    |            |

| 71            | TscH                  | SCK input high time                                     | Continuous     | 1.25Tcy + 30 | _    |     | ns    |            |

| 71A           |                       | (slave mode)                                            | Single Byte    | 40           |      | _   | ns    | Note 1     |

| 72            | TscL                  | SCK input low time                                      | Continuous     | 1.25Tcy + 30 |      | _   | ns    |            |

| 72A           |                       | (slave mode)                                            | Single Byte    | 40           | _    | _   | ns    | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                |                | 100          | —    |     | ns    |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2 |                | 1.5Tcy + 40  | —    |     | ns    | Note 1     |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data inpu                              | t to SCK edge  | 100          | —    |     | ns    |            |

| 75            | TdoR                  | SDO data output rise time                               |                | _            | 20   | 45  | ns    |            |

| 76            | TdoF                  | SDO data output fall time                               |                | _            | 10   | 25  | ns    |            |

| 78            | TscR                  | SCK output rise time (master mode)                      |                | _            | 20   | 45  | ns    |            |

| 79            | TscF                  | SCK output fall time (master mode)                      |                |              | 10   | 25  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDO data output valid afte                              | r SCK edge     | —            | _    | 100 | ns    |            |

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 2-9: EXAMPLE SPI MODE REQUIREMENTS (MASTER MODE, CKE = 1)

| Param.<br>No. | Symbol                | Characteris                                            | tic                                     | Min          | Тур† | Мах | Units | Conditions |

|---------------|-----------------------|--------------------------------------------------------|-----------------------------------------|--------------|------|-----|-------|------------|

| 71            | TscH                  | SCK input high time                                    | Continuous                              | 1.25Tcy + 30 | —    | —   | ns    |            |

| 71A           |                       | (slave mode)                                           | Single Byte                             | 40           | _    |     | ns    | Note 1     |

| 72            | TscL                  | SCK input low time                                     | Continuous                              | 1.25Tcy + 30 | —    |     | ns    |            |

| 72A           |                       | (slave mode)                                           | Single Byte                             | 40           | —    |     | ns    | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data in<br>edge                      | tup time of SDI data input to SCK       |              | _    | _   | ns    |            |

| 73A           | Тв2в                  | ast clock edge of Byte1 to the 1st clock edge of Byte2 |                                         | 1.5Tcy + 40  | _    | —   | ns    | Note 1     |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input                            | Hold time of SDI data input to SCK edge |              | _    | —   | ns    |            |

| 75            | TdoR                  | SDO data output rise time                              | 9                                       |              | 20   | 45  | ns    |            |

| 76            | TdoF                  | SDO data output fall time                              |                                         | —            | 10   | 25  | ns    |            |

| 78            | TscR                  | SCK output rise time (ma                               | ster mode)                              |              | 20   | 45  | ns    |            |

| 79            | TscF                  | SCK output fall time (mas                              | ter mode)                               | —            | 10   | 25  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDO data output valid after                            | er SCK edge                             |              |      | 100 | ns    |            |

| 81            | TdoV2scH,<br>TdoV2scL | SDO data output setup to                               | SCK edge                                | Тсү          |      | —   | ns    |            |

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

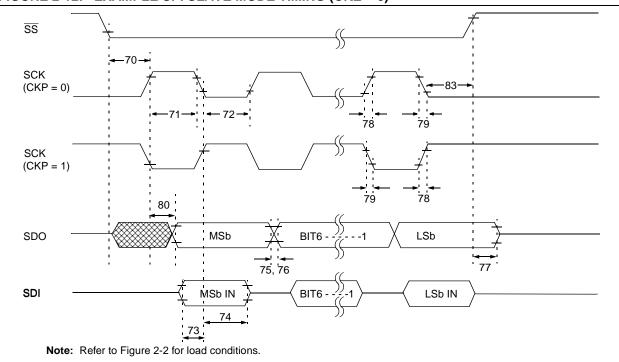

### FIGURE 2-12: EXAMPLE SPI SLAVE MODE TIMING (CKE = 0)

### TABLE 2-10: EXAMPLE SPI MODE REQUIREMENTS (SLAVE MODE TIMING (CKE = 0)

| Param.<br>No. | Symbol                | Characteris                                             | Characteristic                      |              | Тур† | Мах | Units | Conditions |

|---------------|-----------------------|---------------------------------------------------------|-------------------------------------|--------------|------|-----|-------|------------|

| 70            | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ inj                                 | put                                 | Тсү          | _    | —   | ns    |            |

| 71            | TscH                  | SCK input high time                                     | Continuous                          | 1.25Tcy + 30 | —    |     | ns    |            |

| 71A           |                       | (slave mode)                                            | Single Byte                         | 40           | —    |     | ns    | Note 1     |

| 72            | TscL                  | SCK input low time                                      | Continuous                          | 1.25Tcy + 30 | _    |     | ns    |            |

| 72A           |                       | (slave mode)                                            | Single Byte                         | 40           | —    |     | ns    | Note 1     |

| 73            | TdiV2scH,<br>TdiV2scL | Setup time of SDI data input to SCK edge                |                                     | 100          | _    | —   | ns    |            |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2 |                                     | 1.5Tcy + 40  | —    | —   | ns    | Note 1     |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                 |                                     | 100          | —    | —   | ns    |            |

| 75            | TdoR                  | SDO data output rise time                               | ;                                   |              | 20   | 45  | ns    |            |

| 76            | TdoF                  | SDO data output fall time                               |                                     | _            | 10   | 25  | ns    |            |

| 77            | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-imp                    | bedance                             | 10           | —    | 50  | ns    |            |

| 78            | TscR                  | SCK output rise time (mas                               | ster mode)                          |              | 20   | 45  | ns    |            |

| 79            | TscF                  | SCK output fall time (mas                               | ter mode)                           | _            | 10   | 25  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDO data output valid afte                              | DO data output valid after SCK edge |              |      | 100 | ns    |            |

| 83            | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                     |                                     | 1.5Tcy + 40  |      | —   | ns    |            |

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

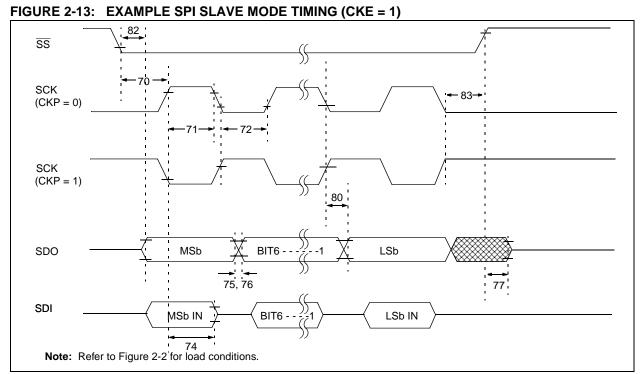

# TABLE 2-11: EXAMPLE SPI SLAVE MODE REQUIREMENTS (CKE = 1)

| Param.<br>No. | Symbol                | Characteri                                                        | stic                      | Min          | Тур† | Max | Units | Conditions |

|---------------|-----------------------|-------------------------------------------------------------------|---------------------------|--------------|------|-----|-------|------------|

| 70            | TssL2scH,<br>TssL2scL | $\overline{SS}\downarrow$ to SCK $\downarrow$ or SCK $\uparrow$ i | nput                      | Тсү          | —    |     | ns    |            |

| 71            | TscH                  | SCK input high time                                               | Continuous                | 1.25Tcy + 30 | _    |     | ns    |            |

| 71A           |                       | (slave mode)                                                      | Single Byte               | 40           |      | _   | ns    | Note 1     |

| 72            | TscL                  | SCK input low time                                                | Continuous                | 1.25Tcy + 30 | _    | _   | ns    |            |

| 72A           |                       | (slave mode)                                                      | Single Byte               | 40           |      | _   | ns    | Note 1     |

| 73A           | Тв2в                  | Last clock edge of Byte1 to the 1st clock edge of Byte2           |                           | 1.5Tcy + 40  | —    | _   | ns    | Note 1     |

| 74            | TscH2diL,<br>TscL2diL | Hold time of SDI data input to SCK edge                           |                           | 100          | —    | _   | ns    |            |

| 75            | TdoR                  | SDO data output rise tin                                          | ne                        |              | 20   | 45  | ns    |            |

| 76            | TdoF                  | SDO data output fall time                                         | e                         | _            | 10   | 25  | ns    |            |

| 77            | TssH2doZ              | SS <sup>↑</sup> to SDO output hi-in                               | npedance                  | 10           | —    | 50  | ns    |            |

| 78            | TscR                  | SCK output rise time (m                                           | aster mode)               |              | 20   | 45  | ns    |            |

| 79            | TscF                  | SCK output fall time (ma                                          | ster mode)                |              | 10   | 25  | ns    |            |

| 80            | TscH2doV,<br>TscL2doV | SDO data output valid after SCK edge                              |                           | —            | —    | 100 | ns    |            |

| 82            | TssL2doV              | SDO data output valid at                                          | fter <del>SS</del> ↓ edge |              | —    | 100 | ns    |            |

| 83            | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                                               |                           | 1.5Tcy + 40  | —    | —   | ns    |            |

† Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

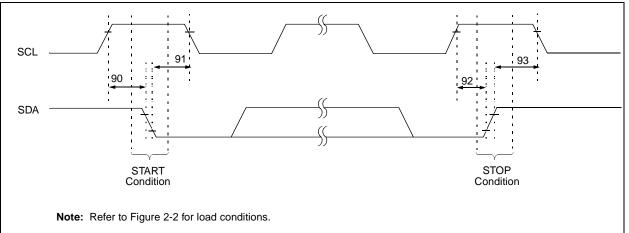

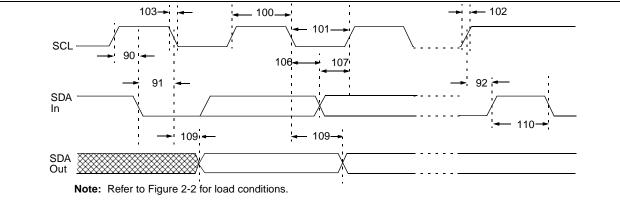

# FIGURE 2-14: I<sup>2</sup>C BUS START/STOP BITS TIMING

| Parameter<br>No. | Sym     | Chara           | cteristic    | Min  | Тур | Max | Units | Conditions                        |

|------------------|---------|-----------------|--------------|------|-----|-----|-------|-----------------------------------|

| 90*              | TSU:STA | START condition | 100 kHz mode | 4700 | —   | —   | ns    | Only relevant for repeated START  |

|                  |         | Setup time      | 400 kHz mode | 600  |     | _   | 113   | condition                         |

| 91*              | THD:STA | START condition | 100 kHz mode | 4000 | —   | _   | nc    | After this period the first clock |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | _   | ns    | pulse is generated                |

| 92*              | Tsu:sto | STOP condition  | 100 kHz mode | 4700 | —   | _   | ns    |                                   |

|                  |         | Setup time      | 400 kHz mode | 600  | —   | _   | 115   |                                   |

| 93               | THD:STO | STOP condition  | 100 kHz mode | 4000 | —   | —   | nc    |                                   |

|                  |         | Hold time       | 400 kHz mode | 600  | —   | —   | ns    |                                   |

These parameters are characterized but not tested.

| TABLE 2-13: | I <sup>2</sup> C BUS DATA REQUIREMENTS |

|-------------|----------------------------------------|

|-------------|----------------------------------------|

| Parameter<br>No. | Sym     | Characte               | eristic      | Min        | Max  | Units | Conditions                                  |

|------------------|---------|------------------------|--------------|------------|------|-------|---------------------------------------------|

| 100*             | Thigh   | Clock high time        | 100 kHz mode | 4.0        | _    | μs    | Device must operate at a minimum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 0.6        | _    | μs    | Device must operate at a minimum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     | —    |       |                                             |

| 101*             | TLOW    | Clock low time         | 100 kHz mode | 4.7        | —    | μs    | Device must operate at a minimum of 1.5 MHz |

|                  |         |                        | 400 kHz mode | 1.3        | _    | μs    | Device must operate at a minimum of 10 MHz  |

|                  |         |                        | SSP Module   | 1.5TCY     |      |       |                                             |

| 102*             | Tr      | SDA and SCL rise       | 100 kHz mode | —          | 1000 | ns    |                                             |

|                  |         | time                   | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from<br>10-400 pF     |

| 103*             | TF      | SDA and SCL fall time  | 100 kHz mode | —          | 300  | ns    |                                             |

|                  |         |                        | 400 kHz mode | 20 + 0.1Cb | 300  | ns    | Cb is specified to be from 10-400 pF        |

| 90*              | TSU:STA | START condition        | 100 kHz mode | 4.7        | —    | μs    | Only relevant for repeated                  |

|                  |         | setup time             | 400 kHz mode | 0.6        | —    | μs    | START condition                             |

| 91*              | THD:STA | START condition hold   | 100 kHz mode | 4.0        |      | μs    | After this period the first clock           |

|                  |         | time                   | 400 kHz mode | 0.6        |      | μs    | pulse is generated                          |

| 106*             | THD:DAT | Data input hold time   | 100 kHz mode | 0          |      | ns    |                                             |

|                  |         |                        | 400 kHz mode | 0          | 0.9  | μs    |                                             |

| 107*             | TSU:DAT | Data input setup time  | 100 kHz mode | 250        | —    | ns    | Note 2                                      |

|                  |         |                        | 400 kHz mode | 100        | —    | ns    |                                             |

| 92*              | Tsu:sto | STOP condition setup   | 100 kHz mode | 4.7        | —    | μs    |                                             |

|                  |         | time                   | 400 kHz mode | 0.6        | —    | μs    |                                             |

| 109*             | ΤΑΑ     | Output valid from      | 100 kHz mode | —          | 3500 | ns    | Note 1                                      |

|                  |         | clock                  | 400 kHz mode | —          |      | ns    |                                             |

| 110*             | TBUF    | Bus free time          | 100 kHz mode | 4.7        | —    | μs    | Time the bus must be free                   |

|                  |         |                        | 400 kHz mode | 1.3        | —    | μs    | before a new transmission can<br>start      |

|                  | Cb      | Bus capacitive loading | -            | —          | 400  | pF    |                                             |

These parameters are characterized but not tested.

Note 1: As a transmitter, the device must provide this internal minimum delay time to bridge the undefined region (min. 300 ns) of the falling edge of SCL to avoid unintended generation of START or STOP conditions.

2: A fast-mode (400 kHz) I<sup>2</sup>C-bus device can be used in a standard-mode (100 kHz) I<sup>2</sup>C-bus system, but the requirement Tsu:DAT  $\geq$  250 ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line TR max.+tsu; DAT = 1000 + 250 = 1250 ns (according to the standard-mode I<sup>2</sup>C bus specification) before the SCL line is released.

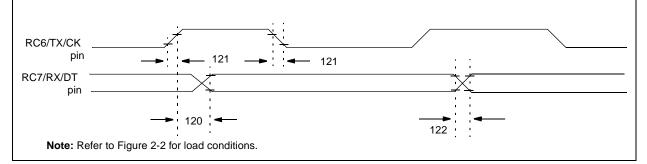

### FIGURE 2-16: USART SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

### TABLE 2-14: USART SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param<br>No. | Sym      | Characteristic                                             | Min | Тур† | Мах | Units | Conditions |

|--------------|----------|------------------------------------------------------------|-----|------|-----|-------|------------|

| 120*         | TckH2dtV | SYNC XMIT (MASTER & SLAVE)<br>Clock high to data out valid |     | —    | 100 | ns    |            |

| 121*         | Tckrf    | Clock out rise time and fall time (Master Mode)            | —   | —    | 50  | ns    |            |

| 122*         | Tdtrf    | Data out rise time and fall time                           | —   |      | 50  | ns    |            |

These parameters are characterized but not tested.

Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not t tested.

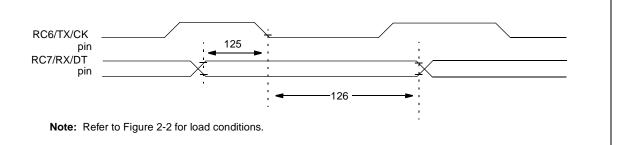

### FIGURE 2-17: USART SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

### **TABLE 2-15**: USART SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                                             | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125*             | TdtV2ckL | $\frac{\text{SYNC RCV (MASTER \& SLAVE)}}{\text{Data setup before CK } \downarrow (\text{DT setup time})}$ | 15  | _    | _   | ns    |            |

| 126*             | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                                                             | 15  | —    | _   | ns    |            |

These parameters are characterized but not tested.

| Param<br>No. | Sym  | Characteristic                                    | Min       | Тур†       | Max        | Units | Conditions                                                                               |

|--------------|------|---------------------------------------------------|-----------|------------|------------|-------|------------------------------------------------------------------------------------------|

| A01          | NR   | Resolution                                        | —         | —          | 8 bits     | bit   | Vref = Vdd                                                                               |

| A02          | Eabs | Total Absolute error                              | _         | _          | < ± 1      | LSb   | VREF = VDD<br>$VSS \le VAIN \le VREF$                                                    |

| A03          | EIL  | Integral linearity error                          | _         | _          | < ± 1      | LSb   | VREF = VDD<br>$VSS \le VAIN \le VREF$                                                    |

| A04          | Edl  | Differential linearity error                      | _         | _          | < ± 1      | LSb   | VREF = VDD<br>$VSS \le VAIN \le VREF$                                                    |

| A05          | Efs  | Full scale error                                  | _         | _          | < ± 1      | LSb   | $\begin{array}{l} VREF=VDD\\ VSS\leqVAIN\leqVREF \end{array}$                            |

| A06          | EOFF | Offset error                                      | —         | _          | < ± 1      | LSb   | VREF = VDD<br>$VSS \le VAIN \le VREF$                                                    |

| A10          | —    | Monotonicity (Note 3)                             |           | guaranteed | _          | —     | $VSS \leq VAIN \leq VREF$                                                                |

| A20          | Vref | Reference voltage                                 | 2.5V      | _          | Vdd + 0.3  | V     |                                                                                          |

| A25          | VAIN | Analog input voltage                              | Vss - 0.3 | _          | Vref + 0.3 | V     |                                                                                          |

| A30          | ZAIN | Recommended impedance of<br>analog voltage source | —         | _          | 10.0       | kΩ    |                                                                                          |

| A40          | IAD  | A/D conversion current (VDD)                      | —         | 90         | _          | μA    | Average current consump-<br>tion when A/D is on.<br>(Note 1)                             |

| A50          | IREF | VREF input current (Note 2)                       | 10        | _          | 1000       | μΑ    | During VAIN acquisition.<br>Based on differential of<br>VHOLD to VAIN to charge<br>CHOLD |

|              |      |                                                   | _         | _          | 10         | μA    | During A/D Conversion cycle                                                              |

### TABLE 2-16: A/D CONVERTER CHARACTERISTICS: PIC16LC74B-16/PTL16-04 (COMMERCIAL)

\* These parameters are characterized but not tested.

†Data in "Typ" column is at 3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** When A/D is off, it will not consume any current other than minor leakage current. The power-down current spec includes any such leakage from the A/D module.

2: VREF current is from RA3 pin or VDD pin, whichever is selected as reference input.

3: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

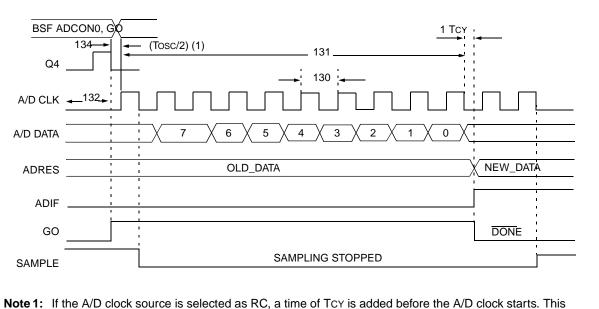

### FIGURE 2-18: A/D CONVERSION TIMING

| Note 1: | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This |

|---------|-----------------------------------------------------------------------------------------------------|

|         | allows the SLEEP instruction to be executed.                                                        |

| <b>TABLE 2-17:</b> | A/D CONVERSION REQUIREMENTS |