# MC92314

# DVB-T Single Chip Demodulator Application Note

Authors

Christoph Patzelt (Motorola),

Adrian Turner (NDS)

(Single Chip DVB-T Demodulator) Rev. 1.3

Date: November 30, 1998 3:37 pm

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Motorola data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

Rev. 1.3 Revision Status: Version 1.2 Finalised.

### **Summary of Changes or Updates:**

• Significant reduction in external intervention.

#### **Rev. 1.1:**

Changes to VCXO LPF included.

#### **Rev. 1.2:**

- Added CSE register to OFDM block register map.

- Added AGC Fix and VCXO Fix descriptions.

## Rev. 1.3:

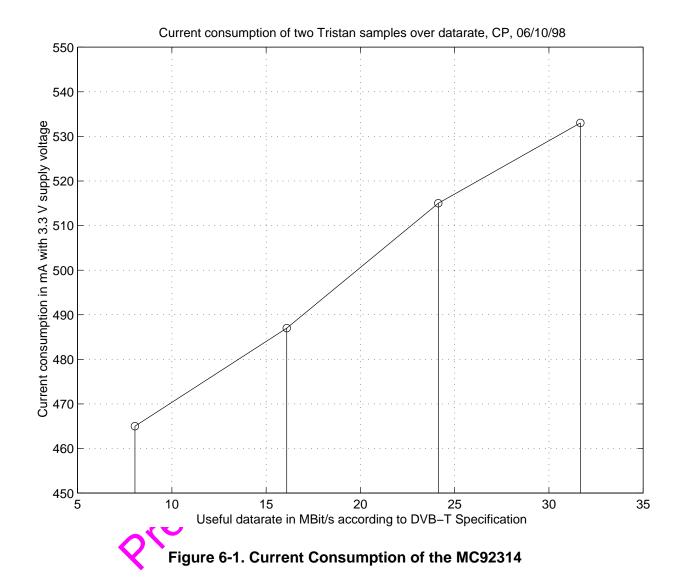

- Included performance values and power consumption values.

- Included suggestions to speed up acquisition (AFC Sweep Start, fixing FEC coderate).

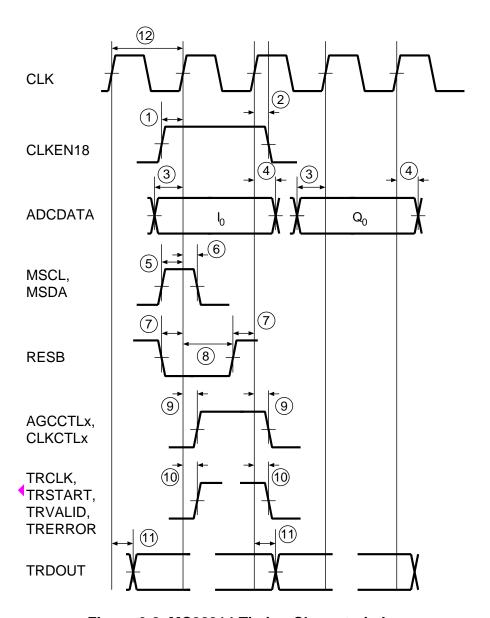

- Added Timing Diagram

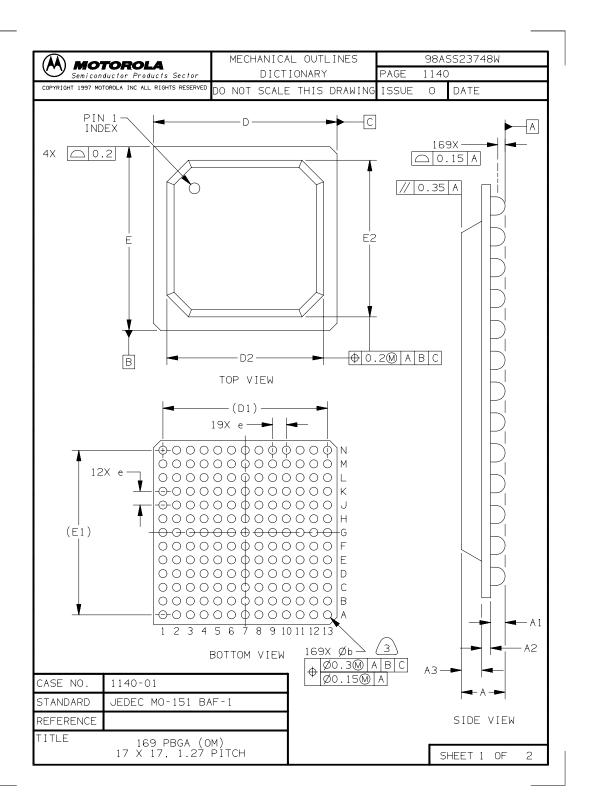

- Added BGA package information

- Added VCXO tolerance requirement

**Trademarks:**

Single Chip DVB-T Demodulator

|                  | - 4 |                     |   |   |

|------------------|-----|---------------------|---|---|

| <br>$\mathbf{a}$ | ct  | $\boldsymbol{\cap}$ | n | • |

|                  |     |                     |   |   |

| <br>TFM | - | <br>/ |

|---------|---|-------|

|         |   |       |

|         |   |       |

| 1.1 General Description1-1                                          |

|---------------------------------------------------------------------|

| 1.2 Considerations on Terrestrial Transmission1-2                   |

| 1.2.1 Echoes on the Transmission Path1-2                            |

| 1.2.2 Noise1-3                                                      |

| 1.3 Advantages of the OFDM Transmission Scheme                      |

|                                                                     |

| 1.4 Overview of the DVB-T System1-4  1.4.1 Modulation Scheme1-4     |

| 1.4.2 OFDM Block                                                    |

| 1.4.2 OFDM Block                                                    |

| 1 4 4 Forward Error Correction Block                                |

| 1.4.4.1 Viterbi Decoder                                             |

| 1.4.4.2 Convolutional Deinterleaver1-7                              |

| 1.4.4.3 Reed-Solomon Decoder1-7                                     |

| 1.4.4.4 Energy Dispersal Removal (Descrambling)1-7                  |

| 1.5 References1-8                                                   |

|                                                                     |

| Section 2                                                           |

|                                                                     |

| PINOUT & SIGNAL DESCRIPTION OF THE MC92314                          |

| 2.1 Pirout for the 160PQFP Package2-2                               |

| 2.2 Pinout for the 169BGA Package2-3                                |

| 2.3 Pin Description of the Single Chip DVB-T Demodulator MC923142-4 |

| 3 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                             |

| Section 3                                                           |

|                                                                     |

| DEVICE DESCRIPTION                                                  |

| 3.1 Complete DVB-T Digital Frontend3-1                              |

| 3.2 Component Descriptions                                          |

| 3.2.1 2K-FFT Processor Block                                        |

| 3.2.2 2K-OFDM Demodulator Block                                     |

| 3.2.2.1 I/Q-Demodulator3-3                                          |

| 3.2.2.2                   | Derotator                                  | 3-3  |

|---------------------------|--------------------------------------------|------|

| 3.2.2.3                   | Time Synchronisation                       | 3-3  |

| 3.2.2.4                   | Channel Estimation                         | 3-4  |

| 3.2.2.5                   | Channel Estimation RAM                     | 3-4  |

| 3.2.2.6                   | Channel Correction                         | 3-4  |

| 3.2.2.7                   | Channel State Estimation                   | 3-4  |

| 3.2.2.8                   | Inner Deinterleaver                        | 3-5  |

|                           | Symbol Demapper and Bit Deinterleaver      |      |

| 3.2.2.10                  | Data Formatter                             | 3-5  |

|                           | Block                                      |      |

| 3.2.3.1                   | Node Synchroniser                          | 3-6  |

| 3.2.3.2                   | Viterbi Error Correction                   | 3-12 |

| 3.2.3.3                   | Frame Synchronisation                      | 3-18 |

| 3.2.3.4                   | Frame Synchronisation  Deinterleaver       | 3-23 |

| 3.2.3.5                   | Reed-Solomon Decoder                       | 3-24 |

| 3.2.3.6                   | Reed-Solomon Decoder  Descrambler          | 3-28 |

| Section 4  DVB-T DEMODULA | ATOR INTERFACES                            |      |

| 4.1 General F             | Purpose Outputs                            | 4-1  |

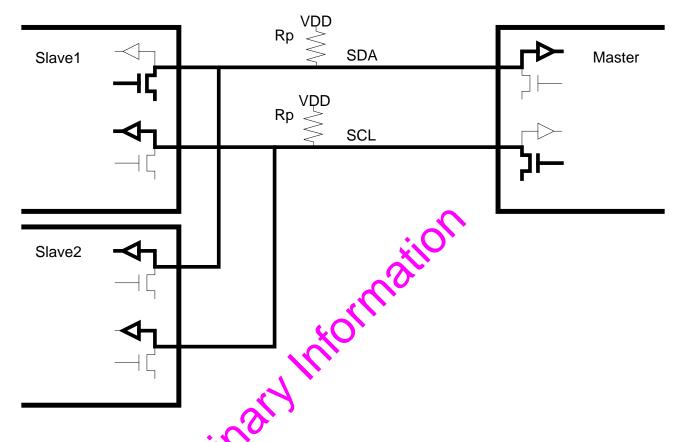

| 4.2 I2C Interf            | ace                                        | 4-1  |

| 4.2.1 I2C F               | unctionality                               | 4-2  |

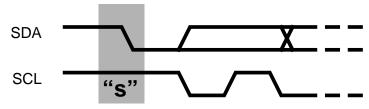

| 4.2.1.1                   | Start Condition                            | 4-2  |

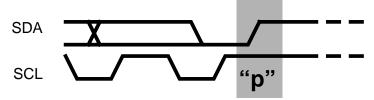

| 4.211.2                   | Stop Condition                             | 4-3  |

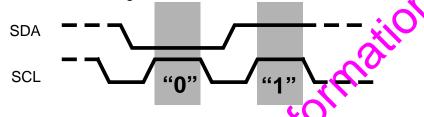

| 4.2.1.3                   | Transmitting "1" and "0"                   | 4-3  |

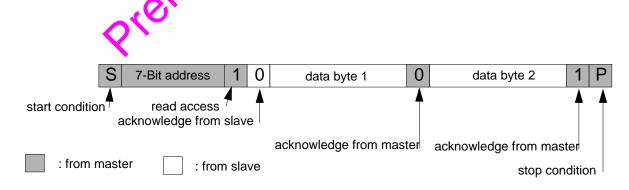

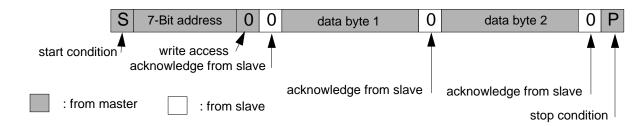

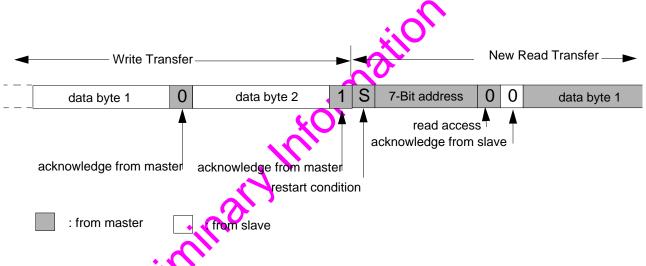

| 4.2.1.4                   | Data Transfer Sequence                     | 4-3  |

|                           | Accessing Registers via I2C                |      |

| 4.2.1.6                   | I2C Interface of the MC92314               | 4-5  |

|                           | egister Maps of the MC92314                |      |

|                           | Register Map for the OFDM Part             |      |

|                           | Register Map for the FEC Part              |      |

|                           | erface                                     |      |

|                           | ral Tuner Characteristics                  |      |

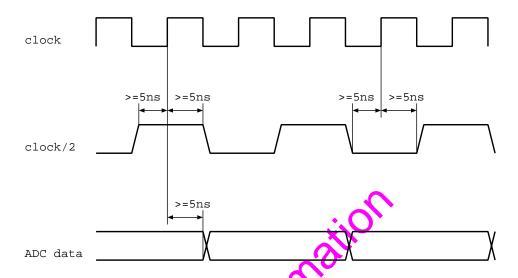

| 4.3.2 Clock               | Signals                                    | 4-26 |

| 4.3.3 Input               | from the Tuner Analog-to-Digital Converter | 4-27 |

| 4.3.4 Tuner Control signals from the MC92314                                                                                       | 4-27 |

|------------------------------------------------------------------------------------------------------------------------------------|------|

| 4.3.4.1 VCXO Control Loop                                                                                                          |      |

| 4.3.4.2 AGC Control Loop                                                                                                           | 4-28 |

| 4.4 MPEG-2 Output Interface of the MC92314                                                                                         | 4-28 |

| 4.5 References                                                                                                                     | 4-29 |

|                                                                                                                                    |      |

| Section 5                                                                                                                          |      |

| USAGE AND PERFORMANCE OF MOTOROLA'S SINGLE-CHIP DVB-T DEV                                                                          | ICE  |

| 5.1 Remarks on the Circuit Diagram                                                                                                 | 5-1  |

| 5.2 Initialising the Chipset                                                                                                       | 5-1  |

| <ul><li>5.1 Remarks on the Circuit Diagram.</li><li>5.2 Initialising the Chipset.</li><li>5.2.1 Setup of the OFDM Block.</li></ul> | 5-2  |

| 5.2.1.1 Registers of the OFDM Block                                                                                                | 5-2  |

| 5.2.1.1 Registers of the OFDM Block                                                                                                | 5-2  |

| 5.3.1 Status Information of the OFDM Block                                                                                         |      |

| 5.3.1.1 Hardware pins                                                                                                              | 5-2  |

| 5.3.1.2 Lock Status Registers                                                                                                      |      |

| 5.3.1.3 Usage of the AGO Feedback Register                                                                                         | 5-3  |

| 5.3.2 Status Information of the FEC Block                                                                                          | 5-3  |

| 5.3.2.1 Hardware Rins                                                                                                              | 5-3  |

| 5.3.2.2 Software Registers                                                                                                         | 5-3  |

| 5.3.2.3 FEC Block QVAL Values corresponding to BER values                                                                          | 5-3  |

| 5.4 Performance Considerations                                                                                                     | 5-4  |

| 5.4.1 Possible Changes in the OFDM Block                                                                                           | 5-4  |

| 5.4.1.1 Speeding up the Acquisition Time                                                                                           | 5-4  |

| 5.4.1.2 Co-Channel Protection vs. Noise                                                                                            | 5-6  |

| 5.4.2 Possible Changes in the FEC Block                                                                                            | 5-6  |

| 5.4.2.1 Fixing the Coderate for the Viterbi Decoder                                                                                |      |

| 5.4.2.2 Adjusting the MPEG Frame Synchroniser                                                                                      | 5-6  |

| 5.5 MC92314 Performance                                                                                                            | 5-7  |

| 5.5.1 Performance in a typical Consumer Application                                                                                | 5-7  |

| 5.5.1.1 Typical Lock Performance                                                                                                   |      |

| 5.5.1.2 Noise and Interference Performance                                                                                         | 5-9  |

| 5.6 References                                                                                                                     | 5-10 |

| Section 6                                |     |

|------------------------------------------|-----|

| Section 6                                |     |

| ELECTRICAL CHARACTERISTICS               |     |

| 6.1 MC92314 Electrical Considerations    | 6-1 |

| 6.2 MC92314 DC Electrical Specifications | 6-3 |

| 6.3 MC92314 Timing Characteristics       | 6-4 |

| Section 7                                |     |

| MECHANICAL CHARACTERISTICS               |     |

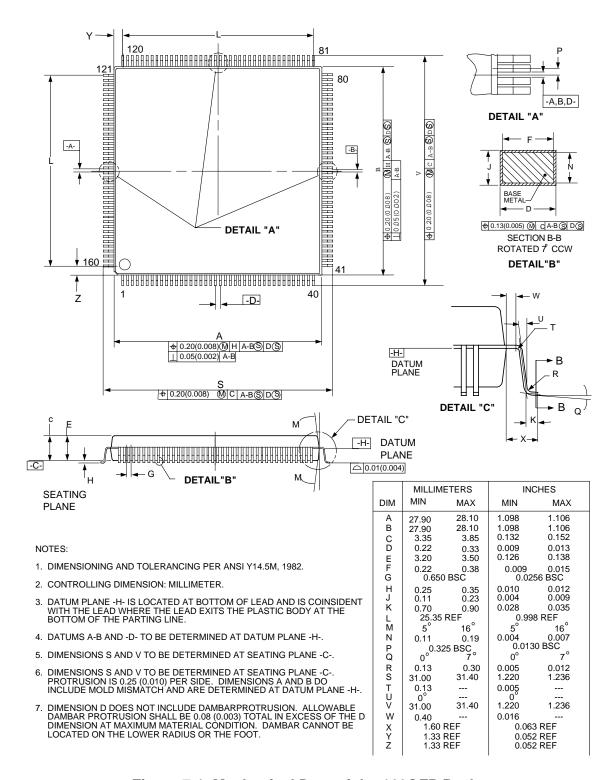

| 7.1 Outlines of the 160PQFP Package      | 7-1 |

| 7.2 Outlines of the 169BGA Package       | 7-3 |

| CHIM                                     |     |

# SECTION 1 SYSTEM OVERVIEW

In this Application Note Motorola's single chip demodulator and FEC for DVB-T receivers along with the usual application is described.

This section covers the overall descriptions as well as an introduction into the DVB-T standard, supporting the understanding of the special features of the OFDM system.

# 1.1 General Description

Before describing the important specialities of the DVB-T system itself the key features of Motorola's single chip are outlined.

- 0.35mm CMOS process at 3.3 V.

- 160 pin QFP package

- 169 BGA package

There are two main sections in the chip, providing the functions necessary to obtain a complete MPEG-2 transport stream out of one real IF-sampled DVB-T signal. The steps necessary are **OFDM demodulation** and **FEC decoding**, corresponding to the three separate devices described in Reference [1-4]:

Important capabilities of the FFT/OFDM block:

- Usable for 8 MHz, 7 MHz and 6 MHz channel bandwidth by adjusting the clock rate.

- C/N performance according to Reference [1-1] Annex A with a degradation margin of 3 dB.

- Supported DVB-T modulation schemes: QPSK, 16-QAM and 64-QAM.

- Automatic lock onto all specified guard interval lengths (<sup>1</sup>/<sub>32</sub>, <sup>1</sup>/<sub>16</sub>, <sup>1</sup>/<sub>8</sub>, <sup>1</sup>/<sub>4</sub>).

- Data input: 8 Bit TTL compatible 2's complement or offset binary.

- Channel estimation and correction using the pilot carriers.

- I<sup>2</sup>C compatible interface (M-Bus).

- Transmission Parameter Signalling (TPS) data is decoded and made available to the system controller via M-Bus.

- Processing of one block of 2048 complex samples (i.e. one 2K-OFDM symbol) in 224 ms.

- FFT input wordlength 8 bit, output accuracy 12 bit.

- Overflow on certain OFDM subcarriers due to co-channel interferes is prevented internally.

Key items of the **FEC** part include:

- Maximum 37 Mbit/s output rate.

- 3 Bit soft-decision input matched to the output of the OFDM block.

- Code rate  $\frac{1}{2}$  and depunctured rates of  $\frac{2}{3}$ ,  $\frac{3}{4}$ ,  $\frac{5}{6}$ , and  $\frac{7}{8}$ .

- · Automatic or manual rate selection.

- Viterbi decoder survivor depth 96

- Signal quality output data.

- DVB compliant 12 x 17 Forney Convolutional Deinterleaver

- Reed-Solomon (204, 188, 8) decoder as specified by DVB

- DVB Descrambler for Energy Dispersal & inverted Sync Byte removal

- Bit Error Rate (BER) and uncorrectable Frame Error (BAD) monitoring

- setting of "transport\_error\_indicator" bit in the MPEG2 output stream (MSB of first byte immediately following the Sync Byte)

## 1.2 Considerations on Terrestrial Transmission

One of the most important aspects in designing a transmission system is to chose the modulation scheme that fits best to the characteristics of the transmission channel employed. Comparing the terrestrial channel in the UHF band with the channels of the satellite or cable system yields several important differences that exclude the modulation schemes used there from an efficient usage in the terrestrial channel.

# 1.2.1 Echoes on the Transmission Path

In Figure 1-1 a typical environment for terrestrial reception is given. The antenna of the stationary receiver receives the signal belonging to the direct path from the transmitter as well as delayed echoes e.g. from buildings (this is called a Ricean channel). In contrast to this a portable receiver may receive only echoes without a signal direct from the transmitter (Rayleigh channel characteristics).

Figure 1-1. Possible echo constellation

In the well known analog TV transmission systems such echoes appear as ghost pictures on the screen, but as long as they don't get too strong the original information remains visible, at the penalty of reduced picture quality.

#### 1.2.2 **Noise**

Another impairment on every transmission channel is the addition of noise. Due to many reasons (e.g. thermal noise, impulse noise from ignition sources) the signal quality degrades with increasing distance from the transmitter. On the analog TV picture the different noise sources decrease the quality of the picture, but as long as the synchronisation circuitry remains in lock even heavily distorted pictures deliver visible information to the viewers.

# 1.3 Advantages of the OFDM Transmission Scheme

In contrast to this the behaviour of analog systems outlined in the paragraphs above the behaviour of digital transmission systems is different. The picture contents are mapped into digital signals, transmission impairments lead to transmission errors, resulting in bit errors of the received datastream. Due to the high compression ration of the source encoded MPEG-2 transport stream used in the DVB systems even single bit errors may have a severe impact on the picture quality. Without careful system layout, taking into account the characteristics of the transmission channel, the performance of a digital transmission system may be very poor.

The problems mentioned above can be circumvented successfully leading to the present system for digital terrestrial transmission. One of the main points is the Orthogonal Frequency Division Multiplex (OFDM) scheme. The following list gives a short overview about the key features of the DVB-T standard:

- Divide the whole available bandwidth into a large number of subchannels with different frequencies (Frequency Division Multiplex).

- each subchannel is independent form all others (Orthogonality).

- To combat the echoes in the terrestrial channel a guard interval is used to absorb them.

- A certain amount of redundancy is added to the bits at the transmitter side, allowing powerful error correction techniques in the receiver.

In principle the whole available bandwidth is divided into a large number N (e.g. 2048) of separate narrowband subchannels (the OFDM subcarriers). Data transmission on each subcarrier frequency is independent from and in parallel with the other subcarriers, leading to a very low datarate on each subcarrier compared to the overall transmission capacity. The splitting into the subchannels including the modulation onto the subcarriers can be done very efficiently by performing an Inverse Fast Fourier Transform (FFT) to the data to be transmitted. In turn the receiver must do a FFT to obtain the original information. Following the usual terms of digital signal processing the region before the IFFT in the transmitter and after the FFT in the receiver is called 'frequency domain' and in contrast to it the signal after the IFFT (in the transmitter) until before the FFT (in the receiver) is associated with the 'time domain'.

All these steps together allow the realisation of a robust transmission scheme specially adapted to the terrestrial channel. Advances in silicon technology enable the implementation of the advanced signal processing algorithms necessary at costs suitable to the consumer electronics industry.

Additional information on the OFDM system can be obtained from Reference [1-2] and Reference [1-3].

# 1.4 Overview of the DVB-T System

After thorough investigation of the requirements the standard for digital terrestrial television was finalised in 1996 (see Reference [1-1]). In line with the standards for the satellite system (DVB-S) and the cable system (DVB-C) it specifies all the transmission parameters for the broadcasting of services via terrestrial (e.g. UHF) channels.

#### 1.4.1 Modulation Scheme

The standard covers the Orthogonal Frequency Division Multiplex (OFDM) scheme, using OFDM symbol lengths of either 2048 (2K) or 8192 (8K) complex-valued samples. The integrated circuit covered in this document can deal only with the 2K-system, so the 8K system is not covered here.

Figure 1-2 gives a block diagram of the complete DVB-T transmission system, the blocks marked with thick lines are unique to the terrestrial system, whereas the other blocks are identical to the satellite standard DVB-S. In this diagram also the basic parameters of the transmission parameters are given, for a more detailed description see Reference [1-1]

MOTOROLA

#### 1.4.2 OFDM Block

The OFMD block performs the functions given in the blocks 'Synchronisation', 'Demapping' and 'Inner Deinterleaving' in Figure 1-2. This includes all the necessary synchronisation tasks, OFDM-related deinterleaving, demapping of the constellation diagram, generation of soft-decision information and output formatting. This block is designed to work directly with the FFT block.

Important capabilities are:

- Usable for 8 MHz, 7 MHz and 6 MHz channel bandwidth by adjusting the clock rate.

- C/N performance according to Reference [1-1] Annex A with a degradation margin of 3 dB.

- Supported DVB-T modulation schemes: QPSK, 16-QAM and 64-QAM.

- Automatic lock on all specified guard interval lengths (<sup>1</sup>/<sub>32</sub>C<sup>1</sup>/<sub>16</sub>, <sup>1</sup>/<sub>8</sub>, <sup>1</sup>/<sub>4</sub>).

- Data input: 8 Bit TTL compatible 2's complement or offset binary.

- Channel estimation and correction using the pilot carriers.

- I<sup>2</sup>C compatible interface (M-Bus) to the system controller.

- Transmission Parameter Signalling (TPS) data is decoded and made available to the system controller via M-Bus.

#### 1.4.3 FFT Block

The FFT block performs the OFDM demodulation in the true sense of the word. It gets the time domain information from the OFDM block, performs a Fast Fourier Transform on it and delivers the frequency domain information, i.e. the constellation diagram (suffering from the channel impairments) back again to the OFDM block.

Main features of the FFT block are:

- Processing of one block of 2048 complex samples (i.e. one 2K-OFDM symbol) in 224 μs.

- FFT input wordlength 8 bit, output accuracy selectable between 10 and 12 bit.

- Overflow on certain OFDM subcarriers due to co-channel interferes is handled internally.

#### 1.4.4 Forward Error Correction Block

The FEC part of the DVB-T transmission is located in the blocks 'FEC-Decoding', 'Deinterleaving', 'Sync-Inversion' and Descrambling. All these tasks are handled by the FEC block. The FEC scheme itself consist of the inner Viterbi decoder and the outer RS decoder.

#### 1.4.4.1 Viterbi Decoder

The Viterbi decoder block is DVB compliant with all the coderates available according to the specification. Its main features are:

- Maximum 37 Mbit/s output rate.

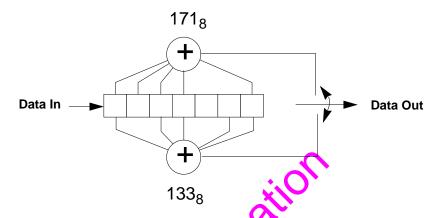

- Constraint length 7, generator polynomial (171<sub>8</sub>, 133<sub>8</sub>)

- 3 Bit soft-decision input in suited to the output of the OFDM block.

- Code rate  $\frac{1}{2}$  and depunctured rates of  $\frac{2}{3}$ ,  $\frac{3}{4}$ ,  $\frac{5}{6}$ , and  $\frac{7}{8}$ .

- · Automatic or manual rate selection.

- Programmable internal synchronizer.

- Provision for external synchronization.

- Survivor depth 96

- No internal APLL needed, clock is provided by the OFDM block.

- · Signal quality output data.

#### 1.4.4.2 Convolutional Deinterleaver

To achieve the optimal performance of any concatenated coding scheme there must be an interleaver in the transmitter between the inner and outer encoder. This interleaver distributes the bytes in a pseudo random order before feeding them into the inner encoder. In turn the deinterleaver in the receiver rearranges the original order, spreading error bursts provoked by overloading the inner decoder due to bad channel conditions.

In case of the DVB system the interleaving scheme uses a Convolutional 12x17 Forney Interleaver: Every 204 bytes of data are interleaved (reordered) at the transmitter and deinterleaved in the receiver using a Convolutional Deinterleaver with I=12 branches and M=17 byte storage cells as defined by the DVB Specifications.

# 1.4.4.3 Reed-Solomon Decoder

The FEC block contains a complete Reed-Solomon decoder as specified by DVB for digital receiver applications (204, 188) of GF(256), that means input blocks with 188 byte in length, added redundancy of 16 checkbytes leading to 204 bytes output block length. The block will accept data from the Viterbi decoder and deliver an MPEG-2 transport stream to the Set-Top Box core demultiplexer.

# 1.4.4.4 Energy Dispersal Removal (Descrambling)

The MPEG-2 data (excluding Sync Bytes) are randomised for Energy Dispersal in the transmitter. This block reverses the process and re-inverts the inverted Sync Byte prior to delivering the data to the MPEG-2 Transport Demultiplexer. It is the last step in the frontend processing chain.

The main features of the deinterleaver, RS decoder and descrambling block are given below:

- 37 MBit/s typical input and output data rates

- optimized Frame Synchronizer performance for DVB parameters

- DVB compliant 12x17 Forney Deinterleaver

- Reed-Solomon (204,188,8) decoder as specified by DVB

- DVB Descrambler for Energy Dispersal & inverted Sync Byte removal

- setting of "transport\_error\_indicator" bit in the MPEG2 output stream (MSB of first byte immediately following the Sync Byte)

- Bit Error Rate (BER) and uncorrectable Frame Error (BAD) monitoring

- 180° input data stream phase error correction

#### 1.5 References

- [1-1] ETSI (European Telecommunication Standards Institute): Digital broadcasting systems for television, sound and data services; Framing structure, channel coding and modulation for digital terrestrial television. Draft prETS 300 744, September 1996.

- [1-2] M. Alard, R. Lassalle: Principles of modulation and channel coding for digital broadcasting for mobile receivers. EBU Collected Papers on concepts for sound broadcasting into the 21st century, August 19988, pp. 47-69.

- [1-3] J. Gledhill, S. Anikhindi, P. Avon: The transmission of digital television in the UHF band using Orthogonal Frequency Division Multiplex. Proceedings of the 6th International IEE Conference on Digital Processing of Signals in Communications, IEEE Conf. Publ. No. 340, pp. 175-180, September 1991.

- [1-4] C. Patzelt, M. Drozd, S. Anikhindi: MC92307 MC92308 MC92309 DVB-T, Chipset Application Note Version 1.1; Motorola, July 1998.

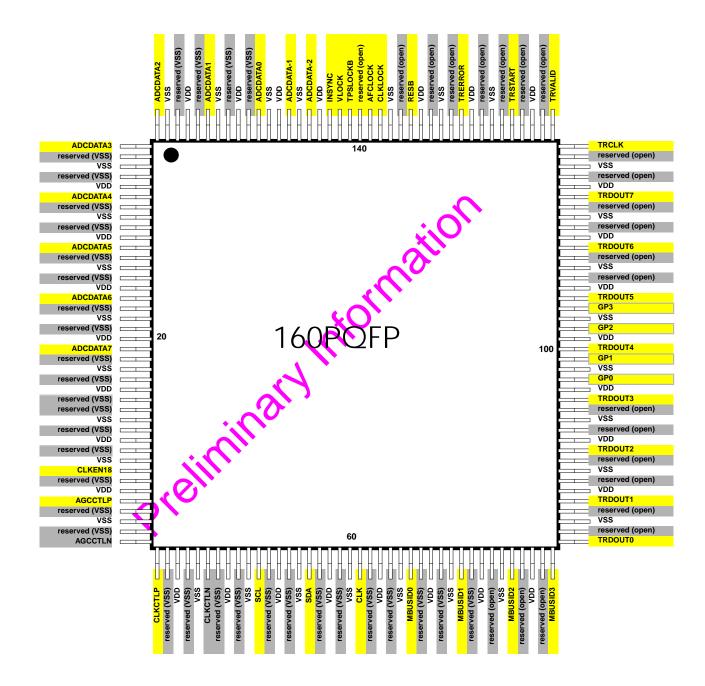

# SECTION 2 PINOUT & SIGNAL DESCRIPTION OF THE MC92314

Motorola's DVB-T demodulator is available in a 160QFP package as well as in a 169BGA. The pinout of this packages as well as the input and output lines are given in Figure 2-1, Figure 2-2 and Table 2-1. The mechanical dimensions of the package are given in Section 7.

The supply voltage of the IC is 3.3 V, its power consumption is app. 1.7 W in a typical DVB-T application as it is described Section 5.

Preliminary mormation

# 2.1 Pinout for the 160PQFP Package

Figure 2-1. Pinout for the 160PQFP

# 2.2 Pinout for the 169BGA Package

View from top, x-ray through package. 7 2 3 4 5 8 9 **10** 11 12 13 ADCDATA3ADCDATA4 ADCDATA5ADCDATA6ADCDATA7 CLKEN18 AGCCTLP AGCCTLN CLKCTLP (VSS) (VSS) (VSS) (VSS) В ADCDATA2 (VSS) (VSS) (VSS) (VSS) (VSS) (VSS) OPEN8 (VSS) (VSS) (VSS) (VSS) (VSS) X  $\mathbf{C}$ (VSS) (VSS) X (VSS) VDD (VSS) VDD X OPEN9 VDD (VSS) (VSS) D ADCDATA1 (VSS) (VSS) **VDD VDD** VDD CLKCTLN MSCL (VSS) **GND VDD VDD GND**  $\mathbf{E}$ ADCDATA0 (VSS) X (VSS) VDD **GND GND GND GND GND** VDD MSDA F (VSS) INSYNC VDD VDD **GND GND GND GND GND** VDD VDD (VSS) CLK **TPSLOCK** G **VLOCK** (OPEN) **GND GND GND** GND **GND GND** GND (VSS) (VSS) (VSS) Η (OPEN) VDD **GND GND** GND VDD VDD MBUSID0 (VSS) AFCLOCK RESB X **GND GND GND** GND **GND GND** VDD (VSS) MBUSID1 (VSS) J CLKLOCK VDD VDD K TRERROR (OPEN) (OPEN) **VDD** VDD **VDD** GND (OPEN) MBUSID2 (OPEN) GP2  $\mathbf{L}$ (OPEN) (OPEN) VDD (OPEN) X **VDD VDD** X (OPEN) X (OPEN) MBUSID3 GP1 GP3 (OPEN) (OPEN) (OPEN) (OPEN) (OPEN) (OPEN) (OPEN) TRDOUT0 TRSTART (OPEN) (OPEN) M GP0 TRDOUT6 TRDOUT5 TRDOUT4 TRDOUT3 TRDOUT2 TRDOUT1 N (OPEN) **TRVALID TRCLK** TRDOUT7 (OPEN) (OPEN)

Figure 2-2. Pinout for the 169BGA

# 2.3 Pin Description of the Single Chip DVB-T Demodulator MC92314

The description of the MC92314 pinout is given in the table below:

Table 2-1. MC92314 Pin List

| SIGNAL         | PIN-NR.                                     | FUNCTIONALITY                                                 | TYPE              | ACTIVE |

|----------------|---------------------------------------------|---------------------------------------------------------------|-------------------|--------|

| CLK            | 61                                          | Common clock input (36.57 MHz)                                | TTL - IN          | high   |

| RESB           | 135                                         | Reset (asynchronous)                                          | TTL - IN          | low    |

| CLKEN18        | 33                                          | ADC data strobe                                               | TTL - IN          | high   |

| ADCDATA[7:0]   | 21, 16, 11,<br>6, 1, 160,<br>155, 150       | ADC input                                                     | TTL - IN          | high   |

| ADCDATA[-1:-2] | 147, 145                                    | 10-Bit extension for future 8K device                         | reserved<br>(VSS) | N/A    |

| CLKCTLP        | 41                                          | ADC clock control (+)                                         | TTL - OUT         | high   |

| CLKCTLN        | 46                                          | ADC clock control (-)                                         | TTL - OUT         | low    |

| AGCCTLP        | 36                                          | Analogue AGC control (+)                                      | TTL - OUT         | high   |

| AGCCTLN        | 40                                          | Analogue AGC control (-)                                      | TTL - OUT         | low    |

| MSDA           | 56                                          | I <sup>2</sup> C compatible control bus, data pin             | TTL - OD          | N/A    |

| MSCL           | 51                                          | I <sup>2</sup> C compatible control bus, clock pin            | TTL - IN          | high   |

| MBUSID[3:0]]   | 80, 76, 71,<br>66                           | I <sup>2</sup> C compatible control bus, variable ID selector | TTL - IN          | high   |

| GP[3:0]        | 104, 102,<br>99, 97                         | General Purpose Output pins                                   | TTL - OUT         | high   |

| TRERROR        | 130                                         | MPEG-2 Frame Error Indicator                                  | TTL - OUT         | high   |

| TRVALID        | 121                                         | MPEG-2 Byte Valid Indicator                                   | TTL - OUT         | high   |

| TRSTART        | 125                                         | MPEG-2 Sync Byte Indicator                                    | TTL - OUT         | high   |

| TRCLK          | 120                                         | MPEG-2 Byte Clock                                             | TTL - OUT         | high   |

| TRDOUT[7:0]    | 115, 110,<br>105, 100,<br>95, 90, 85,<br>81 | MPEG-2 Transport Stream Byte Output                           | TTL - OUT         | high   |

| INSYNC         | 143                                         | FEC Frame Synchronization Status                              | TTL - OUT         | high   |

| VLOCK          | 142                                         | Viterbi Decoder Synchronization Status                        | TTL - OUT         | high   |

| TPSLOCKB       | 141                                         | TPS Data Valid indicator (inverted)                           | TTL - OUT         | low    |

| AFCLCK         | 139                                         | AFC status indicator                                          | TTL - OUT         | high   |

| CLKLCK         | 138                                         | Time Synchronization state indicator                          | TTL - OUT         | high   |

#### **NOTE**

The pins marked with (VSS) in the BGA pinout must be tied to  $V_{SS}$ . As they are reserved pins they need not to be connected directly to  $V_{SS}$ , instead of a pulldown resistor of about 10 K is sufficient.

Similar the pins '(OPEN)' must be left unconnected.

# SECTION 3 DEVICE DESCRIPTION

In this section the chipset as a whole as well as the operation of the several components are described.

# 3.1 Complete DVB-T Digital Frontend

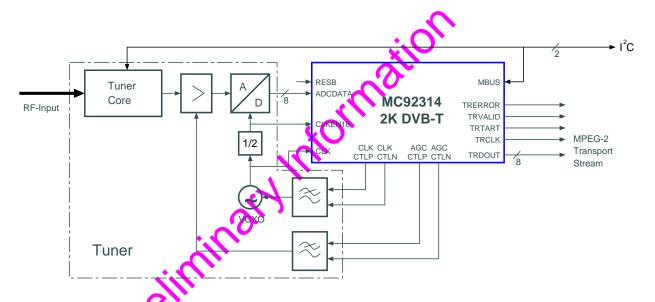

Motorola's terrestrial chipset builds a complete digital frontend for the DVB-T system, it performs according to the following functional diagram:

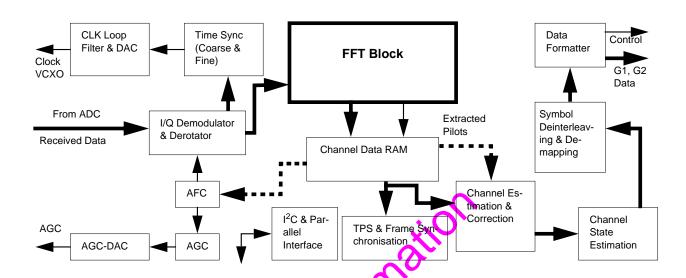

Figure 3-1. Block Diagram of a complete DVB-T Frontend

Whereas Motorola's chipset covers all the digital functions required by the standard, the analog parts (RF amplification, RF filtering, downconversion, AGC, clock generation and AD-conversion) are located in the DVB-T tuner.

The RF signal obtained by the antenna has to be fed into the tuner core, given that the C/N of the signal is high enough for the demodulation the receiver frontend will lock onto it and produce the transmitted transport stream ready to deliver it to the MPEG-2 demultiplexer.

# 3.2 Component Descriptions

After giving the overall functions of the complete digital frontend in the last paragraph we go into more detail of the individual components:

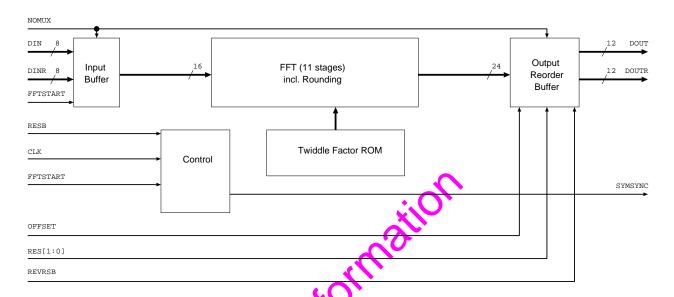

#### 3.2.1 2K-FFT Processor Block

Integrated into the MC92314 is a pipelined Fast Fourier Transformation (FFT) processor with a blocklength of 2048 complex samples. It is especially designed for use in digital terrestrial Set-

Top boxes according to the DVB-T standard for 2K transmission. One block of 2048 complex samples can be processed in 224 µs

Figure 3-2. Block Diagram of the FFT Processor

# 3.2.2 2K-OFDM Demodulator Block

The MC92314 contains also a Demodulator for the Orthogonal Frequency Division Multiplex transmission scheme according to the 2K-mode of the ETSI specification for digital terrestrial transmission (see reference [1-1]). Together with the 2K FFT block described in the previous paragraph it includes all the functions required to demodulate the information transmitted in one single UHF channel. In Figure 3-3 the block diagram of the OFDM block is given, followed by the description of the functional blocks.

Figure 3-3. OFDM Demodulator Part of the MC92314

#### 3.2.2.1 I/Q-Demodulator

In this first stage the complex samples are reconstructed from the (real valued) input stream by means of a discrete Hilbert transformer. The input stream is fed into the Hilbert transformer and delayed appropriately to calculate the real and imaginary parts of the signal.

#### 3.2.2.2 Derotator

Carrier frequency offsets resulting from local oscillator offsets in the tuner are removed digitally by means of a NCO and a phase accumulator, that are controlled by the <u>Au</u>tomatic <u>F</u>requency <u>C</u>ontrol (AFC). During the acquisition phase (when locking onto a DVB-T transmission) the AFC circuit sweeps permanently through the available range until the correct frequency offset has been detected. During the tracking phase the control signal for the phase increment is derived from the pilot carriers in the frequency domain.

#### 3.2.2.3 Time Synchronisation

The Time Synchronisation (separated in the coarse synchronisation valid during the acquisition phase and the fine synchronisation for tracking purposes) sets the FFT window position for the real OFDM demodulation and controls the clocking of the whole chip.

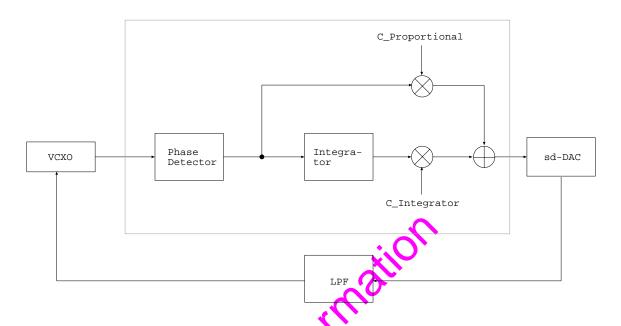

In the tracking mode the time synchronisation generates the VCXO control signal using the filter structure given in Figure 3-4 below. The contribution of the proportional branch and of the integrator branch can be adjusted separately using the Clock Loop Filter Coefficients (see also paragraph 4.2.2.1.5).

The gain of the proportional part is set using Bits [7:4] and the gain of the integrator part is adjusted with Bits [3:0].

Figure 3-4. Time Synchronisation of the OFDM Block

#### 3.2.2.4 Channel Estimation

To compensate for the impairments of the terrestrial channel it is essential to estimate the channel transfer function. This estimation is done using the scattered and continual pilot carriers. As the scattered pilots change in subsequent OFDM symbols a <u>time interpolation</u> over 4 OFDM symbols is necessary to build a complete set of pilot information. This set contains one valid pilot sample at every 3rd carrier position. To obtain a channel estimation value so the set ends up with an estimation value for each carrier position, <u>frequency interpolation</u> must be performed.

#### 3.2.2.5 Channel Estimation RAM

The channel estimation RAM must store the data carriers until the channel estimation is available for a given OFDM symbol.

#### 3.2.2.6 Channel Correction

In the channel correction block the estimate of the channel transfer function is used to compensate the influence of the terrestrial transmission. In principle each data carrier's value is multiplied with the inverse of the estimate to approximate the desired flat overall frequency response to as close as possible.

#### 3.2.2.7 Channel State Estimation

To improve the efficiency of the decoding of the inner convolutional code, information about the reliability of each bit received via the transmission channel, is generated during the demodulation process. So data that were transmitted in subchannels disturbed heavily due to echoes or interference (resulting in a low SNR in these specific subchannels) are marked less reliable than those transmitted in nearly undisturbed subchannels. In the channel state estimation this

reliability information is generated for each carrier individually and passed together with the subcarriers data to the following stage.

#### 3.2.2.8 Inner Deinterleaver

Due to the echoes on the transmission path it is obvious that adjacent subcarriers are disturbed in a similar way: the used bandwidth of 7.61 MHz corresponds to 1705 active carriers, so the difference in the channel transfer function from one carrier to the adjacent carrier is limited. In case of a simple parallel to serial conversion adjacent bits of data would suffer from similar distortions. In this case the Viterbi decoder cannot work with its optimal performance. Instead the best performance is given if the disturbance applied to adjacent data bits is uncorrelated. To achieve this the data of all the relevant subcarriers are interleaved in the transmitter according to par. 4.3.4 in reference [1-1]. This interleaving has to be reversed prior to the demodulation.

## 3.2.2.9 Symbol Demapper and Bit Deinterleaver

The modulated (complex valued) frequency domain samples are demapped into 2, 4 or 6 streams depending on the modulation scheme chosen. Each demodulated data bit is extended to a 3-bit soft decision value using the reliability information from the Channel State Estimation to support the following FEC.

In par. 4.3.4 in reference [1-1], bit interleaving is also specified in order to disperse bursts of bit errors in the receiver after demapping the complex data symbols. This bit interleaving is reversed in the Bit Deinterleaver module.

#### 3.2.2.10 Data Formatter

This is the final stage in the OFDM specific part of the DVB-T frontend. It generates from the up to 6 bitstreams according to par. 4.3.4 in reference [1-1] the correct datastreams corresponding to the G1 and G2 data to be fed into the Viterbi decoder.

Although the FEC scheme and the format of the data delivered by the OFDM block is identical to the satellite system there is a fundamental difference in clocking. In the DVB-S system the data are delivered continuously to the Viterbi decoder, where as, this cannot be the case in DVB-T. The internal clocking is uncorrelated to the transmitted data rate. Instead of going the costly way of synthesizing an extra clock signal for the Viterbi decoder, the demodulated data are output in burst mode at an average frequency corresponding to the transmitted data rate. For details see the paragraph 4.6 OFDM -> FEC Interface in reference [1-1].

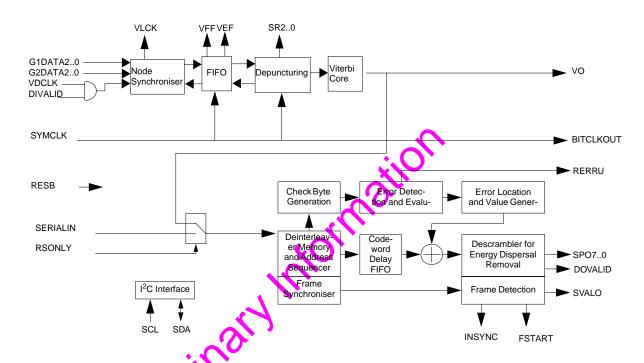

#### 3.2.3 FEC Block

The FEC block completes Motorola's DVB-T single chip demodulator by providing all the FEC functions necessary for the reception of DVB-T transmissions. It is fully compliant to the ETSI specification for digital terrestrial broadcasting (see reference [1-1]).

Figure 3-5. Block Diagram of the FEC Block

## 3.2.3.1 Node Synchroniser

#### 3.2.3.1.1 Syndrome Based Node Synchronisation

Prior to producing valid data the Viterbi decoder block must synchronise to the input data stream, including removing any phase ambiguity in the received symbols and determine the punctured code rate transmitted.

The Viterbi block employs a method known as Syndrome Based Node Synchronisation to achieve both I & Q symbol and punctured rate Synchronisation. This method has certain advantages over other more common Synchronisation methods such as observation of path metric growth rates and re-encoding of the received data stream:

- Path metric growth observations are relatively sensitive to input magnitude variations and require multiple estimation cycles to detect Synchronisation.

- Re-encoding of the data stream (using a convolutional encoder) requires multiple estimation cycles and can increase the latency of the decoder.

| Device | Descri | ptior |

|--------|--------|-------|

|        |        |       |

Syndrome based node synchronisation is independent of the average input magnitude and can also easily detect changes of the synchronisation state.

The theory is based on the observation that the product of the incoming data and a syndrome (predetermined by simulation for each data rate) is zero if synchronised correctly. In any other case, the probability of 0's vs. 1's in the product increases. In the extreme case, i.e. the node synchronisation is completely wrong, the product is random and there is equiprobability of 0's and 1's. This behaviour is exploited for syndrome based node synchronisation.

## 3.2.3.1.2 Synchronisation States

The possible states that the synchroniser has to deal with are a combination of the following factors:

- The phasing of the received symbols. The synchronise must decide which of two possible states the I and Q input streams are in. They can either be processed as-is or can be rotated 90° to account for constellation rotation in the receiver.

- Determination of the framing of the I and Q bit streams so as to extract the correct symbol.

There are four possible ways to frame the two bit streams and the synchroniser must determine the correct one.

#### 3.2.3.1.3 Synchroniser Parameters

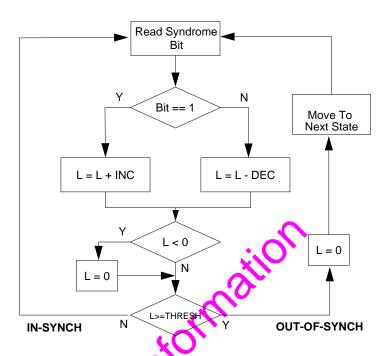

The synchroniser is based on an estimator which determines whether the received symbol sequence is in the correct synchronisation state. This estimate is based on single sided sequential probability ratio tests (SPRTs). The tests are based on the accumulation of the log-likelihood ratio (LLR) that a certain hypothesis (in-sync or out-of-sync) for the input sequence holds. A vote for a hypothesis is obtained if the accumulated LLR reaches a certain threshold. The accumulator value L is computed as shown in the flowchart in Figure .

#### **NOTE**

If a vote for out-of-sync occurs, the synchronisation state (which is output at 12c register SYNCH\_STATE) is increased to test the next hypothesis.

Figure 3-6. Synchronisation Flow

#### 3.2.3.1.4 Choice of DEC and THRES

The constants INC, DEC and THRES influence the acquisition behaviour of the synchroniser as well as it's robustness. The constants INC and DEC should be chosen such that the accumulator is driven towards zero in the case that the syndrome sequence is identifying the in-sync state (i.e. rate of zeroes is  $p_0$ ):

If the syndrome sequence is identifying an out-of-sync state (i.e.  $p_0 = 0.5$ ) the accumulator should be driven with approximately equal average increments towards the threshold. Obviously, the synchroniser will erroneously vote for out-of-sync condition if the channel SNR falls below a certain limit since  $p_0$  will approach 0.5 for very low SNR.

- The decoder uses a fixed Increment of INC = 32.

- DEC is set via 12c register DEC[4:0] and can have a maximum value of 32, default selection of DEC values according to the rate being decoded is enabled by setting the DDEC bit in the CONFIG register to 0. The default values of DEC for each of the supported rates is shown in Table 3-1.

- THRES is set via 1<sup>2</sup>C register THRESHOLD and can have a maximum value of 32, default selection of THRES = 8 is enabled by setting the DTHRES bit in the CONFIG register to be 0.

The actual value of THRES is interpreted as <register\_value> x 29.

The defaults have been chosen such that the synchroniser will operate correctly (but with a performance degradation) roughly 2 dB below the output error rate, which is required for quasi error free operation (BER of the decoded stream approximately  $= 2 \times 10^{-4}$ ).

**Table 3-1. Default Settings For DEC Parameter**

| Rate | Dec | Lower SNR<br>Boundary<br>(dB) | Quasi<br>Error<br>Free SNR<br>(dB) | Design<br>Point SNR<br>(dB) | Design<br>Point<br>Channel<br>BER |

|------|-----|-------------------------------|------------------------------------|-----------------------------|-----------------------------------|

| 1/2  | 29  | 1.2                           | 3.0                                | 2.15                        | 0.100                             |

| 2/3  | 26  | 2.0                           | 3.5                                | 2.49                        | 0.062                             |

| 3/4  | 25  | 2.4                           | 4.0                                | 3.00                        | 0.042                             |

| 5/6  | 24  | 2.9                           | 4.5                                | 3.51                        | 0.026                             |

| 7/8  | 23  | 3.5                           | 5.2                                | 4.10                        | 0.017                             |

# 3.2.3.1.5 Synchroniser Performance

The performance of the synchroniser can be characterized by three figures:

• Short Average Run Length (SARL):

This is the mean time required to detect that the currently investigated synchronisation state is not the correct synchronisation state.

The SARL is calculated as:

$$SARL = \frac{2XTHRES}{INC - DEC}$$

### **NOTE**S

SARL performance is not affected by the channel SNR since the syndrome sequence is composed of equiprobable 1's and 0's for an out of synch condition and low channel SNR would also result in equiprobable 1's and 0's.

• Reacquisition Average Run Length (RARL):

This is the mean time between a erroneous detection of a change of the synchronisation state and successful acquisition of the new synchronisation state (reacquisition). The RARL is calculated as:

$$RARL = \frac{SARL}{(syncstates - 1)}$$

Where "syncstates" is given by:

Table 3-2. Number of Syncstates in Code Rates

| Rate | Synchstates |

|------|-------------|

| 1/2  | 2           |

| 2/3  | 6           |

| 3/4  | 4           |

| 5/6  | 6           |

| 7/8  | 8           |

#### **NOTE**

For automatic rate selection the synchroniser investigates the possible synchronisation states one after the other and RARL is calculated as follows:

$$RARL = \left(\sum_{rate = \frac{1}{2}}^{\frac{7}{8}} Synchstates\right) \times SARL$$

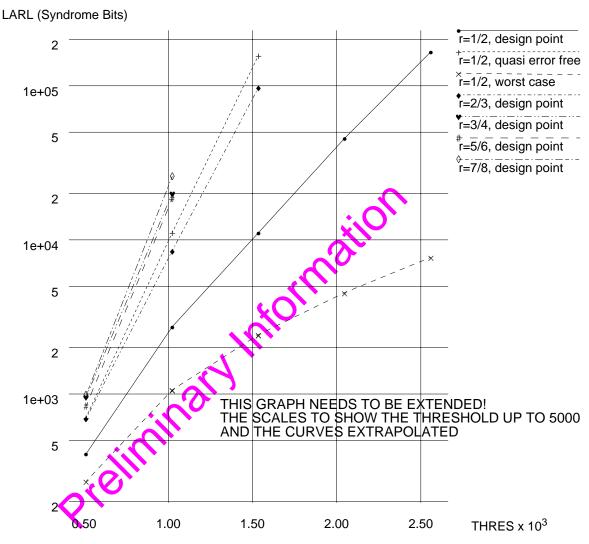

Long Average Run Length (LARL): This is the mean time until the algorithm incorrectly indicates a change of the synchronisation state that did not actually occur. This grows exponentially with the threshold value THRES.

#### **NOTE**

While the SARL and RARL can be determined analytically the evaluation of the LARL is nontrivial and is best determined via simulation.

Figure 6-2. shows the simulated LARL for all code rates, the channel error rate is set so the SNR is 1dB below the error rate required for QEF operation at the output of Viterbi decoder.

Figure 3-7. LARL Versus THRES At Various Design Points

For rate  $^{1}/_{2}$  (worst case for the synchroniser) the results for QEF (BER = 0.0789) and 2.8 dB below (BER = 0.125) are shown extrapolated.

From it can be seen that the LARL increases with decreasing SNR. For QEF operation a threshold below 5000 is sufficient to obtain less than one synchroniser error per day for a rate  $\frac{1}{2}$ .

#### 3.2.3.1.6 Lock Detection and Time-out

Lock of the decoder is indicated if the state of the synchroniser has not changed for a significantly long time, this period is measured in number of syndrome bits. The time-out period can be set via the  $I^2C$  register TIMEOUT, a default value of 8 is used if bit DLT in the CONFIG register is set to 0. The actual period is TIMEOUT \*  $2^{11}$  syndrome bits.

- If the accumulator value L does not reach the threshold value THRES within the period specified by TIMEOUT then it is reset and the decoder continues to indicate a locked state.

- If L exceeds THRES before the end of the TIMEOUT period then an out of lock condition is declared and the synchroniser moves to the next state and restarts the synchronisation process.

To avoid false lock indications, and to quickly detect out of lock situations the optimal value for TIMEOUT is SARL \* 4.

#### 3.2.3.2 Viterbi Error Correction

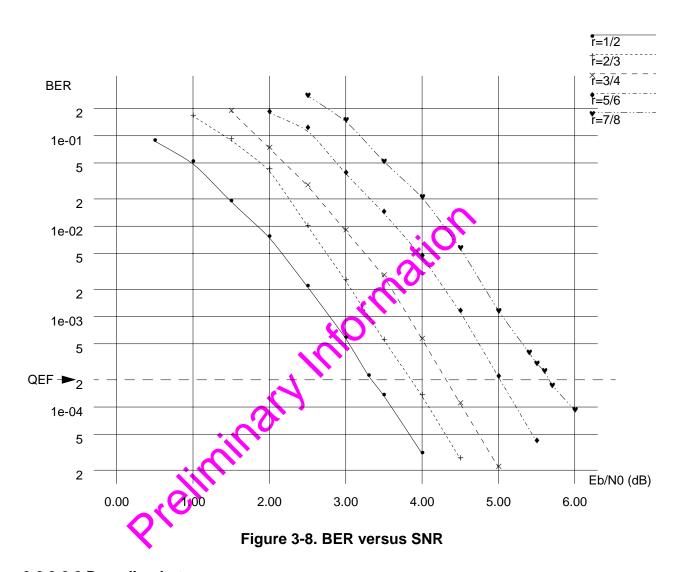

#### 3.2.3.2.1 BER vs. SNR Performance

Figure 3-8 shows the performance curves for each code rate as a function of Bit Error Rate (BER) versus channel Signal to Noise Ratio (SNR). The graph also shows the Quasi Error Free (QEF) operating limit at 2 \* 10<sup>-4</sup>. The graph was generated assuming QPSK transmission over an AWGN channel with a normalized gain of 1 at the output of the receiver A/D.

In paragraph 5.3.2.3 an example is given how to obtain a BER estimate from the QVAL values that are available from the FEC register.

## 3.2.3.2.2 Decoding Latency

A survivor depth of 96 is used to ensure reliable error correction for highrate punctured codes such as the 7/8 code. The latency of the decoder (in symbols) is approximately 2.5 x the survivor depth (the uncertainty in the latency is due to the input FIFO which gives a range of + or - 16 symbols).

#### **NOTE**

This latency applies for all coding rates not just the 7/8 rate.

The absolute worst case latency is thus:  $(2.5 \times 96) + 16 = 256$  symbols.

#### 3.2.3.2.3 Generator Polynomials

The Viterbi decoder is designed to decode bit streams encoded using the DVB standard generator polynomials (171<sub>8</sub>, 133<sub>8</sub>) as shown in Figure 3-9.

Figure 3-9. Generator Polynomials

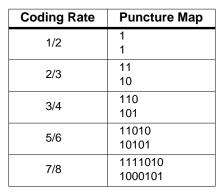

#### 3.2.3.2.4 Punctured Codes

The Viterbi decoder is able to decode a basic rate 1/2 convolutional code and the "standard" punctured codes for a k=7 constraint length. The punctured maps are shown in the table below. Specific bits of the original rate 1/2 code sequence are periodically deleted prior to transmission according to the entries in the table, where a 0 means that the bit is deleted and a 1 means that the bit is transmitted.

Table 3-3. Deletion Map For Punctured Rate 1/2 Codes

#### 3.2.3.2.5 Rate Encoding Data Word

The code rate actually being decoded by the decoder is indicated via external pins SR2..SR0 and via the I<sup>2</sup>C interface.

Table 3-4 shows the encoding of the rate information into a three bit word. This information is used for output information when using automatic synchronisation or for control information when the block is being externally controlled via the I<sup>2</sup>C interface.

**Table 3-4. Rate Encoding**

| Coding Rate | Data Word |

|-------------|-----------|

| 1/2         | 000       |

| 2/3         | 001       |

| 3/4         | 010       |

| 5/6         | 011       |

| 7/8         | 100       |

| Automatic   | 111       |

Notes:

Automatic rate selection is only used as an input value when internal synchronisation is used. The decoder will never output 111 as a coding rate.

All other states of the 3 bit data word are unused.

This table is referred to throughout this document when discussing the various rates supported by the decoder.

## 3.2.3.2.6 Input Data Format

The I and Q data input to the decoder can be interpreted as either sign-magnitude or offset binary format. The choice of input format is specified by setting the IFS bit in the CONFIG register bank of the I2C interface. The default after RESET\_N is to use offset binary.

Table 3-5. I And Q Input Format

|                | VC0[2:0]/VC1[2:0]          |                             | 2's complement    |

|----------------|----------------------------|-----------------------------|-------------------|

| Interpretation | IFS = 0<br>(offset binary) | IFS = 1<br>(sign-magnitude) | (internal format) |

| strong 0       | 000                        | 011                         | 100               |

|                | 001                        | 010                         | 101               |

| weak 0         | 010                        | 001                         | 110               |

|                | 011                        | 000                         | 111               |

| weak 1         | 100                        | 100                         | 000               |

|                | 101                        | 101                         | 001               |

|                | 110                        | 110                         | 010               |

| strong 1       | 111                        | 111                         | 011               |

#### 3.2.3.2.7 Channel SNR Measurement

The synchroniser generated syndrome sequence ( $p_0$ ) is used to determine the channel SNR value. The average value of the number of 1's accumulated from  $p_0$  is calculated over a known period and is accessible via the  $I^2C$  interface.

The window length used is specified by the AVRG\_PERIOD register and is interpreted as AVRG\_PERIOD[3:0] \* 2<sup>15</sup>, the default period of 8 \* 2<sup>15</sup> is used if the DAP bit in the CONFIG register bank is set to 1. The number of 1's in the syndrome stream (divided by 16) which are accumulated over the specified period may be read from the registers QVALMSB[7:0] and QVALLSB[7:0].

The estimated value of  $p_0$  is:

$$p_0 = 1 - \frac{QVAL \times 2^4}{PERIOD \times 2^{15}}$$

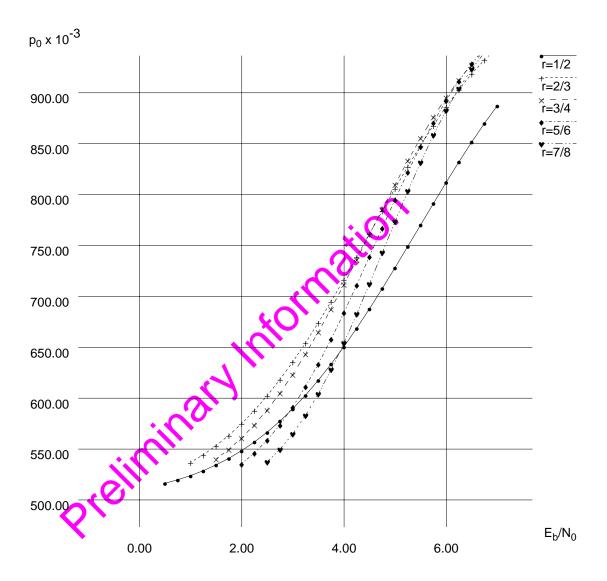

The value of  $p_0$  can be directly related to the signal quality for the various code rates via the curves shown in Figure 3-10. This signal quality value corresponds to the channel SNR of QPSK transmission over an AWGN channel. The curves are generated specifically for the syndrome polynomials actually used in the decoder. To derive a channel SNR value simply look up the value on the x-axis of a given  $p_0$  value for a given code rate.

Figure 3-10. p<sub>0</sub> Versus Channel SNR

## 3.2.3.2.8 Accuracy of SNR Estimate

The accuracy of the p<sub>0</sub> estimate of channel SNR increases with longer averaging periods and with increased SNR. Table 3-6 shows the effect of increasing the AVRG\_PERIOD for different

**Device Description**

code rates and channel SNR. It shows the probability that the estimate from the graph is within +/- 0.1 dB of the actual channel SNR.

Table 3-6. Probability Of p<sub>0</sub> Accuracy

| AVRG_PERIOD | # Of Samples | Probability Of +/- 0.1dB Accuracy          |                                            |

|-------------|--------------|--------------------------------------------|--------------------------------------------|

|             |              | r=1/2, E <sub>b</sub> /N <sub>0</sub> =1.2 | r=7/8, E <sub>b</sub> /N <sub>0</sub> =3.5 |

| 1           | 32768        | 0.541559                                   | 0.999799                                   |

| 2           | 65536        | 0.700163                                   | 1                                          |

| 4           | 131072       | 0.855141                                   | 1                                          |

| 8 (default) | 262144       | 0.960214                                   | 1                                          |

| 15          | 491520       | 0.995069                                   | 1                                          |

From the table it can be seen that even using the default value for AVRG\_PERIOD the probability that the p<sub>0</sub> estimate of SNR is within 0.1 dB is 96% (even for small SNR values). For increased AVRG\_PERIOD values or increased SNR values the probability is 100% for all practical purposes.

#### 3.2.3.3 Frame Synchronisation

# 3.2.3.3.1 MPEG Frame Synchroniser and Deinterleaver

This section of the manual describes the Frontend of the Reed-Solomon decoder in the MC92314. The data received from the Viterbi decoder is internally a continuous stream of bits and must be segmented into blocks (MPEG-2 Transport Packets) and subsequently into bytes that the Reed-Solomon can manipulate. The Frame Synchroniser recognizes the Synchronisation Bytes (Sync Bytes) embedded in the data stream and communicates these as frame boundaries to the Reed-Solomon decoder and the other functional blocks. The 12x17 Forney Deinterleaver processes the input bit stream to break up and distribute the longer burst errors throughout the MPEG-2 packet.

# 3.2.3.3.2 Frame Structure and Synchronisation Scheme

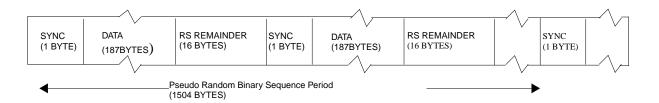

The MPEG-2 Transport Packet consists of one leading Sync Byte (0x47), 187 information bytes and 16 Reed-Solomon Check Bytes (for a total of 204). In addition, the Sync Byte of every eighth packet is inverted from 0x47 to 0xB8. The frame structure of the interleaved data is depicted in Figure 3-11. The synchroniser uses this structure to determine the byte and frame boundaries to synchronise the deinterleaver and the decoder and also to resolve the  $\pi$ -ambiguity of the data within the input stream.

# Freescale Semiconductor, Inc.

**Device Description**

Figure 3-11. MPEG-2 Frame Structure

#### 3.2.3.3 Frame Synchroniser Modes

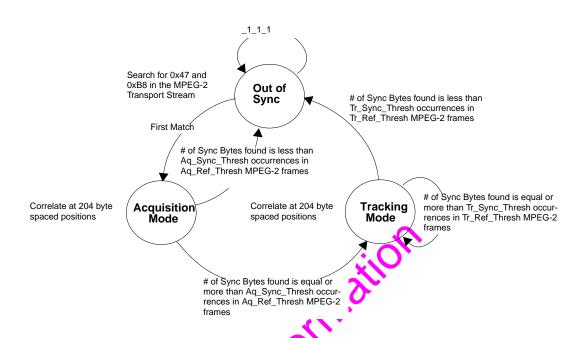

The Frame Synchroniser has two operation modes: the Acquisition and Tracking Modes. The Acquisition Mode starts when an initial Sync Byte is detected and continues until a specified number of additional Sync Bytes has been found at the correct positions within a specified number of MPEG-2 transport packets. In this case the Tracking Mode is entered. The Frame Synchroniser remains in the Tracking mode as long as the (different) set of synchronisation conditions for tracking is met and maintained. Four integer parameters (set through the I<sup>2</sup>C Interface) are used to establish these two modes: Aq\_Sync\_Thresh, Aq\_Ref\_Thresh, Tr\_Sync\_Thresh and Tr\_Ref\_Thresh. Aq\_Sync\_Thresh and Aq\_Ref\_Thresh are used to set the desired level of Acquisition conditions. If Aq Sync\_Thresh Sync Byte or inverted Sync Byte matches are found in Aq Ref Thresh frame spaced positions (e.g. Aq Sync Thresh = 2 and Ag Ref Thresh = 8: if 2 Sync Bytes are found in 8 MPEG-2 frames or in 8 x 204 = 1632 bytes), In\_Sync is signalled and the Tracking Mode is enabled. Otherwise, the correlation upon the input bit stream is continued and the Frame Synchroniser further remains out of the synchronisation state. In the Tracking Mode, Tr Sync Thresh Sync Byte or inverted Sync Byte matches are necessary in Tr Ref Thresh frame spaced positions in order to stay In Sync. See Figure 3-12 for the state diagram of the Frame Synchroniser.

The parameters Aq\_Ref\_Thresh (default: 8) and Tr\_Ref\_Thresh (default: 31) can be set between 0 and 31 and the parameters Ag Sync Thresh (default: 2) and Tr Sync Thresh (default: 3) can be set between 0 and 7.

Figure 3-12. Frame Synchroniser State Diagram

#### 3.2.3.3.4 $\pi$ -Ambiguity Resolution

While in the Tracking Mode,  $\pi$ -ambiguity is also determined and resolved. As frames enter the Frame Synchroniser the number of Sync Bytes found at frame start positions are compared to the number of inverted Sync Bytes that have been identified. If three inverted Sync Bytes are found per Sync Byte occurrence, a  $\pi$ -offset synchronisation of the Viterbi decoder or QAM Demodulator is assumed and all received bits are inverted to correct the  $\pi$  phase mismatch at the output.

#### 3.2.3.3.5 Frame Synchroniser Performance

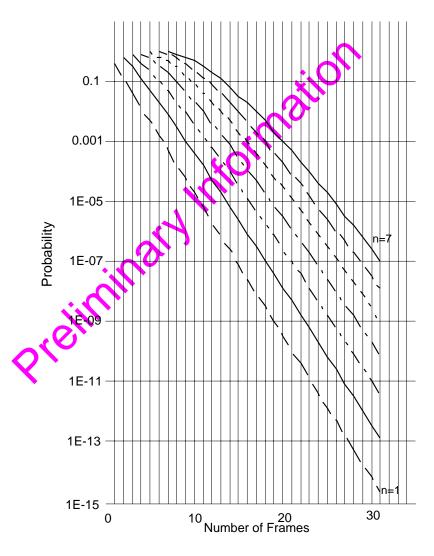

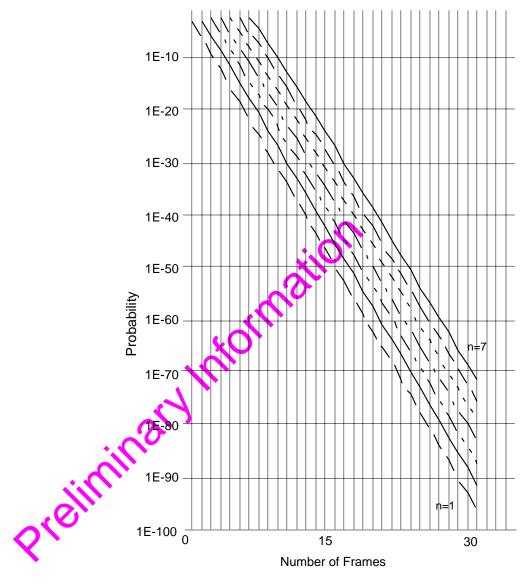

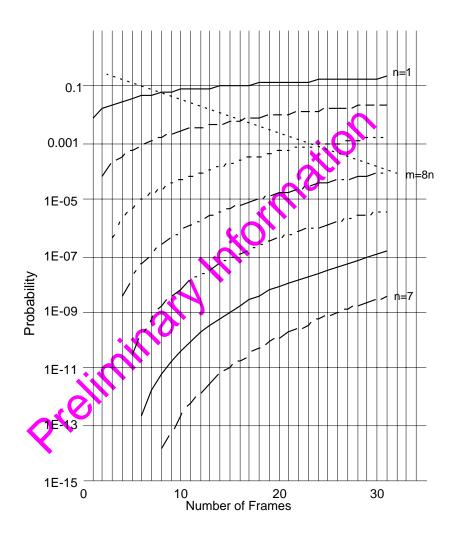

The False Lock Probability (going into or staying in a state of synchronisation although synchronisation is lost), Loss of Sync Probability (detecting an Out\_of\_Sync state in spite of being In\_Sync), Acquisition Time (time needed to assert the In\_Sync condition), and Loss of Sync Time (time required to detect an Out\_of\_Sync situation when synchronisation is lost) are primarily influenced by the parameters: Aq\_Ref\_Thresh, Aq\_Sync\_Thresh, Tr\_Ref\_Thresh and Tr\_Sync\_Thresh, and the BER out of the Viterbi decoder. Typically, in the 1632 bit (204 x 8 = 1632 bits) frame, there are an average of 12.75, including 11.75 coincidental, matches of the (inverted) Sync Byte. Assuming these matches are uniformly distributed in the frame, the number of synchronisation trials (going from the Out\_of\_Sync state into the Acquisition Mode, see Figure 3-12) until the correct position of the Sync Byte is found averages 12.75 times. The probability of not going In\_Sync can be seen in Figure 3-13 for a BER of 5E-2 and in Figure 3-14 for a BER of 1 \* 10<sup>-4</sup>. The value "n" represents the parameter Aq\_Sync\_Thresh and on the x-axis is Aq\_Ref\_Thresh. These figures also show the Loss of Sync Probability if the Frame

Synchroniser is in the Tracking Mode (the value "n" now corresponds to Tr\_Sync\_Thresh and on the x-axis is Tr\_Ref\_Thresh).

The Acquisition Time increases with higher values of Aq\_Ref\_Thresh and decreases with higher MPEG-2 Transport Stream input data rates. Each of the 12.75 synchronisation trials needs the duration of Aq\_Ref\_Thresh (default: 8) times 204 bytes, times 8 bits/byte, and divided by the input data bit rate. At 50 Mbit/s, the time interval until the correct position of the Sync Byte is found averages 3.3 ms at a BER of 5 \* 10<sup>-2</sup>.

Figure 3-13. Loss of Synchronisation Probability for BER=5E-2

Figure 3-14. Loss of Synchronisation for BER=1E-4

The False Lock Probability is independent of the BER and is depicted in Figure 3-15 for both the Acquisition and Tracking Modes. It gives the probability that in a random data stream the specified number of sync byte values (given with the ..\_Sync\_Thres value) in the expected distance of 204 bytes occurs in the specified window of ..\_Ref\_Thresh packets.

Note that whenever a pattern with a period of 1632 bytes is fed into the scrambler at the transmitter side, a bit pattern that accidentally matches the Sync Byte has a 1632 period as well. This applies to any 1632 byte periodical pattern.

**EXAMPLE:** Considering, for example, the case that an all zero bit stream is fed into the scrambling block at the transmitter. The Frame Synchroniser may lock falsely onto this bit pattern, if parameters Aq(Tr)\_Ref\_Thresh are set to eight times Aq(Tr)\_Sync\_Thresh or more (see "m=8n" line in Figure 3-15).

.

Figure 3-15. False Lock Probability

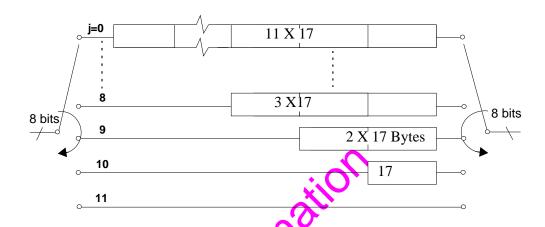

#### 3.2.3.4 Deinterleaver

#### 3.2.3.4.1 Deinterleaver Functionality

The error protected packets of 204 bytes are interleaved in the transmitter and the Deinterleaver must process the byte stream before the Reed-Solomon decoder. The Deinterleaver is a Convolutional Forney Deinterleaver with I=12 branches. Each branch consists of a shift register with M(11-j) cells (M=17, j=branch index). Each register has a word length of eight bits so that

the data stream is deinterleaved byte wise. For synchronisation purposes, the (inverted) Sync Bytes (as well as some 16 other bytes) are always routed in the "0" branch of the Deinterleaver. Figure 3-16 depicts a conceptual diagram of the Convolutional Forney Deinterleaver.

Figure 3-16. Deinterleaver Principle Block Diagram

#### 3.2.3.4.2 Deinterleaver Latency

The latency of the 12x17 Forney Deinterleaver is 17963 CLOCK cycles (not including the Frame Synchroniser synchronisation acquisition time).

#### 3.2.3.5 Reed-Solomon Decoder

#### 3.2.3.5.1 Reed-Solomon Decoder Module

The algorithmic parameters of the Reed-Solomon decoder used in this block were chosen according to the DVB Specifications. The arithmetic is performed using a Finite Field GF(256) of byte data which is specified by the Field Generator Polynomial:

$$p(x) = x^8 + x^4 + x^3 + x^2 + 1$$

The Reed-Solomon decoder works on a shortened (204,188,8) code with Generator Polynomial  $g(x) = (x+\alpha^0)(x+\alpha^1)...(x+\alpha^{15})$ , where  $\alpha$ =0x02. One Codeword consists of a total of 204 bytes, composed of 188 information bytes followed by 16 parity check bytes. Using this code, the Reed-Solomon decoder is able to detect and correct up to 8 byte errors per Codeword (a byte error specifies an erroneous byte, independently of the number of corrupted bits), which can be arbitrarily distributed within the data and check locations in a Codeword.

The following is a summary of the Reed-Solomon parameters:

- R = 16 Check Bytes

- d = 8 Detection Power

- K = 188 Message Length

- m = 8 Symbol Size in Bits

- N = 204 Codeword Length

- T = 8 Number of Error Corrections

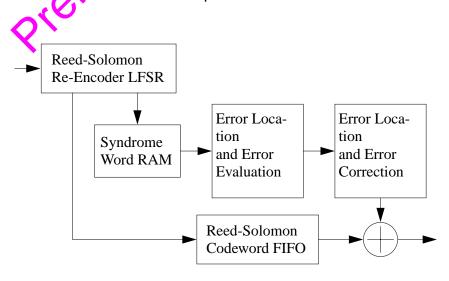

#### 3.2.3.5.2 Reed-Solomon Functional Description

The architecture of the Reed-Solomon decoder is shown in Figure 3-17. The Re-Encoder consists of a Linear Feedback Shift Register (LFSR) of length 16 (bytes) with the feedback connections as specified by the Code Generator Polynomial Coefficients. For each Codeword arriving byte by byte, the Re-Encoder performs a division of this Codeword by the Code Generator Polynomial and stores the remainder. After processing the first 188 information bytes, the Encoder appends the resulting 16 remainder bytes to the byte stream. If, after processing 188 bytes, the Re-Encoder register contents are identical to the 16 last bytes of the Codeword, the Codeword is assumed to have been received without error. Otherwise, the Syndrome (the EXOR of the 16 parity check bytes) and the register contents are stored in the Syndrome RAM.

From the Syndrome, the Reed-Solomon Core iteratively determines the Error Location Polynomial (ELP) and the Error Evaluation Polynomial (EEP). The roots of the ELP specify the error locations inside the Codeword. These roots are determined in the Chien Search Unit, which checks for roots by evaluating the ELP for all 255 possible field elements. Simultaneously, the EEP polynomial is evaluated. For each root found, the corresponding EEP value is used to correct the byte error at the specific bit locations. The input data is stored in the Codeword RAM (Reed-Solomon FIFO) during the operation of the Core and the Chien Search Unit in order to take account of the latencies therein. After the roots and error values are determined by the Chien Search Unit, the data is read from the FIFO, and the necessary byte corrections are performed in the Error Correction Unit.

If more than 8 byte errors occur in a single frame, this is recognized by the decoder and the input data is output unchanged. In this case, the "transport\_error\_indicator" bit in the MPEG-2 Transport Header is set and the RERRU output shall be asserted.

Figure 3-17. Reed-Solomon Block Diagram

#### 3.2.3.5.3 Reed-Solomon Performance Analysis

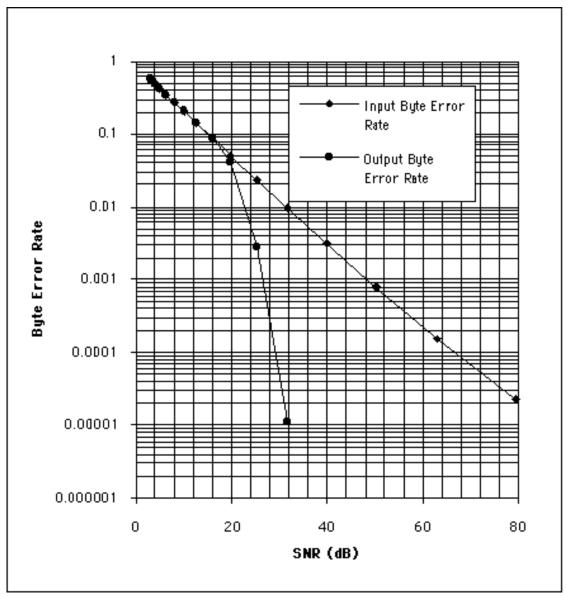

The performance was evaluated by applying BPSK Modulation to the input bits and transmitting over an Additive White Gaussian Noise (AWGN) channel at different Signal-to-Noise Ratios (SNR). The results are shown in Figure 3-18. For high input byte error rates the Reed-Solomon is not able to correct errors since there are too many errors per frame. After crossing the point where the average input byte error rate becomes lower than 8/204, the error correction capability of the (204,188,8) code is used to correct most of the errors, leading to a substantial decrease in byte error rate.

Figure 3-18. Input Byte Error Rate versus Output Byte Error Rate

### Freescale Semiconductor, Inc.

| Device | Description |

|--------|-------------|

|--------|-------------|

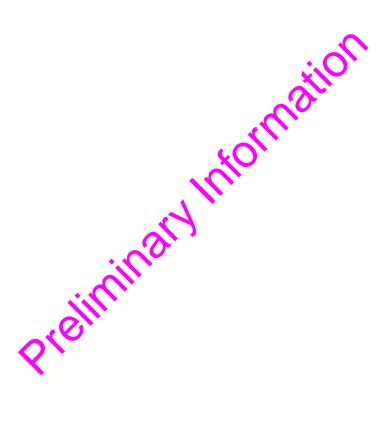

#### 3.2.3.5.4 Reed-Solomon Bit Error and Bad Frame Monitor

There are two parameters accessible through the I<sup>2</sup>C Interface that the Reed-Solomon decoder circuit uses to track error rates: BER\_COUNT and BAD\_FRAME.

#### BAD FRAME

This parameter gives the number of bad frames that could not be decoded and corrected during an interval of frames specified through TIME\_COUNT (another I<sup>2</sup>C Interface parameter register).

#### BER\_COUNT

BER\_COUNT is the number of bit errors within the 188 information bytes during the same interval of frames specified by TIME\_COUNT. Hence, in order to determine a bit error rate, one Codeword should be counted as 188 bytes instead of 204 bytes. If more than 8 byte errors occur in a frame, BER\_COUNT cannot be updated since it is not possible to determine how many bits were corrupted. To obtain a better estimate of the BER rate into the Reed-Solomon decoder block when more than 8 bytes are corrupted, BAD\_FRAME and BER\_COUNT should be combined.

#### TIME\_COUNT

The parameter TIME\_COUNT specifies the number of Codewords during which the bit errors and bad frames are counted (note that a frame is used here to denote a Codeword of 204 bytes). The number of Codewords is given by (TIME\_COUNT \* 4) + 2. In addition, BER\_COUNT and BAD\_FRAMES are updated every (TIME\_COUNT \* 4) + 2 Codewords only. Internally, the corresponding counters are reset and immediately work on the following (TIME\_COUNT \* 4) + 2 window. Both counters have overflow protection; therefore, once the maximum value is reached, it will remain stable throughout the entire period.

As an example, consider the calculation of the post-Viterbi BER using these registers. In the default configuration TIME\_COUNT contains 255, resulting in a number of (255 \* 4 + 2) = 1022 MPEG-2 packets for the update period of the BAD\_FRAME and BER\_COUNT registers.

After reading both values immediately one after the other to ensure consistency of the results, first check the BAD\_FRAME. If it contains zero there were not more than 8 wrong bytes in all the MPEG-2 packets watched in the update period completed before the read-out. The **exact** number of bit errors detected and corrected by the Reed-Solomon decoder is therefore given in the BER\_COUNT register.

To calculate the BER after the Viterbi decoder use the formula

with the number of wrong bits in the numerator and the total number of bits (188 bytes per MPEG-2 packet) in the denominator.

If the BAD\_FRAME is **not zero** there was **at least one** packet with more than 8 wrong bytes leading to a **not correctable packet**. This prevents the BER\_COUNT from being updated

#### Freescale Semiconductor, Inc.

correctly, therefore the number of wrong bits given there does not contain the wrong bits in the uncorrectable packets. Therefore the post-Viterbi BER from the above formula is not applicable.

A threshold value of the post-Viterbi BER for the exact value can be obtained by taking the worst condition of 8 single bit errors leading to 8 wrong bytes in one RS packet of 204 bytes. This gives  $8/(204*8) \sim 4.9*10^{-3}$ . If this threshold is kept in all packets of the update period the BER\_COUNT is guaranteed to be exact and the BAD\_FRAME is automatically zero. In case of more than one wrong bit in one byte the BAD\_FRAME still is zero. But of more than 8 wrong bytes are detected by the RS decoder the BAD\_FRAME is incremented, leading to an invalid BER calculation using the BER COUNT.

#### 3.2.3.5.5 Typical Selection of the Parameters for System Application

For the transmission conditions specified by the DVB, there should be only one frame with more then 8 byte errors per hour of operation. Therefore, the default setting is TIME\_COUNT = 255, which means that  $(255 \times 4) + 2 = 1022$  frames are checked. For a typical transmission scenario, the BER\_COUNT should then include an averaged figure of the transmission quality before the Reed-Solomon, while the BAD\_FRAMES value should be zero.

#### 3.2.3.5.6 Reed-Solomon Decoder Latency

The latency of the Reed-Solomon is 3557 CLOCK cycles.

#### 3.2.3.6 Descrambler

#### 3.2.3.6.1 Descrambler Module

To provide an even frequency spectrum distribution across the channel bandwidth and to allow for easier clock recovery, the data is scrambled prior to transmission with a Pseudo-Random Binary Sequence (PRBS) specified by the polynomial 1+x<sup>14</sup>+x<sup>15</sup>. This block performs the descrambling of the Reed-Solomon output to obtain the originally encoded data.

#### 3.2.3.6.2 Descrambler/Synchronisation Functionality

The PRBS generator's applied to all data except for the MPEG-2 Transport Stream Sync Bytes and inverted Sync Bytes. The seven Sync Bytes of a superframe pass the Descrambler unchanged, although the PRBS generator operates continuously, i.e. the output of the Descrambler is temporarily disabled for the specific transmission of a Sync Byte. Therefore, the period of the PRBS generator is still kept to 1504 bytes (8 x 188).

In addition to the PRBS functionality this unit also re-inverts the inverted Sync Byte occurrences, thereby removing the superframe structure.

It must be pointed out that the Descrambler will take a maximum value of 7 frames to synchronise internally to the inverted Sync Byte that denotes the superframe boundaries for the correct initialization of the PRBS. This may happen even after the Reed-Solomon decoder Block has signalled a valid synchronisation state by asserting the IN\_SYNC signal pin and is already providing MPEG-2 Transport Stream Bytes at the SPO[7:0] output signal pins and generating waveforms at the other related outputs. Therefore, it is recommended to wait for this period of time after Synchronisation Acquisition has been signalled by the Frame Synchroniser at the

signal pins, before the decoding process of output data is initiated, e.g. within the MPEG-2 Transport Stream Demultiplexer.

#### 3.2.3.6.3 Descrambler Latency

The latency of the Descrambler is 13 CLOCK cycles.

PreliminaryInformation

Preliminary Information

# SECTION 4 DVB-T DEMODULATOR INTERFACES

Extensive control and insight into all relevant system parameters is given to the user of Motorola's single chip DVB-T demodulator by the interfaces of the IC. To control the actions of the chip several status lines as well as internal registers are provided. The information presented in this section describes the details of the external interfaces. Also all the information necessary to understand the setup of the circuit as described in Section 5 is given.

According to the characteristics of the interfaces the description is separated into the (physical) control lines and software controllable registers.

# 4.1 General Purpose Outputs

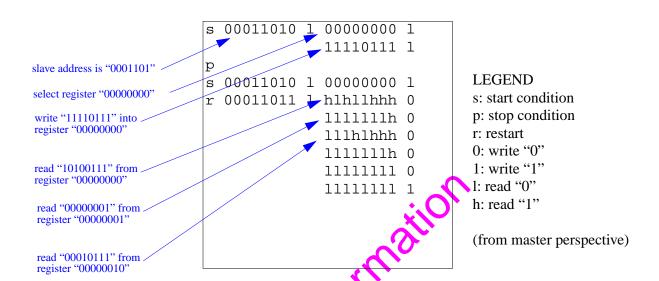

Four general purpose output pins are provided that can be set via the I<sup>2</sup>C interface of the FEC block. The corresponding bits reside in the 4 MSBs of the SOFT\_RESET register (address \$1F in the FEC block), these bits set the outputs of the GP[3:0] pins (pin numbers 104, 102, 99 and 97) of the MC92314.