# 12-Bit A/D Converter with 4-Channel Multiplexer Preliminary Data Features 12-bit resolution Autocalib

SDA 0812 A **SDA 1812 D**

# **CMOS**

- Autocalibration circuitry

- No offset or gain adjustments required

- Total unadjusted error ± 1/2 LSB max. (SDA 0812 A) respectively ± 3/4 LSB max, (SDA 1812 D)

- Fast conversion time (6 μs)

- SDA 1812 D with over 100 kHz sampling rate

- No missing codes

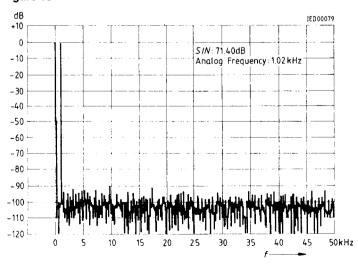

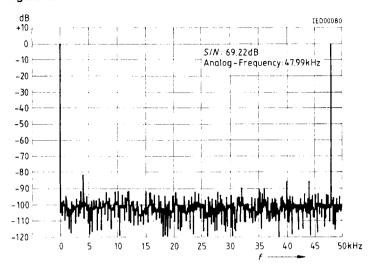

- S/N + THD together 71 dB typ

- Single 5 V supply

- 4-channel multiplexer with latched control logic

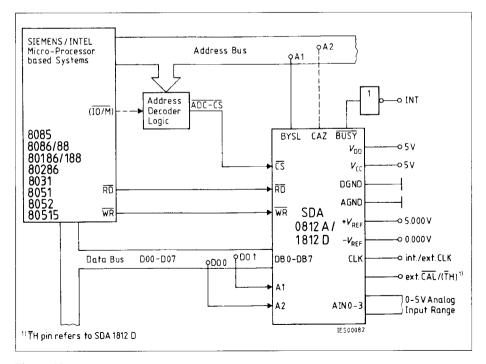

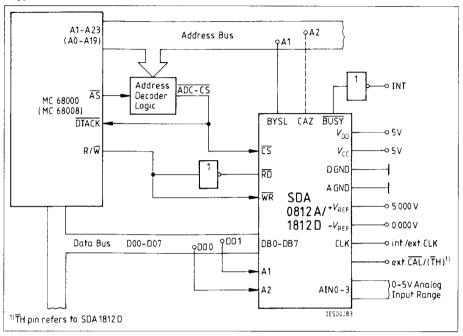

- Easy interfacing to 8- and 16-bit microprocessors

- Data output in a 2-byte format

- 0 V to 5 V analog input voltage range

- Digital inputs and outputs are TTL compatible

- Standby mode (50 µW typ)

- CMOS low power consumption (10 mW typ)

- Temperature range 40 to 85 °C

P-LCC-28-2

| Туре              | Ordering Code | Package          |                  |

|-------------------|---------------|------------------|------------------|

| S SDA 0812 A      | Q67100-A8233  | P-DIP-28         | c <sub>O</sub> , |

| SDA 0812 AN       | Q67100-H8300  | P-LCC-28-2 (SMD) |                  |

| S SDA 1812 D      | Q67100-H8291  | P-DIP-28         |                  |

| SDA 1812 DN       | Q67100-H8301  | P-LCC-28-2 (SMD) | - Cili           |

|                   |               | MM Dajas         |                  |

| Semiconductor Gro |               | 413              | 9.9              |

# **General Description**

SDA 0812 A and SDA 1812 D are monolithic CMOS 12-bit analog to digital converters with a 4-channel analog multiplexer. They need only a 5 V supply and achieve a conversion time of  $6\,\mu s$  plus  $2.5\,\mu s$  sample time.

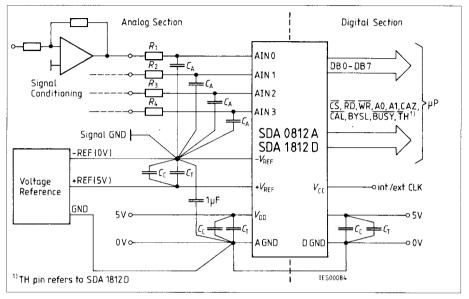

They use the method of successive approximation based on a capacitor network. An autocalibration circuit guarantees a total unadjusted error within  $\pm$  1/2 LSB max. (SDA 0812 A) respectively  $\pm$  1/2 LSB typ. (SDA 1812 D). Therefore the device needs no external offset or gain adjustments. The converters feature a temperature stabilized differential comparator, a sample and hold function and a 12-bit data output in a 2-byte format. Designed for easy microprocessor interface using the standard control signals CS, RD and WR the 4-channel input multiplexer is controlled via address inputs A0 and A1.

Two converter busy flags are available to facilitate polling of the converter's status.

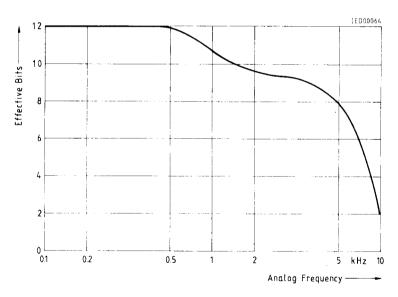

With a sample and hold circuit on chip, the SDA 1812 D is suited for digitizing AC signals as well as DC signals. The maximum sampling rate of the SDA 1812 D is more than 100 kHz according to  $2.5\,\mu s$  sample time plus  $6\,\mu s$  conversion time. The SDA 1812 D is specified with traditional static specifications as well as with dynamic specifications (SNR, THD, effective number of bits).

The temperature range of the SDA 0812 A/1812 D is - 40 °C to 85 °C.

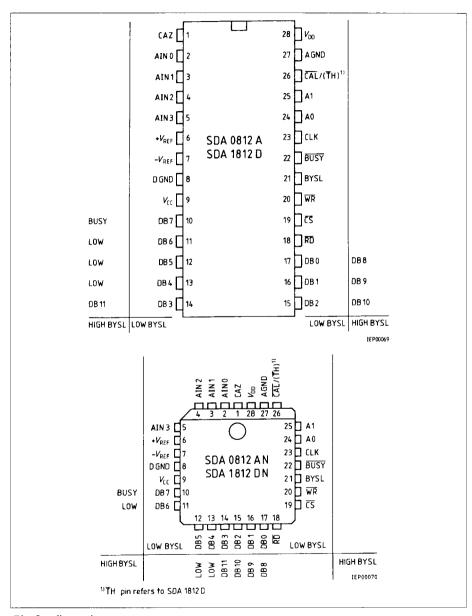

Pin Configurations

(top view)

# Pin Definitions and Functions

| Pin                               | Symbol                                                             | Function                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1                                 | CAZ                                                                | Special function pin (see Reading the Conversion Results, SFR and Internal Clock Operation). Connect to a MP address pin. If not used, CAZ can be connected to AGND or DGND or can be unconnected.                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 2-5                               | AIN 0 to AIN 3                                                     | Analog Input, channel 0 to channel 3                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

| 6                                 | + VREF                                                             | Pos. voltage reference input, + $V_{REF} = 5 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 7                                 | - VREF                                                             | Neg. voltage reference input, $-V_{REF} = 0 \text{ V}$                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| 8                                 | DGND                                                               | Digital Ground, DGND = 0 V                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| 9                                 | Vcc                                                                | Logic supply voltage, $V_{CC} = 5 \text{ V}$ must not be applied before $V_{DD}$ !                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

| 10-17  10 11 12 13 14 15 16 17 18 | DB7-DB0  Symbol (BYSL = HIGH) BUSY LOW LOW DB11 (MSB) DB10 DB9 DB8 | Three-state data outputs.  Data Bus output (CS, RD = LOW)  Symbol (BYSL = LOW)  DB7 BUSY is an active high converter status flag. It is high  DB6 during a conversion and during autocalibration.  DB5 LOW Pin 11 to pin 13 are tied to DGND when  DB4 BYSL = HIGH  DB3 DB11 is the MSB.  DB2  DB1  DB0 (LSB) DB0 is the LSB.  Read input, active low, is used to read the data outputs in combination with CS and BYSL. |  |  |  |  |  |  |  |

| <del></del>                       | CS                                                                 | Chip Select input, active low.                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                                   |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| 20                                | WR                                                                 | <b>Write</b> input, active low, is used to start a new conversion and to select an analog channel via address inputs A0, A1 in combination with CS low. The minimum WR pulse width is 100 ns. It is independent of internal/external clock operation.                                                                                                                                                                    |  |  |  |  |  |  |  |

| 21                                | BYSL                                                               | Byte Select input, is used to select high or low data output byte in combination with CS and RD, or to select SFR.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

# Pin Definitions and Functions (cont'd)

| Pin   | Symbol   | Function                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

|-------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 22    | BUSY     | Converter status output. BUSY is low during conversion or autocalibration. BUSY is high after the converter has finished its operation.                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| 23    | CLK      | Clock input for internal/external clock operation. For external clock operation connect pin 23 to a 74HC compatible clock source. For internal clock operation connect pin 23 to a R timing component (see Clock Operation description).                                                                                                                                                   |  |  |  |  |  |  |  |

| 24-25 | A0 to A1 | <b>Address</b> inputs, are used to select one of four analog input channels, in combination with $\overline{\text{CS}}$ and $\overline{\text{WR}}$ . The address inputs are latched with the rising edge of $\overline{\text{WR}}$ .                                                                                                                                                       |  |  |  |  |  |  |  |

|       |          | A1 A0 Selected Channel                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |

|       |          | LOW LOW AIN0<br>LOW HIGH AIN1<br>HIGH LOW AIN2<br>HIGH HIGH AIN3                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 26    | CAL/TH1) | Calibration input. An autocalibration cycle is initiated with CAL = LOW. If not used, CAL can be connected to Vcc or unconnected. In this case autocalibration is only initiated by power-up/powerfail, or by SFR. The minimum pulse width of CAL is 100 ns. Using the SDA 1812 D, via SFR the function of pin 26 can be defined as an external Track-Hold (TH) pin (see SFR description). |  |  |  |  |  |  |  |

| 27    | AGND     | Analog Ground, AGND = 0 V                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |  |

| 28    | $V_{DD}$ | Analog supply, $V_{DD} = 5 \text{ V}$ , must not be applied after $V_{CC}$ !                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

<sup>1)</sup> TH-pin refers to SDA 1812 D

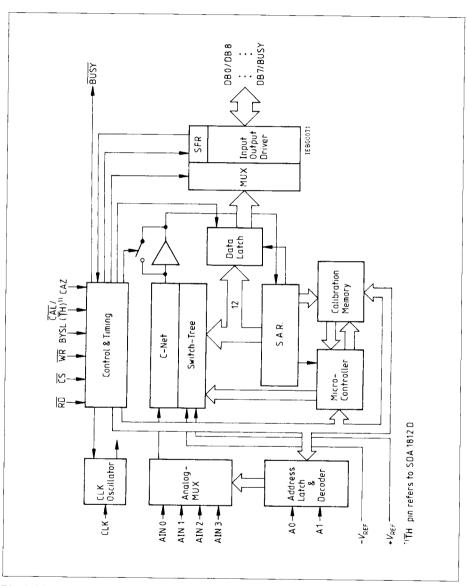

**Block Diagram**

# **Functional Description**

SDA 0812 A and 1812 D are 4-channel 12-bit A/D converters. The successive approximation technique provides 6  $\mu s$  conversion time. The required sampling time of the on-chip sample-and-hold-circuit is 2.5  $\mu s$ . An autocalibration technique guarantees a total unadjusted error within  $\pm$  1/2 LSB max. (SDA 0812 A) and  $\pm$  3/4 LSB max. (SDA 1812 D) over the entire temperature range. The major components are shown in the **block diagram.**

The comparator is a fully differential autozeroed one for a high power supply rejection ratio and very low offset voltages. The charge redistribution design using a binary weighted capacitor network inherents the sampling function to convert AC-signals (SDA 1812 D). A Sub-C Network is used to correct linearity-errors in the Main-Capacitor Network. The correction terms are calculated by a microcontroller in an autocalibration cycle, started by power-up or CAL signal. The correction terms are stored in a calibration memory. The stability of integrated C-Networks guarantees the correction terms to be valid over time and temperature. In the case of a power up/power fail (Vcc less then 3 V typical) new calibration cycles will be initiated automatically. This guarantees the integrity of the correction terms.

Three-state output drivers with multiplexer for 2-byte data format, an analog multiplexer with address latch and a clock oscillator with external or internal clock operation complete the functional components of the device.

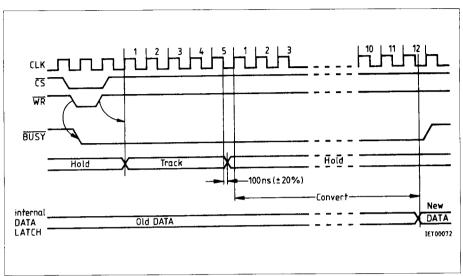

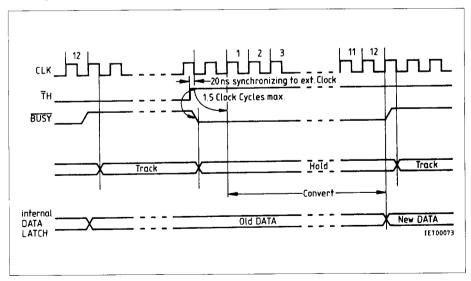

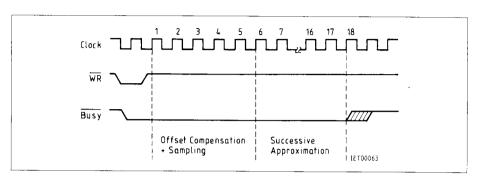

# A/D Converter Timing

# SDA 0812 A

After a conversion has been started with the rising edge of WR the analog input voltage is sampled for 5 clock cycles. The analog source must be capable to charge the capacitor network of appr. 50 pF to full accuracy in this time. In parallel an offset compensation mechanism reduces the comparators offset error below 1/4 LSB. During this period the converter is susceptable to spikes and noise at the analog input, which may cause erroneous codes at the digital outputs. Therefore RC-filtering at the analog inputs is recommended.

Conversion of the sampled analog voltage takes place between the 6th and 17th clock cycle. The CAZ pin is not used for normal operation. However CAZ serves as an additional programming pin. (See Special Function Register).

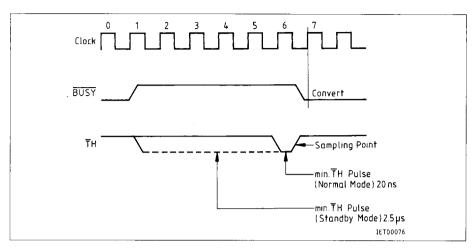

# **SDA 1812 D**

After a conversion has been started with the rising edge of WR the analog input voltage is sampled for 5 clock cycles. The analog source must be capable to charge the capacitor network of appr. 50 pF to full accuracy in this time.

By starting a conversion with WR sampling of the analog signal is defined by the first rising edge of the internal CLK pulse + 4.5 clock cycles + 100 ns (typ) after the rising edge of WR. For precisely defined sampling point WR has to be synchronized with CLK. The conversion of the sampled analog voltage takes place between the 6th and 17th clock cycle.

To avoid synchronizing problems between WR and CLK the CAL pin is programmable into an external Track-Hold pin (TH) via SFR. A low to high transition at this pin defines the sampling point of the ADC with a delay time of 5 ns typ. without synchronizing to CLK. The low pulse width of TH defines the tracking period of internal sample and hold circuit

and should be 2.5  $\mu$ s min. Using this TH pin an additional offset error of  $\pm$  1 LSB may occure. This TH pin should be used in combination with on chip clock generator. Using external clock generator in combination with asynchronous TH function brings offset errors up to  $\pm$  4 LSB via pin coupling effects. By synchronizing the TH signal with external CLK this offset error can be reduced again to  $\pm$  1 LSB. The best conditions are given by delaying the falling clock slope 20 ns to the rising edge of TH.

The SDA 1812 D operates with the master clock. The conversion cycle may not begin until up to 1.5 clock cycles after TH goes high.

The CAZ pin is not used for normal operation. However CAZ serves as an additional programming pin (see Special Function Register).

# Autocalibration

An autocalibration cycle is started

- with the rising edge of a CAL low pulse

- by setting the DB1 in the Special Function Register (SFR)

- by power-up/power-fail

and takes 168 clock cycles. Finally a normal conversion (17 clock cycles) is added automatically. During an autocalibration or conversion cycle each power supply voltage and each reference voltage has to be stable. Therefore an internal timer provides a waiting period of 42 240 clock cycles between power up/power fail and autocalibration function. Power up calibration is finished after 42 425 (42 240 + 168 + 17) clock cycles.

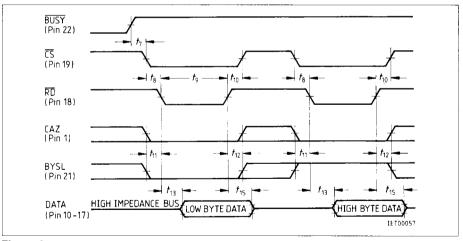

# Reading the Conversion Results

# Normal Mode (Transparent)

The data is read as two 8-bit bytes. The converters digital outputs are positive true. Data is presented in right justified format (i.e., the LSB is the most right-hand bit in a 16-bit word). Two READ operations are required, the BYSL input determines which byte is to be read. Because the conversion results are held in a successive approximation register the high byte may be read out before the conversion is finished.

The 4 most significant bits are valid in the 10<sup>th</sup> clock cycle after starting a conversion with WR. Valid 12-bit data are available for reading after the BUSY pin has gone high, or internal status flag BUSY (available on pin 10) has gone low.

# **Latched Output Mode**

An additional function is reading the data is available via an integrated data latch, which is transparent in normal function mode.

The latched output function may be activated by writing high on DB0 and low on DB7 (see Special Function Register SFR) with  $\overline{W}\overline{R}$ ,  $\overline{CS}$  active in combination with CAZ and BYSL pin high.

The data latch is set transparent by power-up.

When the latch function is active an internal generated latch enable signal shifts the data from the SAR into a 12-bit latch. This occures when BūSŸ gets inactive (high). The conversion result is valid during the next conversion cycle until new data is latched. Therefore it may be read out even after starting a new conversion.

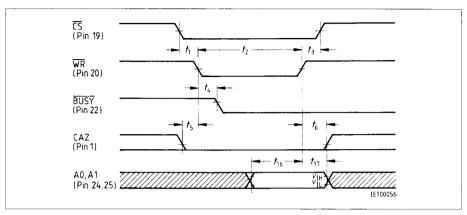

Figure 1 Starting a Conversion with WR

Figure 2 Starting a Conversion with TH (SDA 1812 D)

may be synchronous with internal clock generator and should be synchronized with external clock for best performance.

# The Special Function Register (SFR)

An internal register for additional functions programmed by the microprocessor is available.

# **Special Functions**

# SDA 0812 A

- 12-bit data latch is enabled by setting SFR DB0 high.

- INT-CAL starts a calibration by setting SFR DB1 high, the timing of this calibration refers to EXT-CAL function (168 + 17 clock cycles).

- The converter is set to a standby mode by programming DB3 high. In this mode the analog circuit and the internal CLK-generator are deactivated, total power consumption reduced to 50 μW typ. Wake up the converter by writing low to DB3, ext. CAL, INT-CAL (DB1) or power-up function (Vcc < 3 V). Applying Cs and WR (start of conversion) during standby mode (DB3 high) delivers one correct conversion result, subsequently the converter goes back to standby mode until new conversion start or wake-up signal.</p>

- POWER FAIL FLAG is set if a power fail occured, showing that a new calibration was started (BUSY active) and that the data of SFR (data latch enable) are lost. To reset this flag write low to DB5.

- CAL-ERROR flag is set on DB6 if a calibration overflow occurs (may be in very noisy systems). It is reset by starting a calibration and remains low after a properly finished calibration.

- BUSY flag is high (DB7) if a calibration or a conversion is in process.

### **SDA 1812 D**

- 12-bit data latch is enabled by setting SFR DB0 high.

- INT-CAL starts a calibration by setting SFR DB1 high, the timing of this calibration refers to EXT-CAL function (168 + 17 clock cycles).

- The CAL pin function is modified to an ext. Track-Hold (TH) function by setting DB2 high. Reset the function to CAL by writing low into DB2. The ext. Track-Hold pin (TH) guarantees sampling points precisely defined by the rising edge of TH signal. The internal sampling point is delayed 5 ns typ. to the external TH slope.

- The SDA 1812 D is set to a standby mode by programming DB3 high. In this mode the analog circuit and the internal CLK-generator are deactivated, total power consumption reduces to 50 μW typ. Wake up the SDA 1812 with writing low to DB3, EXT-CĀL, INT-CAL (DB1) or power-up function (Vcc > 3 V). Applying WR and Cs or a rising edge on TH pin (Conversion Start) during standby mode (DB3 high) delivers one correct conversion result, subsequently the SDA 1812 D goes back to standby mode until new SOC or WAKE UP signal.

- POWER FAIL FLAG is set if power fail occured (DB5), showing that a new calibration has been started (BUSY active) and that the data of SFR (data latch enable CÄL/TH pin programming) are lost. To reset this flag write low to DB5.

- CAL-ERROR flag is set on DB6 if a calibration overflow occures (may be in very noisy systems), is reset by starting a calibration and remains low after a properly finished calibration.

- BUSY FLAG is high (DB7) if a calibration or a conversion is in process.

Note that all programmable bits of the SFR are reset to low by power-up.

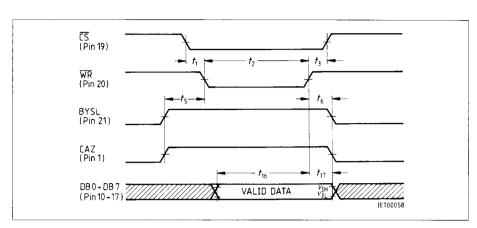

# Writing the SFR (SDA 0812 A/1812 D, see figure 9)

The SFR is activated by pulling CAZ and BYSL pins high and loading a data word with a general low on DB7 by a microprocessor WRITE cycle.

| other<br>DB | DB7 | DB5  | DB3  | DB2*) | DB1  | DB0  | CS/<br>WR | CAZ/<br>BYSL | Function                         |

|-------------|-----|------|------|-------|------|------|-----------|--------------|----------------------------------|

| reserved    | LOW | LOW  |      | _     |      |      | active    | HIGH         | Reset of POWER FAIL FLAG         |

| reserved    | LOW | HIGH |      |       |      |      | active    | HIGH         | Set POWER FAIL FLAG (not locked) |

| reserved    | LOW |      | LOW  |       | _    |      | active    | HIGH         | Wake-up from STANDBY             |

| reserved    | LOW |      | HIGH |       |      |      | active    | HIGH         | STANDBY mode active              |

| reserved    | LOW |      | _    | LOW   |      |      | active    | HIGH         | CAL function on pin 26           |

| reserved    | LOW |      |      | HIGH  |      |      | active    | HIGH         | TH function on pin 26            |

| reserved    | LOW |      |      |       | LOW  |      | active    | HIGH         | _                                |

| reserved    | LOW | -    |      |       | HIGH |      | active    | HIGH         | INT-CĀL is initiated             |

| reserved    | LOW |      |      |       |      | LOW  | active    | HIGH         | Output data latch transparent    |

| reserved    | LOW |      |      |       |      | HIGH | active    | HIGH         | Output data<br>latch enabled     |

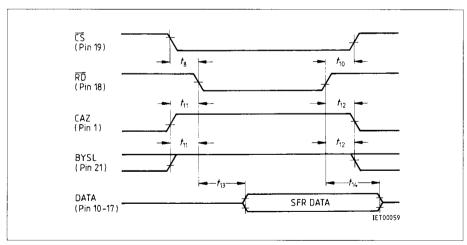

# Reading the SFR (SDA 0812 A; see figure 10)

The contents of SFR are put to the DATA BUS by a microprocessor READ cycle in combination with BYSL and CAZ high.

| Data Bus Pin | Function                                             |

|--------------|------------------------------------------------------|

| DB0          | DATA LATCH State: HIGH enabled, LOW transparent      |

| DB1          | CAL FLAG: HIGH during calibration                    |

| DB2          | RESERVED                                             |

| DB3          | HIGH if STANDBY mode is active                       |

| DB4          | RESERVED                                             |

| DB5          | POWER FAIL FLAG: HIGH if power fail occured          |

| DB6          | CAL ERROR FLAG: HIGH if calibration overflow occured |

| DB7          | BUSY FLAG: HIGH during calibration or conversion     |

**Warning:** Reading on CAZ high and BYSL low is prevented for factory use, unpredictable data may appear on the data bus.

<sup>&</sup>quot;) Refers to SDA 1812 D

# Reading the SFR (SDA 1812 D; see figure 10)

The contents of SFR are put to the DATA BUS by a microprocessor READ cycle in combination with BYSL and CAZ high.

| Data Bus Pin | Definition                                           |  |  |  |  |

|--------------|------------------------------------------------------|--|--|--|--|

| DB0          | DATA LATCH State: HIGH enabled, LOW transparent      |  |  |  |  |

| DB1          |                                                      |  |  |  |  |

| DB2          | CAL/TH: HIGH for TH, LOW for CAL function            |  |  |  |  |

| DB3          | HIGH if STANDBY mode is active                       |  |  |  |  |

| DB4          | RESERVED                                             |  |  |  |  |

| DB5          | POWER FAIL FLAG: HIGH if power fail occured          |  |  |  |  |

| DB6          | CAL ERROR FLAG: HIGH if calibration overflow occured |  |  |  |  |

| DB7          | BUSY FLAG: HIGH during calibration or conversion     |  |  |  |  |

Reading on CAZ high and BYSL low is reserved for factory use only, unpredictable data may appear on the data bus.

# Internal Clock Operation

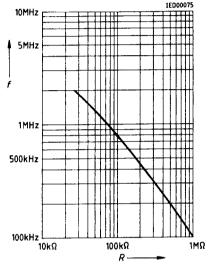

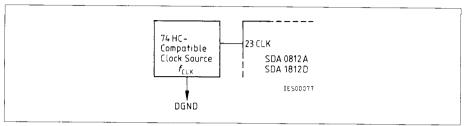

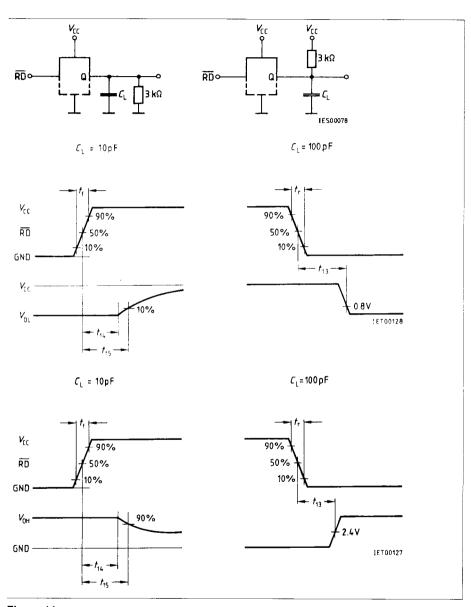

The external circuitry for internal clock operation is shown in figure 3.

23 CLK

SDA 0812A

SDA 1812D

IES00074

Figure 3

The Internal Clock Frequency only depends on the R Value

Figure 4

Clock Frequency of Internal Clock

Generator versus External Resistor Value

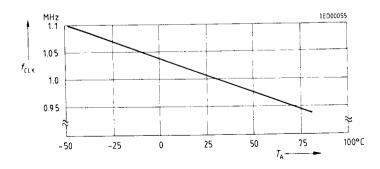

The clock generator can be operated between 100 kHz and 2 MHz. Note that the specifications are referenced to  $f_{\text{CLK}} = 2$  MHz. Typically, the specified accuracy is maintained from 0.5 to 2.0 MHz.

The actual operating frequency of the internal clock oscillator can vary from device to device. Therefore for precisely defined conversion times usage of an external clock generator is recommended.

Figure 5

Typical Internal Clock Frequency versus Temperature

# **External Clock Operation**

The required circuitry for external clock operation is shown in figure 6.

Figure 6

The external clock source has to provide 0.8 Vmax for low voltage level and 3.5 Vmin for high voltage level. The rise and fall times have to be 200 ns max. The minimal pulse width of ext. CLK has to be 200 ns.

There is no synchronizing between external clock and ext. TH signal. Synchronizing should be provided for optimal performance, see A/D converter timing on page 9. Note that the specifications are referenced to  $f_{\rm CLK} = 2$  MHz. Typically, the specified accuracy is maintained from 0.5 to 2.2 MHz.

# **Absolute Maximum Ratings**

| Parameter                                                          | Symbol                  | Lim   | Units     |    |  |

|--------------------------------------------------------------------|-------------------------|-------|-----------|----|--|

|                                                                    |                         | min.  | max.      | V  |  |

| Supply voltages <sup>1)</sup>                                      | $V_{\rm CC},V_{\rm DD}$ |       | 6.5       |    |  |

| Input voltage range (all inputs)                                   | Vı                      | - 0.3 | Vcc + 0.3 | V  |  |

| Package dissipation (at or below 25 °C free-air temperature range) |                         |       | 875       | mW |  |

| Ambient temperature                                                | TA                      | - 40  | 85        | Č  |  |

| Storage temperature                                                | Tstg                    | - 65  | 125       | °C |  |

### Note

<sup>1)</sup> All voltage values are with respect to network ground terminal

# Characteristics (SDA 0812 A)

**SIEMENS**

$V_{\text{CC}} = 5 \text{ V} \pm 5 \text{ %}, V_{\text{CC}} = 5 \text{ V} \pm 5 \text{ %}, V_{\text{REF}} \le V_{\text{DD}} \ge V_{\text{CC}}, -V_{\text{REF}} = 0 \text{ V}, \text{DGND} = 0 \text{ V}, \text{AGND} = 0 \text{ V}$   $f_{\text{CLK}} = 2 \text{ MHz}, \text{ all specifications } t_{\text{min}} \text{ to } t_{\text{max}} \text{ unless otherwise specified.}$

| Parameter                                                     | Symbol     | Lir        | nit Va | lues                                            | Unit  | Test Condition                      |  |

|---------------------------------------------------------------|------------|------------|--------|-------------------------------------------------|-------|-------------------------------------|--|

|                                                               |            | min.       | typ.   | max.                                            |       | <u> </u>                            |  |

| Accuracy                                                      |            |            |        |                                                 |       |                                     |  |

| Resolution                                                    |            | 12         | - "    |                                                 | Bit   | No missing                          |  |

|                                                               |            |            |        | , ,,                                            |       | codes guaranteed                    |  |

| Total unadjusted error 1)                                     | TUE        |            |        | +/- 1/2<br>+/- 1/2                              |       | All channels, AIN0-AIN3             |  |

| Differential nonlinearity                                     | DNL<br>GE  |            |        | +/- 1/2                                         |       | All channels, AIN0-AIN3             |  |

| Full scale error (gain error)                                 | OFS        |            |        | +/- 1/4                                         |       | All channels, AINO-AIN3             |  |

| Offset error<br>Channel to channel                            | UF3        |            | İ      | <del>                                    </del> | LOD   | All Grannels, All to All to         |  |

| mismatch                                                      |            |            |        | +/- 1/4                                         | LSB   |                                     |  |

| Analog Inputs                                                 |            |            |        |                                                 |       |                                     |  |

| Analog input range                                            | Vain       | $-V_{REF}$ |        | $V_{REF}$                                       | ٧     |                                     |  |

| Slew rate <sup>2)</sup>                                       | SR         |            |        | 8                                               | mV/μs |                                     |  |

| Multiplexer                                                   |            |            |        |                                                 |       |                                     |  |

| Settling time                                                 |            |            | 20     |                                                 | ns    | Switch delay after                  |  |

| ON-resistance                                                 | RON        |            | 2      |                                                 | kΩ    | programming                         |  |

| OFF-resistance                                                | ROFF       |            | 10     |                                                 | МΩ    | the input channel                   |  |

| On channel                                                    |            |            | F0     |                                                 |       |                                     |  |

| input capacitance                                             | Cain       | ì          | 50     |                                                 | рF    |                                     |  |

| Input leakage current                                         | IAIN       |            |        | 10                                              | nA    | AINO-AIN3                           |  |

| at 25 °C                                                      | IAIN       |            |        | 100                                             | nA    | AII VO AII VO                       |  |

| at t <sub>min</sub> to t <sub>max</sub> On-state bias current | I AIN      |            | +/- 5  |                                                 | μA    | Depends on analog inpu              |  |

| On-state bias current                                         |            |            | ., .   |                                                 |       | voltage                             |  |

| Reference Inputs                                              |            |            |        |                                                 |       |                                     |  |

| Positive reference voltage                                    | + VREF     | 4.75       | 5      | $V_{DD}$                                        | ٧     | For specified                       |  |

| Negative reference voltage                                    | $-V_{REF}$ |            | 0      |                                                 | V     | performance                         |  |

| Input reference current                                       | IREF       |            | 10     | 100                                             | μA    |                                     |  |

| Power supply rejection                                        | $V_{DD}$   |            | ± 1/8  |                                                 | LSB   | V <sub>REF</sub> = 4.75 V to 5.25 V |  |

| Logic Inputs                                                  |            |            |        |                                                 | ,     |                                     |  |

| CAZ (pin 1), RD (pin 18),                                     |            |            |        |                                                 |       |                                     |  |

| CS (pin 19), WR (pin 20),                                     |            |            |        |                                                 |       |                                     |  |

| BYSL (pin 21), A0 (pin 24),                                   |            |            |        |                                                 |       |                                     |  |

| A1 (pin 25), CAL (pin 26)                                     |            |            |        |                                                 | ,,    |                                     |  |

| L-input voltage                                               | VIL        | 2.4        |        | 0.8                                             | V     |                                     |  |

| H-input voltage                                               | Vıн        | 1          |        |                                                 | V     |                                     |  |

Notes see next page

# Characteristics (cont'd)

| Parameter                                                                                | Symbol                     | Li          | mit V | alues            | Unit                     | Test Condition                                                                   |

|------------------------------------------------------------------------------------------|----------------------------|-------------|-------|------------------|--------------------------|----------------------------------------------------------------------------------|

|                                                                                          |                            | min.        | typ.  | max.             |                          |                                                                                  |

| Logic Inputs                                                                             |                            |             |       |                  |                          |                                                                                  |

| Input current<br>at 25 °C<br>at – 40 °C 85 °C                                            | In<br>In                   | - 1<br>- 10 |       | 1 10             | μ <b>Α</b><br>μ <b>Α</b> | $V_{\text{IN}} = 0 \text{ V to } V_{\text{CC}}$                                  |

| CLK (pin 23)<br>L-input voltage<br>H-input voltage<br>L-input current<br>H-input current | Vіц<br>Vін<br>Иц<br>Иц     | 3.5<br>- 10 |       | 0.8<br>10<br>1.5 | V<br>V<br>μA<br>mA       | 100 nA max. during standby                                                       |

| Logic Outputs                                                                            |                            |             |       |                  |                          |                                                                                  |

| DB0 to DB7 (pins 10 to 17),<br>BUSY (pin 22)<br>L-output voltage<br>H-output voltage     | <i>V</i> аL<br><i>V</i> ан | 4.0         |       | 0.4              | V                        | /SINK = 1.6 mA<br>/SQURCE = 200 µA                                               |

| Floating state leakage<br>current (pins 10-17)                                           |                            | - 1         |       | 1                | μА                       | $V_{\text{OUT}} = 0 \text{ V to } V_{\text{CC}}$                                 |

| Floating state output capacitance                                                        | Co                         |             |       | 15               | pF                       |                                                                                  |

| Conversion Time                                                                          |                            | -           | •     | J                |                          | 1                                                                                |

| With external clock with internal clock $(T_A = 25  ^{\circ}\text{C})$                   | t<br>t<br>t                | 6<br>7.5    |       | 24               | μS<br>μS<br>μS           | fctk = 500 kHz<br>fctk = 2 MHz<br>Using recommended clock<br>components as shown |

| sampling time                                                                            | 1                          | 2.5         |       |                  | μS                       | in <b>fig. 4</b> .<br>See internal clock<br>operation                            |

# Notes

<sup>1)</sup> Includes full scale error, offset error, integral and differential nonlinearity.

<sup>&</sup>lt;sup>2)</sup> Input signals with specified slew rates can be converted without external sample-and-hold. Input signals with higher slew rates may cause digital full scale errors. Filtering by a low pass ( $R = 2 \text{ k}\Omega$ , C = 100 nF) or use of an external sample-and-hold is required then.

# Characteristics (cont'd)

| Parameter                        | Symbol          | Limit Values |      |            | Unit     | Test Condition                                                               |

|----------------------------------|-----------------|--------------|------|------------|----------|------------------------------------------------------------------------------|

|                                  |                 | min.         | typ. | max.       |          |                                                                              |

| Functional Range                 |                 |              |      |            |          |                                                                              |

| Supply voltage                   | V <sub>DD</sub> |              | 5    |            | V<br>V   | ± 5 % for specified performance ± 5 % for specified performance              |

| Supply current                   | IDD<br>Icc      |              | 1.0  | 2.5<br>2.0 | mA<br>mA | Typ. 1 mA with $V_{DD} = 5 \text{ V}$ $V_{IN} = V_{IL} = \text{ or } V_{IH}$ |

| Power dissipation                | PD              |              | 10   | 25         | mW       | WR = RD = CS = BUSY<br>= HIGH                                                |

| Power dissipation (standby mode) | $P_{DSB}$       |              | 50   |            | μW       | WR = RD = CS = BUSY<br>= HIGH                                                |

# Characteristics (SDA 1812 D)

$V_{\text{DD}} = 5 \text{ V} \pm 5 \text{ %}, \ V_{\text{CC}} = 5 \text{ V} \pm 5 \text{ %}, \ V_{\text{REF}} \leq V_{\text{DD}} \geq V_{\text{CC}}, -V_{\text{REF}} = 0 \text{ V}, \ \text{DGND} = 0 \text{ V}, \ \text{AGND} = 0 \text{ V}$   $f_{\text{CLK}} = 2 \text{ MHz}, \ \text{all specifications} \ t_{\text{min}} \ \text{to} \ t_{\text{max}} \ \text{unless otherwise specified}.$

| Parameter | Symbol | l Limit Values |      | lues | Unit | Test Condition |

|-----------|--------|----------------|------|------|------|----------------|

|           |        | min.           | typ. | max. |      |                |

# **DC Accuracy**

| Resolution                    |     | 12 |       |       | Bits | No missing codes guaranteed |

|-------------------------------|-----|----|-------|-------|------|-----------------------------|

| Total unadjusted error 1)     | TUE | -  | ± 1/2 | ± 3/4 | LSB  | All channels, AIN0-AIN3     |

| Differential nonlinearity     | DNL |    | ± 1/4 | ± 1/2 | LSB  |                             |

| Full scale error (gain error) | GE  |    | ± 1/8 | ± 1/4 | LSB  | All channels, AIN0-AIN3     |

| Offset error                  | OFS | ĺ  | ± 1/8 | ± 1/4 | LSB  | All channels, AIN0-AIN3     |

| Offset error with             |     |    |       |       | 1    | with internal clock         |

| TH function                   |     |    | ± 1/2 | ± 1   | LSB  | generator or synchronizing  |

| Channel to channel            |     | İ  |       |       |      | TH to ext. CLK              |

| mismatch                      |     |    |       | ± 1/4 | LSB  |                             |

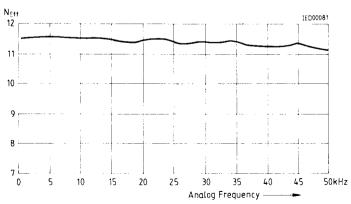

# Dynamic Performance<sup>2) 3)</sup>

| Signal to noise ratio            | SNR | 69 | 71 | dB  | Full scale input sinwave, 1 kHz f sampling is 100 kHz     |

|----------------------------------|-----|----|----|-----|-----------------------------------------------------------|

|                                  |     | 66 | 69 | dB  | Full scale input sinwave,<br>50 kHz f sampling is 100 kHz |

| Total harmonic distortion        | THD |    | 75 | dB  | Full scale input sinwave, 50 kHz f sampling is 100 kHz    |

| Full power bandwidth<br>(– 3 dB) | BW  |    | 4  | MHz | oo ki iz y odinpinig is 100 ki iz                         |

| Aperture delay time              |     |    | 5  | ns  | T/H pin                                                   |

# **Analog Inputs**

| Analog input range<br>Multiplexer | AIN       | $-V_{REF}$ |     | +VREF | ٧  | Selected and unselected channels AIN0-AIN3; |

|-----------------------------------|-----------|------------|-----|-------|----|---------------------------------------------|

| Settling time                     |           |            | 10  |       | ns |                                             |

| On channel input                  |           |            |     |       | _  |                                             |

| Capacitance                       | CAIN      |            | 50  |       | pF |                                             |

| ON-resistance                     | Ron       |            | 2   |       | kΩ |                                             |

| OFF-resistance                    | $R_{OFF}$ |            | 10  |       | МΩ |                                             |

| Input leakage current             | İ         |            |     |       |    |                                             |

| + 25 ℃                            | IAIN      |            |     | 10    | nΑ |                                             |

| $t_{\sf min}$ to $t_{\sf max}$    | IAIN      |            |     | 100   | nΑ |                                             |

| On-state bias current             |           |            | ± 5 |       | μА | Depends on analog input voltage             |

Notes see next page

# Characteristics (cont'd)

| Symbol Limit Values          |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                       | Test Condition                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                              | min. typ.                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|                              |                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| + VREF<br>- VREF             | 4.75<br>0                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ν<br>ν                                                                                                                                                                                                                                                                                | (For specified performance)<br>(For specified performance)<br>+ VBEF = 5.0 V                                                                                                                                                                                                                                           |  |  |  |  |

| THEF                         |                                                           | l                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | μΛ                                                                                                                                                                                                                                                                                    | T V HEF = 3.0 V                                                                                                                                                                                                                                                                                                        |  |  |  |  |