# CMOS 8-BIT MICROCONTROLLERS

# TMP90C844AN/TMP90C844AF

#### 1. **OUTLINE AND CHARACTERISTIC**

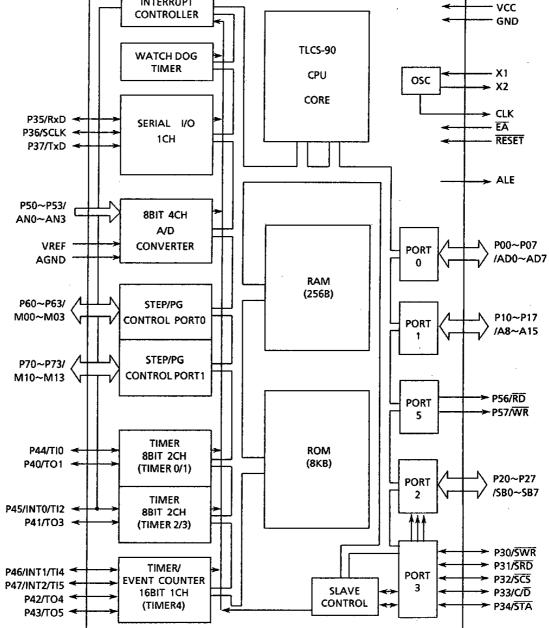

TMP90C844A is a high speed, high performance 8-bit microcontroller developed for application in the control of various devices.

TMP90C844A, CMOS 8-bit microcontroller, integrates an 8-bit CPU, ROM, RAM, A/D converter, multi-function timer/event counter, general-purpose serial interface and slave functions in a single chip, and with which external program memory and data memory can be extended up to 56KB.

TMP90C844AN is a device with a 64pin shrink DIP. TMP90C844AF is a device with a 64pin flat package. The following are the features of TMP90C844A.

- (1) Highly efficient instructions 163 types of basic instructions, including Multiplication, division, 16-bit arithmetic operations, bit manipulation instructions.

- (2) Minimum instruction executing time: 250 ns (at 16 MHz oscillation frequency)

- (3) Built-in ROM: 8KB

- (4) Built-in RAM: 256 bytes

- (5) Memory expansion External program memory 56 KBExternal data memory 56KB

- (6) Highly accurate 8-bit A/D converter (4 channels)

- (7) General-purpose serial interface (1 channel) With asynchronous mode and I/O interface mode

- (8) Multi-function 16-bit timer/event counter (1 channel)

- (9) 8-bit timer (4 channels)

- (10) Stepping motor control and pattern generation ports (2 channels)

- (11) Input/Output ports: 54 pins

- (12) Slave function

- (13) Interrupt function: 12 internal, 3 external

- 922 MM. Datasheethu.com (14) Micro Direct Memory Access (DMA) function (13 channels)

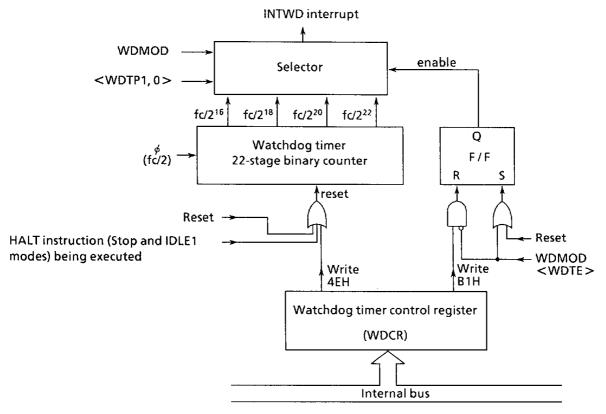

- (15) Watchdog timer function

- (16) Standby function (3 HALT modes)

MCU90-143

9097249 0041255

MCU90-144

**9**097249 0041256 869 **F**

# 2. PIN ASSIGNMENT AND FUNCTIONS

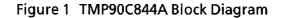

The assignment of input/output pins for TMP90C844A, their name and outline functions are described below.

### 2.1 Pin Assignment

Figure 2.1 (1) shows pin assignment of TMP90C844AN.

|                          | <u> </u> | 1          |    | 1     |            |

|--------------------------|----------|------------|----|-------|------------|

| VREF 🗖                   | 1        | $\bigcirc$ | 64 |       |            |

| AGND 🗔                   | 2        |            | 63 | 🗆 P47 | (INT2/TI5) |

| (AN0) P50 🖂              | 3        |            | 62 | 🗀 P46 | (INT1/TI4) |

| (AN1) P51 🗀              | 4        |            | 61 | 🗀 P45 | (INTO/Ti2) |

| (AN2) P52 🗖              | 5        |            | 60 | 🗖 P44 | (TIO)      |

| (AN3) P53 🗔              | 6        |            | 59 | 🗀 P43 | (TO5)      |

| (SWR) P30 🗆              | 7        |            | 58 | 🗖 P42 | (TO4)      |

| (SRD) P31 🖂              | 8        |            | 57 | 🗇 P41 | (TO3)      |

| ( <del>SCS</del> ) P32 🗖 | 9        |            | 56 | 🗀 P40 | (TO1)      |

| (C/D) P33 🗀              | 10       |            | 55 | 🗀 P73 | (M13)      |

| (STA) P34 🖂              | 11       |            | 54 | 🗆 P72 | (M12)      |

| (RxD) P35 🖂              | 12       | ۷          | 53 | 🖵 P71 | (M11)      |

| (SCLK) P36 🖂             | 13       | 4          | 52 | 🗀 P70 | (M10)      |

| (TxD) P37 🖂              | 14       | 4          | 51 | 🗀 P63 | (M03)      |

| (SBO) P20 🗆              | 15       | C 8        | 50 | 🗆 P62 | (M02)      |

| (SB1) P21 🖂              | 16       | õ          | 49 | 🗀 P61 | (M01)      |

| (SB2) P22 🖂              | 17       | ი          | 48 | 🗀 P60 | (M00)      |

| (SB3) P23 🖂              | 18       | 2          | 47 | RESET | :          |

| (SB4) P24 🚞              | 19       | ĭ⊾         | 46 | 🗆 P57 | (WR)       |

| (SB5) P25 🖂              | 20       |            | 45 | 🗆 P56 | (RD)       |

| (SB6) P26 🖂              | 21       |            | 44 | □ськ  |            |

| (SB7)/(WAIT) P27         | 22       |            | 43 | D P17 | (A15)      |

| (AD0) P00 🗀              | 23       |            | 42 | D P16 | (A14)      |

| (AD1) P01 🖂              | 24       |            | 41 | D P15 | (A13)      |

| (AD2) P02 🖂              | 25       |            | 40 | 🗆 P14 | (A12)      |

| (AD3) P03 🚞              | 26       |            | 39 | 🖵 P13 | (A11)      |

| (AD4) P04 🖂              | 27       |            | 38 | □ P12 | (A10)      |

| (AD5) P05 🖂              | 28       |            | 37 | D P11 | (A9)       |

| (AD6) P06 🖂              | 29       |            | 36 | □ P10 | (A8)       |

| (AD7) P07 🗀              | 30       |            | 35 |       |            |

|                          | 31       |            | 34 |       |            |

| GND 🗔                    | 32       |            | 33 | ⊐x1   |            |

|                          |          |            |    | }     |            |

Figure 2.1 (1) Pin Assignment (Shrink DIP)

Figure 2.1 (2) shows the pin assignment of TMP90C844AF.

MCU90-146

### 🛛 9097249 0041258 631 🎞

ſ

# 2.2 Pin Names and Functions

The names of input/output pins and their functions are summarized in Table 2.2.

Table 2.2 (1/3)

| Pin name | No. of pins | I/O or<br>tristate | Function                                                                                                                        |

|----------|-------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------|

| P00~P07  | 8           | I/O                | Port 0: An 8-bit I/O port. Each bit can be set for input or output.                                                             |

| /AD0~AD7 |             | /Tristate          | Address/data bus: Operates as an 8-bit bi-directional address bus or data bus when using external memory.                       |

| P10~P17  | 8           | 1/0                | Port 1: An 8-bit I/O port. Each bit can be set for input or output.                                                             |

| /A8~A15  |             | /Output            | Address bus: Operates as an address bus (upper 8 bits) when using external memory                                               |

| P20~P27  | 8           | I/O                | Port 2: An 8-bit I/O port. Each bit can be set for input or output.                                                             |

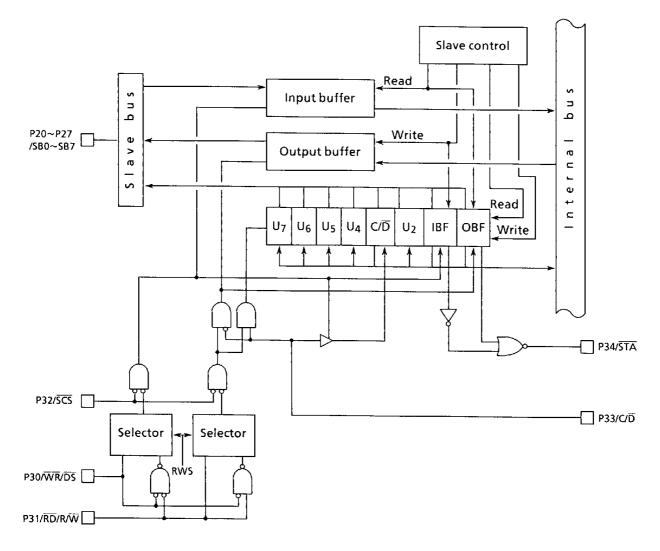

| /SB0~SB7 | (8)         |                    | Slave bus: When used as a slave processor, operates as the slave bus for the transfer of data to and from the master processor. |

| /WAIT    | (1)         | /Input             | Wait: Input pin for connecting a memory or peripheral LSI with delayed access time.                                             |

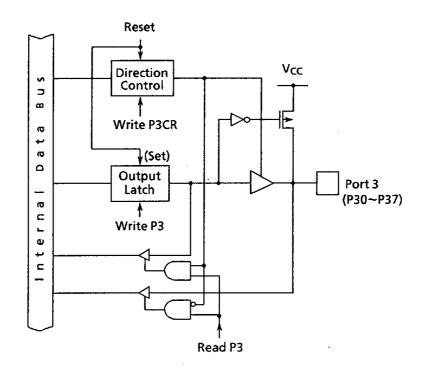

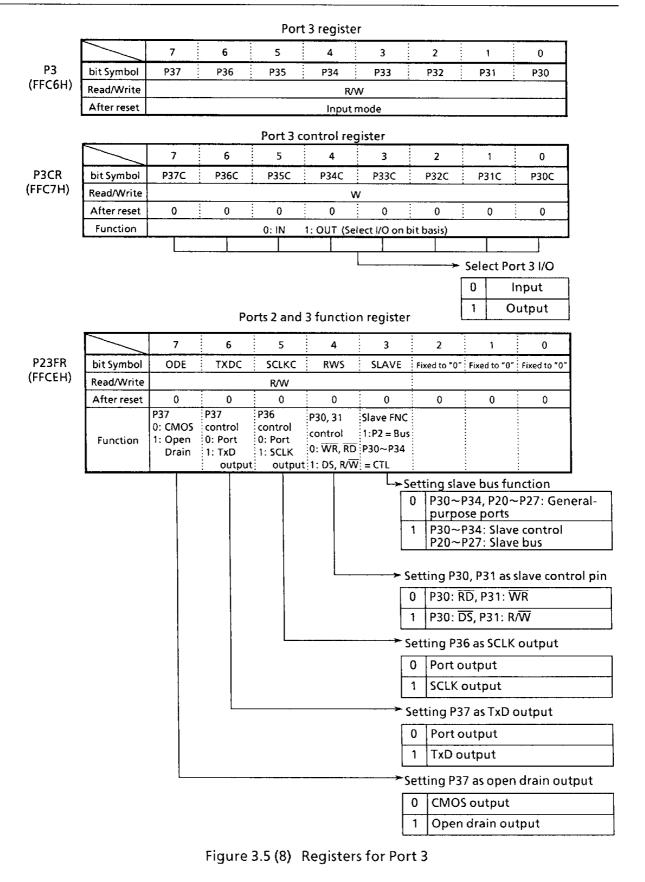

| P30~P37  | 8           | I/O                | Port 3: 8-bit I/O port which allows I/O selection on bit basis (with programmable pull-up resistor).                            |

| /SWR     | (1)         | /Input             | Slave write: The strobe signal input to write data from the master processor.                                                   |

| /SRD     | (1)         | /Input             | Slave read: The strobe signal used by the master processor to read data.                                                        |

| /SCS     | (1)         | /Input             | Slave chip select: The chip select signal input from the master processor.                                                      |

| C/D      | (1)         | Input              | Command/data: The command/data select signal input from the master processor.                                                   |

| /STA     | (1)         | /Output            | Status output: Used to report the slave bus status to the master processor.                                                     |

| RxD      | (1)         | Input              | Receiver of serial data                                                                                                         |

| /SCLK    | (1)         | /I/O               | Serial clock                                                                                                                    |

| /TxD     | (1)         | /Output            | Transmitter of serial data                                                                                                      |

MCU90-147

# TOSHIBA

Table 2.2 (2/3)

| No. of pins | I/O or<br>tristate                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

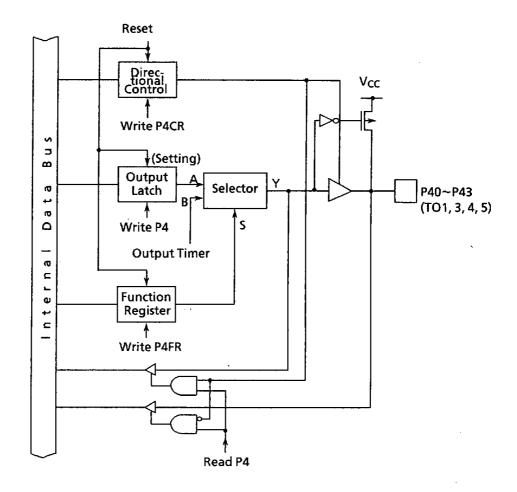

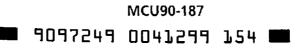

| 8           | I/O                                                                                    | Port 4: 8-bit I/O port which allows I/O selection on bit basis (with programmable pull-up resistor).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| (4)         | /Output                                                                                | Timer outputs 1, 3, 4, and 5: Output ports for timer 0, or timer 1,<br>timer 2, timer 3 and timer 4 (2 lines).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

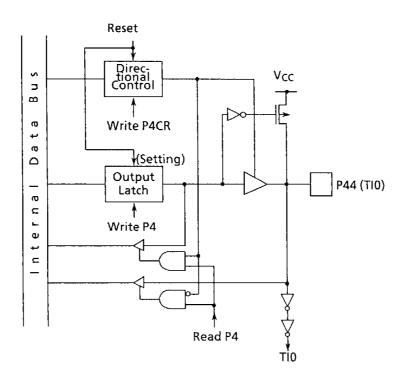

| (4)         | /Input                                                                                 | Timer inputs 0, 2, 4, and 5: Input ports for timer 0, or timer 1,<br>timer 2 and timer 4 (2 lines).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (1)         | /Input                                                                                 | Interrupt request terminal 0: Interrupt request pin 0: Level/rise<br>edge programmable interrupt<br>request pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | -                                                                                      | Interrupt request terminal 1: Interrupt request pin 1: Rise/fall edge<br>programmable interrupt request pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| (17         | mput                                                                                   | Interrupt request terminal 2: Interrupt request pin 2: Rise edge<br>interrupt request pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

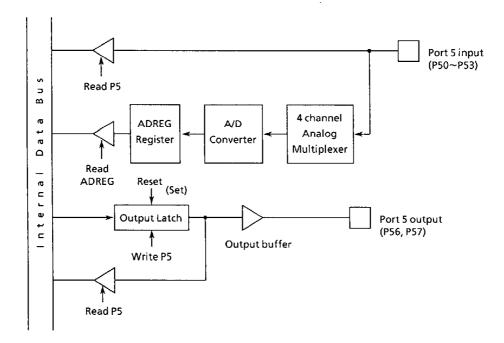

| 4           | Input                                                                                  | Ports 50 ~ 53: 1-bit output ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|             |                                                                                        | Analog input: 4 analog inputs to A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1           | Output                                                                                 | Port 56: A 1-bit output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                                                        | Read: Strobe signal output for reading external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1           | Output                                                                                 | Port 57: A 1-bit output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                                                                        | Write: Strobe signal output for writing external memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

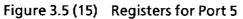

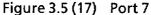

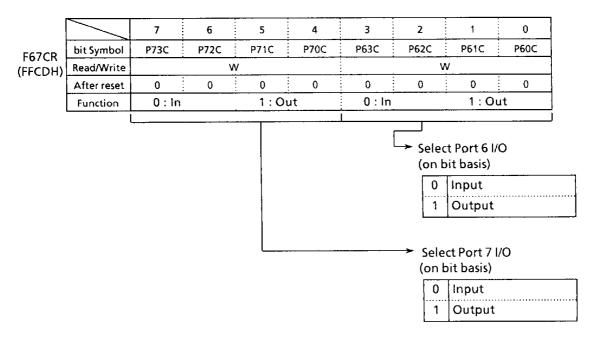

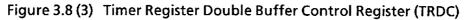

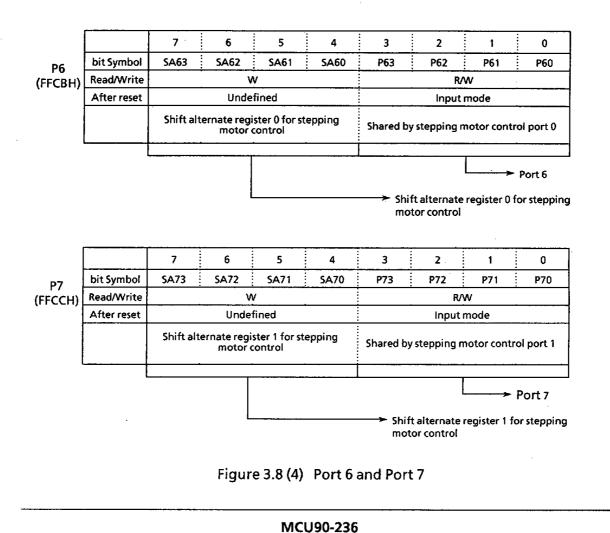

| 4           | I/O                                                                                    | Port 6: 4-bit I/O port which allows I/O selection on bit basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | /Output                                                                                | Stepping motor control port 0 or pattern generation port 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

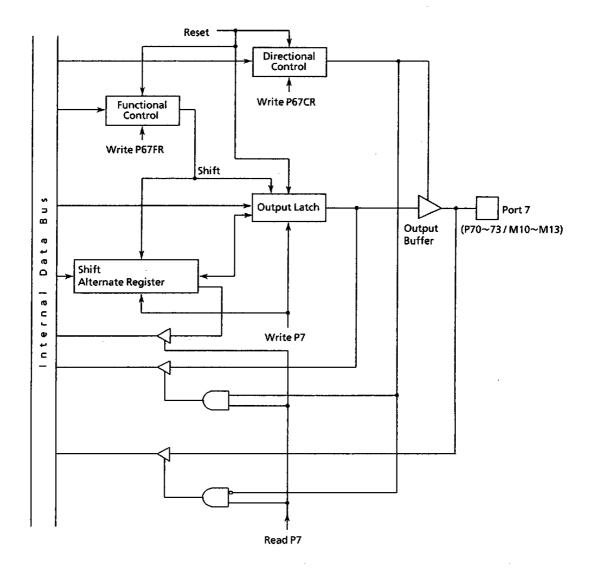

| 4           | 1/0                                                                                    | Port 7: 4-bit I/O port which allows I/O selection on bit basis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | /Output                                                                                | Stepping motor control port 0 or pattern generation port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1           | Output                                                                                 | Address latch enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1           | Output                                                                                 | Clock output: Generates clock pulse at 1/4 frequency of clock oscillation. It is pulled up during resetting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1           | Input                                                                                  | External access: Connects to the Vcc pin when the TMP90C844 built<br>ROM is used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | 8<br>(4)<br>(1)<br>(1)<br>(1)<br>(1)<br>4<br>1<br>1<br>4<br>4<br>4<br>4<br>1<br>1<br>1 | No. of pins         tristate           8         I/O           (4)         /Output           (4)         /Input           (1)         /Input           1         Output           1         Output           4         I/O           /Output         /Output           4         I/O           1         Output           1         Output           1         Output           1         Output           1         Output           1         Output |

MCU90-148 9097249 0041260 29T 🖿

| Pin name | No. of pins | l/O or<br>tristate | Function                                                       |

|----------|-------------|--------------------|----------------------------------------------------------------|

| RESET    | 1           | Input              | Reset: Initializes TMP90C844 (pull-up resistance is built-in). |

| X1, X2   | 2           | 1/0                | Crystal oscillator connection pin                              |

| VREF     | 1           |                    | Input of reference voltage to A/D converter                    |

| AGND     | 1           |                    | GND pin for A/D converter                                      |

| Vcc      | 1           |                    | Power supply pin ( + 5V +/- 10%)                               |

| GND      | 1           |                    | GND pin (0V)                                                   |

Table 2.2 (3/3)

### 3. OPERATION

This section explains the functions and basic operations of the TMP90C844 in blocks.

#### 3.1 CPU

TMP90C844 has a built-in, high performance 8-bit CPU.

For the operation of the CPU, see "TLCS-90 CPU" described in the previous section. This section explains the CPU functions unique to the TMP90C844 that are not explained in "TLCS-90 CPU".

#### 3.1.1 Reset

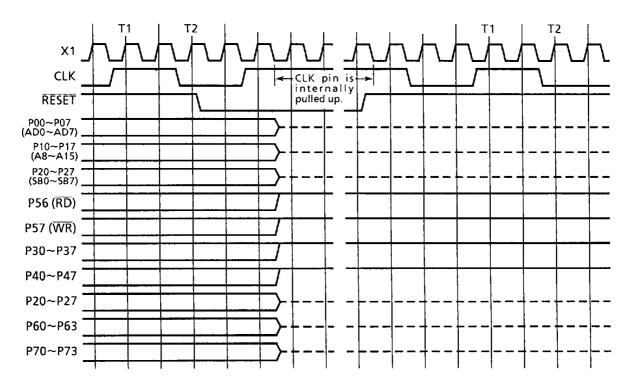

Figure 3.1 (1) shows the basic timing of reset.

To reset TMP90C844, it is required that the power supply voltage is within operating range, the internal oscillator is stably functioning, and  $\overline{\text{RESET}}$  input be kept at "0" at least 10 system clocks (10 states: 2 microseconds with 10 MHz system clock).

When reset is accepted, among I/O common ports, port 0 (address data bus AD0~AD7), port 1 (address bus A8~A15) and port 2 are set to input status (with high impedance). Output ports P56 (RD) and P57 (WR) and CLK are set to "1" and ALE is cleared to "0".

CPU registers and external memory are not changed. However, program counter PC and interrupt enable/disable flag IFF are cleared to "0". The A register becomes undefined.

When the reset is released, instruction execution starts from address 0000H.

9097249 0041262 062 |

Figure 3.1 (1) Reset Timing of TMP90C844

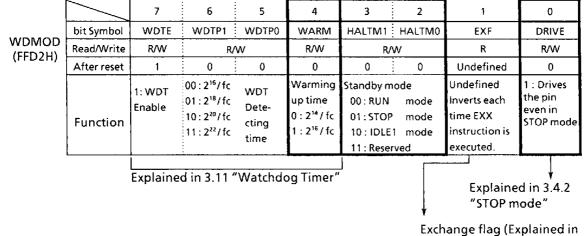

### 3.1.2 EXF (Exchange flag)

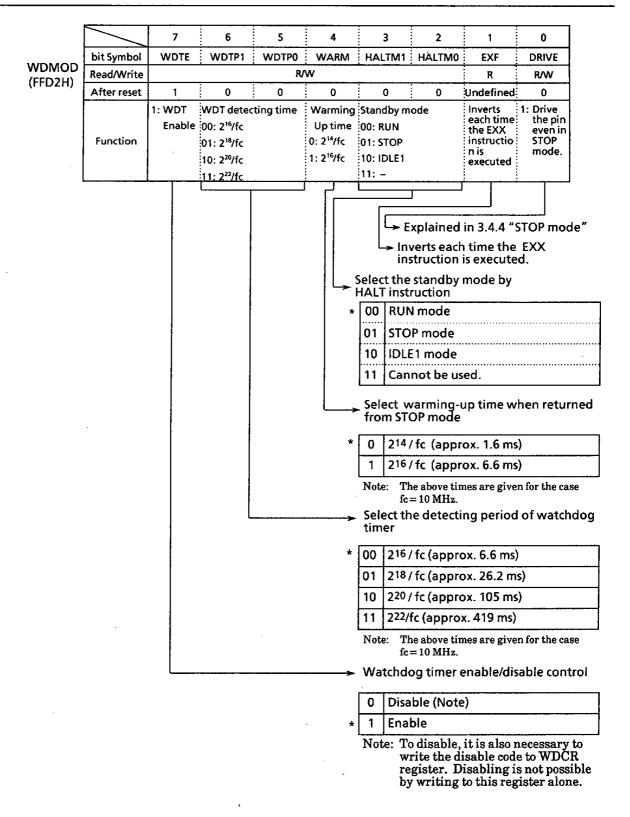

The exchange flag EXF is inverted when the EXX instruction is executed to exchange data between the TMP90C844 main registers and auxiliary registers. This flag is assigned to bit 1 at memory address FFD2H.

|         |             | 7                | 6                       | 5              | 4                                                                      | 3              | 2                   | 1                                                                  | 0                                                   |

|---------|-------------|------------------|-------------------------|----------------|------------------------------------------------------------------------|----------------|---------------------|--------------------------------------------------------------------|-----------------------------------------------------|

|         | bit Symbol  | WDTE             | WDTP1                   | WDTP0          | WARM                                                                   | HALTM1         | HALTM0              | EXF                                                                | DRIVE                                               |

|         | Read/Write  |                  |                         | R/             | w                                                                      |                |                     | R                                                                  | R/W                                                 |

| (FFD2H) | After reset | 1                | 0                       | 0              | 0                                                                      | 0              | 0                   | Un-defined                                                         | 0                                                   |

|         | Function    | 1: WDT<br>Enable | 00: 2<br>01: 2<br>10: 2 | 16/fc<br>18/fc | Warming<br>up time<br>0: 2 <sup>14</sup> /fc<br>1: 2 <sup>16</sup> /fc | 00: F<br>01: S | RUN<br>ITOP<br>DEL1 | Inverts<br>each time<br>the EXX<br>instructio<br>n is<br>executed. | 1: Drives<br>the pin<br>even in<br>the STOP<br>mode |

### 3.1.3 Wait Control

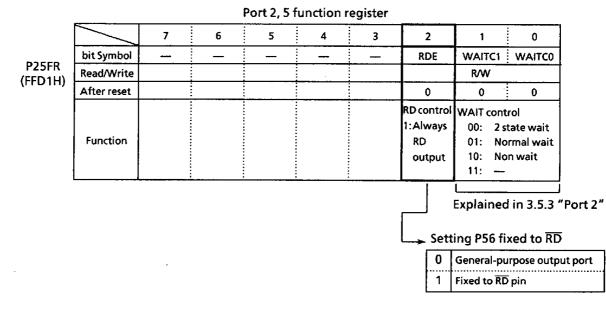

For the TMP90C844, wait control register (WAITC) is assigned to bits 0 and 1 at memory address FFD1H.

|                  | $\square$   | 7 | 6 | 5 | 4 | 3 | 2                                       | 1        | 0                    |

|------------------|-------------|---|---|---|---|---|-----------------------------------------|----------|----------------------|

| 00550            | bit Symbol  | - | - | - |   | - | RDE                                     | WAITC1   | WAITCO               |

| P25FR<br>(FFD1H) | Read/Write  |   |   |   |   |   | R/W                                     | R/       | w                    |

| (ITDTII)         | After reset |   |   |   |   |   | 0                                       | 0        | 0                    |

|                  | Function    |   |   |   |   |   | RD control<br>1: Always<br>RD<br>output | 00: 2 st | ate wait<br>mal Wait |

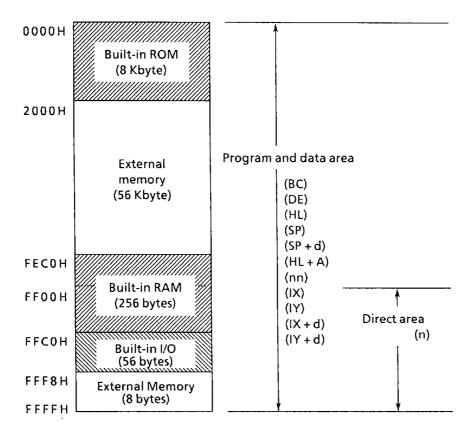

#### 3.2 Memory Map

The TMP90C844 can provide a maximum 64Kbyte program and data memory. The program and data memories may be allocated to the addresses 0000H~FFFFH.

(1) Built-in ROM

TMP90C844 has an internal 8-byte ROM. This ROM is located at addresses 0000H~1FFFH. Program execution starts from address 0000H after a reset operation. Addresses 0008H~0078H in the internal ROM area are used as the interrupt processing entry area.

(2) Built-in RAM

TMP90C844 contains a 256-byte built-in RAM which is allocated to the addresses FEC0H~FFBFH. The CPU can also access some portions of the RAM (192 byte area FF00H~FFBFH) using short instruction codes in the direct addressing mode.

Addresses of FF18H~FF78H this RAM area are used as the parameter area for micro DMA processing. (This area can freely be used when micro DMA function is not used.)

(3) Built-in I/O

TMP90C844 uses 56 bytes of the address space as a built-in I/O area. The area is allocated to the addresses FFC0H $\sim$ FFF7H. The CPU can access the built-in I/O using short instruction codes in the direct addressing mode.

Figure 3.2 shows the memory map and the access ranges of the CPU for each addressing mode.

### TOSHIBA

#### 3.3 Interrupt Functions

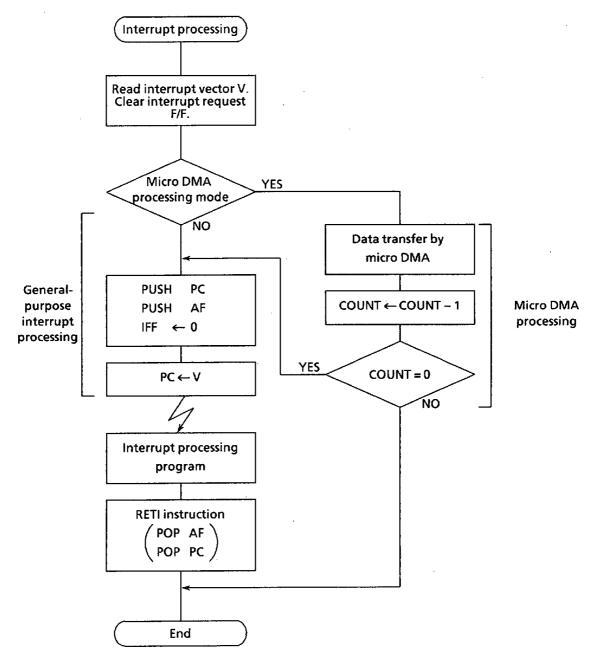

TMP90C844 provides the two processing modes for internal and external interrupt requests; a general-purpose interrupt processing mode and a micro DMA processing mode in which the CPU can automatically transfer data.

Immediately after a reset is released, all the responses to interrupt requests are set in the general-purpose interrupt processing mode. Using DMA enable/disable register which will be described later, each interrupt request can be set to the micro DMA processing mode.

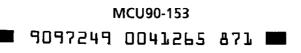

Figure 3.3 (1) shows a flowchart of the interrupt response sequence.

310189

Figure 3.3 (1) Interrupt Response Flowchart

When an interrupt request is generated, it is reported to the CPU via the built-in interrupt controller. The CPU starts the interrupt processing if it is a non-maskable or maskable interrupt requested in the EI state (interrupt enable/disable flag (IFF bit of the F register)="1").

However, a maskable interrupt in the DI state (IFF = "0") is ignored and not accepted. (The CPU samples interrupt requests at the fall edge of CLK signal of the last bus cycle of each instruction.)

When an interrupt is accepted, the CPU first reads the interrupt vector from the built-in interrupt controller to find out the source of the interrupt request.

Then, the CPU checks if the request should be processed in the general-purpose interrupt processing mode or micro DMA processing mode, and proceeds to the appropriate process.

The interrupt vector is read in an internal operation cycle, so the bus cycle results in dummy cycles.

### 3.3.1 General purpose Interrupt Processing

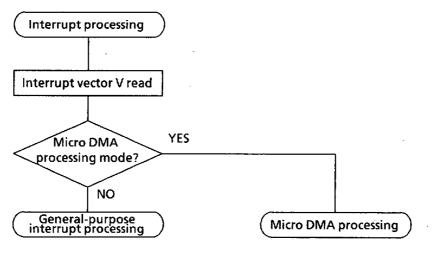

Figure 3.3 (2) shows the flow of general-purpose interrupt processing.

The CPU first saves the contents of program counter PC and register AF (including the interrupt enable/disable flag just before the interrupt is issued) into the stack and resets the interrupt enable/disable flag IFF to "0" (interrupt disable). Finally, it transfers the contents "V" of interrupt vector to the program counter and jumps to the interrupt processing program.

The overhead for the entire process from accepting an interrupt to jumping to an interrupt processing program is 20 states.

Figure 3.3 (2) General Purpose Interrupt Processing

The interrupt processing program ends with RETI instruction for both non-maskable and maskable interrupts.

When this instruction is executed, the contents of the program counter PC and register AF will be restored from the stack (returns to the interrupt enable/disable flag just before the interrupt was issued).

When the CPU reads an interrupt vector, the interrupt request source acknowledges that the CPT accepts the request, and then clears the request.

Non-maskable interrupts cannot be disabled by program. Maskable interrupts, however, can be enabled or disabled by programming. An interrupt enable/disable flip-flop (IFF) is provided on the bit 5 of the F register in the CPU.

Interrupts are enabled by setting IFF to "1" with the EI instruction and disabled by resetting IFF to "0" with the DI instruction. IFF is reset to "0" by reset operation or the acceptance of any interrupt (including non-maskable interrupts).

Interrupts enabled with the EI instruction become effective when the instruction after the EI is executed.

Table 3.3 (1) shows the interrupt sources.

| Priority<br>order | Туре     | Interrupt source                | Vector<br>value/8 | Vector<br>value | Start address<br>of general-<br>purpose<br>interrupt<br>processing | Start address<br>of micro<br>DMA<br>processing<br>parameter |

|-------------------|----------|---------------------------------|-------------------|-----------------|--------------------------------------------------------------------|-------------------------------------------------------------|

| 1                 | Non-     | SWI instruction                 |                   | 08H             | 0008H                                                              |                                                             |

| 2                 | maskable | INTWD (watchdog)                |                   | 10H             | 0010H                                                              |                                                             |

| 3                 |          | INTO (External input 0)         | 03Н               | 18H             | 0018H                                                              | FF18H                                                       |

| 4                 |          | INTTO (Timer 0)                 | 04H               | 20H             | 0020H                                                              | FF20H                                                       |

| 5                 |          | INTT1 (Timer 1)                 | 05H               | 28H             | 0028H                                                              | FF28H                                                       |

| 6                 |          | INTT2 (Timer 2)                 | 06H               | 30H             | 0030H                                                              | FF30H                                                       |

| 6                 |          | INTAD (A/D conversion end)      | 06H               | 30Н             | 0030Н                                                              | FF30H                                                       |

| 7                 | Maskable | INTT3 (Timer 3)                 | 07H               | 38H             | 0038H                                                              | FF38H                                                       |

| 8                 |          | INTT4 (Timer 4)                 | 08H               | 40H             | 0040н                                                              | FF40H                                                       |

| 9                 |          | INT1 (External input 1)         | 09H               | 48H             | 0048H                                                              | FF48H                                                       |

| 10                |          | INTT5 (Timer 5)                 | 0AH               | 50H             | 0050H                                                              | FF50H                                                       |

| 11                |          | INT2 (External input 2)         | ОВН               | 58H             | 0058H                                                              | FF58H                                                       |

| 12                |          | INTRX (Serial receiving end)    | осн               | 60H             | 0060H                                                              | FF60H                                                       |

| 13                |          | INTTX (Serial transmission end) | 0DH               | 68H             | 0068H                                                              | FF68H                                                       |

| 14                |          | INTFL (Slave buffer full)       | 0EH               | 70H             | 0070H                                                              | FF70H                                                       |

| 15                | -        | INTEP (Slave buffer empty)      | OFH               | 78H             | 0078H                                                              | FF78H                                                       |

Table 3.3 (1) Interrupt Sources

Note: Either INTT2 or INTAD interrupt is selected by the A/D interrupt selection register INTEH<ADIS>.

The "priority order" in the table 3.3 (1) indicates the order of the interrupt sources to be acknowledged by the CPU when two or more interrupts are requested at one time.

If interrupt requests of 4th and 5th orders are generated at the same time, for example, an interrupt of the "5th" priority is acknowledged after the "4th" priority interrupt processing has been completed by a RETI instruction. However, the "5th" priority interrupt can be acknowledged immediately by executing an EI instruction in a program that processes the "4th" priority interrupt.

The built-in interrupt controller only determines the priority of interrupt sources which are to be accepted by the CPU when two or more interrupts are requested at a time.

It is, therefore, unable to compare the priority of interrupt being executed with the one being requested.

To enable other interrupt while an interrupt is being processed, set an interrupt enable/disable flag for the interrupt source to be enabled and execute EI instruction.

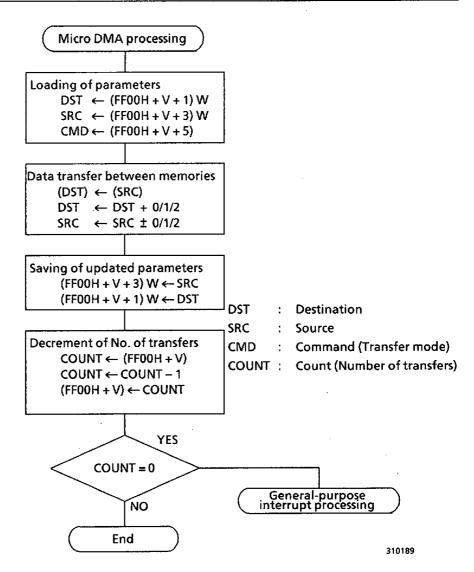

### 3.3.2 Micro DMA Processing

Figure 3.3 (3) shows the flowchart of micro DMA processing. The CPU first loads parameters (addresses of source and destination, and transfer mode) necessary for the data transfer between memories from an address modified by an interrupt vector value. After the data transfer between the memories according to these parameters, the parameters are updated and saved into the original locations. The CPU then decrements the number of transfers, and completes the micro DMA processing unless the result is "0". If the number of transfers become "0", the CPU proceeds to the generalpurpose interrupt handling described in the previous section.

Figure 3.3 (3) Micro DMA Processing Flowchart

Since most interrupt processing involves only simple data transfers, the micro DMA processing executes such processing only by hardware. Accordingly, the micro DMA processing can handle the interrupt in a higher speed than the conventional processing using software. Naturally, the CPU registers are not affected by the micro DMA processing.

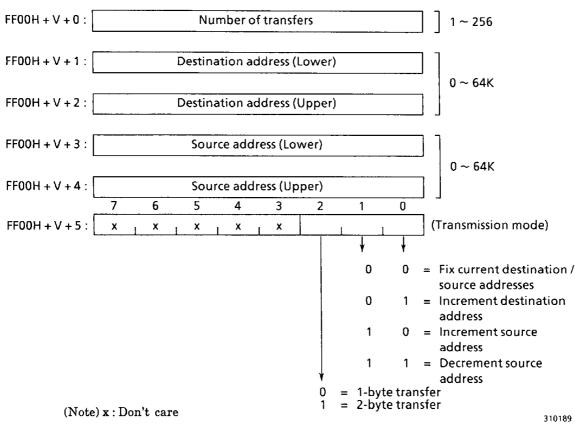

Figure 3.3 (4) shows the functions of the parameters used in the micro DMA processing.

Parameters for micro DMA processing are located in the internal RAM area (see Table 3.3 (1) Interrupt Sources). The start address of each parameter for micro DMA processing becomes "FF00H+interrupt vector value", 6 bytes of which are used as the parameter. When micro DMA processing mode is not used, the area can be freely used as user memory.

The parameters consist of the number of transfers, destination address, source address, and transfer mode. The number of transfers specifies the number of data transfers accepted by micro DMA processing. A single time micro DMA processing transfers 1-byte or 2-byte data. The number of transfers is 256 when the number of transfers value is "00H". Both the destination and source addresses are specified by 2-byte data. The address space available for the micro DMA processing ranges 0000H~FFFFH.

Bits 0 and 1 of the transfer mode indicate the mode updating the source and/or destination, and the bit 2 indicates the data length (one byte or two bytes).

Table 3.3 (2) shows the relation between transfer modes and the incremented or decremented values of the destination/source addresses.

| Transfer<br>mode |                  | Function                                         | Destination<br>address | Source<br>address |

|------------------|------------------|--------------------------------------------------|------------------------|-------------------|

| 000              | 1-byte transfer: | Fix the current destination/<br>source addresses | 0                      | 0                 |

| 001              | 1-byte transfer: | Increment the destination address                | +1                     | 0                 |

| 010              | 1-byte transfer: | Increment the source address                     | 0                      | + 1               |

| 011              | 2-byte transfer: | Decrement the source address                     | o                      | - 1               |

| 100              | 2-byte transfer: | Fix the current<br>destination/source addresses  | o                      | 0                 |

| 101              | 2-byte transfer: | Increment the destination address                | + 2                    | 0                 |

| 110              | 2-byte transfer: | Increment the source address                     | 0                      | + 2               |

| 111              | 2-byte transfer: | Decrement the source address                     | 0                      | - 2               |

Table 3.3 (2) Addresses Updated by Micro DMA Processing

021290

In the 2-byte transfer mode, data are transferred as follows:

$(Destination address) \leftarrow (Source address)$  $(Destination address + 1) \leftarrow (Source address + 1)$

Similar data transfers are made in the modes that "decrement the source address" and addresses are updated as shown in the table 3.3 (2).

Address updating in micro DMA processing is designed considering the I/O transfer from/to memory. Therefore, at least either destination or source address is fixed.

Figure 3.3 (5) shows an example of the micro DMA processing that handles data receiving of internal serial I/O.

This is an example of executing "an interrupt processing program after serial data receiving" after receiving 7-frame data (Assume 1 frame = 1 byte for this example) and saving them into the memory addresses  $FF00H \sim FF06H$ .

```

CALL

SIOINIT

Initial setting for serial receiving.

SET

3,(0FFF4H)

Enable an interrupt for serial data receiving.

SET

3,(0FFF6H)

Set the micro DMA processing mode for serial receiving

interrupt.

LD

(OFF60H),7

Set the number of transfers = 7.

LDW

(OFF61H), OFF00H

Set FF00H for the destination start address.

LDW

(OFF63H), OFFE8H

Set FFEBH for the source (serial receiving buffer) address.

;

LD

(OFF65H),1

Set the transfer mode (1-byte transfer; increment

1

destination address).

ΕI

:

:

ORG

0060H

Interrupt processing program after serial data receiving

```

RETI

060890

Figure 3.3 (5) Example of Micro DMA Processing

For the bus operation in the general-purpose interrupt processing and micro DMA processing, see "Table 1.4 (2) Bus Operation for Executing Instructions" in the previous section "TLCS-90 CPU".

Execution time for micro DMA processing (when decremented number of transfers is not zero) is 46 states (5.75  $\mu$ s at 16 MHz oscillation), regardless of whether 1-byte or 2-byte transfer mode is used.

Figure 3.3 (6) shows the flowchart of overall interrupt processing.

310189

#### 3.3.3 Interrupt Controller

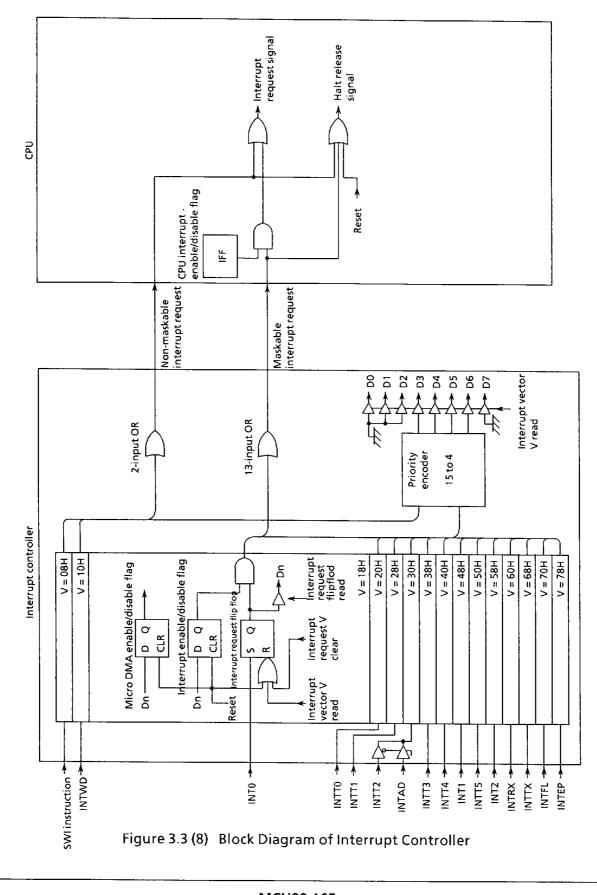

Figure 3.3 (8) shows the block diagram of interrupt circuit. The left half of this diagram shows the interrupt controller, and the right half includes the CPU's interrupt request signal circuit and the HALT release signal circuit.

The interrupt controller has an interrupt request flip-flop, interrupt enable/disable flag, and micro DMA enable/disable flag for each interrupt channel (total; 15 channels). The interrupt request flip-flop latches an interrupt request when it is issued from the peripheral devices. This flip-flop is reset to "0" when reset operation or interrupt is accepted by the CPU and the vector of that interrupt channel is read by the CPU, or when the CPU executes an instruction that clears the interrupt request for the specified channel (write "vector divided by 8" into the memory address FFEAH). For example, when executing

#### LD (0FFEAH), 38H/8

the interrupt request flip-flop of interrupt channel "INTT3" whose vector value is 38H will be reset to "0". (Write to FFEAH even when clearing the interrupt request flag that is assigned to FFEBH.)

The status of an interrupt request flip-flop can be known by reading the memory address FFEAH or FFEBH. "0" denotes there is no interrupt request, and "1" denotes that an interrupt is requested. Figure 3.3 (7) shows the bit configuration of the interrupt request flip-flops.

MCU90-163 9097249 0041275 710 |

# TOSHIBA

|         | $\square$   | 7                                       | 6                                                                                                | 5             | 4                                                           | 3     | 2     | 1                                               |       |  |  |

|---------|-------------|-----------------------------------------|--------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------|-------|-------|-------------------------------------------------|-------|--|--|

|         | bit Symbol  | -                                       |                                                                                                  |               |                                                             |       |       |                                                 | 0     |  |  |

| IRFL    | Read/Write  |                                         | IRFT4 IRF1 IRFT5 IRF2 IRFRX IRFTX IRFFUL IRFEM<br>R (Write is possible only for IRF clear code.) |               |                                                             |       |       |                                                 |       |  |  |

| (FFEAH) | After reset | 0                                       |                                                                                                  |               |                                                             |       |       |                                                 |       |  |  |

|         | Function    | -                                       |                                                                                                  | urrently requ |                                                             |       | •     | • -                                             | •     |  |  |

|         |             |                                         |                                                                                                  |               |                                                             |       |       | → INTFI<br>→ INTT<br>→ INTR<br>→ INT2<br>→ INT1 | •     |  |  |

|         | $\square$   | 7                                       | 6                                                                                                | 5             | 4                                                           | 3     | 2     | 1                                               | 0     |  |  |

|         | bit Symbol  | EXT                                     |                                                                                                  |               | IRFO                                                        | IRFTO | IRFT1 | IRFT2                                           | IRFT3 |  |  |

| IRFH    | Read/Write  | w                                       |                                                                                                  |               |                                                             |       | R     | ····-                                           |       |  |  |

| FEBH)   | After reset | 0                                       |                                                                                                  |               | 0                                                           | 0     | 0     | 0                                               | 0     |  |  |

|         | Function    | P1 control<br>0: I/O port<br>1: Address |                                                                                                  |               | Interrupt Request Flag 1: Interrupt is currently requested. |       |       |                                                 |       |  |  |

|         |             | Explaine<br>3.5.2 "Po                   |                                                                                                  |               |                                                             |       |       | ]<br>→ INTT:<br>→ INTT2                         |       |  |  |

Note: When "vector value/8" is written in memory address FFEAH, the specified interrupt request flag will be cleared.

Figure 3.3 (7) Interrupt Request Flip-flops

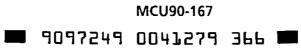

The interrupt enable/disable flags provided for all interrupt request channels are assigned to the memory address FFF4H or FFF5H. Interrupts for a channel are enabled by setting the flag to "1". The flags are cleared to "0" by resetting.

Clear the interrupt enable flag in the DI status.

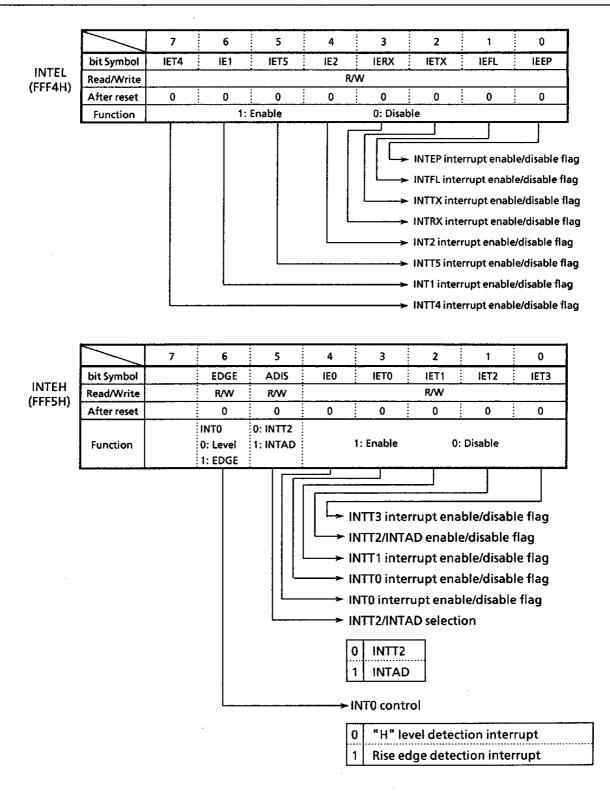

The micro DMA enable/disable flag also provided for each interrupt request channel is assigned to the memory address FFF6H or FFF7H. The interrupt processing for each channel is placed in the micro DMA processing mode by setting this flag to "1". This flag is cleared to "0" (general-purpose interrupt processing mode) by resetting.

Figure 3.3 (9) shows the bit configurations for interrupt enable/disable flag and micro DMA enable/disable flag.

Interrupt by timer 2 (INTT2) and that by A/D converter (INTAD) use a common interrupt request channel. Immediately after resetting, INTT2 is input in the interrupt controller. To use INTAD, set "INTT2/INTAD selection bit" (ADIS: bit 5 of memory address FFF5H) to "1".

| Interrupt | Common<br>pin | Mode         | Setting                                          |

|-----------|---------------|--------------|--------------------------------------------------|

|           | 545           | Level        | INTEH < EDGE > = 0                               |

| INTO      | P45           | Rise edge    | INTEH < EDGE > = 1                               |

|           | D.C.          | Rise edge    | T4MOD <capm1, 0=""> = 0,0 or 0,1 or 1,1</capm1,> |

| INT1      | P46           | Fall edge    | T4MOD <capm1,0> = 1,0</capm1,0>                  |

| INT2      | P47           | _f Rise edge |                                                  |

External interrupt features are as follows.

For the pulse width for external interrupt, refer to "4.7 Interrupt Operation".

Be careful that the following five are exceptional circuits.

| INT0 level mode | As the INTO is not edge type interrupt, the interrupt request<br>flip-flop function is canceled, and thus an interrupt request<br>from peripheral devices passes through S input of the flip-flop<br>to become Q output. When the mode is changed over (from<br>edge type to level type), the previous interrupt request flag<br>will be cleared automatically.<br>When the mode is changed from level to edge, the interrupt<br>request flag set in the level mode is not cleared. Thus, use the<br>following sequence to clear the interrupt request flag. |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | DI<br>SET 6, (0FFF5H) : Switch the mode from level to<br>edge<br>LD (0FFEAH), 03H : Clear interrupt request flag<br>EI                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| INTAD           | The interrupt request flip-flop can be cleared only by reset<br>operation or reading the register that stores the A/D<br>conversion value, and cannot be cleared by instruction. When<br>the interrupt source is changed (from INTAD to INTT2), the<br>previous interrupt request flag is cleared automatically.                                                                                                                                                                                                                                             |

| INTRX           | The interrupt request flip-flop is cleared only by reset<br>operation or reading the serial channel receiving buffer, and<br>cannot be cleared by an instruction.                                                                                                                                                                                                                                                                                                                                                                                            |

| INTFL           | The interrupt request flip-flop is cleared only by reset<br>operation or reading the slave bus input data buffer, and<br>cannot be cleared by an instruction.                                                                                                                                                                                                                                                                                                                                                                                                |

| INTEP           | The interrupt request flip-flop is cleared only by reset<br>operation or writing the slave bus output data buffer, and<br>cannot be cleared by an instruction.                                                                                                                                                                                                                                                                                                                                                                                               |

Figure 3.3 (9) Interrupt Enable/Disable Flags

MCU90-168 9097249 004ኌ280 088 ∎

# TOSHIBA

Figure 3.3 (10) Micro DMA Enable/Disable Flag

INTO DMA enable/disable flag

#### 3.4 Standby Function

When a HALT instruction is executed, TMP90C844 enters the RUN, IDLE1, or STOP mode according to the contents of the halt mode setting register. The features are as follows:

- (1) RUN : Only the CPU halts, and the power consumption remains unchanged.

- (2) IDLE1 : Only the internal oscillator operates, while all other internal circuits halt. Power consumption is 1/10 or less than that during normal operation.

- (3) STOP : All internal circuits halt, including the internal oscillator. Power consumption is extremely reduced.

The HALT mode setting register WDMOD<HALTM1,0> is assigned to bits 2 and 3 of memory address FFD2H in the built-in I/O register area (all other bits are used to control other block functions). The RUN mode ("00") is entered by resetting.

These HALT states can be released by requesting an interrupt or resetting. Table 3.4 (2) shows how to release the HALT state. If the CPU is in the EI state for non-maskable or maskable interrupt, the interrupt will be acknowledged by the CPU and the CPU starts interrupt processing. If the CPU is in the DI state for maskable interrupt, the CPU restarts execution from the instruction following HALT instruction, but the interrupt request flag remains at "1".

But if interrupt request occur before MPU practices "HALT" command in the state of DI and it latches interrupt request flag, it causes to release HALT state and to state will be released as soon after MPU practices "HALT" command. (MPU doesn't HALT state.)

Therefore clear interrupt request flag or disable interrupt enable flag before MPU practices "HALT" command.

ex) MPU becomes STOP mode in the state of DI and refease it by INT0 interrupt. (But "built-in I/O" uses only "Timer 0")

DI SET 4, (INTEH) RES 3, (INTEH) LD (WDMOD), 04H HALT

INTO interrupt enable INTTO interrupt disable STOP mode

After release "HALT" , Practice Program

Even when HALT state is released by reset operation, the state (including the builtin RAM) just before entering the HALT state can be retained. However, if HALT instruction has already been executed in the built-in RAM, the RAM contents may not be retained.

MCU90-170

9097249 0041282 950 🎟

Exchange flag (Explained in 3.1.2 "Register")

**1** 9097249 0041283 897 **1**

#### 3.4.1 RUN Mode

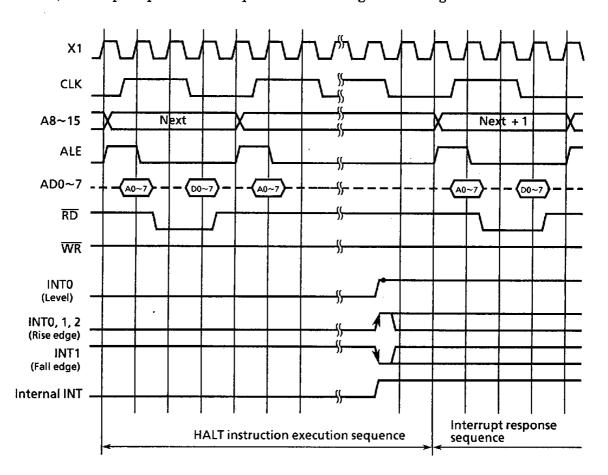

Figure 3.4 (2) shows the timing for releasing the HALT state by an interrupt during RUN mode. In the RUN mode, the system clock inside MCU does not stop even after HALT instruction has been executed; the CPU merely stops executing instructions. Accordingly, the CPU repeats dummy cycle until HALT state is released. In the HALT state, interrupt requests are sampled at the fall edge of CLK signal.

Figure 3.4 (2) HALT Release Timing Using Interrupts in RUN mode

# TOSHIBA

### 3.4.2 IDLE1 Mode

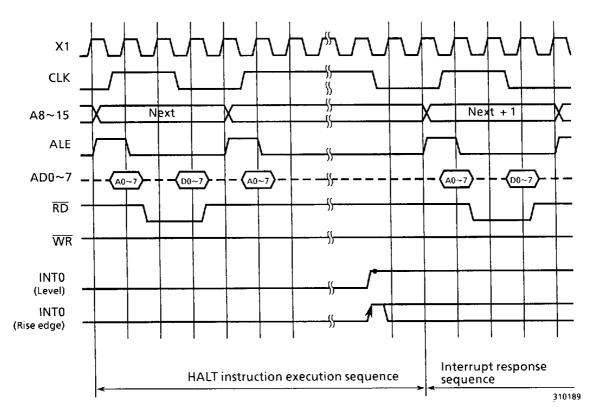

Figure 3.4 (3) shows the timing for releasing the HALT mode by interrupts in the IDLE1 mode.

In the IDLE1 mode, only the internal oscillator operates, the system clock inside MCU stops and CLK signal is fixed to "1".

In the HALT state, interrupt requests are sampled asynchronously with the system clock, whereas the HALT release (restart of operation) is performed synchronously with it.

Figure 3.4 (3) HALT Release Timing Using Interrupts in IDLE1 mode.

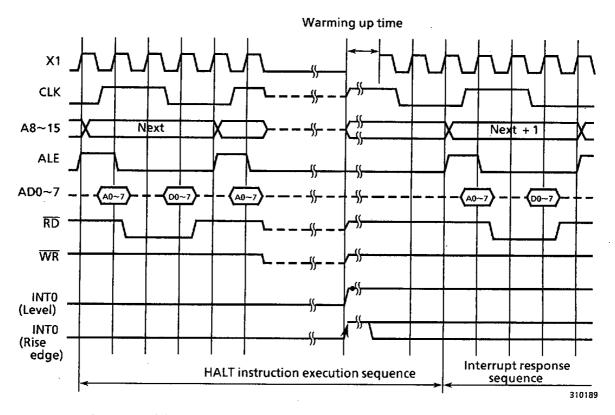

#### 3.4.3 STOP Mode

Figure 3.4 (4) shows the timing of HALT release caused by interrupts in STOP mode. In the STOP mode, all internal circuits stop, including internal oscillator. When the STOP mode is activated, all pins except special ones are put in the high-impedance state, isolated from the internal operation of MCU. Table 3.4 (1) shows the state of each pin in the STOP mode. However, if WDMOD<DRVE> (drive enable: bit 0 of memory address FFD2H) of the built-in I/O register is set to "1", the pre-halt state of the pins can be retained. The register is cleared to "0" by reset operation.

When the CPU accepts an interrupt request, the internal oscillator first restarts. However, to get the stabilized oscillation, the system clock starts its output after the time set by the warming up counter has passed. WDMOD<WARM> (warming up: bit 4 at memory address FFD2H) is used to set the warming up time. Warming up is executed for  $2^{14}$  clock oscillation time when this bit is set to "0", while  $2^{16}$  clock oscillation time when set to "1". This bit is cleared to "0" by reset operation.

Figure 3.4 (4) HALT Release Timing Using Interrupts in STOP Mode

The internal oscillator can also be restarted by inputting the  $\overline{\text{RESET}}$  signal "0" to the CPU.

However, the warming up counter remains inactive in order to make the CPU rapidly operate when the power is turned on. Accordingly, wrong operation may occur due to unstable clocks immediately after the internal oscillator has restarted. To release the HALT state by resetting in the STOP mode,  $\overline{\text{RESET}}$  signal must be kept at "0" for a sufficient period of time.

| Pin name                        | I/O                                                             | DRVE = 0                | DRVE = 1                             |

|---------------------------------|-----------------------------------------------------------------|-------------------------|--------------------------------------|

| P00~P07                         | Input mode<br>Output mode                                       |                         | <br>Output                           |

| P10~P17                         | Input mode<br>Output mode                                       |                         | Output                               |

| P20~P27                         | Input mode<br>Output mode                                       |                         | Input<br>Output                      |

| P30~P37                         | Input mode<br>Output mode                                       |                         | Input<br>Output                      |

| P40~P44                         | Input mode<br>Output mode                                       |                         | input<br>Output                      |

| P45 (INT0)                      | Input mode<br>Output mode                                       | Input                   | Input<br>Output                      |

| P46, P47                        | Input mode<br>Output mode                                       |                         | Input*<br>Output                     |

| P50~P53                         | Input pin                                                       |                         |                                      |

| P56, P57                        | Output pin                                                      |                         | Output                               |

| P60~P63                         | Input mode<br>Output mode                                       | Output                  | Output                               |

| P70~P73                         | Input mode<br>Output mode                                       | Output                  | Output                               |

| CLK<br>RESET<br>ALE<br>EA<br>X1 | Output pin<br>Input pin<br>Output pin<br>Input pin<br>Input pin | Input<br>" 0 "<br>Input | " 1 "<br>Input<br>" 0 "<br>Input<br> |

| X2                              | Output pin                                                      | "1"                     | "1"                                  |

Table 3.4 (1) State of Pins in STOP Mode

\* : When in zero cross detect mode, intermediate bias is still applied to this pin.

Indicates that input mode/input pin cannot be used for input and that the output mode/output pin have been set to high impedance.

Input : Input is enabled.

Input : The input gate is operating. Fix the input voltage at "0" or "1" to prevent input pin floating.

Output : Output status

|                                 | ,                         | HALT mode                | RUN IDLE1                                            |              | STOP              |  |  |

|---------------------------------|---------------------------|--------------------------|------------------------------------------------------|--------------|-------------------|--|--|

|                                 | WDM                       | OD <haltm1,0></haltm1,0> | 00                                                   | 10           | 01                |  |  |

| 0                               | CPU                       |                          | Halt                                                 |              |                   |  |  |

| p<br>e                          | I/O port                  |                          | Retains the state when HALT instruction is executed. |              | See Table 3.4 (1) |  |  |

| r<br>a                          |                           | t timer                  | instruction                                          | is executed. |                   |  |  |

| t<br>i<br>g<br>b<br>l<br>o<br>c | 16-bit timer              |                          |                                                      |              |                   |  |  |

|                                 | Stepping motor controller |                          |                                                      |              |                   |  |  |

|                                 | Serial interface          |                          | Operation                                            | На           |                   |  |  |

|                                 | A/D converter             |                          |                                                      |              |                   |  |  |

|                                 | Watchdog timer            |                          |                                                      |              |                   |  |  |

| k                               | Interrupt controller      |                          |                                                      |              |                   |  |  |

| H<br>A<br>L<br>T                |                           | INTWD                    | 0                                                    |              |                   |  |  |

|                                 | 1                         | INTO                     | 0                                                    | 0            | 0                 |  |  |

|                                 |                           | INTT1                    | 0                                                    |              | —                 |  |  |

|                                 | n                         | INTT2                    | Ο.                                                   |              |                   |  |  |

| r<br>e                          | t                         | INTAD                    | 0                                                    | ·····        | —                 |  |  |

| l<br>e                          | e<br>r                    | INTT3                    | 0                                                    |              | —                 |  |  |

| a<br>s                          |                           | INTT4                    | 0                                                    |              |                   |  |  |

| i                               |                           | INT1                     | 0                                                    |              |                   |  |  |

| n<br>g                          | r.                        | INTT5                    | 0                                                    |              | . —               |  |  |

| S                               | u                         | INT2                     | 0                                                    |              |                   |  |  |

| o<br>u                          | .p<br>t                   | INTRX                    | 0                                                    | —            |                   |  |  |

| r                               |                           | INTTX                    | 0                                                    |              | _                 |  |  |

| c<br>e                          |                           | INTFL                    | 0                                                    |              | —                 |  |  |

|                                 |                           | INTEP                    | 0                                                    |              |                   |  |  |

| l                               | Rese                      | t                        | 0                                                    | 0 0          |                   |  |  |

Table 3.4 (2) I/O Operation and Release in HALT Mode

Can be used for HALT release Cannot be used for HALT release <u>O</u>:

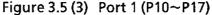

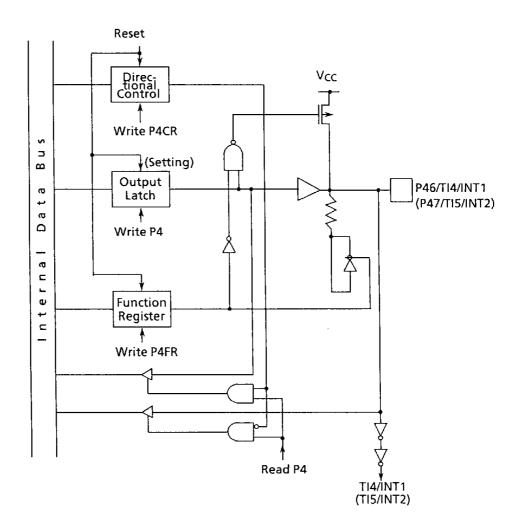

## 3.5 Function of Ports

TMP90C844 has a total of 54 I/O port pins. These port pins function not only as the general-purpose I/O ports but also as the I/O ports for the internal CPU and built-in I/O. Table 3.5 shows the functions of these port pins.

| Port name | Pin name | No. of<br>pins | Direction | Direction<br>setting unit | Pin name for internal function |

|-----------|----------|----------------|-----------|---------------------------|--------------------------------|

| Port 0    | P00~P07  | 8              | 1/0       | Bit                       | AD0~AD7                        |

| Port 1    | P10~P17  | 8              | I/O       | Bit                       | A8~A15                         |

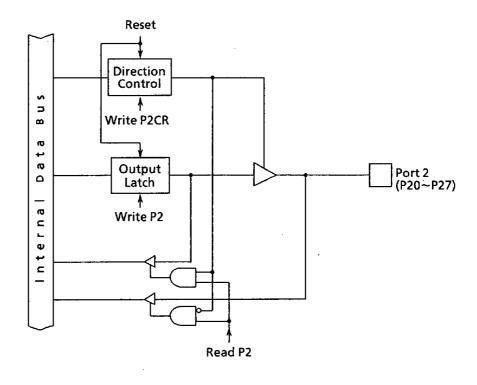

| Port 2    | P20~P27  | 8              | I/O       | Bit                       | SB0~SB7 (P27: WAIT)            |

| Port 3    | P30      | 1              | I/O       | Bit                       | SWR                            |

|           | P31      | 1              |           |                           | SRD                            |

|           | P32      | 1              |           |                           | SCS                            |

|           | P33      | 1              |           |                           | C/D                            |

|           | P34      | 1              |           |                           | STA                            |

|           | P35      | 1              |           |                           | RxD                            |

|           | P36      | 1              |           |                           | SCLK                           |

|           | P37      | 1              |           |                           | TxD                            |

| Port 4    | P40      | 1              | I/O       | Bit                       | TO1                            |

|           | P41      | 1              |           |                           | ТОЗ                            |

|           | P42      | 1              |           |                           | TO4                            |

|           | P43      | 1              |           |                           | TO5                            |

|           | P44      | 1              |           |                           | тю                             |

|           | P45      | 1              |           |                           | INT0/TI2                       |

|           | P46      | 1              |           |                           | INT1/TI4                       |

|           | P47      | 1              |           |                           | INT2/TI5                       |

| Port 5    | P50~P53  | 4              | Input     |                           | AN0~AN3                        |

|           | P56      | 1              | Output    | _                         | RD                             |

|           | P57      | 1              | Output    |                           | WR                             |

| Port 6    | P60~P63  | 4              | I/O       | Bit                       | M00~M03                        |

| Port 7    | P70~P73  | 4              | I/O       | Bit                       | M10~M13                        |

| Table 3.5 | Function | of | Ports |

|-----------|----------|----|-------|

|-----------|----------|----|-------|

These port pins function as the general-purpose I/O ports by resetting. The port pins, for which input or output is programmably selectable, function as input ports by resetting. A separate program is required to use them for an internal function.

### TOSHIBA

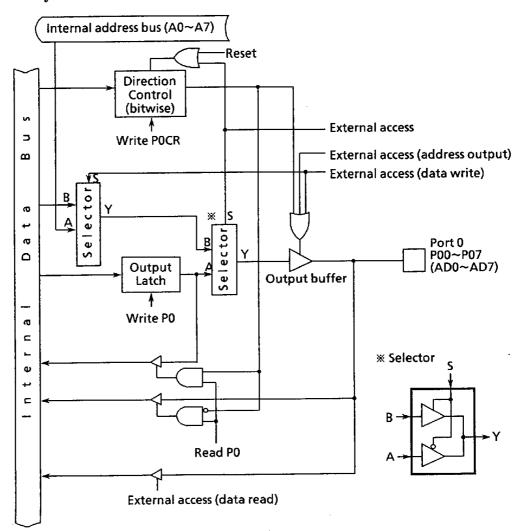

#### 3.5.1 Port 0 (P00~P07)

Port 0 is the 8-bit general-purpose I/O port P0, each bit of which can be set independently for input or output. The control register P0CR is used to set input or output. Reset operations clear all output latch and control register bits to "0" and set port 0 to the input mode. In addition to the general-purpose I/O port function, port 0 also functions as an address/data bus (AD0~AD7). When external memory is accessed, port 0 automatically functions as the address/data bus.

Figure 3.5 (1) Port 0 (P00~P07)

Figure 3.5 (2) Registers for Port 0

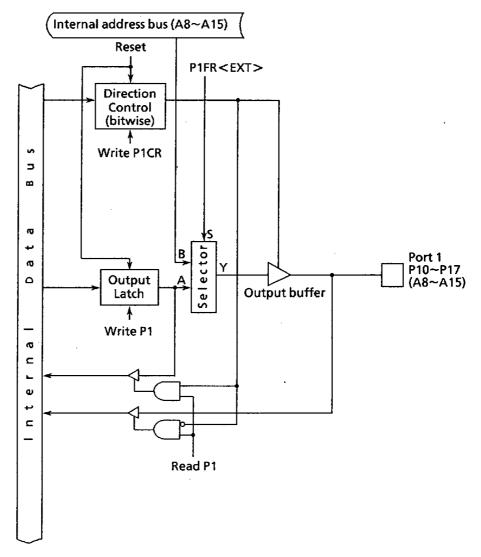

### 3.5.2 Port 1 (P10~P17)

Port 1 is the 8-bit general-purpose I/O port P1, each bit of which can be set to input or output. The port 1 control register P1CR is used to set input or output. Reset operations clear all output latch and control register bits to "0" and sets all port 1 bits to the input mode.

In addition to the general-purpose I/O port function, port 1 also functions as an address bus (A8~A15). This is specified by setting the external extended specification register IRFL<EXT> to "1" and setting P1CR to the output mode. When the P1CR value is "0," port 1 is set to the input mode, regardless of the external extended specification register value.

MCU90-180 9097249 0041292 8TT M

|           |                           |            |       | Port        | t 1 registe | г            |                     |                          |                                  |

|-----------|---------------------------|------------|-------|-------------|-------------|--------------|---------------------|--------------------------|----------------------------------|

|           | /                         | 7          | 6     | 5           | 4           | 3            | 2                   | 1                        | 0                                |

| P1        | bit Symbol                | P17        | P16   | P15         | P14         | P13          | P12                 | P11                      | P10                              |

| (FFC2H)   | Read/Write                |            |       |             | RA          | N            |                     |                          |                                  |

|           | After reset               |            |       |             | Input       | node         |                     |                          |                                  |

|           |                           |            |       | Port 1 c    | ontrol reg  | jister       |                     |                          |                                  |

|           |                           | 7          | 6     | 5           | 4           | 3            | 2                   | 1                        | 0                                |

| P1CR      | bit Symbol                | P17C       | P16C  | P15C        | P14C        | P13C         | P12C                | P11C                     | P10C                             |

| (FFC3H)   | Read/Write                |            |       |             | N           | /            |                     |                          |                                  |

|           | After reset               | 0          | 0     | 0           | 0           | 0            | 0                   | 0                        | D                                |

|           | Function                  |            | 0: IN | 1: OUT (inp | ut or outpu | t can be spe | cified for e        | each bit)                |                                  |

|           |                           | L          |       |             | <u> </u>    |              |                     |                          |                                  |

|           |                           |            |       |             |             |              |                     | Port 1 I/C               | ) setting<br>nput                |

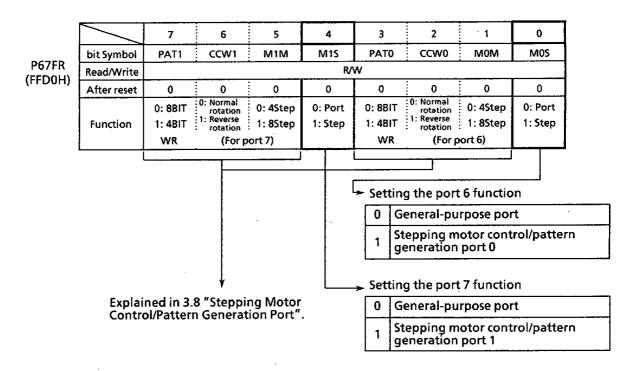

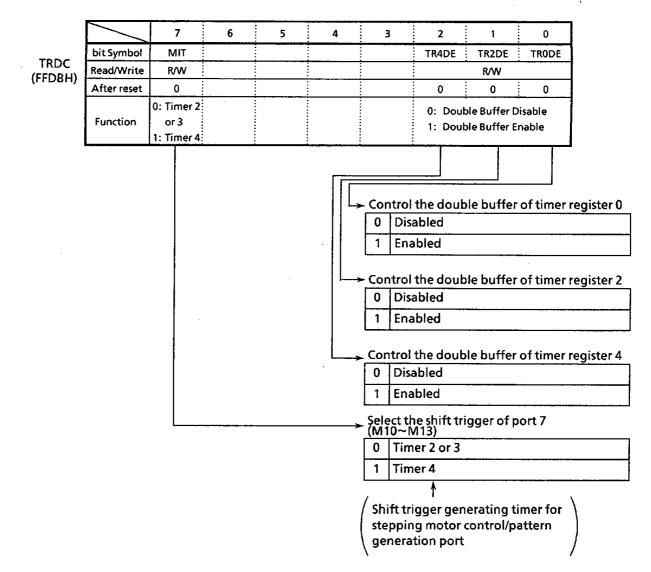

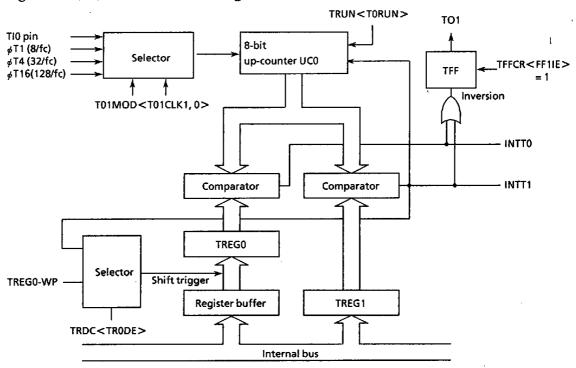

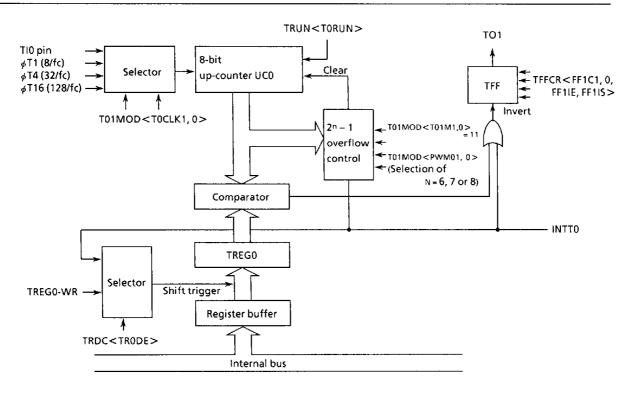

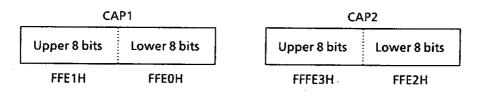

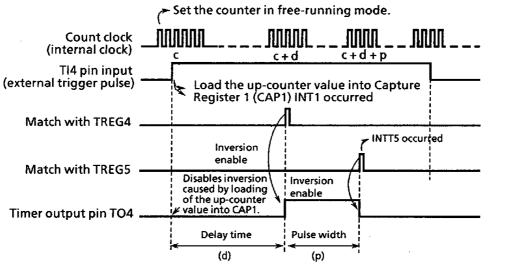

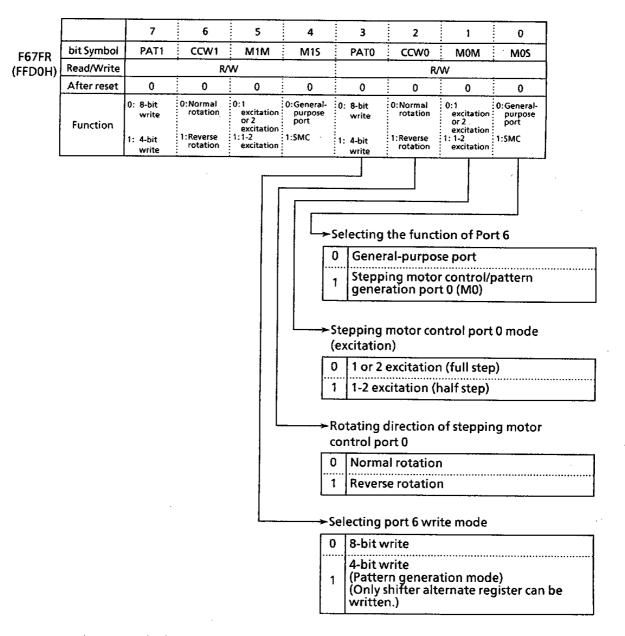

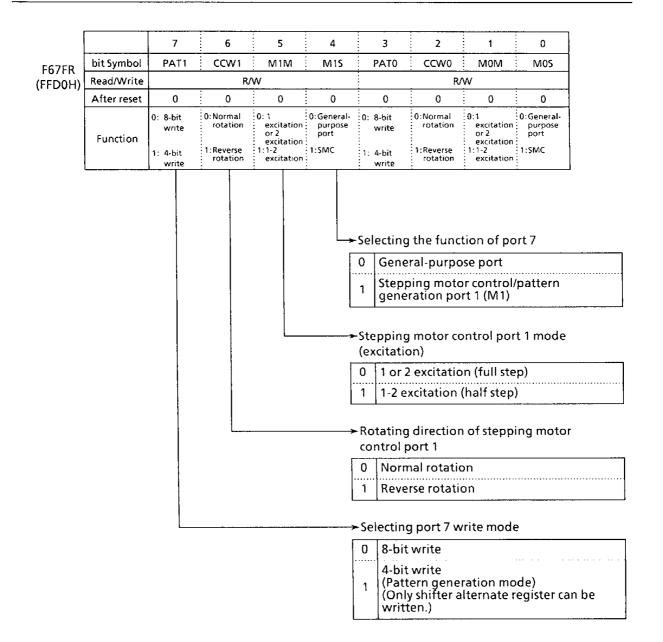

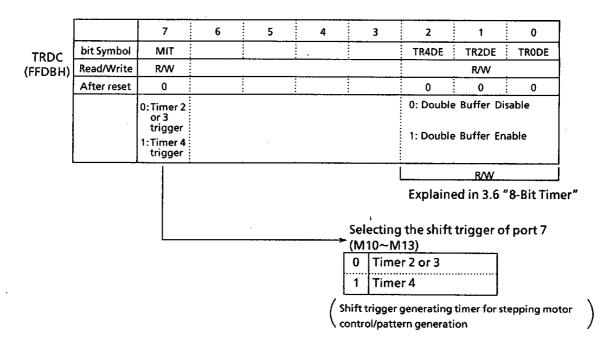

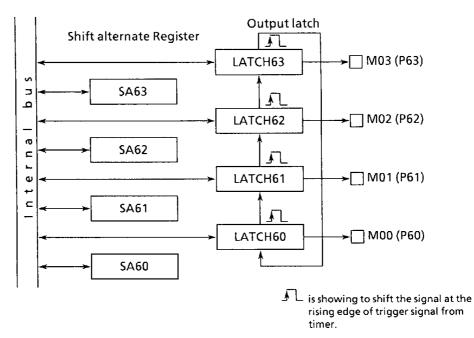

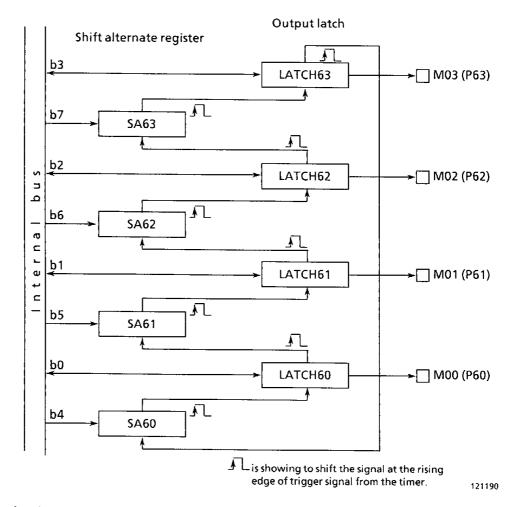

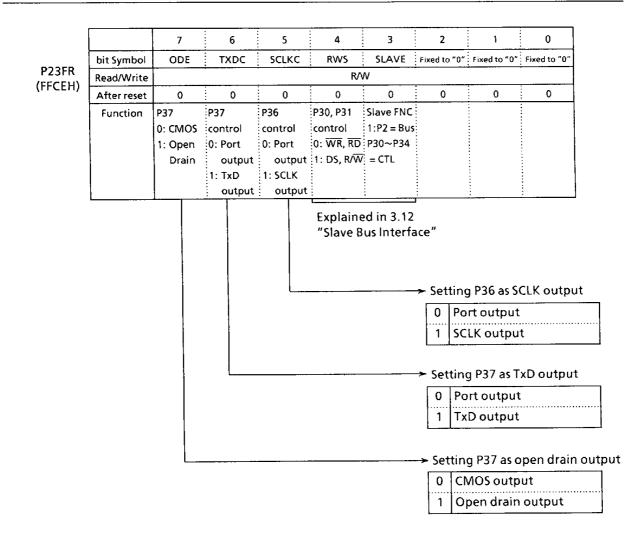

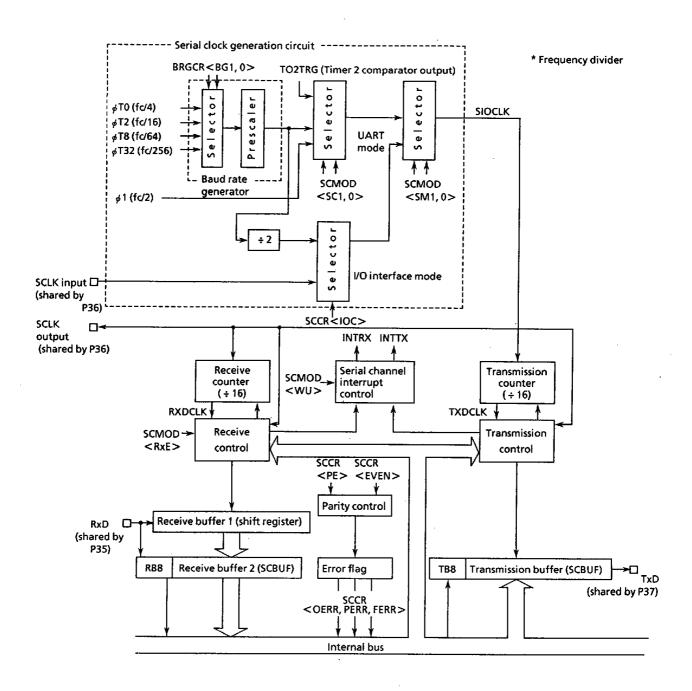

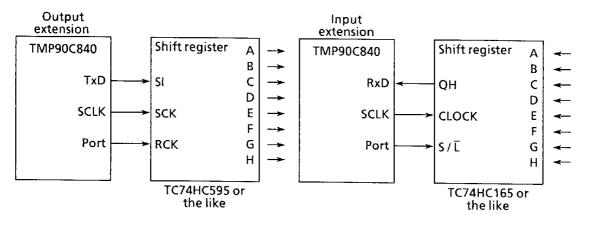

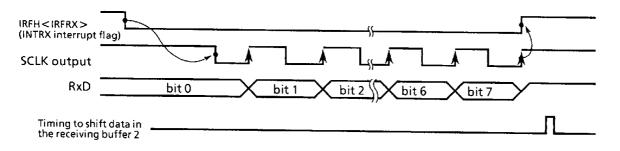

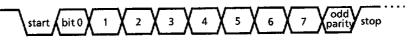

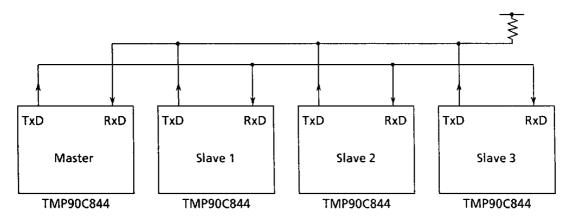

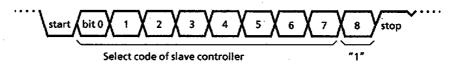

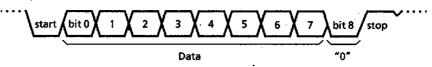

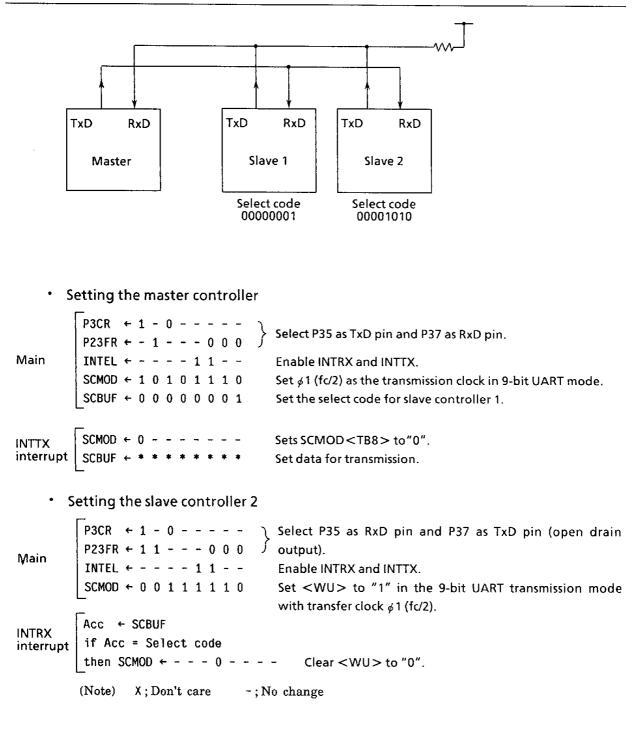

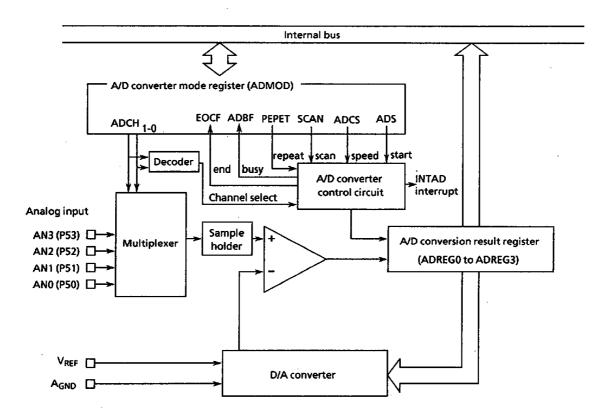

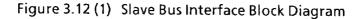

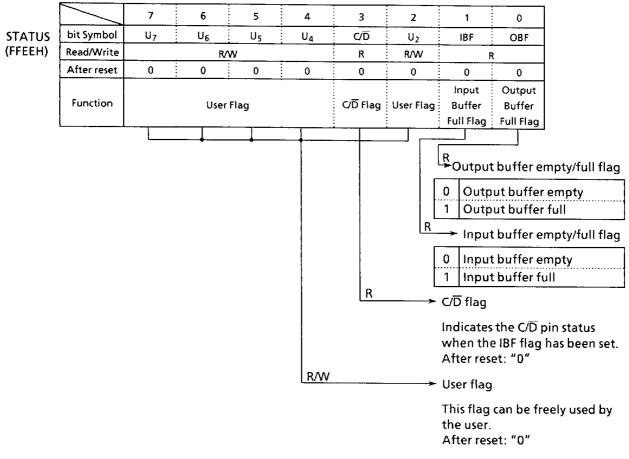

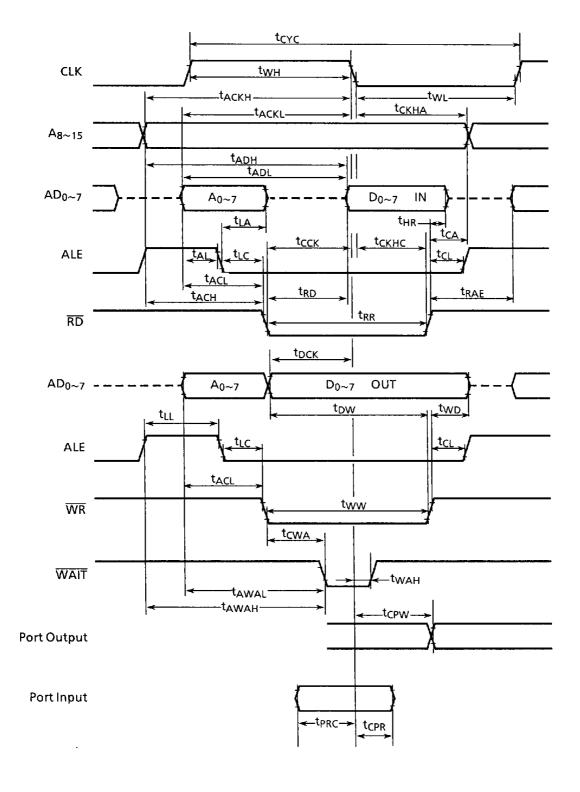

|           |                           |            |       |             |             |              |                     | ····                     |                                  |