# SULCON SYSTEMS INNOVATORS IN INTEGRATION

# SS1 78P8060 CMOS Digital IC T1 Receiver

July 1988

DESCRIPTION

The SSI 78P8060 is a CMOS digital IC that receives and deserializes serial unipolar data in a T1, D2 or T1, D3 format. The IC is functionally identical and pin compatible with the Rockwell R8060 but offers reduced power consumption and provides greater output current drive (fully TTL).

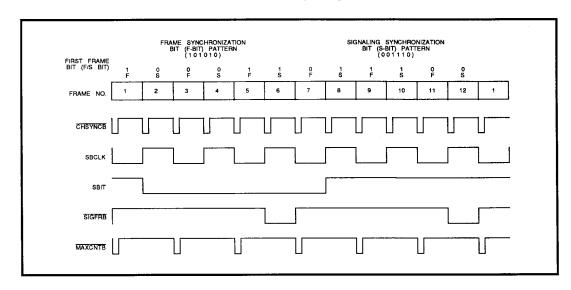

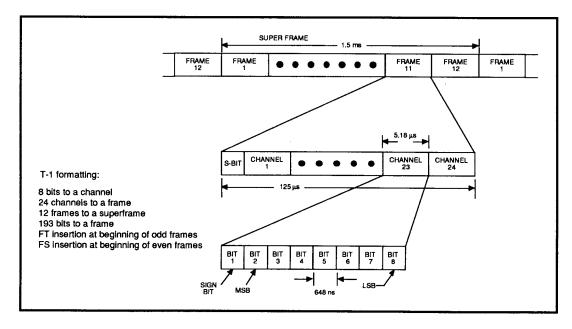

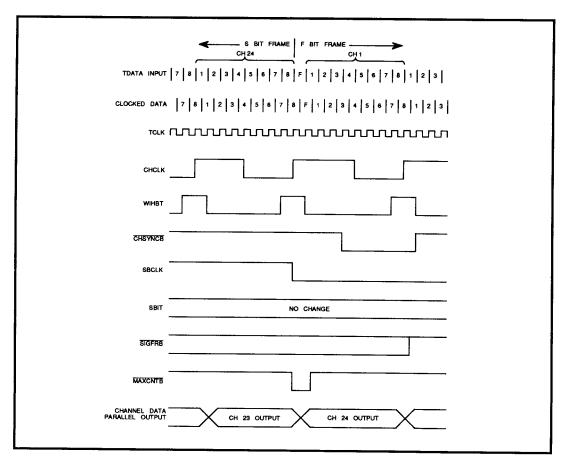

The IC receives 1.544 MBit/s unipolar data and an extracted clock. The data pattern is in 193 bit frames, each frame consisting of a frame bit (FT) or a signaling bit (FS) followed by 192 bits of data representing 24 channels of 8-bit words. F frames and S frames alternate. The receiver sychronizes by locking to (FT) which occurs every 386 bits and which continually alters between 1 and 0, and deserializes the data stream into 24 eight-bit wide channels which are clocked out of the 8 data bit pins at a 192,000 channel/s rate with each channel repeated at a 8000 frame/s rate. Signaling bits (FS), which are positioned 193 bits behind the frame bit, are output at the SBIT pin.

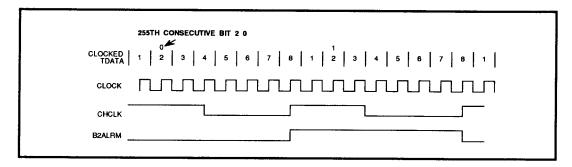

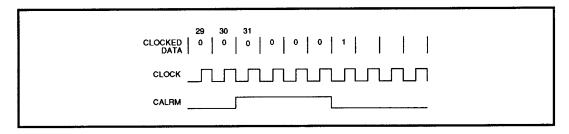

Remote alarm reporting is monitored and an alarm is indicated at the B2ALRM pin if 255 consecutive bit two zeros are received. The incoming data is monitored for loss of carrier and an alarm is indicated at the CALRM pin if 31 consecutive zero bits are received.

#### **FEATURES**

- Locks onto and deserializes incoming T1, D2 and T1, D3 data in 5 ms

- Generates timing signals to synchronize channel and frame information

- Monitors and detects

- FS bit

- Frame sync

- Carrier

- Remote alarm reporting

- TTL compatible

- CMOS low power dissipation, 5 mW typical

- Single 5V supply

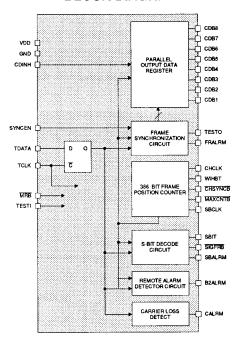

#### **BLOCK DIAGRAM**

#### **PIN DIAGRAM**

CAUTION: Use handling procedures necessary for a static sensitive component.

# SSI 78P8060 CMOS Digital IC T1 Transmitter

### **PIN DESCRIPTION**

| NAME    | TYPE | DESCRIPTION                                                                                                                                                                                                                      |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLK    | I    | Data Clock. Nominal clock frequency is 1.544 MHz. Data bits are clocked into the chip on the falling edge of the clock.                                                                                                          |

| WIHBT   | 0    | Write Inhibit Clock. Strobes high once every channel for two TCLK periods and is used to load the 8-bit parallel channel output data into external circuitry.                                                                    |

| B2ALRM  | 0    | Bit 2 Alarm Signal, active high. Goes high indicating a remote alarm when 255 consectutive 0's are received in the bit 2 position. Resets low after bit 2 becomes 1.                                                             |

| TESTI   | I    | Test Input, when low puts the circuit in its test mode. Must be high or left open during normal operation.                                                                                                                       |

| FRALRM  | 0    | Frame Alarm, active high. Goes high when frame sync is lost.                                                                                                                                                                     |

| CHCLK   | 0    | Output Data Channel Clock. Going high signals new parallel data output.                                                                                                                                                          |

| MAXCNTB | 0    | Strobes low once every two frames for one TCLK period during the expected input of FT.                                                                                                                                           |

| CHSYNCB | 0    | Channel Sync Clock. Strobes low once every frame for six TCLK periods during channel 1.                                                                                                                                          |

| SYNCEN  | I    | Frame Synchronization Enable. When low, disables the automatic resync search intitiated by a frame alarm condition.                                                                                                              |

| MRB     | 1    | Master Reset. Active low resets the circuit.                                                                                                                                                                                     |

| GND     | -    | Ground                                                                                                                                                                                                                           |

| CALRM   | 0    | Carrier Alarm Signal, active high. Goes high if 31 consecutive zeros are received in the TDATA input. Resets low when TDATA becomes 1.                                                                                           |

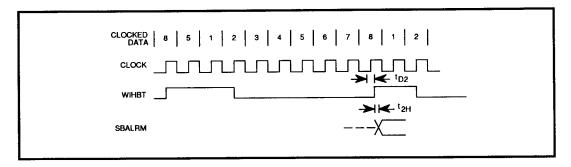

| SBALRM  | 0    | FS Alarm Signal, active high. Signals an FS alarm when the previous FS bits have been 0 followed by 1111. SBALRM is reset low when the FS bit pattern 10001 occurs. The SBALRM transition occurs during channel 1 of FS frame.   |

| TESTO   | 0    | Test Mode Output.                                                                                                                                                                                                                |

| SBIT    | 0    | Signalling Bit. Outputs the FS received 2 frames before the current FS.                                                                                                                                                          |

| CDINH   | I    | Channel Data Inhibit. When high forces CDB1 through CDB7 pins high. CDB8 is not affected.                                                                                                                                        |

| CDB1-8  | 0    | Bit 1, the sign bit, will be serially received first, followed by bits 2 (MBS) through bit 8 (LBS). The rising edge of CHCLK indicates output channel data has been clocked out and occurs as the final bit (bit 8) is received. |

| TDATA   | I    | Serial Data Input.                                                                                                                                                                                                               |

| SBCLK   | 0    | 4 KHz signal that is low during even frames and higfh during odd frames.                                                                                                                                                         |

| SIGFRB  | 0    | Signal Frame Clock. Strobes low during frames 6 and 12.                                                                                                                                                                          |

4-64 0788

#### **ELECTRICAL SPECIFICATIONS**

ABSOLUTE MAXIMUM RATINGS (Operation above absolute maximum ratings may permanently damage the device.)

| 7                   | V                      |

|---------------------|------------------------|

|                     |                        |

| - 65 to 150         | °C                     |

| 260                 | °C                     |

| V to VDD + 0.3V     | V                      |

| VDD + 0.3V or 15 mA | V                      |

| ,                   | 260<br>V to VDD + 0.3V |

#### RECOMMENDED OPERATING CONDITIONS

| PARAMETER          |     | CONDITIONS                                    | MIN | МОМ | MAX  | UNIT |

|--------------------|-----|-----------------------------------------------|-----|-----|------|------|

| VDD Supply Current | IDD | Clock active,<br>Outputs open, Inputs to rail |     |     | 5    | mA   |

| CLOCK Frequency    |     |                                               | 10  |     | 1600 | KHz  |

| VDD                | VDD |                                               | 4.5 |     | 5.5  | ٧    |

| Temperature        |     |                                               | 0   |     | 70   | °C   |

#### DC REQUIREMENTS

| PARAMETER         |     | CONDITIONS         | MIN | МОМ | MAX | UNIT     |  |

|-------------------|-----|--------------------|-----|-----|-----|----------|--|

| Input Hi Voltage  | VIH |                    | 2.0 |     |     | ٧        |  |

| Input Lo Voltage  | VIL |                    |     |     | 0.8 | V        |  |

| Output Hi Voltage | VOH | I source = -1.0 mA | 2.4 |     |     | ٧        |  |

| Output Lo Voltage | VOL | 1 sink = 2.0 mA    |     |     | 0.4 | <b>V</b> |  |

#### **TIMING CHARACTERISTICS**

| PARAMETER        |     | CONDITIONS                 | MIN | МОМ | МАХ | UNIT |

|------------------|-----|----------------------------|-----|-----|-----|------|

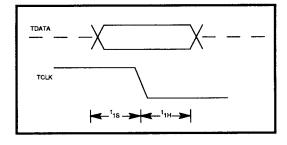

| TDATA Setup Time | t1s | from CLOCK edge falling    | 100 |     |     | ns   |

| TDATA Hold Time  | t1h | from CLOCK edge falling    | 100 |     |     | ns   |

| Setup Time       | t2h | (1) from WIHBT edge rising | 0   |     |     | ns   |

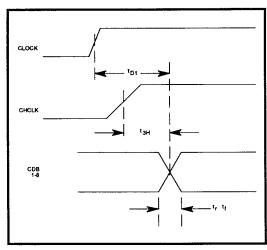

| CDB1-8 Hold Time | t3h | from CHCLK edge rising     | 0   | 200 |     | ns   |

| Output Delay     | td1 | (2) from CLOCK edge rising |     | 300 |     | ns   |

| Output Delay     |     | (3) from CLOCK edge rising |     | 400 |     | ns   |

4-65 0788

# SSI 78P8060 CMOS Digital IC T1 Transmitter

#### TIMING CHARACTERISTICS (Continued)

| PARAMETER                     | CONDITIONS                      | MIN | NOM | MAX | UNIT |

|-------------------------------|---------------------------------|-----|-----|-----|------|

| CALRM Delay                   | from CLOCK edge                 |     |     | 300 | ns   |

| FRALRM Delay                  | from CLOCK edge                 |     |     | 600 | ns   |

| Output Rise, Fall Time tr, tf | 90% to 10%                      |     |     | 100 | ns   |

| SYNCEN low (inhibit sync)     | before FRALARM edge rising      | 200 |     |     | ns   |

| SYNCEN high (initiate sync)   | before MRB edge rising          | 200 |     |     | ns   |

| CBD1-7 valid/high             | after CDINH edge falling/rising |     |     | 150 | ns   |

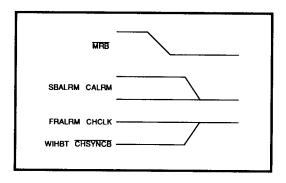

| FRALRM high                   | after MRB falling edge          |     |     | 250 | ns   |

- (1) SIGFRM, FRALRM

- (2) CHCLK, CHSYNCB, WIHBT, MAXCNTB, SBCLK

- (3) SIGFRM, SBALRM, B2ALRM, SBIT, CDB1-8

#### FRAME ALARM

FRALRM goes high indicating an out-of-frame condition when:

- The frame synchronization algorithm is in progress.

- (2 MRB is low.

- (3) The current FT is in error and a previous FT error occurred in the past four frames.

- (4) After falling edge of CALRM.

FRALRM returns low when:

- (1) Frame synchronization is complete.

- (2) CALRM is high.

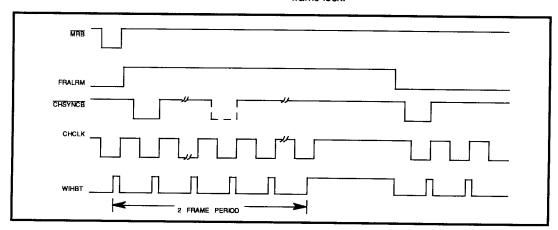

# OUTPUT CLOCK SIGNALS DURING FRAME SYNCHRONIZATION FUNCTION

During frame sync, output signals CHCLK, CHSYNCB and WIHBT will continue normally for two frame periods, then they will go high. For most data patterns frame sync requires less than 5 milliseconds to acquire frame lock

FIGURE 1: Signal Relationship during Frame Alarm and Search for Resynchronization

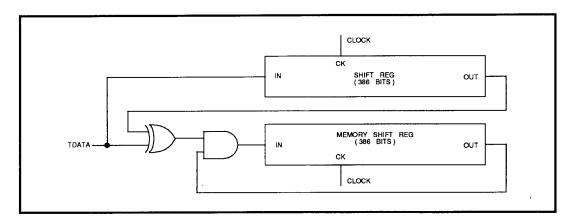

FIGURE 2: Frame Sync Algorithm

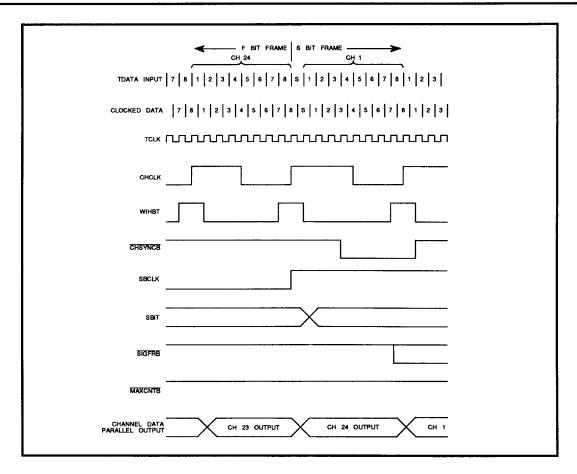

FIGURE 3: Multiframe Signal Relationships

0788 4-67

FIGURE 4: T1 Framing Format

FIGURE 5: B2ALRM

4-68 0788

FIGURE 6: SBALRM

FIGURE 7: CALRM

FIGURE 8: Input Timing

FIGURE 9: Output Timing

0788 4-69

FIGURE 10: MRB Timing

FIGURE 11: Signal Relationship at Beginning of FS Frame (S-BIT)

4-70

FIGURE 12: Signal Relationship at Beginning of FT Frame (F-BIT)

## SSI 78P8060 CMOS Digital IC T1 Transmitter

#### **PACKAGE PIN DESIGNATIONS**

TESTI ∏5 CDB8 FRALRM [ 24 CDB7 CHCLK [ Псове MAXCNTB ☐8 22 CDB5 CHSYNCB I 9 21 CDB4 П CDB3 SYNCEN 10 MRB []11 T CDB2 13 14 15 CALRM CDB1

28-Pin DIP

28-Pin PLCC

#### ORDERING INFORMATION

| PART DESCRIPTION | ORDER NO.      | PKG. MARK  |

|------------------|----------------|------------|

| SSI 78P8060      |                |            |

| 28-Pin DIP       | SSI 78P8060-CP | 78P8060-CP |

| 28-Pin PLCC      | SSI 78P8060-CH | 78P8060-CH |

No responsibility is assumed by SSi for use of this product nor for any infringements of patents and trademarks or other rights of third parties resulting from its use. No license is granted under any patents, patent rights or trademarks of SSi. SSi reserves the right to make changes in specifications at any time without notice.

Silicon Systems

Silicon Systems, Inc., 14351 Myford Road, Tustin.

CA 92680 (714) 731-7110, TWX 910-595-2809