SATURN USER NETWORK INTERFACE (622-MAX)

# **PM5356**

# S/UNI-622-MAX

# SATURN USER NETWORK INTERFACE (622-MAX)

# **DATASHEET**

**ISSUE 6: JUNE 2000**

SATURN USER NETWORK INTERFACE (622-MAX)

# **REVISION HISTORY**

| ISSUE | DATE      | DETAIL                                                                                                                                                                       |

|-------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6     | June 2000 | Corrected block diagram.                                                                                                                                                     |

|       |           | Corrected function name errors in Register 0x03: S/UNI-622 MAX Clock Monitors. Changed PTCLKI to PTCLK, REFCLKI to REFCLK, RFCLKI to RFCLK, RCLKI to RCLK and TCLKI to TCLK. |

|       |           | Added line loopback operation information to RXDINV and TXDINV in Register 0x07: S/UNI-622-MAX Miscellaneous Configuration.                                                  |

|       |           | Rewrote IINVCNT bit functionality for clarity. Register 0x30 (EXTD=1): RPOP Status/Control.                                                                                  |

|       |           | Rewrote DOOLI bit functionality to indicate change to DOOLV bit and CRU out of lock conditions in Register 0.5C: CRSI Configuration.                                         |

|       |           | Rewrote DOOLE bit functionality to indicate change to DOOLV register events in Register 0x5D: CRSI Status.                                                                   |

| ISSUE | DATE               | DETAIL                                                                                                                       |

|-------|--------------------|------------------------------------------------------------------------------------------------------------------------------|

| 5     | Dec, 1999          | #1 Modified section 9.4 (UTOPIA pin description) and section 14.2 (Functional timing) to reflect operation of the RCA signal |

|       |                    | #2 DC characteristics update (Section 16)                                                                                    |

|       |                    | #3 Registers updated with correct defaults and descriptions:                                                                 |

|       |                    | Register 0X01, Bit 4 (TFPEN), Defaults To 1, Not 0                                                                           |

|       |                    | Register 0X08, Description Incorrect                                                                                         |

|       |                    | Register 0X09 Description Incorrect                                                                                          |

|       |                    | New Register 0XFC: Concatenation Status And Enable                                                                           |

|       |                    | New Register 0XFD: Concatenation Interrupt Status                                                                            |

|       |                    | New Register Bit Required For OC-3 Operation (Register 0X07)                                                                 |

|       |                    | Register 0X5E Bit 5 (RTYPE) should be set to zero for improved Jitter Tolerance                                              |

|       |                    | Register 0X00 Type Bits Incorrect                                                                                            |

|       |                    | Loss Of Multi-frame Tributary AIS (LOMTUAIS) Bit 2 Incorrectly Stated In Register 0X0D                                       |

|       |                    | #4 APS pin description modified #6 Updated TFCLK timing specifications, RFCLK timing specifications                          |

|       |                    | #7 Diagnostic Loop-back Clarification                                                                                        |

|       |                    | #8 Bit Error Rate Monitor Table Update                                                                                       |

|       |                    | #9 Receive Data Requires 3 RFCLK Cycles Before Becoming Valid (Utopia Level 3 Only)                                          |

|       |                    | #11 Receive Line AIS Insertion Is Not Gated By ALLONES                                                                       |

|       |                    | #12 Large Power Supply Glitch (Beyond Specification) Can Cause Clock Synthesis Unit To Lose Lock To Reference.               |

| 4     | January 4,<br>1999 | Corrected wrong pin number assignments in pin description.                                                                   |

| 3     | Dec 15,<br>1999    | General update                                                                                                               |

| 2     | Aug 30,<br>1998    | Re-organized registers. Removed UDF. Update pin list and block diagram. Add preliminary simulation and test sections text.   |

*PM5356* S/U<u>NI-622-MAX</u>

ISSUE 6

| ISSUE | DATE        | DETAIL           |

|-------|-------------|------------------|

| 1     | Jan 5, 1998 | Created document |

#### SATURN USER NETWORK INTERFACE (622-MAX)

# **CONTENTS**

| 1  | FEATU  | JRES                                                               | 1  |

|----|--------|--------------------------------------------------------------------|----|

|    | 1.1    | GENERAL                                                            | 1  |

|    | 1.2    | THE SONET RECEIVER                                                 | 2  |

|    | 1.3    | THE RECEIVE ATM PROCESSOR                                          | 2  |

|    | 1.4    | THE SONET TRANSMITTER                                              | 3  |

|    | 1.5    | THE TRANSMIT ATM PROCESSOR                                         | 4  |

| 2  | APPLI  | CATIONS                                                            | 5  |

| 3  | REFE   | RENCES                                                             | 6  |

| 4  | DEFIN  | IITIONS                                                            | 7  |

| 5  | APPLI  | CATION EXAMPLES                                                    | 10 |

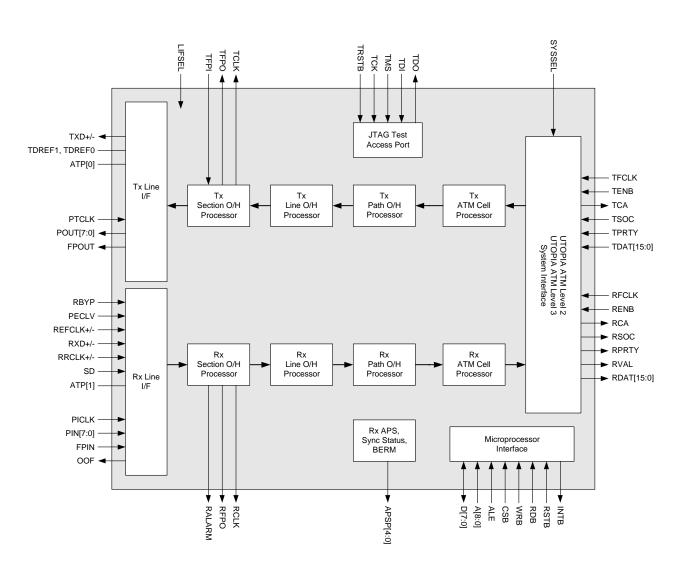

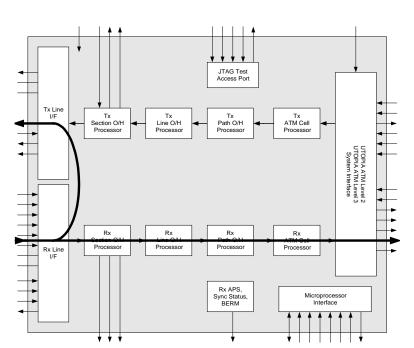

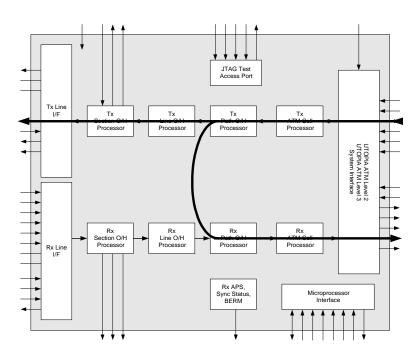

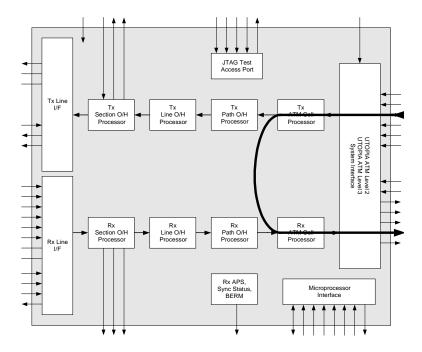

| 6  | BLOC   | K DIAGRAM                                                          | 13 |

| 7  | DESC   | RIPTION                                                            | 14 |

| 8  | PIN DI | IAGRAM                                                             | 16 |

| 9  | PIN DI | ESCRIPTION                                                         | 17 |

|    | 9.1    | SERIAL LINE SIDE INTERFACE SIGNALS                                 | 17 |

|    | 9.2    | PARALLEL LINE SIDE INTERFACE SIGNALS - CRU AND CSU BYPASS          | 19 |

|    | 9.3    | CLOCKS AND ALARMS SIGNALS                                          | 22 |

|    | 9.4    | ATM (UTOPIA) SYSTEM INTERFACE                                      | 24 |

|    | 9.5    | MICROPROCESSOR INTERFACE SIGNALS                                   | 31 |

|    | 9.6    | JTAG TEST ACCESS PORT (TAP) SIGNALS                                | 33 |

|    | 9.7    | ANALOG SIGNALS                                                     | 34 |

|    | 9.8    | POWER AND GROUND                                                   | 35 |

| 10 | FUNC   | TIONAL DESCRIPTION                                                 | 41 |

|    | 10.1   | RECEIVE LINE INTERFACE (CRSI-622)                                  | 41 |

|    | 10.2   | RECEIVE SECTION OVERHEAD PROCESSOR (RSOP)                          | 43 |

|    | 10.3   | RECEIVE LINE OVERHEAD PROCESSOR (RLOP)                             | 45 |

|    | 10.4   | THE RECEIVE APS, SYNCHRONIZATION EXTRACTOR AND BIT ERROR MO (RASE) |    |

|    | 10.5   | RECEIVE PATH OVERHEAD PROCESSOR (RPOP)                             | 47 |

|    | 10.6   | RECEIVE ATM CELL PROCESSOR (RXCP)                                  | 52 |

|    | 10.7   | TRANSMIT LINE INTERFACE (CSPI-622)               | 56  |

|----|--------|--------------------------------------------------|-----|

|    | 10.8   | TRANSMIT SECTION OVERHEAD PROCESSOR (TSOP)       | 57  |

|    | 10.9   | TRANSMIT LINE OVERHEAD PROCESSOR (TLOP)          | 58  |

|    | 10.10  | TRANSMIT PATH OVERHEAD PROCESSOR (TPOP)          | 58  |

|    | 10.11  | TRANSMIT ATM CELL PROCESSOR (TXCP)               | 60  |

|    | 10.12  | ATM UTOPIA SYSTEM INTERFACES                     | 61  |

|    | 10.13  | JTAG TEST ACCESS PORT                            | 63  |

|    | 10.14  | MICROPROCESSOR INTERFACE                         | 63  |

| 11 | NORM   | AL MODE REGISTER DESCRIPTION                     | 69  |

| 12 | TEST F | FEATURES DESCRIPTION                             | 227 |

|    | 12.1   | MASTER TEST AND TEST CONFIGURATION REGISTERS     | 227 |

|    | 12.2   | JTAG TEST PORT                                   | 230 |

| 13 | OPER/  | ATION                                            | 237 |

|    | 13.1   | SONET/SDH FRAME MAPPINGS AND OVERHEAD BYTE USAGE | 237 |

|    | 13.2   | ATM CELL DATA STRUCTURE                          | 242 |

|    | 13.3   | SETTING SONET OR SDH MODE OF OPERATION           | 243 |

|    | 13.4   | BIT ERROR RATE MONITOR                           | 245 |

|    | 13.5   | AUTO ALARM CONTROL CONFIGURATION                 | 246 |

|    | 13.6   | CLOCKING OPTIONS                                 | 247 |

|    | 13.7   | LOOPBACK OPERATION                               | 248 |

|    | 13.8   | 1+1 APS SUPPORT                                  | 252 |

|    | 13.9   | JTAG SUPPORT                                     | 253 |

|    | 13.10  | BOARD DESIGN RECOMMENDATIONS                     | 258 |

|    | 13.11  | POWER SUPPLIES                                   | 259 |

|    | 13.12  | INTERFACING TO ECL OR PECL DEVICES               | 262 |

|    | 13.13  | CLOCK SYNTHESIS AND RECOVERY                     | 264 |

|    | 13.14  | SYSTEM INTERFACE DLL OPERATION                   | 265 |

| 14 | FUNCT  | FIONAL TIMING                                    | 267 |

|    | 14.1   | PARALLEL LINE INTERFACE                          | 267 |

|    | 14.2   | ATM UTOPIA LEVEL 2 SYSTEM INTERFACE              | 268 |

|    | 14.3   | ATM UTOPIA LEVEL 3 SYSTEM INTERFACE              | 269 |

| 15 | ABSOL  | LUTE MAXIMUM RATINGS                             | 272 |

PMC-1980589

#### ISSUE 6

| 16 | D.C. CI  | HARACTERISTICS                             |

|----|----------|--------------------------------------------|

| 17 | MICRO    | PROCESSOR INTERFACE TIMING CHARACTERISTICS |

| 18 | A.C. TII | MING CHARACTERISTICS                       |

|    | 18.1     | SYSTEM RESET TIMING                        |

|    | 18.2     | PARALLEL LINE INTERFACE TIMING             |

|    | 18.3     | SERIAL LINE INTERFACE TIMING               |

|    | 18.4     | UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING     |

|    | 18.5     | UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING     |

|    | 18.6     | CLOCK AND FRAME PULSE INTERFACE TIMING     |

|    | 18.7     | JTAG TEST PORT TIMING                      |

| 19 | ORDEF    | RING AND THERMAL INFORMATION               |

| 20 | MECHA    | ANICAL INFORMATION295                      |

#### SATURN USER NETWORK INTERFACE (622-MAX)

# **LIST OF TABLES**

| TABLE 1: POINTER INTERPRETER EVENT (INDICATIONS) DESCRIPTION          | 48  |

|-----------------------------------------------------------------------|-----|

| TABLE 2: POINTER INTERPRETER TRANSITION DESCRIPTION                   | 50  |

| TABLE 3: REGISTER MEMORY MAP                                          | 63  |

| TABLE 4: TEST MODE REGISTER MEMORY MAP                                | 227 |

| TABLE 5: INSTRUCTION REGISTER (LENGTH - 3 BITS)                       | 230 |

| TABLE 6: S/UNI-622-MAX IDENTIFICATION REGISTER                        | 230 |

| TABLE 7: S/UNI-622-MAX BOUNDARY SCAN REGISTER                         | 230 |

| TABLE 8: SETTINGS FOR SONET OR SDH OPERATION                          | 244 |

| TABLE 9: RECOMMENDED BERM SETTINGS                                    | 246 |

| TABLE 10: PATH RDI AND EXTENDED RDI REGISTER SETTINGS                 | 246 |

| TABLE 11: 1+1 APS REGISTER 0X06 SETTINGS                              | 253 |

| TABLE 12: ABSOLUTE MAXIMUM RATINGS                                    | 272 |

| TABLE 13: D.C CHARACTERISTICS                                         | 273 |

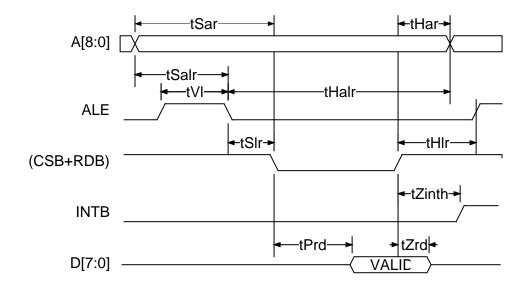

| TABLE 14: MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 35)            | 276 |

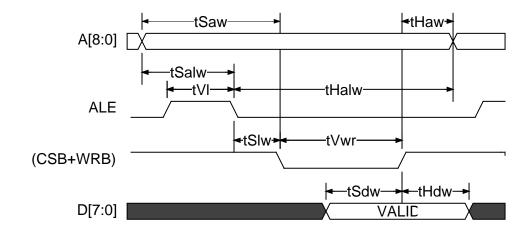

| TABLE 15: MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 36)           | 278 |

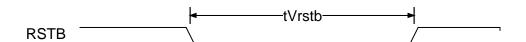

| TABLE 16: RSTB TIMING (FIGURE 37)                                     | 280 |

| TABLE 17: TRANSMIT PARALLEL LINE INTERFACE TIMING (FIGURE 38)         | 281 |

| TABLE 18: RECEIVE PARALLEL LINE INTERFACE TIMING (FIGURE 39)          | 282 |

| TABLE 19: RECEIVE SERIAL LINE INTERFACE TIMING (FIGURE 40)            | 283 |

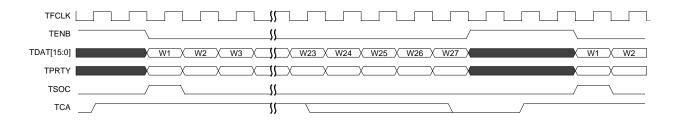

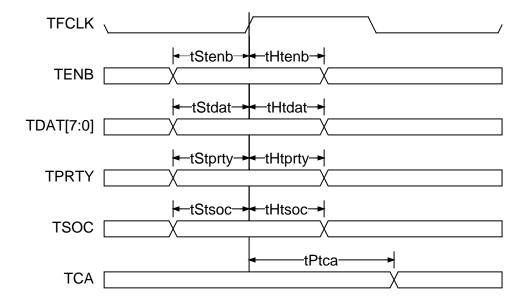

| TABLE 20: TRANSMIT UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING (FIGURE 41) | 284 |

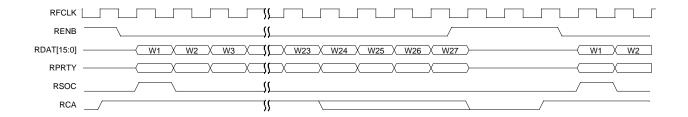

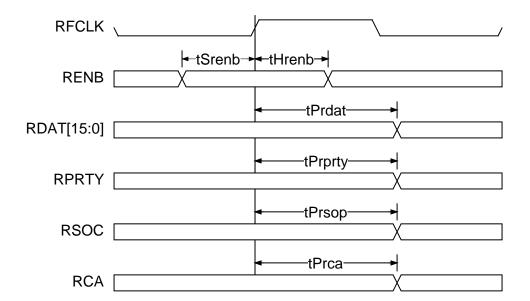

| TABLE 21: RECEIVE UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING (FIGURE 42)  | 286 |

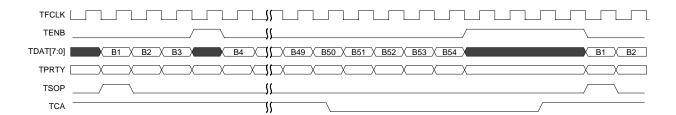

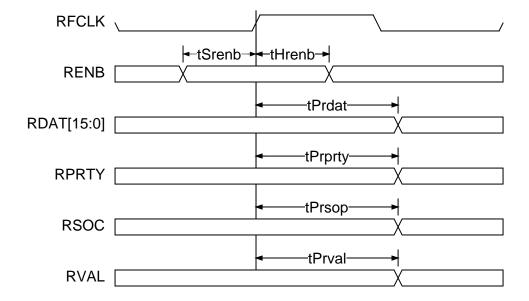

| TABLE 22: TRANSMIT UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING (FIGURE 43) | 288 |

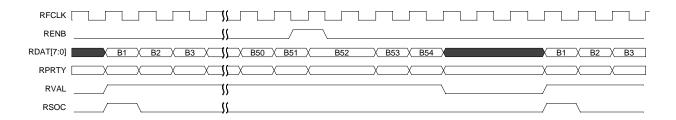

| TABLE 23: RECEIVE UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING (FIGURE 44)  | 290 |

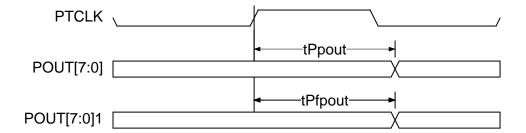

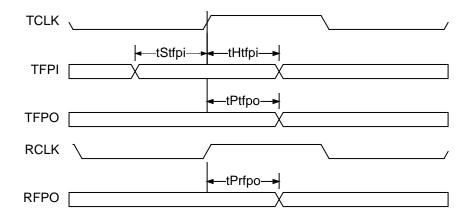

| TABLE 24: CLOCK AND FRAME PULSE INTERFACE TIMING (FIGURE 45)          | 291 |

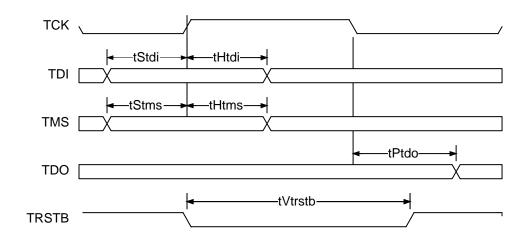

| TABLE 25: JTAG PORT INTERFACE (FIGURE 46)                             | 292 |

| TABLE 26: ORDERING INFORMATION                                        | 294 |

| TABLE 27: THERMAL INFORMATION                                         | 294 |

#### SATURN USER NETWORK INTERFACE (622-MAX)

# **LIST OF FIGURES**

| FIGURE 1: TYPICAL STS-12C/STM-4-4C ATM (UTOPIA LEVEL 2) SWITCH PORT APPLICATION | 11    |

|---------------------------------------------------------------------------------|-------|

| FIGURE 2: TYPICAL STS-12C/STM-4-4C ATM (UTOPIA LEVEL 3) SWITCH PORT APPLICATION | 11    |

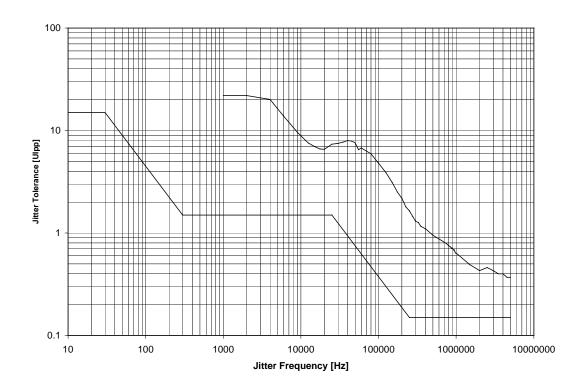

| FIGURE 3: TYPICAL STS-12C/STM-4-4C S/UNI-622-MAX JITTER TOLERANCE               | 42    |

| FIGURE 4: POINTER INTERPRETATION STATE DIAGRAM                                  | 48    |

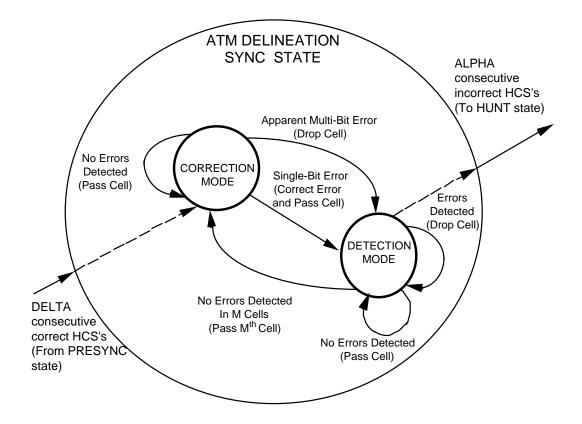

| FIGURE 5: CELL DELINEATION STATE DIAGRAM                                        | 53    |

| FIGURE 6: HCS VERIFICATION STATE DIAGRAM                                        | 55    |

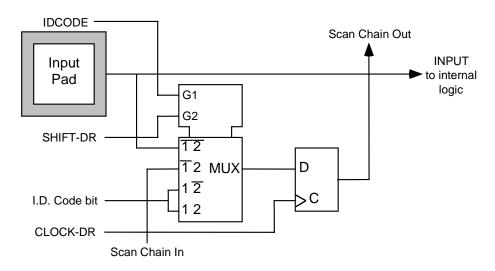

| FIGURE 7: INPUT OBSERVATION CELL (IN_CELL)                                      | . 235 |

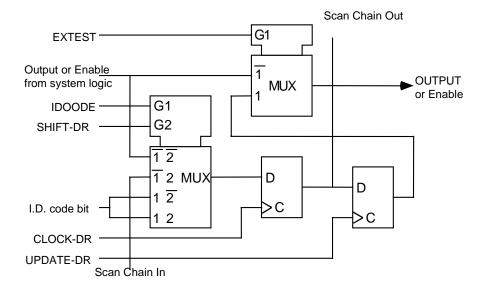

| FIGURE 8: OUTPUT CELL (OUT_CELL)                                                | . 235 |

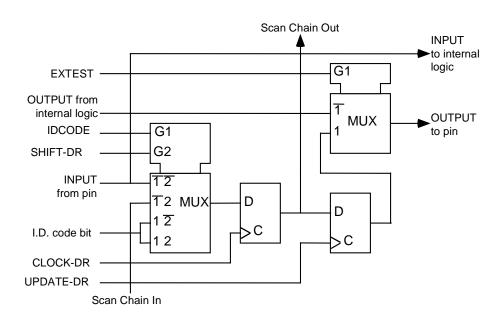

| FIGURE 9: BIDIRECTIONAL CELL (IO_CELL)                                          | . 236 |

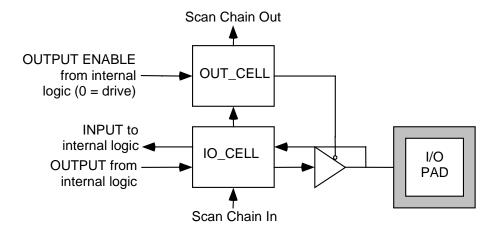

| FIGURE 10: LAYOUT OF OUTPUT ENABLE AND BIDIRECTIONAL CELLS                      | . 236 |

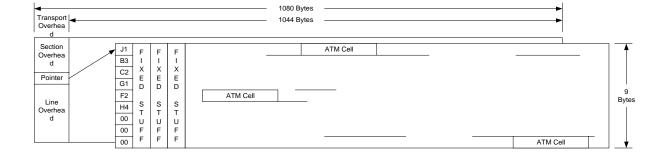

| FIGURE 11: ATM MAPPING INTO THE STS-12C/STM-4-4C SPE                            | . 237 |

| FIGURE 12: STS-12C/STM-4-4C OVERHEAD                                            | . 238 |

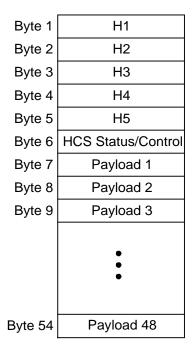

| FIGURE 13: 16-BIT WIDE, 27 WORD ATM CELL STRUCTURE                              | . 242 |

| FIGURE 14: 8-BIT WIDE, 54 BYTE ATM CELL STRUCTURE                               | . 243 |

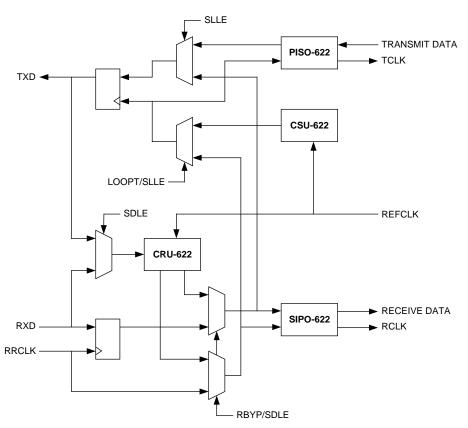

| FIGURE 15: CLOCKING STRUCTURE                                                   | . 247 |

| FIGURE 16: LINE LOOPBACK MODE                                                   | . 249 |

| FIGURE 17: SERIAL DIAGNOSTIC LOOPBACK MODE                                      | . 250 |

| FIGURE 18: PARALLEL DIAGNOSTIC LOOPBACK MODE                                    | . 250 |

| FIGURE 19: PATH DIAGNOSTIC LOOPBACK MODE                                        | . 251 |

| FIGURE 20: DATA DIAGNOSTIC LOOPBACK MODE                                        | . 251 |

| FIGURE 21: 1+1 APS ARCHITECTURE                                                 | . 252 |

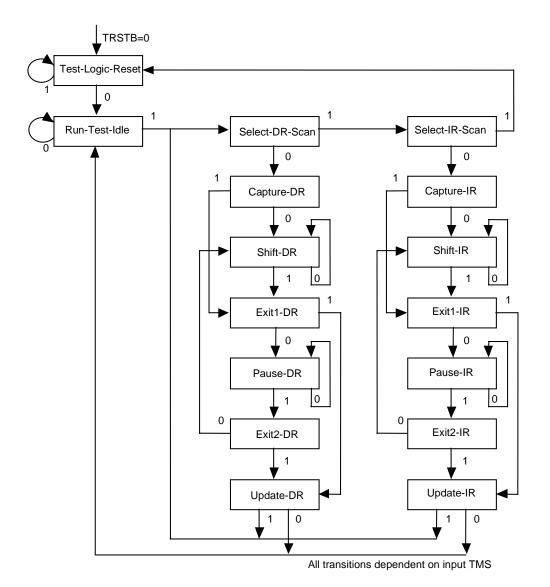

| FIGURE 22: BOUNDARY SCAN ARCHITECTURE                                           | . 254 |

| FIGURE 23: TAP CONTROLLER FINITE STATE MACHINE                                  | . 255 |

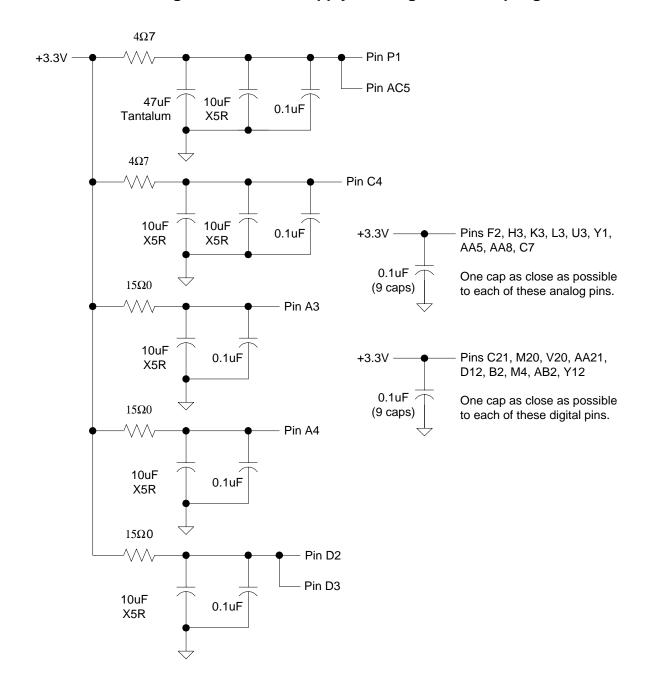

| FIGURE 24: POWER SUPPLY FILTERING AND DECOUPLING                                | . 261 |

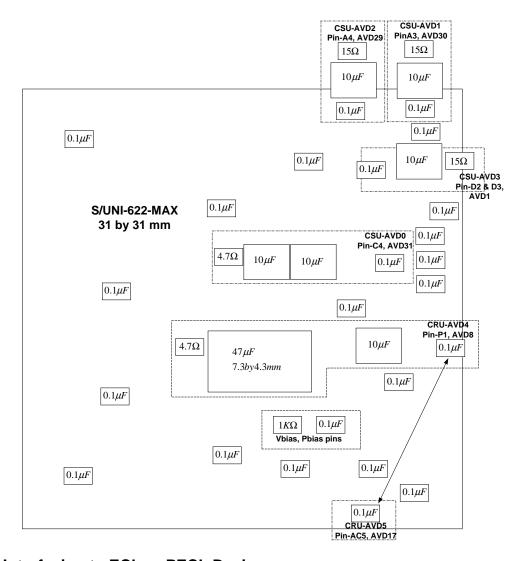

| FIGURE 25: POWER SUPPLY COMPONENT LAYOUT                                        | . 262 |

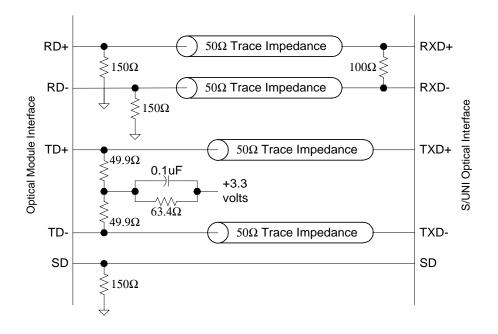

| FIGURE 26: INTERFACING S/UNI-622-MAX PECL PINS TO 3.3V DEVICES                  | . 263 |

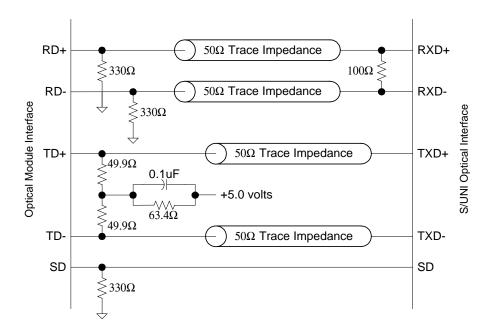

| FIGURE 27: INTERFACING S/UNI-622-MAX PECL PINS TO 5.0V DEVICES                  | . 264 |

| FIGURE 28: IN FRAME DECLARATION TIMING                                          | . 267 |

| FIGURE 29: OUT OF FRAME DECLARATION TIMING                                      | . 268 |

| FIGURE 30: PARALLEL TRANSMIT INTERFACE TIMING                                   | . 268 |

| FIGURE 31: T | RANSMIT UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING          | 269 |

|--------------|---------------------------------------------------------|-----|

| FIGURE 32: R | RECEIVE UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING          | 269 |

| FIGURE 33: T | RANSMIT UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING          | 270 |

| FIGURE 34: R | RECEIVE UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING          | 271 |

| FIGURE 35: N | MICROPROCESSOR INTERFACE READ TIMING                    | 276 |

| FIGURE 36: N | MICROPROCESSOR INTERFACE WRITE TIMING                   | 278 |

| FIGURE 37: F | RSTB TIMING DIAGRAM                                     | 280 |

| FIGURE 38: T | FRANSMIT PARALLEL LINE INTERFACE TIMING DIAGRAM         | 281 |

| FIGURE 39: F | RECEIVE PARALLEL LINE INTERFACE TIMING DIAGRAM          | 282 |

| FIGURE 40: F | RECEIVE SERIAL LINE INTERFACE TIMING DIAGRAM            | 283 |

| FIGURE 41: T | FRANSMIT UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING DIAGRAM | 285 |

| FIGURE 42: F | RECEIVE UTOPIA LEVEL 2 SYSTEM INTERFACE TIMING DIAGRAM  | 287 |

| FIGURE 43: T | FRANSMIT UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING DIAGRAM | 289 |

| FIGURE 44: F | RECEIVE UTOPIA LEVEL 3 SYSTEM INTERFACE TIMING DIAGRAM  | 290 |

| FIGURE 45: ( | CLOCK AND FRAME PULSE INTERFACE TIMING                  | 291 |

| FIGURE 46: J | JTAG PORT INTERFACE TIMING                              | 292 |

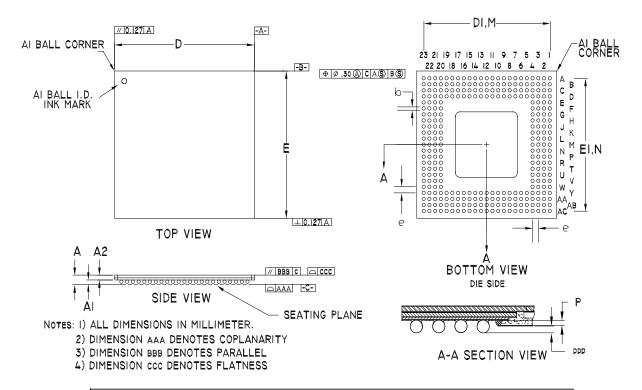

| FIGURE 47: N | MECHANICAL DRAWING 304 PIN SUPER BALL GRID ARRAY (SBGA) | 295 |

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

#### **1 FEATURES**

#### 1.1 General

- Single chip ATM over SONET/SDH Physical Layer Device operating at 622.08 Mbit/s.

- Implements the ATM Forum User Network Interface Specification and the ATM physical layer for Broadband ISDN according to CCITT Recommendation I.432.

- Processes duplex bit-serial 622.08 Mbit/s STS-12c/STM-4-4c data streams with on-chip clock and data recovery and clock synthesis.

- Supports a duplex byte-serial 77.76 Mbyte/s STS-12c/STM-4-4c line side interface for use in applications where by-passing clock recovery, clock synthesis, and serializer-deserializer functionality is desired.

- Supports a byte-serial 19.44 Mbyte/s STS-3c/STM-1 line side interface on the transmit and/or receive interface for use in applications where a 155.52 Mbit/s data rate is desired.

- Supports clock recovery by-pass for use in applications where external clock recovery is desired.

- Provides UTOPIA Level 2 16-bit wide System Interface (clocked up to 50 MHz) with parity support for ATM applications.

- Provides UTOPIA Level 3 compatible 8-bit wide System Interface (clocked up to 100 MHz) with parity support for ATM applications.

- Provides support functions for a two chip solution for 1+1 APS operation.

- Provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

- Provides a generic 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power 3.3V CMOS with TTL compatible digital inputs and CMOS/TTL digital outputs. PECL inputs and outputs are 3.3V and 5V compatible.

- Industrial temperature range (-40°C to +85°C).

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

304 pin Super BGA package.

#### 1.2 The SONET Receiver

- Provides a serial interface at 622.08 Mbit/s with clock and data recovery.

- Frames to and de-scrambles the received STS-12c/STM-4-4c stream.

- Optionally frames to and de-scrambles a received STS-3c/STM-1 stream.

- Interprets the received payload pointer (H1, H2) and extracts the STS-12c/STM-4-4c or STS-3c/STM-1 synchronous payload envelope and path overhead.

- Filters and captures the automatic protection switch channel (APS) bytes in readable registers and detects APS byte failure.

- Captures and de-bounces the synchronization status (S1) nibble in a readable register.

- Detects signal degrade (SD) and signal fail (SF) threshold crossing alarms based on received B2 errors.

- Extracts the 16-byte or 64-byte section trace (J0/Z0) sequence and the 16-byte or 64-byte path trace (J1) sequence into internal register banks.

- Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line alarm indication signal (AIS-L), line remote defect indication (RDI-L), loss of pointer (LOP), path alarm indication signal (AIS-P), path remote defect indication (RDI-P), path extended remote defect indicator (extended RDI-P).

- Counts received section BIP-8 (B1) errors, received line BIP-96 (B2) errors, line remote error indicates (REI-L), received path BIP-8 (B3) errors and path remote error indications (REI-P) for performance monitoring purposes.

#### 1.3 The Receive ATM Processor

- Extracts ATM cells from the received STS-12c/STM-4-4c or STS-3c/STM-1 payload using ATM cell delineation.

- Provides ATM cell payload de-scrambling.

- Performs header check sequence (HCS) error detection and correction, and idle/unassigned cell filtering.

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

- Detects out of cell Delineation (OCD) and loss of cell delineation (LCD) alarms.

- Counts number of received cells, idle cells, errored cells and dropped cells.

- Provides a UTOPIA Level 2 compliant 16-bit wide datapath interface (clocked up to 50 MHz) with parity support to read extracted cells from an internal four-cell FIFO buffer.

- Provides a UTOPIA Level 3 compatible 8-bit wide datapath interface (clocked up to 100 MHz) with parity support to read extracted cells from an internal four-cell FIFO buffer.

#### 1.4 The SONET Transmitter

- Synthesizes the 622.08 MHz transmit clock from a 77.76 MHz reference.

- Provides a differential PECL bit-serial interface at 622.08 Mbit/s.

- Inserts a register programmable path signal label (C2).

- Generates the transmit payload pointer (H1, H2) and inserts the path overhead.

- Optionally inserts the 16-byte or 64-byte section trace (J0/Z0) sequence and the 16-byte or 64-byte path trace (J1) sequence from internal register banks.

- Optionally inserts externally generated data communication channels (D1-D3, D4-D12) via a 192 kbit/s (D1-D3) serial stream and a 576 kbit/s (D4-D12) serial stream.

- Scrambles the transmitted STS-12c/STM-4-4c or STS-3c/STM-1 stream and inserts the framing bytes (A1, A2).

- Optionally inserts register programmable APS bytes.

- Provides a byte-serial transmit path data stream allowing two devices to implement 1+1 APS.

- Inserts path BIP-8 codes (B3), path remote error indications (REI-P), line BIP-96 codes (B2), line remote error indications (REI-L), and section BIP-8 codes (B1) to allow performance monitoring at the far end.

- Allows forced insertion of all-zeros data (after scrambling) and the corruption of the section, line, or path BIP-8 codes for diagnostic purposes.

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

Inserts ATM cells into the transmitted STS-12c/STM-4-4c or STS-3c/STM-1 payload.

#### 1.5 The Transmit ATM Processor

- Provides idle/unassigned cell insertion.

- Provides HCS generation/insertion, and ATM cell payload scrambling.

- Counts number of transmitted and idle cells.

- Provides a UTOPIA Level 2 compliant 16-bit wide datapath interface (clocked up to 50 MHz) with parity support for writing cells into an internal four-cell FIFO.

- Provides a UTOPIA Level 3 compatible 8-bit wide datapath interface (clocked up to 100 MHz) with parity support for writing cells into an internal four-cell FIFO.

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

# **2 APPLICATIONS**

- WAN and Edge ATM switches.

- LAN switches and hubs.

- Routers and Layer 3 Switches

- Network Interface Cards and Uplinks

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

#### 3 REFERENCES

- ATM Forum ATM User-Network Interface Specification, V3.1, October, 1995.

- ATM Forum "UTOPIA, An ATM PHY Interface Specification, Level 2, Version 1", June, 1995.

- Bell Communications Research GR-253-CORE "SONET Transport Systems: Common Generic Criteria", Issue 2, December 1995.

- Bell Communications Research GR-436-CORE "Digital Network Synchronization Plan", Issue 1 Revision 1, June 1996..

- ETS 300 417-1-1, "Generic Functional Requirements for Synchronous Digital Hierarchy (SDH) Equipment", January, 1996.

- ITU-T Recommendation G.703 "Physical/Electrical Characteristics of Hierarchical Digital Interfaces", 1991.

- ITU-T Recommendation G.704 "General Aspects of Digital Transmission Systems; Terminal Equipment Synchronous Frame Structures Used At 1544, 6312, 2048, 8488 and 44 736 kbit/s Hierarchical Levels", July, 1995.

- ITU, Recommendation G.707 "Network Node Interface For The Synchronous Digital Hierarchy", 1996.

- ITU Recommendation G781, "Structure of Recommendations on Equipment for the Synchronous Design Hierarchy (SDH)", January 1994.

- ITU, Recommendation G.783 "Characteristics of Synchronous Digital Hierarchy (SDH) Equipment Functional Blocks", 1996.

- ITU Recommendation I.432, "ISDN User Network Interfaces", March 93.

SATURN USER NETWORK INTERFACE (622-MAX)

# **DEFINITIONS**

The following table defines the abbreviations for the S/UNI-622-MAX.

| AIS  | Alarm Indication Signal                 |

|------|-----------------------------------------|

| APS  | Automatic Protection Switching          |

| ASSP | Application Specific Standard Product   |

| ATM  | Asynchronous Transfer Mode              |

| BER  | Bit Error Rate                          |

| BIP  | Byte Interleaved Parity                 |

| CBI  | Common Bus Interface                    |

| CMOS | Complementary Metal Oxide Semiconductor |

| CRC  | Cyclic Redundancy Check                 |

| CRSI | CRU and Serial-In Parallel-Out          |

| CRU  | Clock Recovery Unit                     |

| CSPI | CSU and Parallel-In Serial-Out          |

| CSU  | Clock Synthesis Unit                    |

| ECL  | Emitter Controlled Logic                |

| ERDI | Enhanced Remote Defect Indication       |

| ESD  | Electrostatic Discharge                 |

| FEBE | Far-End Block Error                     |

| FIFO | First-In First-Out                      |

| GFC  | Generic Flow Control                    |

| HCS  | Header Check Sequence                   |

| LAN  | Local Area Network                      |

| LCD  | Loss of Cell Delineation                |

| LOF  | Loss of Frame                           |

| LOH  | Line Overhead                           |

| LOP  | Loss of Pointer                         |

| LOS  | Loss of Signal                          |

| LOT   | Loss of Transition                                           |

|-------|--------------------------------------------------------------|

| _     |                                                              |

| NC    | No Connect, indicates an unused pin                          |

| NDF   | New Data Flag                                                |

| NNI   | Network-Network Interface                                    |

| ODL   | Optical Data Link                                            |

| OOF   | Out of Frame                                                 |

| PECL  | Pseudo-ECL                                                   |

| PLL   | Phase-Locked Loop                                            |

| PSL   | Path Signal Label                                            |

| PSLM  | Path Signal Label Mismatch                                   |

| RASE  | Receive APS, Synchronization Extractor and Bit Error Monitor |

| RDI   | Remote Defect Indication                                     |

| RLOP  | Receive Line Overhead Processor                              |

| RPOP  | Receive Path Overhead Processor                              |

| RSOP  | Receive Section Overhead Processor                           |

| RXCP  | Receive ATM Cell Processor                                   |

| SBGA  | Super Ball Grid Array                                        |

| SD    | Signal Degrade (alarm), Signal Detect (pin)                  |

| SDH   | Synchronous Digital Hierarchy                                |

| SF    | Signal Fail                                                  |

| SOH   | Section Overhead                                             |

| SONET | Synchronous Optical Network                                  |

| SPE   | Synchronous Payload Envelope                                 |

| TLOP  | Transmit Line Overhead Processor                             |

| TOH   | Transport Overhead                                           |

| TPOP  | Transmit Path Overhead Processor                             |

| TSOP  | Transmit Section Overhead Processor                          |

| TXCP  | Transmit ATM Cell Processor                                  |

| UI    | Unit Interval                                                |

|       |                                                              |

| UNI | User-Network Interface       |

|-----|------------------------------|

| VCI | Virtual Connection Indicator |

| VPI | Virtual Path Indicator       |

| WAN | Wide Area Network            |

| XOR | Exclusive OR logic operator  |

SATURN USER NETWORK INTERFACE (622-MAX)

#### **5 APPLICATION EXAMPLES**

The PM5357 S/UNI-622-MAX is applicable to equipment implementing Asynchronous Transfer Mode (ATM) User-Network Interfaces (UNI) and ATM Network-Network Interfaces (NNI).

The S/UNI-622-MAX may find application at either end of switch-to-switch links or switch-to-terminal links, both in public network (WAN) and private network (LAN) situations. The S/UNI-622-MAX performs the mapping of ATM cells into the SONET/SDH STS-12c/STM-4-4c synchronous payload envelope (SPE) and processes applicable SONET/SDH section, line and path overheads.

In a typical STS-12c/STM-4-4c ATM application, the S/UNI-622-MAX performs clock and data recovery in the receive direction and clock synthesis in the transmit direction of the line interface. The S/UNI-622-MAX can also be configured to by-pass the clock recovery, clock synthesis, and serializer/deserializer functions. In this mode, an external clock and data recovery/serial-to-parallel converter device is required in the receive direction, and an external serial-to-parallel converter/clock synthesis device is required in the transmit direction.

On the system side, the S/UNI-622-MAX interfaces directly with ATM layer processors and switching or adaptation functions using a UTOPIA Level 2 compliant 16-bit (clocked up to 50 MHz) or an UTOPIA Level 3 8-bit (clocked up to 100 MHz) synchronous FIFO style interface.

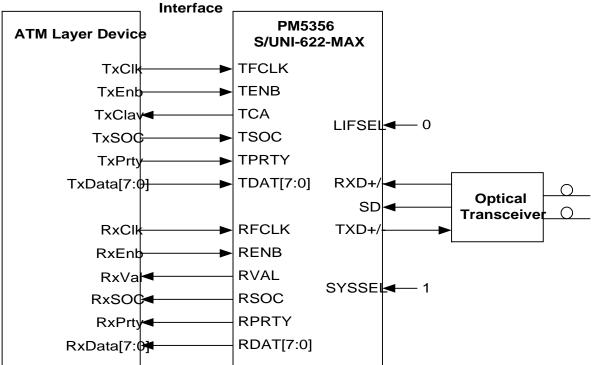

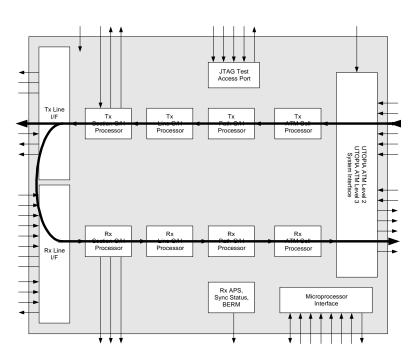

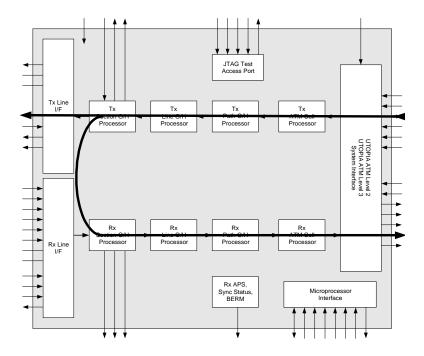

An application with a UTOPIA Level 2 system side interface is shown in Figure 1. An application with a UTOPIA Level 3 system side is shown in Figure 2. The initial configuration and ongoing control and monitoring of the S/UNI-622-MAX are normally provided via a generic microprocessor interface.

SATURN USER NETWORK INTERFACE (622-MAX)

Figure 1: Typical STS-12c/STM-4-4c ATM (UTOPIA Level 2) Switch Port Application

#### **UTOPIA Level 2** Interface PM5356 **ATM Layer Device** S/UNI-622-MAX **TFCLK TxClk TENB** TxEnb **TCA** TxClav LIFSEL □ 0 **TSOC** TxSOC **TPRTY** TxPrty TxData[15:0] TDAT[15:0] RXD+/ Optical SD Transceive **RFCLK** TXD+/ **RxClk RENB** RxEnb **RCA** RxClav SYSSEI<u></u> ■ 0 **RSOC** RxSOC RxPrty-**RPRTY** RDAT[15:0] RxData[15:0 Fig

ure 2: Typical STS-12c/STM-4-4c ATM (UTOPIA Level 3) Switch Port Application

SATURN USER NETWORK INTERFACE (622-MAX)

# UTOPIA Level 3

PMC-1980589

ISSUE 6

# **BLOCK DIAGRAM**

စ

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

#### **7 DESCRIPTION**

The PM5357 S/UNI-622-MAX SATURN User Network Interface is a monolithic integrated circuit that implements SONET/SDH processing, ATM mapping over SONET/SDH mapping functions at the STS-12c/STM-4-4c 622.08 Mbit/s rate.

The S/UNI-622-MAX receives SONET/SDH streams using a bit serial interface, recovers the clock and data and processes section, line, and path overhead. The S/UNI-622-MAX can also be configured for clock and data recovery and clock synthesis by-pass where it receives SONET/SDH frames via a byte-serial interface. The S/UNI-622-MAX performs framing (A1, A2), de-scrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level for performance monitoring purposes. Line and path remote error indications (M1, G1) are also accumulated. The S/UNI-622-MAX interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell payload.

When used to implement an ATM UNI or NNI, the S/UNI-622-MAX frames to the ATM payload using cell delineation. HCS error correction is provided. Idle/unassigned cells may be optionally dropped. Cells are also dropped upon detection of an uncorrectable header check sequence error. The ATM cell payloads are descrambled and are written to a four-cell FIFO buffer. The received cells are read from the FIFO using a 16-bit wide UTOPIA Level 2 (clocked up to 50 MHz) or an 8-bit wide UTOPIA Level 3 (clocked up to 100 MHz) datapath interface. Counts of received ATM cell headers that are errored and uncorrectable and those that are errored and correctable are accumulated independently for performance monitoring purposes.

The S/UNI-622-MAX transmits SONET/SDH streams using a bit serial interface. The S/UNI-622-MAX can also be configured for clock and data recovery and clock synthesis by-pass where it transmits the SONET/SDH frames via a byte-serial interface. The S/UNI-622-MAX synthesizes the transmit clock from a 77.76MHz frequency reference and performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section, line, and path bit interleaved parity codes (B1, B2, B3) as required to allow performance monitoring at the far end. Line and path remote error indications (M1, G1) are also inserted. The S/UNI-622-MAX also supports the insertion of a large variety of errors into the transmit stream, such as framing pattern errors, bit interleaved parity errors, and illegal pointers, which are useful for system diagnostics and tester applications.

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

When used to implement an ATM UNI or NNI, ATM cells are written to an internal four cell FIFO using a 16-bit wide UTOPIA Level 2 (clocked up to 50 MHz) or an 8-bit wide UTOPIA Level 3 (clocked up to 100 MHz) datapath interface. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one complete cell. The S/UNI-622-MAX provides generation of the header check sequence and scrambles the payload of the ATM cells. Each of these transmit ATM cell processing functions can be enabled or bypassed.

No line rate clocks are required directly by the S/UNI-622-MAX as it synthesizes the transmit clock and recovers the receive clock using a 77.76 MHz reference clock. The S/UNI-622-MAX outputs a differential PECL line data (TXD+/-).

The S/UNI-622-MAX is configured, controlled and monitored via a generic 8-bit microprocessor bus interface. The S/UNI-622-MAX also provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

The S/UNI-622-MAX is implemented in low power, +3.3 Volt, CMOS technology. It has TTL compatible digital inputs and TTL/CMOS compatible digital outputs. High speed inputs and outputs support 3.3V and 5.0V compatible pseudo-ECL (PECL). The S/UNI-622-MAX is packaged in a 304 pin SBGA package.

SATURN USER NETWORK INTERFACE (622-MAX)

## **8 PIN DIAGRAM**

The S/UNI-622-MAX is available in a 304 pin SBGA package having a body size of 31 mm by 31 mm and a ball pitch of 1.27 mm.

|    | 23           | 22            | 21      | 2.0          | 19    | 18     | 17     | 1.6   | 15        | 14    | 13      | 12     | 11    | 10     | 9      |        | 7        | 6       | 5       | 4      | 3       | 2         | 1        |       |

|----|--------------|---------------|---------|--------------|-------|--------|--------|-------|-----------|-------|---------|--------|-------|--------|--------|--------|----------|---------|---------|--------|---------|-----------|----------|-------|

| A  | YDD          | YES           | TFF     | TFFO         | Artiq | YES    | ngq    | HEE   | ORI       | ARI   | AM      | Y65    | 198   | ALE    | TEK    | YES    | watni    | HSS     | veital  | avagaq | water   | Y65       | 400      | A     |

| 8  | 100          | V00           | V96     | м            | TOLK  | AP1021 | 094    | 004   | 068       | ANI   | AN      | A(7)   | noe   | пого   | 39670  | NO     | AVSEIG   | AVOLUTI | AHOSHS  | AMERI  | 458     | V00       | V90      | В     |

| с  | UF183.       | 799           | 100     | мс           | rec . | APROT  | APS(E) | 1921  | 0(1)      | N/10  | API     | 491    | CSID  | TDI    | TDO    | NC     | AVERA    | wated   | Ampri   | AVERT  | Y00     | 700       | Arsen    | с     |

| D  | NC.          | PECLI         | VIII    | VEE          | ruc . | 400    | APIEZ  | NC.   | VOID      | opt   | API     | VOID   | ARI   | TME    | VDD    | weps   | AVIDEO . | YEE     | vertosi | HOD    | MORI    | wen       | dwalid   | D     |

| E  | TOATUS       | rec .         | neur    | Apmote       |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | APROL  | ONVOIR  | ATPIN     | NC       | E     |

| F  | 196          | TOAT(11)      | тритун  | V00          |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | 100    | ATP[1]  | APDIQ     | V99      | Р     |

| G  | толти        | TOAT[10]      | тактра  | TOATUS       |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | NE     | AVIET   | wated     | ANIE     | G     |

| и  | 1155         | токгра        | TEATIF  | TOATH        |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | AMER   | ANDES   | AVIDE     | VSS      | н     |

| J  | TOATUS       | токли         | TDATIS  | V00          |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | 100    | AVS(7)  | AHON      | AMOUN    | ,     |

| ĸ  | MC .         | токлуп        | TEATIN  | TOATU        |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | AVERT  | MON     | TOPEF1    | TEMEFI   | к     |

| ı  | TEA.         | 1038          | TROC    | TENTY        |       |        |        |       |           |       |         | 622    |       |        |        |        |          |         |         | watel  | AND(T)  | TID:      | TIE.     | 1     |

| ж  | 100          | TFOLK         | WOK     | V00          |       |        |        |       |           | -     | SUNT    | -622   | -MA   |        |        |        |          |         |         | 100    | AVSENS  | PRINCES   | V90      | н     |

| и  | PENE         | PRC .         | RVAL    | RCA.         |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | жире   | AVSETS  | Arrect    | F/9010   | н     |

| r  | PROC         | PMC .         | PERT    | RDAT<br>(75) |       |        |        |       |           |       | BOTT    | OM 1   | VIEW  |        |        |        |          |         |         | dvatel | MC.     | PAC       | wasii    | p.    |

| 2  | PEAT<br>(14) | MEJAT<br>[13] | TNON    | YEE          |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | HOD    | POASES  | 5D        | gAVO(1)  | В     |

| т  | 196          | MOAT          | HOAT    | PENTIN       |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | AVD(N  | AVS[16] | Arragrass | V99      | т     |

| u  | PEATIN       | MINTEL        |         | PERTIN       |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | entiti | AVG[10] | PRESENT   | PRICLE:  | u u   |

| 7  | 1155         | MOVATAL       | MONTE   | YDD          |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | HOD    | Penago  | mo.       | VES      | ,     |

| w  | POAT[2]      | ROAT(1)       | noA7(s) | VEHICLE      |       |        |        |       |           |       |         |        |       |        |        |        |          |         |         | AVIONS | AVG(12) | POWORK    | nio-     | ų.    |

| 7  | MC .         | PIC           | NC      | YEE          | ruc . | 400    | MC     | PROFI | 400       | PTOX  | POUTES  | YDO    | NC    | AVERES | VDO    | APROST | AVIDE    | YDD     | ARREST  | HOD    |         |           | AMOUNT   | ų     |

| ** | D/SUB.       | VEE           | 100     | uc           | PALPM | DDF    | PMII   | PREZI | magn      | POSTO | POUT(1) | POLITY | NC    | AVIEN  | wahii  | AVDDIE | AVERTHE  | AVIEG   | AHDENE  | AVERGE |         | WEE       | PREPELIE | **    |

| 18 | 105          | V90           | V96     | 10           | NTO   | PAGE   | 7761   | PHED  |           |       | POUTE   |        | NO    |        | AVSEN  |        |          |         |         |        |         | V00       | V90      | 18    |

|    | V00          | 700           | MC MC   | RCLE         | PCLE  | V89    | MC MC  | 199   |           |       | POUTES  |        | NC NC |        |        |        | AVIET    |         |         |        | AVG(14) |           | 100      | AC AC |

| AC | 23           | 22            | 21      | 20           | 19    | 10     | 17     | 16    | 25 People | 14    | 13      | 12     | 11    | 10     | MO(21) | 1      | 7        | 6       | 5       | 4      | 3       | 2         | 1        | ***   |

|    | 2.7          | 2.5           |         | 2.0          | 4.0   | 4.00   | 40.0   |       | 4.0       | 4.4   | 2.0     |        | 4.4   | 4.50   |        | -      |          | 100     |         | -      | 100     | -         | -        |       |

SATURN USER NETWORK INTERFACE (622-MAX)

# 9 PIN DESCRIPTION

## 9.1 Serial Line Side Interface Signals

| Pin Name           | Туре                          | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                  |

|--------------------|-------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBYP               | Input                         | E21        | The receive bypass (RBYP) input disables clock recovery. If RBYP is high, RXD+/- is sampled on the rising edge of RRCLK+/ If RBYP is low, the receive clock is recovered from the RXD+/- bit stream.                                                                                                                                      |

|                    |                               |            | Please refer to the Operation section for a discussion of the operating modes.                                                                                                                                                                                                                                                            |

| PECLV              | Input                         | D22        | The PECL signal voltage select (PELCV) selects between 3.3V PECL signaling and 5V PECL signaling for the PECL inputs. When PECLV is low, the PECL inputs expect a 5V PECL signal. When PECLV is high, the PECL inputs expect a 3.3V PECL signal. The PECL biasing pins PBIAS should be set to the appropriate voltage to prevent latchup. |

|                    |                               |            | Please refer to the Operation section for a discussion of PECL interfacing issues.                                                                                                                                                                                                                                                        |

| REFCLK+<br>REFCLK- | Differential<br>PECL<br>Input | Y2<br>AA1  | The differential reference clock inputs (REFCLK+/-) provides a jitter-free 77.76 MHz reference clock for both the clock recovery and the clock synthesis circuits. REFCLK+/- is not required if the clock recovery and clock synthesis features are not used.                                                                             |

|                    |                               |            | Please refer to the Operation section for a discussion of PECL interfacing issues and reference clocks.                                                                                                                                                                                                                                   |

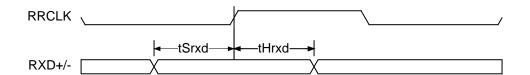

| RXD+<br>RXD-       | Differential<br>PECL<br>Input | W1<br>V2   | The receive differential data PECL inputs (RXD+/-) contain the NRZ bit serial receive stream. The receive clock is recovered from the RXD+/- bit stream when RBYP is set low. RXD+/- is sampled on the rising edge of RRCLK+/- when RBYP is set high.                                                                                     |

|                    |                               |            | Please refer to the Operation section for a discussion of PECL interfacing issues.                                                                                                                                                                                                                                                        |

| Pin Name         | Туре                           | Pin<br>No. | Function                                                                                                                                                                                                                                                                      |

|------------------|--------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRCLK+<br>RRCLK- | Differential<br>PECL<br>Input  | U1<br>U2   | When clock recovery is bypassed (RBYP set high), RRCLK+/- is nominally a 622.08 MHz 50% duty cycle clock and provides timing for the S/UNI-622-MAX receive functions. In this case, RXD+/- is sampled on the rising edge of RRCLK+/ RRCLK+/- is ignored when RBYP is set low. |

|                  |                                |            | Please refer to the Operation section for a discussion of PECL interfacing issues.                                                                                                                                                                                            |

| SD               | PECL<br>Input                  | R2         | The receive signal detect PECL input (SD) indicates the presence of valid receive signal power from the Optical Physical Medium Dependent Device. A PECL logic high indicates the presence of valid data. A PECL logic low indicates a loss of signal.                        |

|                  |                                |            | Please refer to the Operation section for a discussion of PECL interfacing issues                                                                                                                                                                                             |

| TXD+<br>TXD-     | Differential<br>PECL<br>Output | L2<br>L1   | The transmit differential data PECL outputs (TXD+/-) contain the 622.08 Mbit/s transmit stream. The TXD+/- outputs are driven using the synthesized clock from the CSU-622.                                                                                                   |

|                  |                                |            | Please refer to the Operation section for a discussion of PECL interfacing issues.                                                                                                                                                                                            |

SATURN USER NETWORK INTERFACE (622-MAX)

# 9.2 Parallel Line Side Interface Signals - CRU and CSU Bypass

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                 |

|----------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIFSEL   | Input  | C23        | The line interface select (LIFSEL) selects between serial and parallel line interface modes of operation.                                                                                                                                                                                |

|          |        |            | When tied high, the parallel mode is selected by-<br>passing the clock and data recovery, clock synthesis<br>and the serializer/de-serializer functions.                                                                                                                                 |

|          |        |            | When tied low, serial mode is selected, enabling clock and data recovery, clock synthesis and the serializer/de-serializer functions. During this operation, the parallel interface may be used for 1+1 APS operation. See the Operation section for more discussion of 1+1 APS support. |

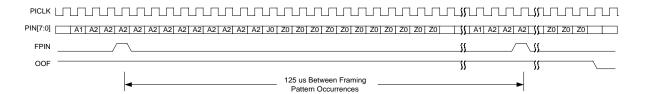

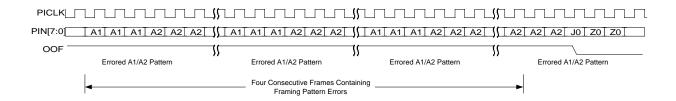

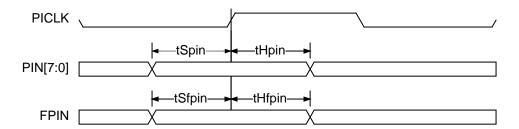

| PICLK    | Input  | AC19       | The parallel input clock (PICLK) provides timing for S/UNI-622-MAX receive function operation when the device is configured for the parallel interface mode of operation.                                                                                                                |

|          |        |            | When the RSOC3 bit is set high, PICLK is a 19.44 MHz nominally 50% duty cycle clock. When the RSOC3 bit is set low, PICLK is a 77.76 MHz nominally 50% duty cycle clock.                                                                                                                 |

|          |        |            | When parallel operation is not used, PICLK may be used for 1+1 APS operation. See the Operation section for more discussion of 1+1 APS.                                                                                                                                                  |

| OOF      | Output | AA18       | The out of frame (OOF) signal is high while the S/UNI-622-MAX is out of frame. OOF is set low while the S/UNI-622-MAX is in-frame. An out of frame declaration occurs when four consecutive errored framing patterns (A1 and A2 bytes) have been received.                               |

|          |        |            | OOF is intended to enable an upstream framing pattern detector to search for the framing pattern. This alarm indication is also available via register access. OOF is an asynchronous output with a minimum period of one PICLK clock.                                                   |

| Pin Name                                                                     | Туре  | Pin<br>No.                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------------------------------------------------------|-------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPIN                                                                         | Input | AB17                                                        | The active-high framing position input (FPIN) signal indicates the SONET/SDH frame position on the PIN[7:0] bus. In parallel interface operation, the byte on the PIN[7:0] bus indicated by FPIN is the third A2 of the SONET/SDH framing pattern. FPIN is sampled on the rising edge of PICLK.                                                                                                    |

|                                                                              |       |                                                             | When parallel interface operation is not used, FPIN may be used for 1+1 APS operation. In this mode, FPIN marks the first synchronous payload envelope byte after the J0/Z0 bytes on PIN[7:0]. See the Operation section for more discussion of 1+1 APS.                                                                                                                                           |

| PIN[0]<br>PIN[1]<br>PIN[2]<br>PIN[3]<br>PIN[4]<br>PIN[5]<br>PIN[6]<br>PIN[7] | Input | AB18<br>AA17<br>AB16<br>AA16<br>Y16<br>AC15<br>AB15<br>AA15 | In parallel interface operation, the data input (PIN[7:0]) bus carries the byte-serial STS-12c/STM-4-4c or STS-3c/STM-1 stream. PIN[7] is the most significant bit (corresponding to bit 1 of each serial byte, the first bit received). PIN[0] is the least significant bit (corresponding to bit 8 of each serial byte, the last bit received). PIN[7:0] is sampled on the rising edge of PICLK. |

|                                                                              |       |                                                             | When parallel interface operation is not used, PIN[7:0] may be used for 1+1 APS operation. In this mode, PIN[7:0] carries the byte-serial STS-12c/STM-4-4c transmit path. See the Operation section for more discussion of 1+1 APS.                                                                                                                                                                |

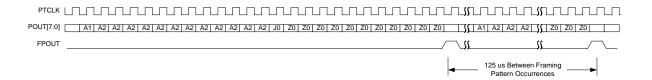

| PTCLK                                                                        | Input | Y14                                                         | The parallel transmit clock (PTCLK) provides timing for S/UNI-622-MAX transmit function operation when the device is configured for the parallel interface mode of operation.                                                                                                                                                                                                                      |

|                                                                              |       |                                                             | When TOC3 is low, PTCLK should be a 77.76 MHz nominally 50% duty cycle clock free-running (non gapped) clock. When TOC3 is high, PTCLK should be a 19.44 MHz nominally 50% duty cycle clock.                                                                                                                                                                                                       |

| Pin Name                                                                             | Туре   | Pin<br>No.                                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------------------------------------------------------------------|--------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FPOUT                                                                                | Output | AC14                                                        | In parallel interface operation, the parallel outgoing stream frame pulse (FPOUT) marks the frame alignment on the POUT[7:0] bus. FPOUT marks the first synchronous payload envelope byte after the J0/Z0 bytes. FPOUT is updated on the rising edge of PTCLK.                                                                                                                                                                              |

|                                                                                      |        |                                                             | When parallel interface operation is not used, FPOUT may be used for 1+1 APS operation. In this mode, FPOUT marks the first synchronous payload envelope byte after the J0/Z0 bytes. FPOUT is updated on the rising edge of TCLK. See the Operation section for more discussion of 1+1 APS.                                                                                                                                                 |

| POUT[0]<br>POUT[1]<br>POUT[2]<br>POUT[3]<br>POUT[4]<br>POUT[5]<br>POUT[6]<br>POUT[7] | Output | AA14<br>AB14<br>AC13<br>AB13<br>AA13<br>Y13<br>AB12<br>AA12 | In parallel interface operation, the parallel outgoing stream, (POUT[7:0]) carries the scrambled STS-12c/STM-4-4c or STS-3c/STM-1 stream in byte-serial format. POUT[7] is the most significant bit (corresponding to bit 1 of each serial word, the first bit transmitted). POUT[0] is the least significant bit (corresponding to bit 8 of each serial word, the last bit transmitted). POUT[7:0] is updated on the rising edge of PTCLK. |

|                                                                                      |        |                                                             | When parallel interface operation is not used, POUT[7:0] may be used for 1+1 APS operation. In this mode, POUT[7:0] carries the byte-serial STS-12c/STM-4-4c transmit path and updates on the rising edge of TCLK. See the Operation section for more discussion of 1+1 APS.                                                                                                                                                                |

SATURN USER NETWORK INTERFACE (622-MAX)

# 9.3 Clocks and Alarms Signals

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RCLK     | Output | AC20       | The receive clock (RCLK) provides a timing reference for the S/UNI-622-MAX receive function outputs. RCLK is a 77.76 MHz, 50% duty cycle clock.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RFPO     | Output | AB19       | The receive frame pulse output (RFPO), when the framing alignment has been found (the OOF register bit is low), is an 8 kHz signal derived from the receive clock RCLK. RFPO pulses high for one RCLK cycle every 9720 RCLK cycles (STS-12c / STM-4-4c).                                                                                                                                                                                                                                                                                                               |

|          |        |            | RFPO is updated on the rising edge of RCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RALRM    | Output | AA19       | The receive alarm (RALRM) output indicates the state of the receive framing. RALRM is low if no receive alarms are active. RALRM is optionally high if line AIS (LAIS), path AIS (PAIS), line RDI (LRDI), path RDI (PRDI), enhanced path RDI (PERDI), loss of signal (LOS), loss of frame (LOF), out of frame (OOF), loss of pointer (LOP), loss of pointer concatenation (LOPC/AISC), loss of cell delineation (LCD), signal fail BER (SFBER), signal degrade BER (SDBER), path trace identification mismatch (TIM) or path signal label mismatch (PSLM) is detected. |

| TCLK     | Output | B19        | period of one RCLK clock.  The transmit clock (TCLK) provides timing for the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TOLK     | Output | פוס        | S/UNI-622-MAX transmit function operation. TCLK is a 77.76 MHz, 50% duty cycle clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TFPO     | Output | A20        | The active-high framing position output (TFPO) signal is an 8 kHz signal derived from the transmit clock TCLK. TFPO pulses high for one TCLK cycle every 9720 TCLK cycles (STS-12c / STM-4-4c).                                                                                                                                                                                                                                                                                                                                                                        |

|          |        |            | TFPO is updated on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

RELEASED S/UNI-622-MAX DATASHEET PMC-1980589

ISSUE 6

| Pin Name                                       | Туре  | Pin<br>No.                      | Function                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------|-------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TFPI                                           | Input | A21                             | The active high framing position (TFPI) signal is an 8 kHz timing marker for the transmitter. TFPI is used to align the SONET/SDH transport frame generated by the S/UNI-622-MAX device to a system reference. TFPI should be brought high for a single TCLK period every 9720 TCLK cycles or a multiple thereof. TFPI must be tied low if such synchronization is not required. |

|                                                |       |                                 | TFPI is sampled on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                                      |

| APS[0]<br>APS[1]<br>APS[2]<br>APS[3]<br>APS[4] | I/O   | A19<br>C18<br>B18<br>D17<br>C17 | The APS Port bus (APS[4:0]) is a bi-directional control bus that can be used to implement a 1+1 APS system. When the APSPOE register bit is set low, the APS[4:0] bus is an input. Data on this bus is used by TPOP to generate the path RDI and path FEBE. When the APSOE register bit is set high, the APS[4:0] bus is an output with data generated by RPOP.                  |

|                                                |       |                                 | APS[0] FEBE Clock (576 kHz)  APS[1] FEBE Data  APS[2] RDI[0] (G1 bit 5)  APS[3] RDI[1] (G1 bit 6)  APS[4] RDI[2] (G1 bit 7)                                                                                                                                                                                                                                                      |

|                                                |       |                                 | See the Operation section for more discussion of 1+1 APS.                                                                                                                                                                                                                                                                                                                        |

ISSUE 6

SATURN USER NETWORK INTERFACE (622-MAX)

# 9.4 ATM (UTOPIA) System Interface

| Pin Name | Туре | Pin<br>No. | Function |

|----------|------|------------|----------|

|----------|------|------------|----------|

| Pin Name                                                                                                                              | Туре  | Pin<br>No.                                                                                                   | Function                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

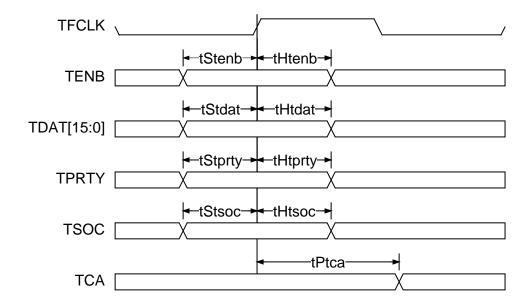

| TFCLK                                                                                                                                 | Input | M22                                                                                                          | UTOPIA transmit FIFO write clock (TFCLK) is used to write ATM cells to the four cell transmit FIFO.                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                       |       |                                                                                                              | When in 16-bit Level 2 ATM mode, TFCLK must cycle at a 50 MHz to 40 MHz instantaneous rate, and must be a free running clock (cannot be gapped).                                                                                                                                                                                                                                                                      |

|                                                                                                                                       |       |                                                                                                              | When in 8-bit Level 3 ATM mode, TFCLK must cycle at a 100 MHz to 60 MHz instantaneous rate, and must be a free running clock (cannot be gapped).                                                                                                                                                                                                                                                                      |

| TDAT[0] TDAT[1] TDAT[2] TDAT[3] TDAT[4] TDAT[5] TDAT[6] TDAT[7] TDAT[8] TDAT[9] TDAT[10] TDAT[11] TDAT[12] TDAT[13] TDAT[14] TDAT[14] | Input | K22<br>K21<br>K20<br>J23<br>J22<br>J21<br>H22<br>H21<br>H20<br>G23<br>G22<br>G21<br>G20<br>F22<br>F21<br>E23 | The UTOPIA transmit cell data (TDAT[15:0]) bus carries the ATM cell octets that are written to the transmit FIFO.  In 16-bit Level 2 ATM mode, the TDAT[15:0] is considered valid only when TENB is simultaneously asserted.  In 8-bit Level 3 ATM mode, the TDAT[7:0] bus is considered valid only when TENB is simultaneously asserted. TDAT[15:8] are ignored.  TDAT[15:0] is sampled on the rising edge of TFCLK. |

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                  |

|----------|-------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSOC     | Input | L21        | The UTOPIA transmit start of cell (TSOC) signal marks the start of a cell structure on the TDAT bus.                                                                                                                                                      |

|          |       |            | In 16-bit Level 2 ATM mode, the first word of the cell structure is present on the TDAT[15:0] bus when TSOC is high. It is not necessary for TSOC to be present for each cell.                                                                            |

|          |       |            | In 8-bit Level 3 ATM mode, the first byte of the cell structure is present on the TDAT[7:0] bus when TSOC is high. TSOC must be present for each cell.                                                                                                    |

|          |       |            | TSOC is considered valid only when TENB is simultaneously asserted. TSOC is sampled on the rising edge of TFCLK.                                                                                                                                          |

| TPRTY    | Input | L20        | The UTOPIA transmit bus parity (TPRTY) signal indicates the parity on the TDAT bus. A parity error is indicated by a status bit and a maskable interrupt. Cells with parity errors are inserted in the transmit stream, so the TPRTY input may be unused. |

|          |       |            | In 16-bit Level 2 ATM mode, the TPRTY signal indicates the parity on the TDAT[15:0] bus. Odd or even parity selection is made in the TXCP registers.                                                                                                      |