## OV7930 Color CMOS Analog CAMERACHIP<sup>TM</sup>

## **General Description**

The OV7930 (color) is a high performance quarter-inch CMOS CAMERACHIP<sup>TM</sup> designed for all applications requiring a small footprint, low voltage, low power consumption and low cost color video camera.

The device supports NTSC composite video output and can directly interface with a VCR TV monitor or other 75 ohm terminated input with 2X standard TV signal range. The OV7930 CAMERACHIPs require only a single 5-volt DC power supply and have been designed for very low power operation.

#### Features

- Single chip 1/4" lens video camera

- Composite video: NTSC

- Sensitivity boost (+27 dB)/AGC ON/OFF

- Automatic exposure/gain/white balance

- External frame sync capability

- Aperture correction

- SCCB programmable controls:

- Color saturation

- Brightness

- Hue

- White balance

- Exposure

- Gain

- Gamma curve

- Aperture correction

- Gamma correction (0.45) ON/OFF

- Low power consumption

- +5 volt only power supply

- Wide dynamic range, anti-blooming, zero smearing

## **Ordering Information**

| Product                           | Packages         |

|-----------------------------------|------------------|

| OV7930 (Color, VGA,<br>NTSC, CVO) | CLCC-28, PLCC-28 |

#### **Applications**

- Video Conferencing

- Video Phones

- Video E-mail

- PC Multimedia

- Toys

- Security

- Surveillance

- Finger Printing

- Medical and Dental Equipment

## **Key Specifications**

|   |              | Array Size             | 510 x 492                         |

|---|--------------|------------------------|-----------------------------------|

|   |              | Power Supply           | 5 VDC <u>+</u> 5%                 |

|   | Power        | Without Loading        | 20 mA                             |

|   | Requirements | With 75 ohm<br>Loading | < 35 mA                           |

|   | 7            | Image Area             | 4.00 mm x 3.08 mm                 |

| 1 | Auto Electro | nic Exposure Time      | 1/60s - 6.3µs                     |

|   | Minimum III  | umination (3000K)      | < 2.0 Lux                         |

|   |              | S/N Ratio              | > 46 dB                           |

|   |              | Dynamic Range          | > 70 dB                           |

|   |              | Pixel Size             | 7.86 µm x 6.25 µm                 |

|   |              | Dark Current           | < 100 mV/s                        |

|   | F            | ixed Pattern Noise     | < 0.03% V <sub>PEAK-TO-PEAK</sub> |

|   | Pa           | ckage Dimensions       | 0.45 in. x 0.45 in.               |

|   |              |                        |                                   |

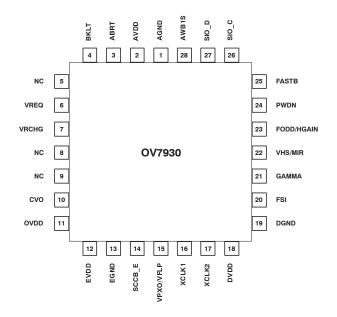

#### Figure 1 OV7930 Pin Diagram

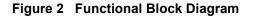

#### **Functional Description**

This section describes the various functions of the OV7930. Refer to Figure 2 for the functional block diagram of the OV7930.

#### **Video Standards**

NTSC TV standards are implemented and available as output in the OV7930 CAMERACHIP. Note that the accuracy and stability of the crystal clock frequency is important to avoid unwanted color shift in the TV video system. A 14.31818 MHz crystal is recommended when using the OV7930 CAMERACHIP.

#### **Video Format**

The OV7930 CAMERACHIP supports Composite (CVBS) video format only. Composite signals are generated from the built-in NTSC TV encoder.

#### **Image Sensor Functions**

#### White Balance

The function of white balance in the OV7930 CAMERACHIP is to adjust and calibrate the image device sensitivity on the primary (RGB) colors to match the color cast of the light source. The Auto White Balance (AWB) can be enabled or disabled by SCCB register bit COMD[1] (see "COMD" on page 12).

#### **Mirror and Vertical Flip**

The OV7930 has pin control functions:

- Mirror (pin22 see "VHS/MIR" on page 4)

- VFLIP (pin 15 input see "VPXO/VFLP" on page 4)

These two functions can be controlled separately using SCCB register bit COME[6] (see "COME" on page 12) for the mirror function and register bit COMJ[0] (see "COMJ" on page 13) for the vertical flip function.

#### **Multi-Chip Synchronize**

The OV7930 CAMERACHIP provides the multi-chip Synchronize function where one chip works as the master and all others as slave devices. The master chip provides the frame synchronize signal through the FODD pin (pin 23 - see "FODD/HGAIN" on page 5). All slave devices accept the frame synchronize signal through the FSI pin (pin 20 - see "FSI" on page 4). This mode allows all devices to synchronize together.

### **Chip Configuration**

The OV7930 CAMERACHIP has been designed for ease-of-use in many stand-alone applications. Most of the on-chip functions are configurable by connecting the appropriate pins high (logic "1") or low (logic "0") through a 10 K $\Omega$  resistor. The CAMERACHIP reads the input pins at power up which enable user-defined default configurations.

The OV7930 CAMERACHIP also has a SCCB slave interface for programmable access to all registers functions. Refer to *OmniVision Technologies Serial Camera Control Bus (SCCB) Specification* for detailed usage of the serial control port.

- **NOTE** Once the SCCB interface is enabled (pin 14 see "SCCB\_E" on page 4), the following pin assignment functions will be ignored and functions will be defined by the related SCCB register. These pins are:

- ABRT (pin 3)

- BKLT (pin 4)

- VFLIP (pin 15)

- GAMMA (pin 21)

- MIR (pin 22)

- HGAIN (pin 23)

- FASTB (pin 25)

#### **Additional Picture Controls**

The OV7930 CAMERACHIP provides additional picture control functions to enhance image quality and chip performance.

#### Automatic Gain Control (AGC)

The default gain range is 1x - 8x while the user can set the gain range up to 4x or 16x.

## **Brightness Control**

Brightness can be controlled either by internal automatic algorithms or by the user through the following SCCB register bits:

BRT[7:0] (see "BRT" on page 11)

#### **Gamma Correction**

The OV7930 has luminance and chrominance Gamma correction through the GAMMA pin (pin 21 - see "GAMMA" on page 4).

#### **Backlight Control**

The OV7930 manages backlight conditions through register bit COME[4] (see "COME" on page 12).

#### **Color Saturation**

Color saturation can be updated manually through the SCCB register bits SAT[7:4] (see "SAT" on page 11).

#### **Hue Adjustment**

Image hue can be adjusted through the SCCB register bits HUE[5:0] (see "HUE" on page 11).

# **Pin Description**

## Table 1Pin Description

| Pin Number | Name      | Pin Type | Default (V)             | Function/Description                                                                                                                                                                         |

|------------|-----------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01         | AGND      | Power    | 0                       | Analog ground                                                                                                                                                                                |

| 02         | AVDD      | Power    | 5                       | Analog Power (+5 VDC)                                                                                                                                                                        |

| 03         | ABRT      | Input    | 0                       | Auto brightness control ON/OFF                                                                                                                                                               |

| 04         | BKLT      | Input    | 0 0: OFF<br>1: ON       |                                                                                                                                                                                              |

| 05         | NC        | —        | —                       | No connection                                                                                                                                                                                |

| 06         | VREQ      | Analog   | 2.5                     | Internal reference                                                                                                                                                                           |

| 07         | VRCHG     | Analog   | 3.6                     | Internal reference                                                                                                                                                                           |

| 08         | NC        |          |                         | No connection                                                                                                                                                                                |

| 09         | NC        |          | _                       | No connection                                                                                                                                                                                |

| 10         | CVO       | Output   | -                       | Composite video output, 2X standard NTSC TV signal                                                                                                                                           |

| 11         | OVDD      | Power    | 5                       | Analog power for video output (+5 VDC)                                                                                                                                                       |

| 12         | EVDD      | Power    | 5 Analog power (+5 VDC) |                                                                                                                                                                                              |

| 13         | EGND      | Power    | 0                       | Analog ground                                                                                                                                                                                |

| 14         | SCCB_E    | Input    | 5                       | SCCB interface enable signal, active low                                                                                                                                                     |

| 15         | VPXO/VFLP | 1/0      | 0                       | Valid pixels detect output. CLK is asserted on this pin during<br>the active image period. Power up initial pin value will be<br>latched as vertical flip ON/OFF control.<br>0: OFF<br>1: ON |

| 16         | XCLK1     | Input    |                         | Crystal clock input. 14.31818 MHz for NTSC                                                                                                                                                   |

| 17         | XCLK2     | Output   | _                       | Crystal clock output                                                                                                                                                                         |

| 18         | DVDD      | Power    | 5                       | Digital power (+5 VDC)                                                                                                                                                                       |

| 19         | DGND      | Power    | 0                       | Digital ground                                                                                                                                                                               |

| 20         | FSI       | Input    | 0                       | Frame synchronizing signal input                                                                                                                                                             |

| 21         | GAMMA     | Input    | 5                       | Gamma function ON/OFF<br>0: OFF<br>1: ON                                                                                                                                                     |

| 22         | VHS/MIR   | I/O      | 0                       | Vertical/Horizontal SYNC output. Power up initial pin value<br>will be latched as mirror function ON/OFF control.<br>0: OFF<br>1: ON                                                         |

## Table 1Pin Description

| Pin Number | Name       | Pin Type | Default (V) | Function/Description                                                                                                                                                               |

|------------|------------|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | FODD/HGAIN | I/O      | 0           | Even/odd field flag and frame synchronize signal output.<br>Power up initial pin value will be latched as AGC gain range<br>control.<br>0: AGC gain 1x - 4x<br>1: AGC gain 1x - 8x |

| 24         | PWDN       | Input    | 0           | Power down mode selection<br>0: OFF<br>1: ON                                                                                                                                       |

| 25         | FASTB      | Input    | 0           | AEC/AGC mode selection<br>0: Fast mode<br>1: Normal mode                                                                                                                           |

| 26         | SIO_C      | Input    |             | SCCB serial interface clock                                                                                                                                                        |

| 27         | SIO_D      | I/O      |             | SCCB serial interface data I/O                                                                                                                                                     |

| 28         | AWB1S      | Input    | 0           | After power up, first high pulse edge will trigger one shot<br>AWB. System performs fast AWB only when this pin is high<br>at this mode.                                           |

## **Electrical Characteristics**

## Table 2Operating Conditions

| Parameter             | Min | Мах | Unit |

|-----------------------|-----|-----|------|

| Operating temperature | 0   | 40  | °C   |

| Storage temperature   | -40 | 125 | °C   |

| Operating humidity    | TBD | TBD |      |

| Storage humidity      | TBD | TBD |      |

# Table 3DC Electrical Characteristics ( $0^{\circ}C \le T_A \le 85^{\circ}C$ )

| Symbol          | Parameter                                | Тур  | Мах | Unit                         |    |  |  |

|-----------------|------------------------------------------|------|-----|------------------------------|----|--|--|

| Supply          |                                          |      |     |                              |    |  |  |

| V <sub>DD</sub> | Supply voltage (AVDD, DVDD, OVDD, EVDD)  | 5.25 | V   |                              |    |  |  |

| I <sub>DD</sub> | Supply current in VDDs (without loading) |      | 20  | —                            | mA |  |  |

| Digital Inpu    | ts                                       |      |     |                              |    |  |  |

| V <sub>IL</sub> | Input voltage LOW                        |      |     | 1.0                          | V  |  |  |

| V <sub>IH</sub> | Input voltage HIGH                       | 3.5  |     |                              | V  |  |  |

| C <sub>IN</sub> | Input capacitor                          |      |     | 10                           | pF |  |  |

| Digital Outp    | puts                                     |      |     |                              |    |  |  |

| V <sub>OH</sub> | Output voltage HIGH                      | 4    |     |                              | V  |  |  |

| V <sub>OL</sub> | Output voltage LOW                       |      |     | 0.6                          | V  |  |  |

| SCCB (SIO       | SCCB (SIO_C and SIO_D)                   |      |     |                              |    |  |  |

| V <sub>IL</sub> | SIO_C and SIO_D                          | -0.5 | 0   | 1                            | V  |  |  |

| V <sub>IH</sub> | SIO_C and SIO_D                          | 3.5  | 5   | V <sub>DD</sub> <u>+</u> 0.5 | V  |  |  |

| Symbol              | Parameter                                 | Min | Тур      | Мах | Unit  |

|---------------------|-------------------------------------------|-----|----------|-----|-------|

| Clock Input         | t/Crystal Oscillator                      |     |          |     |       |

| f <sub>OSC</sub>    | Resonator frequency                       | _   | 14.31818 |     | MHz   |

|                     | Load capacitor                            |     | 33       |     | pF    |

|                     | Parallel resistance                       |     | 1        |     | MΩ    |

|                     | Rise/fall time for external clock input   | _   | 5        |     | ns    |

|                     | Duty cycle for external clock input       | 40  | 50       | 60  | %     |

| CVO Analo           | g Video Output Parameters                 |     |          |     |       |

| V <sub>TO_P</sub>   | Video peak signal level                   | _   | 2.0      |     | V     |

| V <sub>TO_B</sub>   | Video black signal level                  | E   | 0.58     |     | V     |

| V <sub>SYNC</sub>   | Video sync pulse amplitude                | -0  | 0.58     |     | V     |

| Ro                  | Video output load                         |     | 75       |     | Ω     |

| I/O Pin             |                                           |     |          |     |       |

| I <sub>source</sub> | Output pin source current (Output = 1.5v) | 8   | 10       | 12  | mA    |

| l <sub>sink</sub>   | Output pin sink current (Output = 3v)     | 8   | 10       | 12  | mA    |

| Miscellaneo         | ous Timing                                |     |          |     |       |

| t <sub>SYNC</sub>   | External FSI cycle time                   | _   | 2        | _   | field |

| t <sub>PU</sub>     | Chip power up time                        | _   | —        | 100 | μs    |

| t <sub>PD</sub>     | Power up delay time                       | —   | 10       | _   | μs    |

| t <sub>PZ</sub>     | Power up low-z delay                      | _   | 1000     | _   | μs    |

|                     |                                           |     |          |     |       |

# Table 4AC Characteristics ( $T_A = 25^{\circ}C, V_{DD} = 5V$ )

## **Timing Specifications**

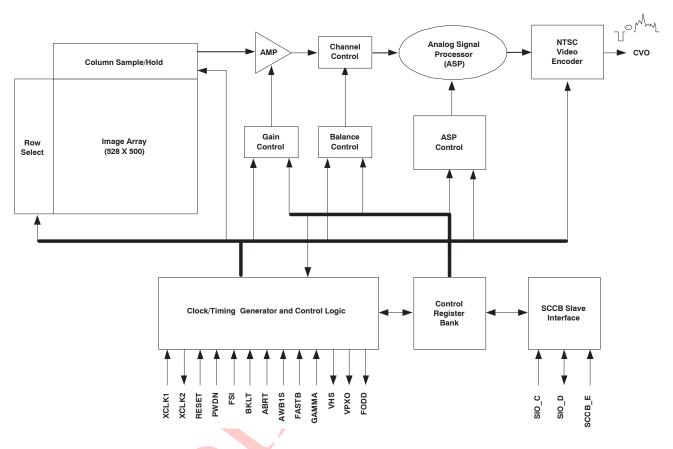

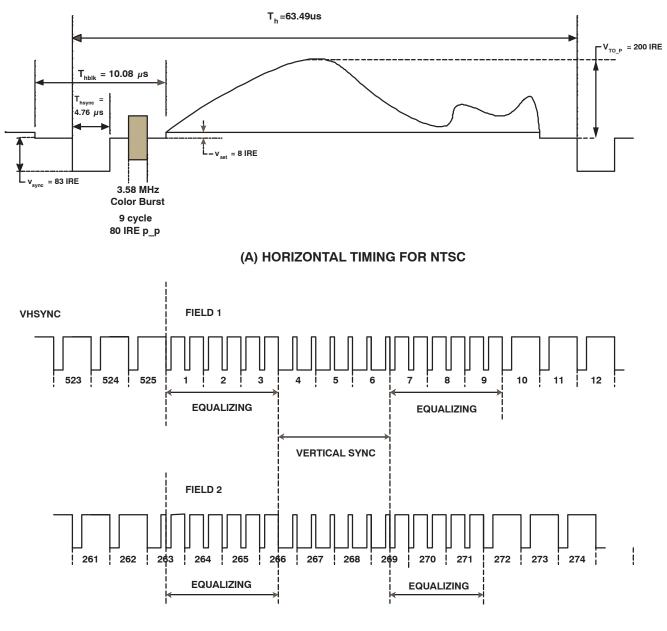

The OV7930 timing is standard NTSC TV timing. Figure 3 shows the NTSC timing and signal range. The OV7930 outputs 2X standard TV signals.

(B) VERTICAL TIMING FOR NTSC

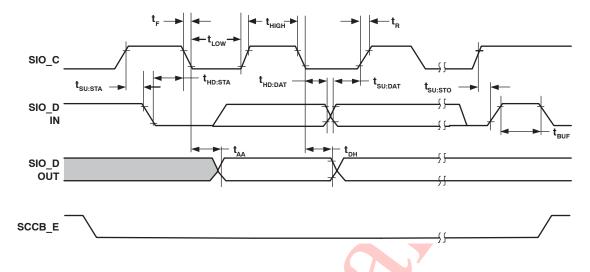

## Figure 4 SCCB Timing Diagram

| Symbol                         | Parameter                      | Min | Тур | Мах | Unit |

|--------------------------------|--------------------------------|-----|-----|-----|------|

| f <sub>SIO_C</sub>             | Clock Frequency                |     |     | 400 | KHz  |

| t <sub>LOW</sub>               | Clock Low Period               | 1.3 |     |     | μS   |

| t <sub>HIGH</sub>              | Clock High Period              | 600 |     |     | ns   |

| t <sub>AA</sub>                | SIO_C low to Data Out valid    | 100 |     | 900 | ns   |

| t <sub>BUF</sub>               | Bus free time before new START | 1.3 |     |     | μS   |

| t <sub>HD:STA</sub>            | START condition Hold time      | 600 |     |     | ns   |

| t <sub>SU:STA</sub>            | START condition Setup time     | 600 |     |     | ns   |

| t <sub>HD:DAT</sub>            | Data-in Hold time              | 0   |     |     | μS   |

| t <sub>SU:DAT</sub>            | Data-in Setup time             | 100 |     |     | ns   |

| t <sub>SU:STO</sub>            | STOP condition Setup time      | 600 |     |     | ns   |

| t <sub>R,</sub> t <sub>F</sub> | SCCB Rise/Fall times           |     |     | 300 | ns   |

| t <sub>DH</sub>                | Data-out Hold time             | 50  |     |     | ns   |

## Table 5 SCCB Timing Specifications

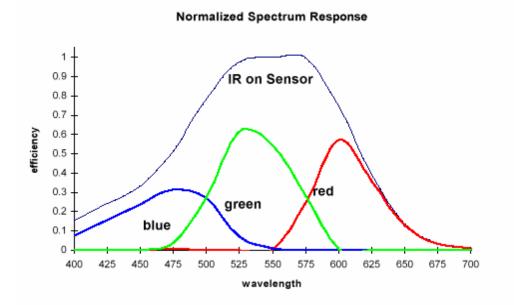

## **OV7930 Light Response**

#### Figure 5 OV7930 Light Response

## **Register Set**

Table 6 provides a list and description of the Device Control registers contained in the OV7930. The device slave addresses are 80 for write and 81 for read.

| Table 6          | Device C         | ontrol Reg       | ister List |                                                                                                                                                                                                                                                                     |  |  |

|------------------|------------------|------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W        | Description                                                                                                                                                                                                                                                         |  |  |

| 00               | GAIN             | 00               | RW         | AGC Gain Control                                                                                                                                                                                                                                                    |  |  |

| 01               | BLUE             | 80               | RW         | Blue Channel Gain Control MSB, 8 bits<br>(LSB 2 bits in register BRLOW[1:0] (see "BRLOW" on page 11).                                                                                                                                                               |  |  |

| 02               | RED              | 80               | RW         | Red Channel Gain Control MSB, 8 bits<br>(LSB 2 bits in register BRLOW[5:4] (see "BRLOW" on page 11).                                                                                                                                                                |  |  |

| 03               | SAT              | 80               | RW         | Saturation Control<br>Bit[7:4]: Saturation adjustment<br>0000: Lowest<br>1111: Highest<br>Bit[3:0]: Reserved                                                                                                                                                        |  |  |

| 04               | HUE              | 10               | RW         | Hue Adjustment Control<br>Bit[7:6]: Reserved<br>Bit[5]: Hue control ON/OFF<br>0: OFF<br>1: ON<br>Bit[4:0]: Hue control setting<br>• Range: -20° to +20° (10000 in the middle)                                                                                       |  |  |

| 05               | RSVD             | XX               | -          | Reserved                                                                                                                                                                                                                                                            |  |  |

| 06               | BRT              | 80               | RW         | <ul> <li>Brightness Adjustment Control</li> <li>Range: [00] to [FF]</li> <li>Note: If auto brightness is enabled, this register will be automatically updated by internal control. If auto brightness is disabled, the user can update brightness value.</li> </ul> |  |  |

| 07               | SHP              | D4               | RW         | Sharpness Adjustment<br>Bit[7:4]: Sharpness ON/OFF threshold<br>Bit[3:0]: Sharpness adjustment                                                                                                                                                                      |  |  |

| 08-09            | RSVD             | XX               | _          | Reserved                                                                                                                                                                                                                                                            |  |  |

| 0A               | BRLOW            | 00               | RW         | Blue/Red Channel Gain LSBs<br>Bit[7:6]: Reserved<br>Bit[5:4]: Red channel AWB gain two lower bits<br>Bit[3:2]: Reserved<br>Bit[1:0]: Blue channel AWB gain two lower bits                                                                                           |  |  |

| 0B-0D            | RSVD             | XX               | -          | Reserved                                                                                                                                                                                                                                                            |  |  |

| 0E               | СОМВ             | 96               | RW         | Common Control B<br>Bit[7]: Edge enhancement ON/OFF<br>0: OFF<br>1: ON<br>Bit[6:0]: Reserved                                                                                                                                                                        |  |  |

## Table 6 Device Control Register List

| Table 6 | Device Control Register List |

|---------|------------------------------|

|         | Device Control Register List |

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------|------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0F               | RSVD             | XX               | -   | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 10               | VER              | 01               | R   | Version number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11               | MIDH             | 7F               | R   | Manufacturer ID Byte High (Read only = 0x7F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 12               | MIDL             | A2               | R   | Manufacturer ID Byte – Low (Read only = 0xA2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 13               | AEC              | 82               | RW  | Exposure Control Value<br>• Range: [00] to [82]<br>Tex = (2 x AEC[7:0] + 1) x 63.5 µs                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14               | COMD             | 1F               | RW  | Common Control D<br>Bit[7:6]: AEC/AGC algorithm analyze image area selection<br>00: Whole image<br>01: Lower two-thirds image<br>10: Lower one-half image<br>11: Lower one-third image<br>Bit[5:3]: Reserved<br>Bit[2]: AGC ON/OFF<br>0: OFF<br>1: ON<br>Bit[1]: AWB ON/OFF<br>0: OFF<br>1: ON<br>Bit[0]: AEC ON/OFF<br>0: OFF<br>1: ON<br>Bit[0]: AEC ON/OFF<br>0: OFF<br>1: ON                                                                                                                                                                     |

| 15               | COME             | 04               | RW  | Common Control E<br>Bit[7]: SRST<br>1: Initiates soft reset. All registers are set to default<br>values after which the chip resumes normal<br>operation.<br>Bit[6]: Mirror image selection<br>0: Normal<br>1: Output mirror image<br>Bit[5]: Vertical sync option (see "COMG" on page 13 for details)<br>Bit[4]: Backlight exposure mode ON/OFF<br>0: OFF<br>1: ON<br>Bit[3]: Reserved<br>Bit[2]: AGC gain ceiling selection - combined with COMJ[3] (see<br>"COMJ" on page 13) as follows:<br>0: 1x to 4x<br>1: 1x to 8x/16x<br>Bit[1:0]: Reserved |

| 16               | COMF             | 44               | RW  | Common Control F<br>Bit[7:3]: Reserved<br>Bit[2]: Banding filter ON/OFF<br>0: OFF<br>1: ON<br>Bit[1:0]: Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Table 6 Device Control Register List

| Address<br>(Hex) | Register<br>Name | Default<br>(Hex) | R/W       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------|------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17               | COMG             | 95               | RW        | Common Control G         Bit[7]:       Fast AGC/AEC algorithm ON/OFF         0:       OFF         1:       ON         Bit[6:5]:       Reserved         Bit[4]:       FODD pin (pin 23 - see "FODD/HGAIN" on page 5) output signal selection - combined with COME[5] (see "COME" on page 12) as follows:         COMG[4]       COME[5]       FODD (pin 23)         0       0       VSYNC every field         0       1       VSYNC every two fields         1       X       FODD (odd field flagged)         Bit[3:0]:       Reserved |

| 18               | AECPT            | A5               | RW        | AEC/AGC Luminance Level Control<br>Bit[7:4]: Low level luminance percentage<br>Bit[3:0]: High level luminance percentage<br><b>Note:</b> Stable condition is AECPT[7:4] + AECPT[3:0] > 0x0E.                                                                                                                                                                                                                                                                                                                                         |

| 19               | ВКРТ             | 59               | RW        | AEC/AGC Luminance Level Control in Backlight Mode<br>Bit[7:4]: Low level luminance percentage in backlight mode<br>Bit[3:0]: High level luminance percentage in backlight mode<br><b>Note:</b> Stable condition is BKPT[7:4] + BKPTT[3:0] > 0x0E.                                                                                                                                                                                                                                                                                    |

| 1A-1C            | RSVD             | XX               |           | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1D               | СОМЈ             | 30               | RW        | Common Control J<br>Bit[7]: Pixel clock polarity selection<br>0: Normal<br>1: Revised pixel clock output<br>Bit[6:4]: Reserved<br>Bit[3]: AGC gain ceiling - in effect only if COME[2] = "1" (see<br>"COME" on page 12)<br>0: 8X<br>1: 16X<br>Bit[2]: Reserved<br>Bit[2]: Reserved<br>Bit[1]: NTSC with 50 Hz light compensation. In effect only when<br>COMD[0] = "1" (see "COMD" on page 12) and<br>COMF[2] = "1" (see "COMF" on page 12)<br>Bit[0]: Vertical flip selection<br>0: Normal<br>1: Vertical flip output image         |

| 1E-20            | RSVD             | XX               | _         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 21               | VPT              | A4               | RW        | AEC/AGC Fast mode threshold<br>Bit[7:4]: Fast AEC/AGC low level percentage threshold<br>Bit[3:0]: Fast AEC/AGC high level percentage threshold                                                                                                                                                                                                                                                                                                                                                                                       |

| 22-33            | RSVD             | XX               | -         | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NOTE: All        | other register   | rs are factory   | -reserved | . Please contact OmniVision Technologies for reference register settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

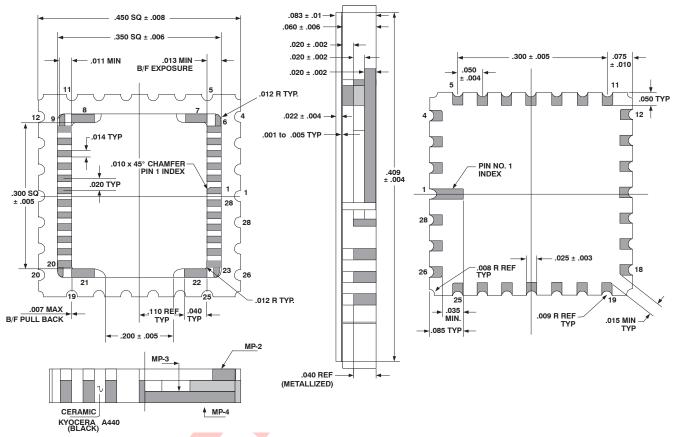

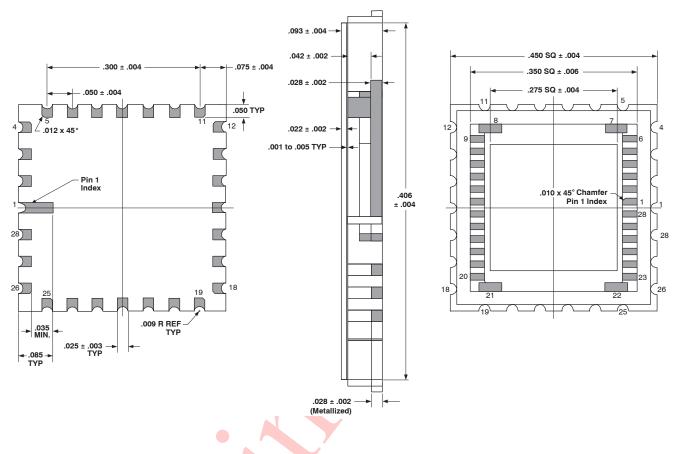

## **Package Specifications**

The OV7930 uses either a 28-pin ceramic package or 28-pin plastic package. Refer to Figure 6 for ceramic package information, Figure 7 for plastic package information, and Figure 8 for the array center on the chip.

Table 7

OV7930 Ceramic Package Dimensions

| Dimensions                        | Millimeters (mm)       | Inches (in.)          |

|-----------------------------------|------------------------|-----------------------|

| Package Size                      | 11.43 <u>+</u> 0.20 SQ | .450 <u>+</u> .008 SQ |

| Package Height                    | 2.11 <u>+</u> 0.25     | .083 <u>+</u> .01     |

| Substrate Height                  | 0.51 <u>+</u> 0.05     | .020 <u>+</u> .002    |

| Cavity Size                       | 7.62 <u>+</u> 0.13 SQ  | .300 <u>+</u> .005 SQ |

| Castellation Height               | 1.02 <u>+</u> 0.1      | .040 <u>+</u> .004    |

| Pin #1 Pad Size                   | 0.64 x 2.16            | .025 x .085           |

| Pad Size                          | 0.64 x 1.27            | .025 x .050           |

| Pad Pitch                         | 1.27 <u>+</u> 0.10     | .050 <u>+</u> .004    |

| Package Edge to First Lead Center | 1.91 <u>+</u> 0.25     | .075 <u>+</u> .010    |

| End-to-End Pad Center-Center      | 7.62 <u>+</u> 0.13     | .300 <u>+</u> .005    |

| Glass Size                        | 10.41 <u>+</u> 0.10 SQ | .409 <u>+</u> .004 SQ |

| Glass Height                      | 0.55 <u>+</u> 0.05     | .022 <u>+</u> .002    |

## Table 8 OV7930 Plastic Package Dimensions

| Dimensions                        | Millimeters (mm)       | Inches (in.)          |

|-----------------------------------|------------------------|-----------------------|

| Package Size                      | 11.43 <u>+</u> 0.10 SQ | .450 <u>+</u> .004 SQ |

| Package Height                    | 2.35 <u>+</u> 0.1      | .093 <u>+</u> .004    |

| Substrate Height                  | 0.70 <u>+</u> 0.05     | .028 <u>+</u> .002    |

| Cavity Size                       | 7.00 <u>+</u> 0.10 SQ  | .275 <u>+</u> .004 SQ |

| Castellation Height               | 1.07 <u>+</u> 0.05     | .042 <u>+</u> .002    |

| Pin #1 Pad Size                   | 0.64 x 2.16            | .025 x .085           |

| Pad Size                          | 0.64 x 1.27            | .025 x .050           |

| Pad Pitch                         | 1.27 <u>+</u> 0.10     | .050 <u>+</u> .004    |

| Package Edge to First Lead Center | 1.90 <u>+</u> 0.10     | .075 <u>+</u> .004    |

| End-to-End Pad Center-Center      | 7.62 <u>+</u> 0.10     | .300 <u>+</u> .004    |

| Glass Size                        | 10.30 <u>+</u> 0.10 SQ | .406 <u>+</u> .004 SQ |

| Glass Height                      | 0.55 <u>+</u> 0.05     | .022 <u>+</u> .002    |

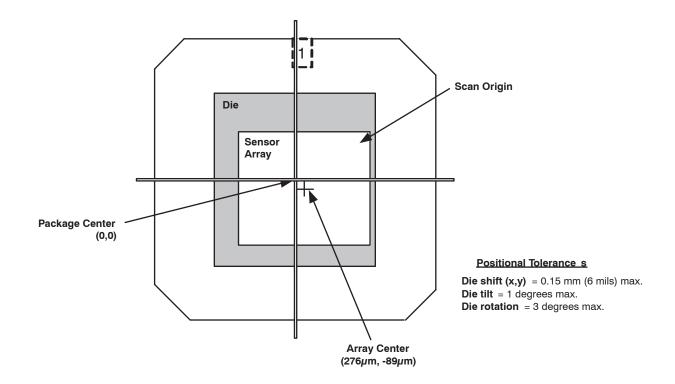

## **Sensor Array Center**

#### Figure 8 OV7930 Sensor Array Center

NOTES: 1. This drawing is not to scale and is for reference only.

2. As most optical assemblies invert and mirror the image, the chip is typically mounted with pin one oriented down on the PCB.

# <u>Note</u>:

- All information shown herein is current as of the revision and publication date. Please refer to the OmniVision web site (<u>http://www.ovt.com</u>) to obtain the current versions of all documentation.

- OmniVision Technologies, Inc. reserves the right to make changes to their products or to discontinue any product or service without further notice (It is advisable to obtain current product documentation prior to placing orders).

- Reproduction of information in OmniVision product documentation and specifications is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. In such cases, OmniVision is not responsible or liable for any information reproduced.

- This document is provided with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. Furthermore, OmniVision Technologies Inc. disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this document. No license, expressed or implied, by estoppels or otherwise, to any intellectual property rights is granted herein.

- 'OmniVision', 'CameraChip' are trademarks of OmniVision Technologies, Inc. All other trade, product or service names referenced in this release may be trademarks or registered trademarks of their respective holders. Third-party brands, names, and trademarks are the property of their respective owners.

For further information, please feel free to contact OmniVision at info@ovt.com.

OmniVision Technologies, Inc. Sunnyvale, CA USA (408) 733-3030